Изобретение относится к области автоматики и вычислительной техники и может быть использовано в выводных графических устройствах и в системах числового программного управления.

Цель изобретения - расширение области применения интерполятора за счет формирования векторов во всех квадрантах, а также повышение его быстродействия за счет останова интерполяции при реализации отсечения.

В известных линейных интерполяторах интерполяция происходит, как в поле индикации (ПИ) (экран дисплея), так и в невиди- зоне поля дискретного координатного пространства (ПДКП). В свою очередь, ПИ

является четвертой частью поля видеопамяти (ПВ), которое ограничивается сигналом регистрации границы поля видеопамяти (РГВП).

Таким образом, ПИ и ПВ являются подмножеством ПДКП, которое ограничивается координатными счетчиками Рх - по оси X и Ру - по оси Y. Сигнал РГПВ зависит от глубины видеопамяти и отслеживается до определенного значения координ ными счетчиками. В ПИ интерполяция отрезка сводится к отображению его на экране дисплея, а вне ПИ интерполяция невидимой части отрезка прямой сводится к попаданию в конечную точку, которая может быть начальной для последующего отрезка. Т.е.

со

о ел

N 4 Ю

время на интерполяцию отрезка можно разделить на эффективно затраченное и неэффективно затраченное : Ти Тэ + Тнэ. Следовательно, в таких линейных интерпо- ляторах время интерполяции заданного отрезка прямой увеличивается за счет неэффективной составляющей (интерполяция в невидимой зоне). Очевидно, интерполяцию в невидимой зоне можно не производить:, а конечную точку можно спо зициониро$ать программным путем.

В предлагаемом цифровом линейном интерполяторе за счет введения блока отсечения (БО) в определенных случаях выполняется процедура отсечения, с помощью которой отбрасывается составляющая ТНз.

Таким образом, сокращается общее время интерполяции Ти заданного отрезка прямой. Чем длиннее часть отрезка в невидимой зоне, тем значительней экономится время на его интерполяцию. Следовательно, увеличивается быстродействие интерпо- лятора.

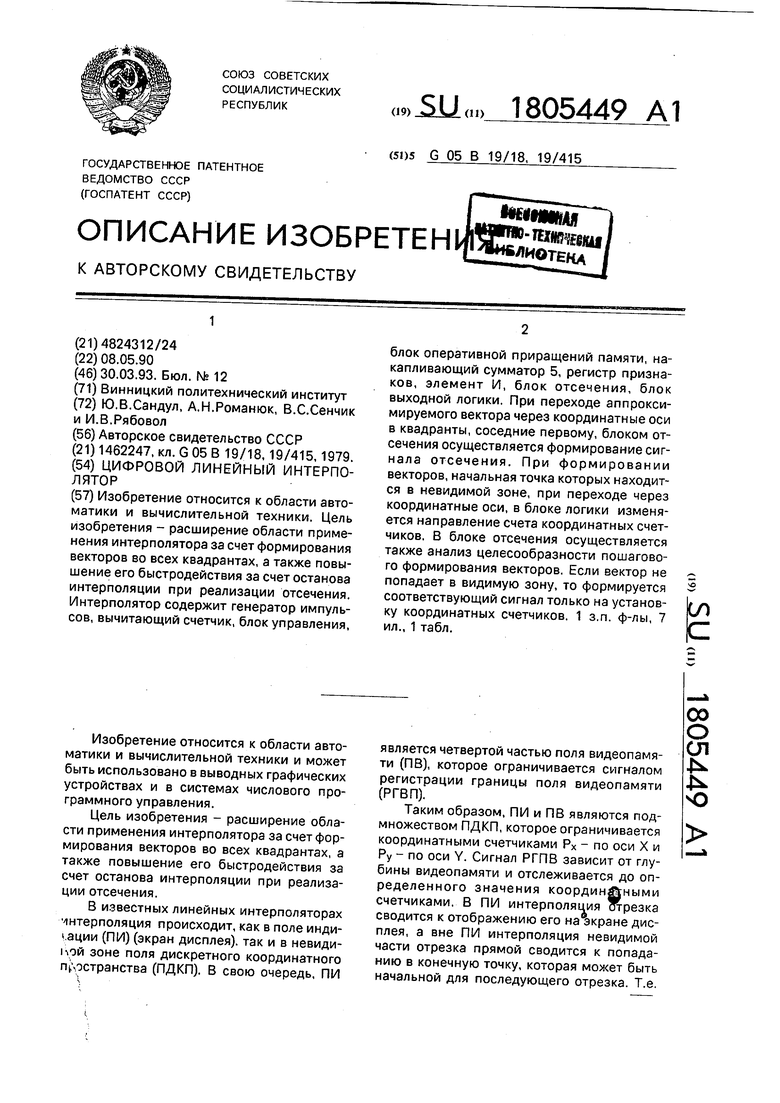

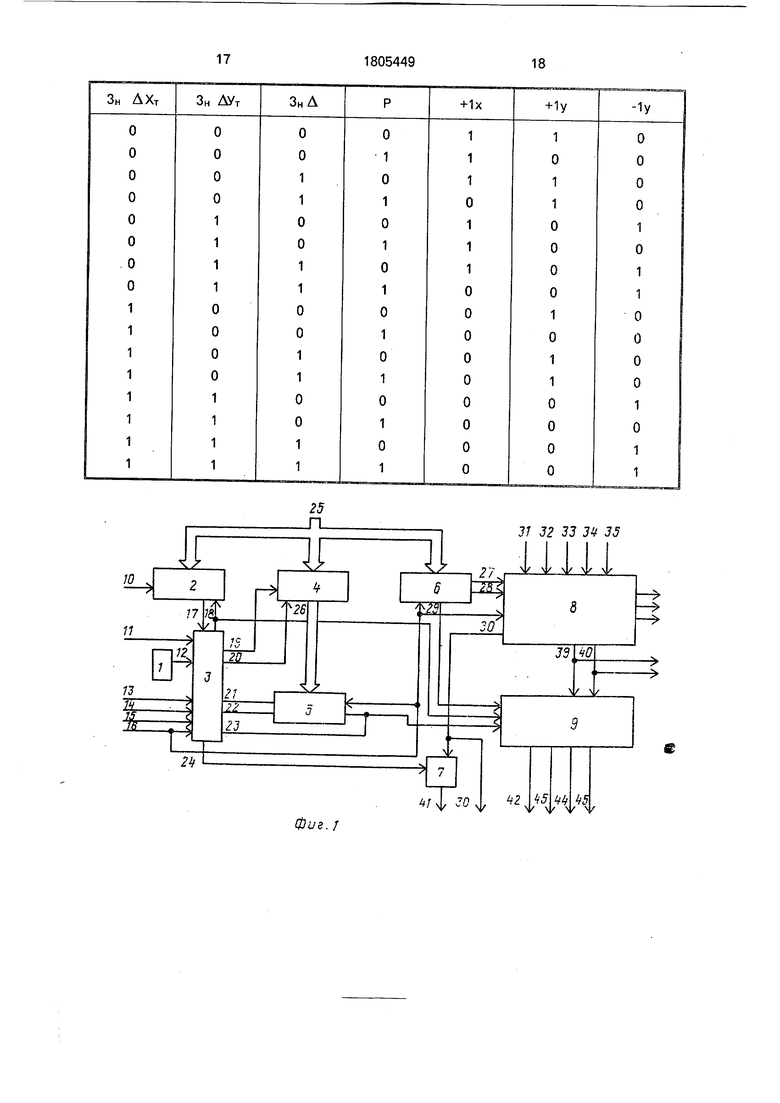

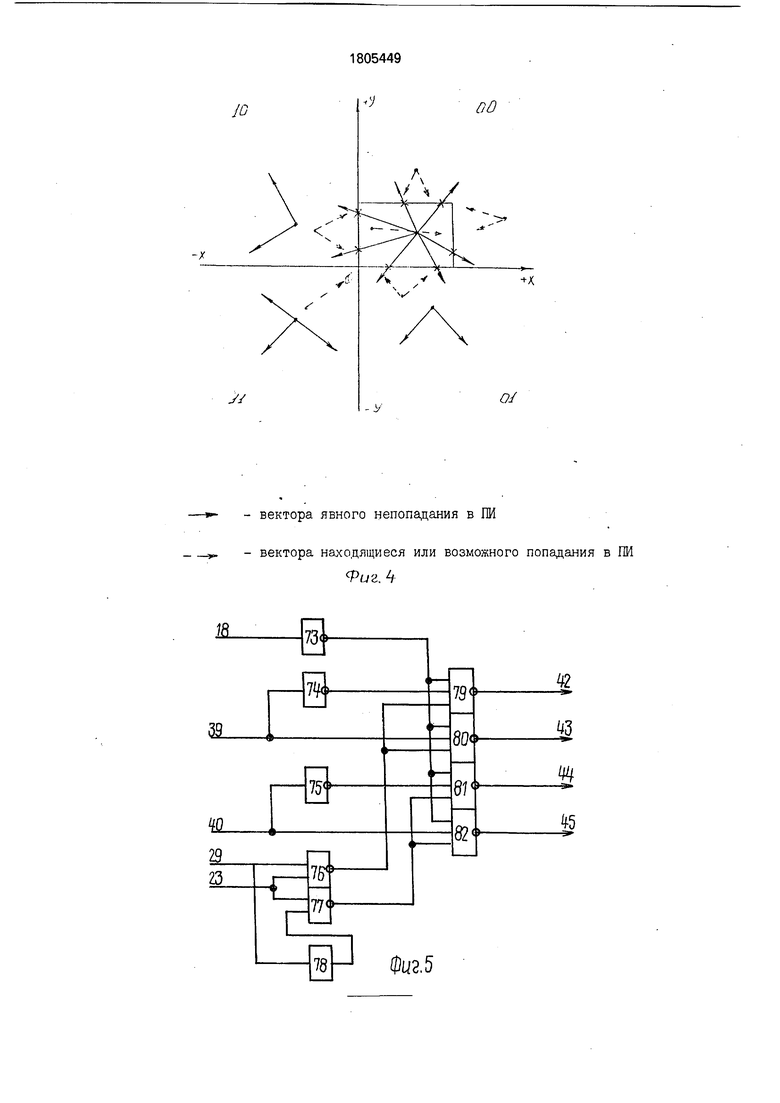

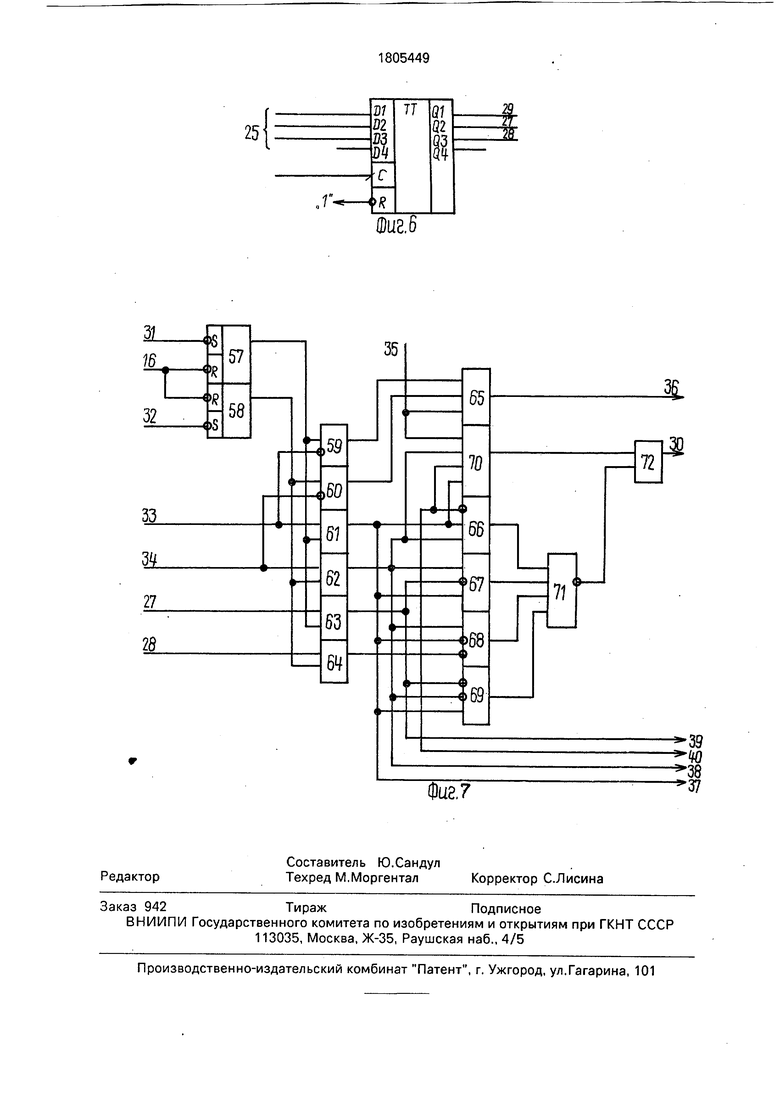

На фиг. 1 представлена структурная схема предлагаемого цифрового линейного интерполятора; на фиг. 2 - пример реализации блока отсечения; на фиг. 3 - взаимное расположение поля дискретного координатного пространства (ПДКП) Рх; Ру; -Ру; -Рх; поля индикации (ПИ) OLMN, поля видеопамяти (ПВ) WMDE, которые являются подмножеством ПДКП, разбиение ПДКП на квадранты, формирование в ПДКП векторов АВ и ВК и точки отсечения S и Т данных векторов с осями координат; на фиг. 4 - расположение и направление векторов, подлежащих процедуре отсечения; на фиг.

5 - пример блока выходной логики; на фиг.

6 - блок регистров; на фиг. 7 - блок отсечения.

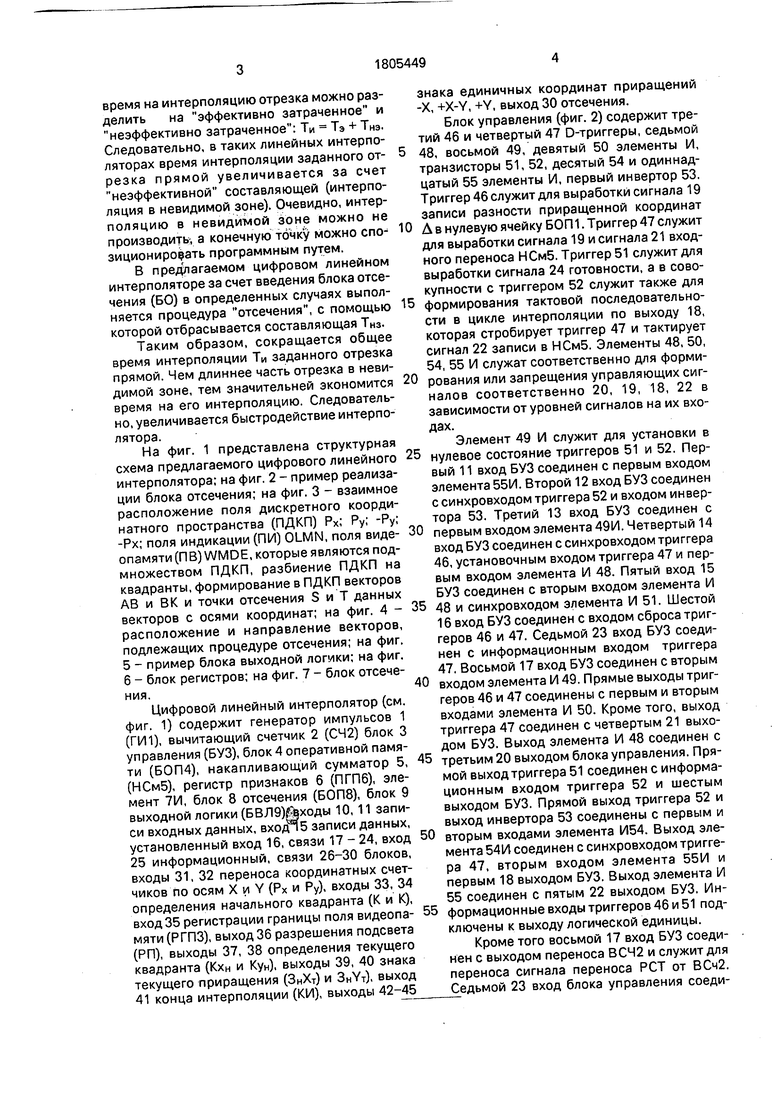

Цифровой линейный интерполятор (см. фиг. 1) содержит генератор импульсов 1 (ГИ1), вычитающий счетчик 2 (СЧ2) блок 3 управления (БУЗ), блок 4 оперативной памяти (БОП4), накапливающий сумматор 5, (НСм5), регистр признаков 6 (ПГП6), элемент 7И, блок 8 отсечения (БОП8), блок 9 выходной логики (БВЛ9)йвходы 10, 11 записи входных данных, входЧ5 записи данных, установленный вход 16, связи 17 - 24, вход 25 информационный, связи 26-30 блоков, входы 31, 32 переноса координатных счетчиков по осям X и Y (Рх и Ру), входы 33, 34 определения начального квадранта (К и К), вход 35 регистрации границы поля видеопамяти (РГПЗ), выход 36 разрешения подсвета (РП), выходы 37, 38 определения текущего квадранта (Кхн и Кун), выходы 39, 40 знака текущего приращения (3НХТ) и SnYj), выход 41 конца интерполяции (КИ), выходы 42-45

знака единичных координат приращений -X, +X-Y, +Y, выход 30 отсечения.

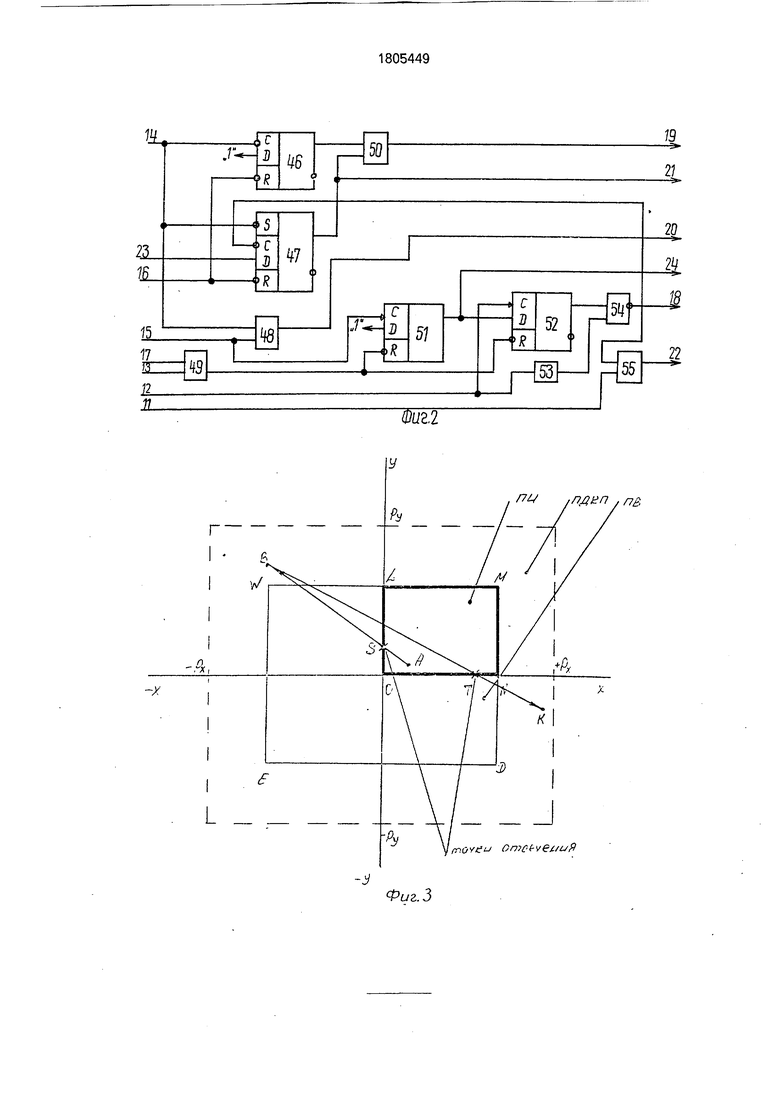

Блок управления (фиг. 2) содержит третий 46 и четвертый 47 D-триггеры, седьмой

48, восьмой 49, девятый 50 элементы И, транзисторы 51, 52, десятый 54 и одиннадцатый 55 элементы И, первый инвертор 53. Триггер 46 служит для выработки сигнала 19 записи разности приращенной координат

0 А в нулевую ячейку БОП1. Триггер 47 служит для выработки сигнала 19 и сигнала 21 входного переноса НСм5. Триггер 51 служит для выработки сигнала 24 готовности, а в совокупности с триггером 52 служит также для

5 формирования тактовой последовательности в цикле интерполяции по выходу 18, которая стробирует триггер 47 и тактирует сигнал 22 записи в НСм5. Элементы 48, 50, 54, 55 И служат соответственно для форми0 рования или запрещения управляющих сигналов соответственно 20, 19, 18, 22 в зависимости от уровней сигналов на их входах.

Элемент 49 И служит для установки в

5 нулевое состояние триггеров 51 и 52. Первый 11 вход БУЗ соединен с первым входом элемента 55И. Второй 12 вход БУЗ соединен с синхровходом триггера 52 и входом инвертора 53. Третий 13 вход БУЗ соединен с

0 первым входом элемента 49И. Четвертый 14 вход БУЗ соединен с синхровходом триггера 46, установочным входом триггера 47 и первым входом элемента И 48. Пятый вход 15 БУЗ соединен с вторым входом элемента И

5 48 и синхровходом элемента И 51. Шестой 16 вход БУЗ соединен с входом сброса триггеров 46 и 47. Седьмой 23 вход БУЗ соединен с информационным входом триггера 47. Восьмой 17 вход БУЗ соединен с вторым

0 входом элемента И 49. Прямые выходы триггеров 46 и 47 соединены с первым и вторым входами элемента И 50. Кроме того, выход триггера 47 соединен с четвертым 21 выходом БУЗ. Выход элемента И 48 соединен с

5 третьим 20 выходом блока управления. Прямой выход триггера 51 соединен с информационным входом триггера 52 и шестым выходом БУЗ. Прямой выход триггера 52 и выход инвертора 53 соединены с первым и

0 вторым входами элемента И54. Выход элемента 541/1 соединен с синхровходом триггера 47, вторым входом элемента 55И и первым 18 выходом БУЗ. Выход элемента И 55 соединен с пятым 22 выходом БУЗ. Ин5 формационные входы триггеров 46 и 51 подключены к выходу логической единицы.

Кроме того восьмой 17 вход БУЗ соединен с выходом переноса ВСЧ2 и служит для переноса сигнала переноса РСТ от ВСч2. Седьмой 23 вход блока управления соединен с выходом переноса накапливающего сумматора 5 и служит для приема сигнала переполнения накапливающего сумматора, который фиксируется триггером 47.

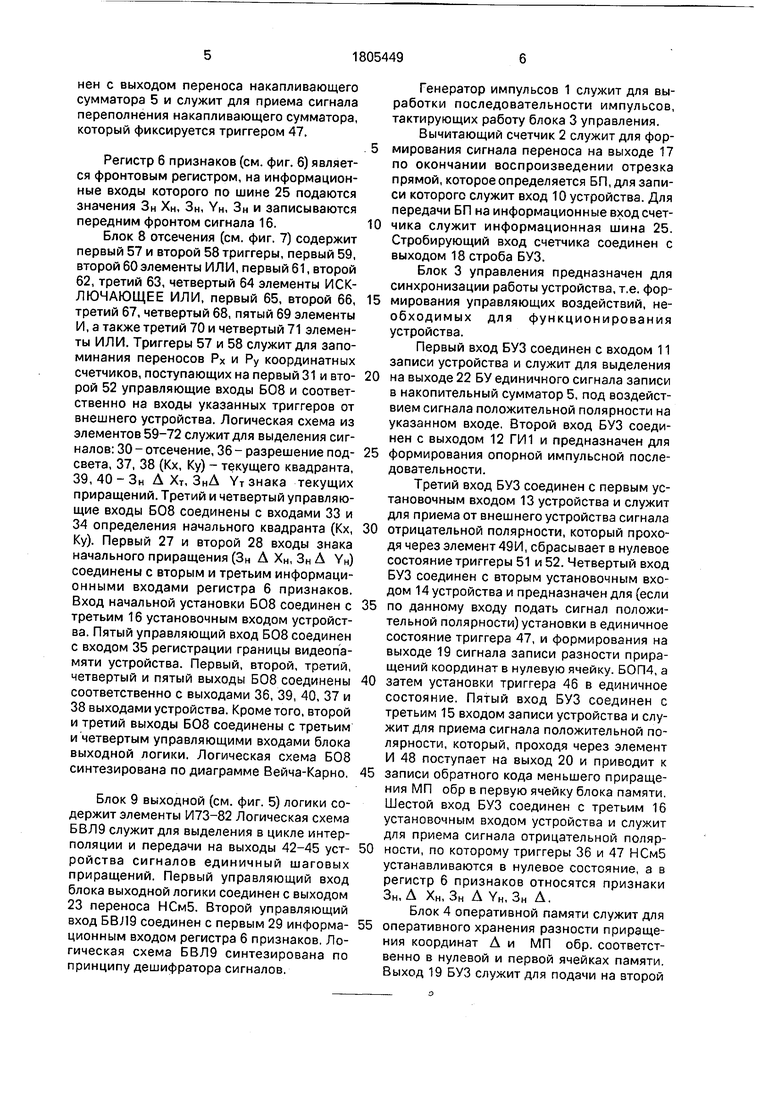

Регистр 6 признаков (см. фиг. 6) является фронтовым регистром, на информационные входы которого по шине 25 подаются значения Зн Хн, Зн, YH, Зн и записываются передним фронтом сигнала 16.

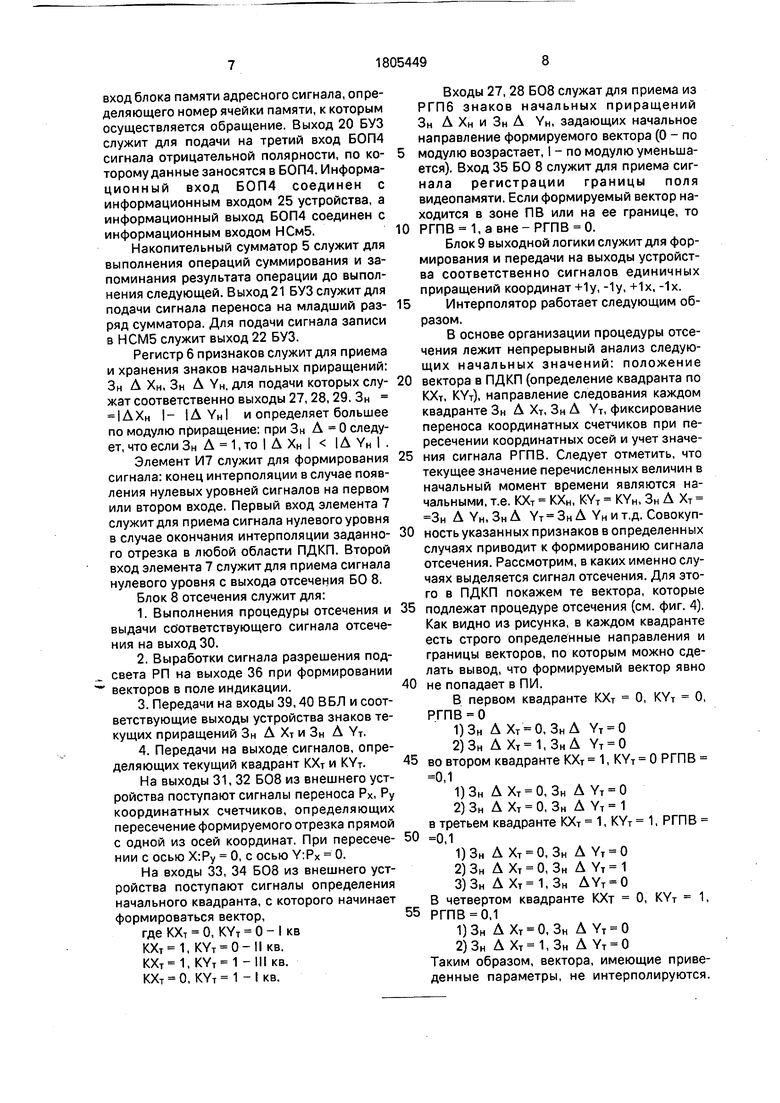

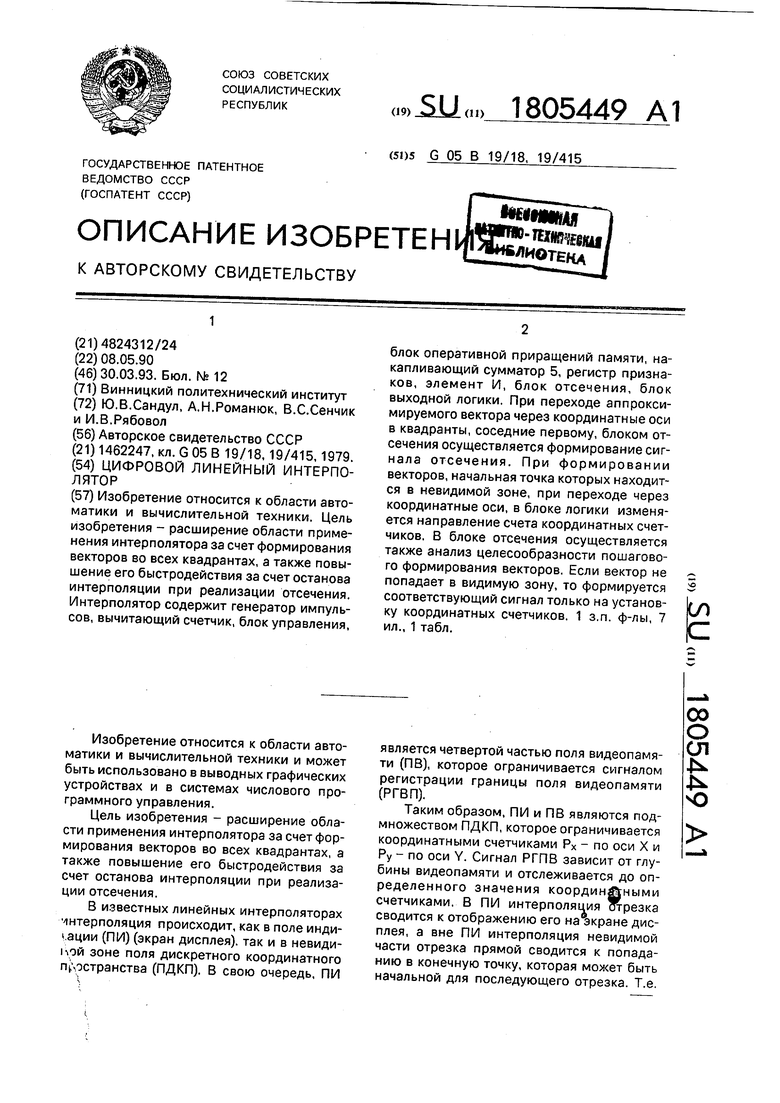

Блок 8 отсечения (см. фиг. 7) содержит первый 57 и второй 58 триггеры, первый 59, второй 60 элементы ИЛИ, первый 61, второй 62, третий 63, четвертый 64 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 65, второй 66, третий 67, четвертый 68, пятый 69 элементы И, а также третий 70 и четвертый 71 элементы ИЛИ. Триггеры 57 и 58 служит для запоминания переносов Рх и Ру координатных счетчиков, поступающих на первый 31 и второй 52 управляющие входы Б08 и соответственно на входы указанных триггеров от внешнего устройства. Логическая схема из элементов 59-72 служит для выделения сигналов: 30 - отсечение, 36 - разрешение подсвета, 37, 38 (Кх, Ку) - текущего квадранта, 39, 40-Зн А Хт, ЗиЛ YT знака текущих приращений. Третий и четвертый управляющие входы Б08 соединены с входами 33 и 34 определения начального квадранта (Кх, Ку). Первый 27 и второй 28 входы знака начального приращения (Зн А Хн, Зн A YH) соединены с вторым и третьим информационными входами регистра 6 признаков. Вход начальной установки Б08 соединен с третьим 16 установочным входом устройства. Пятый управляющий вход Б08 соединен с входом 35 регистрации границы видеопамяти устройства. Первый, второй, третий, четвертый и пятый выходы Б08 соединены соответственно с выходами 36, 39, 40, 37 и 38 выходами устройства. Кроме того, второй и третий выходы Б08 соединены с третьим и четвертым управляющими входами блока выходной логики. Логическая схема Б08 синтезирована по диаграмме Вейча-Карно.

Блок 9 выходной (см. фиг. 5) логики содержит элементы И73-82 Логическая схема БВЛ9 служит для выделения в цикле интерполяции и передачи на выходы 42-45 устройства сигналов единичный шаговых приращений. Первый управляющий вход блока выходной логики соединен с выходом 23 переноса НСм5. Второй управляющий вход БВЛ9 соединен с первым 29 информационным входом регистра 6 признаков, Логическая схема БВЛ9 синтезирована по принципу дешифратора сигналов.

Генератор импульсов 1 служит для выработки последовательности импульсов, тактирующих работу блока 3 управления. Вычитающий счетчик 2 служит для фор5 мирования сигнала переноса на выходе 17 по окончании воспроизведении отрезка прямой, которое определяется БП, для записи которого служит вход 10 устройства. Для передачи БП на информационные вход счет0 чика служит информационная шина 25. Стробирующий вход счетчика соединен с выходом 18 строба БУЗ.

Блок 3 управления предназначен для синхронизации работы устройства, т.е. фор5 мирования управляющих воздействий, необходимых для функционирования устройства.

Первый вход БУЗ соединен с входом 11 записи устройства и служит для выделения

0 на выходе 22 БУ единичного сигнала записи в накопительный сумматор 5, под воздействием сигнала положительной полярности на указанном входе. Второй вход БУЗ соединен с выходом 12 ГИ1 и предназначен для

5 формирования опорной импульсной последовательности.

Третий вход БУЗ соединен с первым установочным входом 13 устройства и служит для приема от внешнего устройства сигнала

0 отрицательной полярности, который проходя через элемент 49И, сбрасывает в нулевое состояние триггеры 51 и 52. Четвертый вход БУЗ соединен с вторым установочным входом 14 устройства и предназначен для (если

5 по данному входу подать сигнал положительной полярности) установки в единичное состояние триггера 47, и формирования на выходе 19 сигнала записи разности приращений координат в нулевую ячейку. БОП4, а

0 затем установки триггера 46 в единичное состояние. Пятый вход БУЗ соединен с третьим 15 входом записи устройства и служит для приема сигнала положительной полярности, который, проходя через элемент И 48 поступает на выход 20 и приводит к

5 записи обратного кода меньшего приращения МП обр в первую ячейку блока памяти. Шестой вход БУЗ соединен с третьим 16 установочным входом устройства и служит для приема сигнала отрицательной поляр0 ности, по которому триггеры 36 и 47 НСм5 устанавливаются в нулевое состояние, а в регистр 6 признаков относятся признаки Зн, А Хн, Зн A YH, Зн А.

Блок 4 оперативной памяти служит для

5 оперативного хранения разности приращения координат А и МП обр. соответственно в нулевой и первой ячейках памяти. Выход 19 БУЗ служит для подачи на второй

вход блока памяти адресного сигнала, определяющего номер ячейки памяти, к которым осуществляется обращение. Выход 20 БУЗ служит для подачи на третий вход БОП4 сигнала отрицательной полярности, по которому данные заносятся в БОП4. Информационный вход БОП4 соединен с информационным входом 25 устройства, а информационный выход БОП4 соединен с информационным входом НСм5.

Накопительный сумматор 5 служит для выполнения операций суммирования и запоминания результата операции до выполнения следующей. Выход 21 БУЗ служит для подачи сигнала переноса на младший разряд сумматора. Для подачи сигнала записи в НСМ5 служит выход 22 БУЗ.

Регистр 6 признаков служит для приема и хранения знаков начальных приращений: Зн А Хн, Зн A YH, для подачи которых служат соответственно выходы 27, 28,29. Зн |АХН I- IA YHI и определяет большее по модулю приращение: при Зн А 0 следует, что если Зн А 1, то I A XH I IA YH I .

Элемент И7 служит для формирования сигнала: конец интерполяции в случае появления нулевых уровней сигналов на первом или втором входе. Первый вход элемента 7 служит для приема сигнала нулевого уровня в случае окончания интерполяции заданного отрезка в любой области ПДКП. Второй вход элемента 7 служит для приема сигнала нулевого уровня с выхода отсечения БО 8.

Блок 8 отсечения служит для:

1. Выполнения процедуры отсечения и выдачи соответствующего сигнала отсечения на выход 30.

2. Выработки сигнала разрешения подсвета РП на выходе 36 при формировании векторов в поле индикации.

3. Передачи на входы 39,40 ВБЛ и соответствующие выходы устройства знаков текущих приращений Зн А Хт и Зн A YT.

4. Передачи на выходе сигналов, определяющих текущий квадрант КХТ и KYT.

На выходы 31, 32 Б08 из внешнего устройства поступают сигналы переноса Рх, Ру координатных счетчиков, определяющих пересечение формируемого отрезка прямой с одной из осей координат. При пересечении с осью Х:РУ 0, с осью Y:PX 0.

На входы 33, 34 Б08 из внешнего устройства поступают сигналы определения начального квадранта, с которого начинает формироваться вектор,

где КХТ О, KYT 0 - I кв

, KYT 0-II кв.

, -III кв.

КХТ О, KYT 1 - I кв.

Входы 27, 28 Б08 служат для приема из РГП6 знаков начальных приращений Зн А Хн и Зн A YH, задающих начальное направление формируемого вектора (0 - по

модулю возрастает, I - по модулю уменьшается). Вход 35 БО 8 служит для приема сигнала регистрации границы поля видеопамяти. Если формируемый вектор находится в зоне ПВ или на ее границе, то

РГПВ 1,авне-РГПВ 0.

Блок 9 выходной логики служит для формирования и передачи на выходы устройства соответственно сигналов единичных приращений координат +1у, -1у, +1х, -1х.

Интерполятор работает следующим образом.

В основе организации процедуры отсечения лежит непрерывный анализ следующих начальных значений: положение

вектора в ПДКП (определение квадранта по КХТ, KYT), направление следования каждом квадранте Зн А Хт, Зн A YT, фиксирование переноса координатных счетчиков при пересечении координатных осей и учет значения сигнала РГПВ. Следует отметить, что текущее значение перечисленных величин в начальный момент времени являются начальными, т.е. КХТ КХН, KYT - KYH, Зн А Хт 3Н A YH, Зн A YT Зн A YH и т.д. Совокупность указанных признаков в определенных случаях приводит к формированию сигнала отсечения. Рассмотрим, в каких именно случаях выделяется сигнал отсечения. Для этого в ПДКП покажем те вектора, которые

подлежат процедуре отсечения (см. фиг. 4). Как видно из рисунка, в каждом квадранте есть строго определенные направления и границы векторов, по которым можно сделать вывод, что формируемый вектор явно

не попадает в ПИ.

В первом квадранте КХТ О, KYT О, РГПВ О

1)3Н Д Хт 0, ЗнА YT 0

2)3Н Д ,ЗнД YT 0 во втором квадранте КХТ 1, KYT О РГПВ 0,1

1)3Н АХТ 0, Зн A YT 0

2) Зн А Хт О, Зн A YT 1 в третьем квадранте КХТ 1, KYT 1, РГПВ 0,1

1) Зн А Хт О, Зн A YT О

2) Зн А Хт 0, Зн A YT 1

3)3Н А ,3Н AYT 0 В четвертом квадранте КХт О, KYT 1, РГПВ 0,1

1)3Н Д Хт 0, Зн A YT 0

2)3Н Д ,3н A YT 0 Таким образом, вектора, имеющие приведенные параметры, не интерполируются.

Задавши начальные условия таких векторов или если в процессе работы они преобразуют такие параметры, на выходе 30 Б08 вырабатывается сигнал отсечения, который передается на выход 41 Конец интерполяции. Позиционирование конечной точки вектора осуществляется внешним устройством программным путем. Вектора, имеющие оставшиеся параметры, относятся к группе находящихся в ПИ или возможного попадания в ПИ. Поэтому вектора данной группы интерполируются с анализом текущих параметров. Основополагающим фактором данного анализа является пересечение вектора с одной из осей координат, которое фиксируется переносом координатных счетчиков (см. фиг. 3). В момент пересечения изменяются текущие параметры формируемого вектора; текущий квадрант и текущее значение приращений. Следовательно, по-новому происходит новый анализ возможностей попадания вектора в ПИ. Если в момент пересечения текущие параметры вектора становятся такими, как в вышеприведенных случаях, то в данный момент на выходе 30 Б08 формируется сигнал отсечения.

Таким образом, текущие значения векторов изменяются при пересечении вектора одной из осей координат. В момент пересечения происходит анализ текущих параметров. Если измененные параметры формируемого вектора относятся к вышеприведенной группе явного непопадания в ПИ, то на выходе 30 Б08 формируется сигнал отсечения.

Рассмотрим группу векторов возможного попадания в ПИ или находящихся в ней (см. фиг. 4). Это вектора, имеющие следующие параметры: В первом квадранте - КХт 0, KYT О

1) возможного попадания ПИ РГПВ О Зн ,ЗнА Ут-Г

зн дхт о,ЗиЛ YT-I

2) находящихся ПИ РГПВ 1 - все направления

Во втором квадранте - Кхт 1, KYT О ПГПВ 0

1) Возможного попадания Зн ЛХТ 10 Зн AYT 0

Зн ,Зн В третьем квадранте Кхт 1 Кут 1 РГПВ 0

1) Возможного попадания 3НХТ 1 3HYT 1

В четвертом квадранте - КХТ О KYT 1. РГПВ О

1) Возможного попадания Зн Зн

Зн АХТ 0 ЗнА

Вектора данной группы подлежат интерполяции. Вектора возможного попадания в ПИ интерполируются в невидимой зоне с целью фиксирования точки пересечения вектора с границей ПИ. В момент пересечения формируемого вектора с границей ПИ формируется сигнал разрешения подсвета (РП), который разрешает внешнему устройству отражать на экране дисплея интерполируемый вектор.

Поле индикации ограничивается осью +Y, +Х, а также верхней и правой границей действия сигнала РГПВ. Формируемый отрезок прямой, который выходит из ПИ, пересекая границу ПИ в любом месте, подлежит отсечению,

Рассмотрим работу интерполятора с учетом процедуры отсечения,

В исходном состоянии, устанавливаемом по сигналу начального сброса, поступающему по входу 13 интерполятора, триггеры 51 и 52 БУЗ устанавливаются в нулевое состояние, вследствие чего на выходе 24 БУЗ, а следовательно, на выходе 41 конца интерполяции устройства будет нулевой уровень, сигнализирующий о том, что интерполятор готов принять задание на отрезок прямой, Задание на отрезок прямой принимается по входной информационной шине 25

под воздействием синхроимпульсов на входах 16, 10, 11, 14, 15 интерполятора, Под воздействием импульса на входе 16 в регистр 6 признаков заносятся признаки Зн АХН, Зн A YH, Зн А , триггеры 46,47, БУЗ

и накапливающий сумматор устанавливаются в нулевое состояние, триггеры 57, 58 Б08 - в нулевое состояние. На входах 31 - 35 выставляются начальные параметры формируемого вектора: Рх, Ру, КХТ, KYT РГПВ, а

также с РГП6 направление приращений Зн Хн, Зн YH, вследствие чего на выходе 30 Б08 формируется определенное значение сигнала, Если на указанном выходе формируется нулевой уровень, что соответствует

процедуре отсечения, внешнему устройству сигнализируется, что задаваемый вектор относится к группе векторов неявного попадания в ПИ. На выходе 41 формируется нулевой уровень (конец интерполяции), т.е.

внешнему устройству необходимо спозиционировать, если это необходимо, конечную точку вектора и задать новые данные на работу.

Если на выходе 30 после задания начальных параметров вектора формируется высокий уровень, значит, задаваемый вектор относится к группе возможного попадания в ПИ или находящегося в ней. Такой вектор подлежит интерполированию. Алгоритм работы интерполятора продолжается в следующей последовательности.

На вход 10 интерполятора поступает сигнал положительной полярности, под воздействием которого в ВСч2 заносится боль- шее приращение БП. Под воздействием сигнала, поступающего на вход 11 интерполятора и проходящего через элемент 55 И БУЗ, в накапливающий сумматор 5 заносится половина большего приращения БП/2, которое поступает со входной шины 25 через Б04. Под воздействием сигнала, поступающего на вход 14 интерполятора (по нулевому значению этого сигнала), триггер 47 БУЗ устанавливается в единичное состо- яние, а по положительному перепаду этого сигнала осуществляется запись разности приращений в нулевую ячейку БОП4 и установка единичное состояние триггера 46 БУЗ, что приводит к изменению адреса ячейки БОП4 с нулевого на единичный. Под воздействием сигнала, поступающего на вход 15 интерполятора, в первую ячейку БОП4 заносится код меньшего приращения МП обр, а триггер 51 БУЗ устанавливается в единичное состояние. При этом, на D-вхо- де триггера 52 БУЗ появится единичный уровень и по первому же после этого положительному перепаду опорной импульсной последовательности f0 четвертый триггер 52 БУЗ устанавливается в единичное состояние. На этом прием задания на отрезок прямой закончен. По окончанию, действия активного значения сигнала на входе 15 интерполятора, что соответствует моменту ус- тановки в единичное состояние триггера 51 БУЗ, сигнал готовности на выходе 24 примет единичное состояние, что будет сигнализировать о том, что цикл интерполяции начат, но не закончен.

В цикле интерполяции с каждым тактом, определяемым опорной импульсной последовательностью fo, в накапливающем сумматоре 6 определяется очередное значение оценочной функции ОФ по формуле:

ОФн-1 ОФ| + А, при ОФ 0; ОФн-1 ОФ| + I МП I обр. +1, при ОФ 0 (1) Ввиду того что при вычислении оценочной функции слагаемые всегда имеют противоположные знаки, переполнение Р накапливающего сумматора 5 представляет собой обратное значение знака оценочной функции. Это переполнение фиксируется триггером 47 БУЗ, состояние которого определяет значение входа переноса 21 НСМ 5 и адресного входа 19 БОП4, что обеспечива- ет вычисление ОФ по выражениям (1). Кроме этого, в цикле интерполяции с каждым тактом содержимое ВСЧ2 уменьшается на

единицу, а блок выходной логики 9 формирует очередные единичные приращения +1х, -1х, +1у, -1у, а зависимости от знаков приращений координат Зн АХТ, Зн A YT, знака разности координат и переполнения НСМ 5.

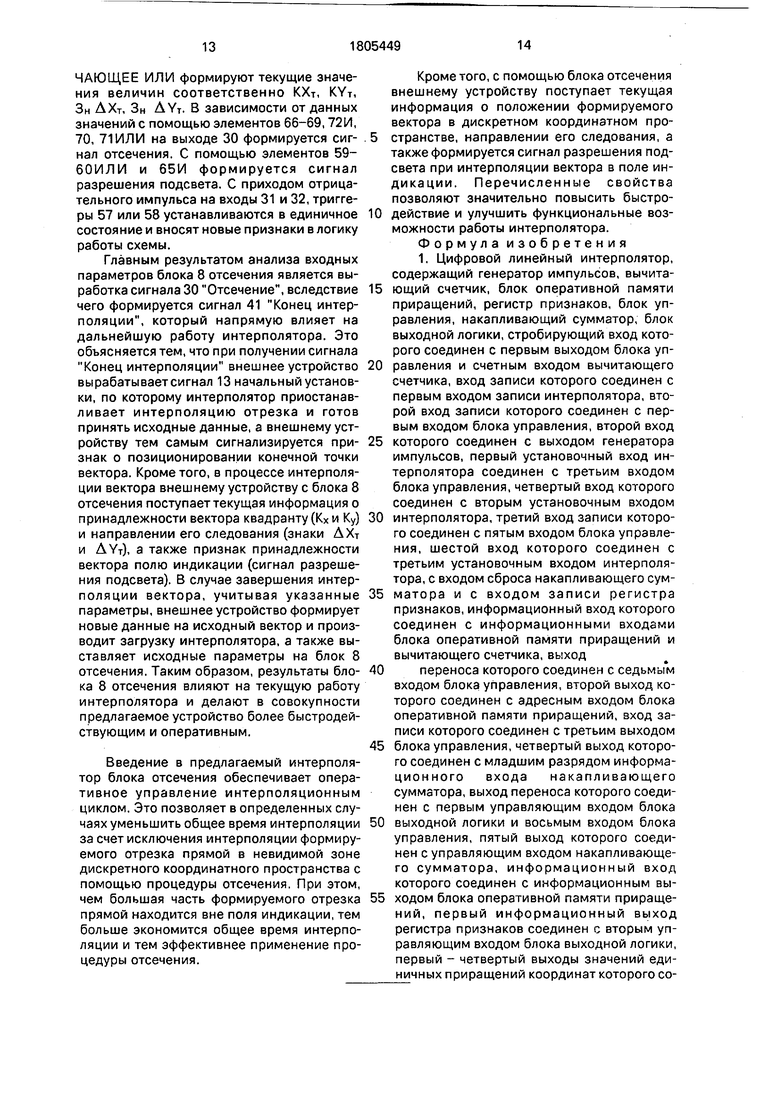

Эта зависимость приведена в таблице.

При достижении вычитающим счетчиком 2 нулевого состояния на выходе 17 формируется нулевой сигнал, который, проходя через элемент 49И БУЗ, сбрасывает триггеры 51 и 52 в нулевое состояние, что свидетельствует об окончании цикла интерполяции и формирования нулевого значения сигнала на выходе 24 БУЗ, следовательно, на выходе 41 интерполятора. Следует отметить, что если на выходе 41 появляется активный (нулевой) уровень сигнала конца интерполяции, а на выходе 30 устройства единичный уровень сигнала конца интерполяции, то интерполяция формируемого отрезка прямой произведена полностью (от начальной и до конечной точки). Если же на выходе 41 нулевой уровень и на выходе 30 также нулевой уровень, это значит, что сигнал конец интерполяции дан с учетом процедуры вычисления. Следовательно, внешнему устройству сигнализируется, что в данном случае необходимо спозиционировать конечную точку формируемого отрезка прямой.

Также внешнему устройству в процессе работы интерполятора на выходах 37,38,39, 40 Б08 выдается текущая информация о том, в каком квадранте находится вектор (КХТ и KY-г), а также направление его следования (Зн АХТ и Зн A YT).

Рассматриваемое устройство за исключением блока 8 отсечения, элемента 71/1 и некоторых связей, повторяет структуру устройства прототипа. Также функциональная работа данного устройства в цикле интерполяции повторяет алгоритм работы устройства-прототипа.

Блок 8 отсечения работает следующим образом. Во время установки и загрузки интерполятора на блок 8 отсечения поступают следующие данные. Сигналом на входе 16 триггеры 57 и 58, служащие для фиксирования переноса координатных счетчиков Рх и Ру, устанавливаются в нулевое состояние. Затем на информационные входы 27,28, 33, 34, 35 подаются начальные значения КХН и KYH, Зн АХН, ЗнАУн РГПВ. Следовательно, на выходах 30 отсечения, 36 - разрешения подсвета, 37 - КХТ, 38 - KYT, 39 - Зн АХТ, 40 - Зн AYT выставляются определенные значения, в зависимости от логики работы блока 8, Причем элементы 61 - 64 ИСКЛЮЧАЮЩЕЕ ИЛИ формируют текущие значения величин соответственно КХТ, KYT, Зн АХТ, Зн AYT. В зависимости отданных значений с помощью элементов 66-69,72И, 70, 71 ИЛИ на выходе 30 формируется сигнал отсечения. С помощью элементов 59- 60ИЛИ и 65И формируется сигнал разрешения подсвета. С приходом отрицательного импульса на входы 31 и 32, триггеры 57 или 58 устанавливаются в единичное состояние и вносят новые признаки в логику работы схемы.

Главным результатом анализа входных параметров блока 8 отсечения является выработка сигнала 30 Отсечение, вследствие чего формируется сигнал 41 Конец интерполяции, который напрямую влияет на дальнейшую работу интерполятора. Это объясняется тем, что при получении сигнала Конец интерполяции внешнее устройство вырабатывает сигнал 13 начальный установки, по которому интерполятор приостанавливает интерполяцию отрезка и готов принять исходные данные, а внешнему устройству тем самым сигнализируется признак о позиционировании конечной точки вектора. Кроме того, в процессе интерполяции вектора внешнему устройству с блока 8 отсечения поступает текущая информация о принадлежности вектора квадранту (Кх и Ку) и направлении его следования (знаки ДХТ и AYT), а также признак принадлежности вектора полю индикации (сигнал разрешения подсвета). В случае завершения интерполяции вектора, учитывая указанные параметры, внешнее устройство формирует новые данные на исходный вектор и производит загрузку интерполятора, а также выставляет исходные параметры на блок 8 отсечения. Таким образом, результаты блока 8 отсечения влияют на текущую работу интерполятора и делают в совокупности предлагаемое устройство более быстродействующим и оперативным.

Введение в предлагаемый интерполятор блока отсечения обеспечивает оперативное управление интерполяционным циклом. Это позволяет в определенных случаях уменьшить общее время интерполяции за счет исключения интерполяции формируемого отрезка прямой в невидимой зоне дискретного координатного пространства с помощью процедуры отсечения. При этом, чем большая часть формируемого отрезка прямой находится вне поля индикации, тем больше экономится общее время интерполяции и тем эффективнее применение процедуры отсечения.

Кроме того, с помощью блока отсечения внешнему устройству поступает текущая информация о положении формируемого вектора в дискретном координатном про5 странстве, направлении его следования, а также формируется сигнал разрешения подсвета при интерполяции вектора в поле индикации. Перечисленные свойства позволяют значительно повысить быстро0 действие и улучшить функциональные возможности работы интерполятора. Ф о р м у л а и з о б р е т е н и я 1. Цифровой линейный интерполятор, содержащий генератор импульсов, вычита5 ющий счетчик, блок оперативной памяти приращений, регистр признаков, блок управления, накапливающий сумматор, блок выходной логики, стробирующий вход которого соединен с первым выходом блока уп0 равления и счетным входом вычитающего счетчика, вход записи которого соединен с первым входом записи интерполятора, второй вход записи которого соединен с первым входом блока управления, второй вход

5 которого соединен с выходом генератора импульсов, первый установочный вход интерполятора соединен с третьим входом блока управления, четвертый вход которого соединен с вторым установочным входом

0 интерполятора, третий вход записи которого соединен с пятым входом блока управления, шестой вход которого соединен с третьим установочным входом интерполятора, с входом сброса накапливающего сум5 матора и с входом записи регистра признаков, информационный вход которого соединен с информационными входами блока оперативной памяти приращений и вычитающего счетчика, выход

0 переноса которого соединен с седьмым входом блока управления, второй выход которого соединен с адресным входом блока оперативной памяти приращений, вход записи которого соединен с третьим выходом

5 блока управления, четвертый выход которого соединен с младшим разрядом информа- ционного входа накапливающего сумматора, выход переноса которого соединен с первым управляющим входом блока

0 выходной логики и восьмым входом блока управления, пятый выход которого соединен с управляющим входом накапливающего сумматора, информационный вход которого соединен с информационным вы5 ходом блока оперативной памяти приращений, первый информационный выход регистра признаков соединен с вторым управляющим входом блока выходной логики, первый - четвертый выходы значений единичных приращений координат которого соответственно соединены с первым - четвертым выходами управления интерполятора, отличающийся тем, что, с целью расширения области применения и повышения быстродействия, в него введены блок отсечения и элемент И, первый вход которого соединен с шестым выходом блока управления, а второй вход - с управляющим выходом интерполятора и выходом отсечения блока отсечения, первый вход знака начального приращения которого соединен с вторым информационным выходом регистра, третий информационный выход которого соединен с вторым входом знака начального приращения блока отсечения, первый управляющий вход которого соединен с выходом переноса координатного счетчика по оси X устройства, выход переноса координатного счетчика по оси Y которого соединен с вторым управляющим входом блока отсечения, вход начальной установки которого соединен с третьим установочным входом интерполятора, первый и второй входы определения начального квадранта которого соединен соответственно с третьим и четвертым управляющими входами блока отсечения, пятый управляющий вход которого соединен с входом регистрации границы видеопамяти интерполятора, выход разрешения подсвета которого соединен с первым управляющим выходом блока отсечения, второй и третий выходы которого соединены соответственно с первым и вторым выходами знака текущих координатных приращений интерполятора, а также с третьим и четвертым управляющими входами блока выходной логики, выход элемента И соединен с выходом конца интерполяции интерполятора, первый и второй выходы текущего квадранта соединены соответственно с четвертым и пятым управляющим выходом блока отсечения.

2. Интерполятор по п. 1, о т л и ч а ю щ- и и с я тем, что блок отсечения содержит первый и второй RS-триггеры, первый - четвертый элементы ИЛИ, первый - четвертый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый - шестой элементы И, S-вход первого RS- триггера соединен с первым управляющим входом блока, вход начальной установки которого соединен с R-входами первого и второго RS-триггеров, S-вход второго RS-триггера соединен с вторым управляющим входом блока, третий управляющий вход которого соединен с первым входом

первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым инверсным входом первого элемента ИЛИ, четвертый управляющий вход блока отсечения соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым инверсным входом второго элемента ИЛИ, первый вход знака начального приращения блока отсечения соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а второй вход-с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с третьим выходом блока отсечения, и первыми инверсными входами третьего и первого элементов И и первым входом третьего элемента ИЛИ, второй вход которого соединен с четвертым управляющим выходом блока, вторым входом первого элемента И, выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,

первым входом второго элемента И, вторым инверсным входом третьего элемента И и первым входом четвертого элемента И, второй инверсный вход которого соединен с пятым управляющим выходом блока отсечения, третьим входом третьего И, и вторым входом второго элементов И, выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третьими входами первого элемента И и третьего элемента ИЛИ, четвертый вход которого соединен с пятым управляющим входом блока отсечения и первым входом пятого элемента И, выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с третьими инверсными входами второго и четвертого элементов И и вторым выходом блока, первый управляющий выход которого соединен с выходом пятого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, а первый вход пятого элемента И - с выходом первого элемента ИЛИ, второй вход которого соединен с выходом RS-триггера, вторыми входами первого и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго RSтриггера соединен с вторыми входами второго элемента ИЛИ, второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы пер- вого-четвертого элементов И, соединены

соответственно с первым - четвертым входами четвертого элемента ИЛИ, инверсный выход которого соединен с первым входом шестого элемента И, второй вход которого соединен с выходом третьего элемента

ИЛИ, выход шестого элемента И - с выходом отсечения блока.

8L

Li

JL

ШГГ

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Линейно-круговой интерполятор | 1985 |

|

SU1259218A1 |

| Многокоординатный линейно-круговой интерполятор | 1984 |

|

SU1156008A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Линейный интерполятор | 1986 |

|

SU1423984A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1709269A1 |

| Линейно-круговой интерполятор | 1974 |

|

SU500518A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - расширение области применения интерполятора за счет формирования векторов во всех квадрантах, а также повышение его быстродействия за счет останова интерполяции при реализации отсечения. Интерполятор содержит генератор импульсов, вычитающий счетчик, блок управления, блок оперативной приращений памяти, накапливающий сумматор 5, регистр признаков, элемент И, блок отсечения, блок выходной логики. При переходе аппроксимируемого вектора через координатные оси в квадранты, соседние первому, блоком отсечения осуществляется формирование сиг- нала отсечения. При формировании векторов, начальная точка которых находится в невидимой зоне, при переходе через координатные оси, в блоке логики изменяется направление счета координатных счетчиков. В блоке отсечения осуществляется также анализ целесообразности пошагового формирования векторов. Если вектор не попадает в видимую зону, то формируется соответствующий сигнал только на установку координатных счетчиков. 1 з.п. ф-лы, 7 ил., 1 табл. ё

Риг.З

- вектора явного непопадания в Ш

- вектора находящиеся или возможного попадания в Ш Риг. 4

18

33

75

29 23

ОТ 77

78

73

S

3

W

82

44

Jj

Фиг 5

Шиг.6

| Авторское свидетельство СССР |

Авторы

Даты

1993-03-30—Публикация

1990-05-08—Подача