|;

СО

со

Сл

со ю

Изобрететсе относится к автоматике и вычислитепьной технике и может быть использовано в устройствах программного управления cтaнкa И и графических устройствах ввода-вывода щ фровых вычислительных машин. Цель изобретения - повышение .быстродействия и точности интерполятора,

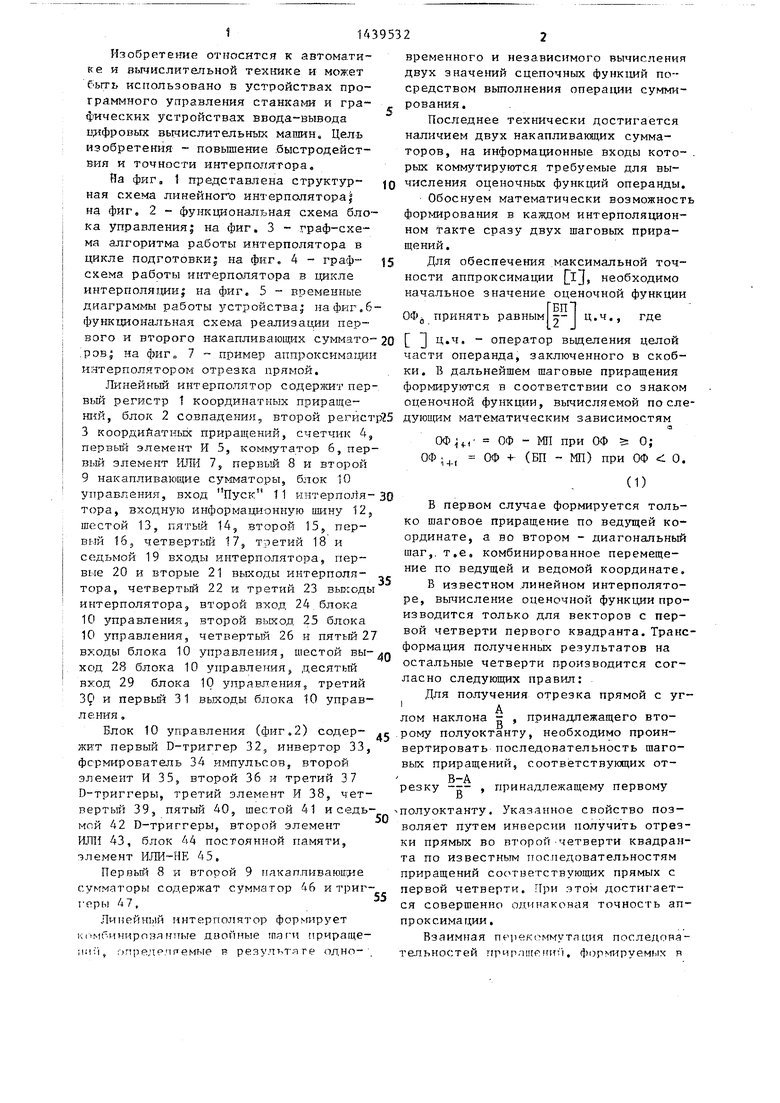

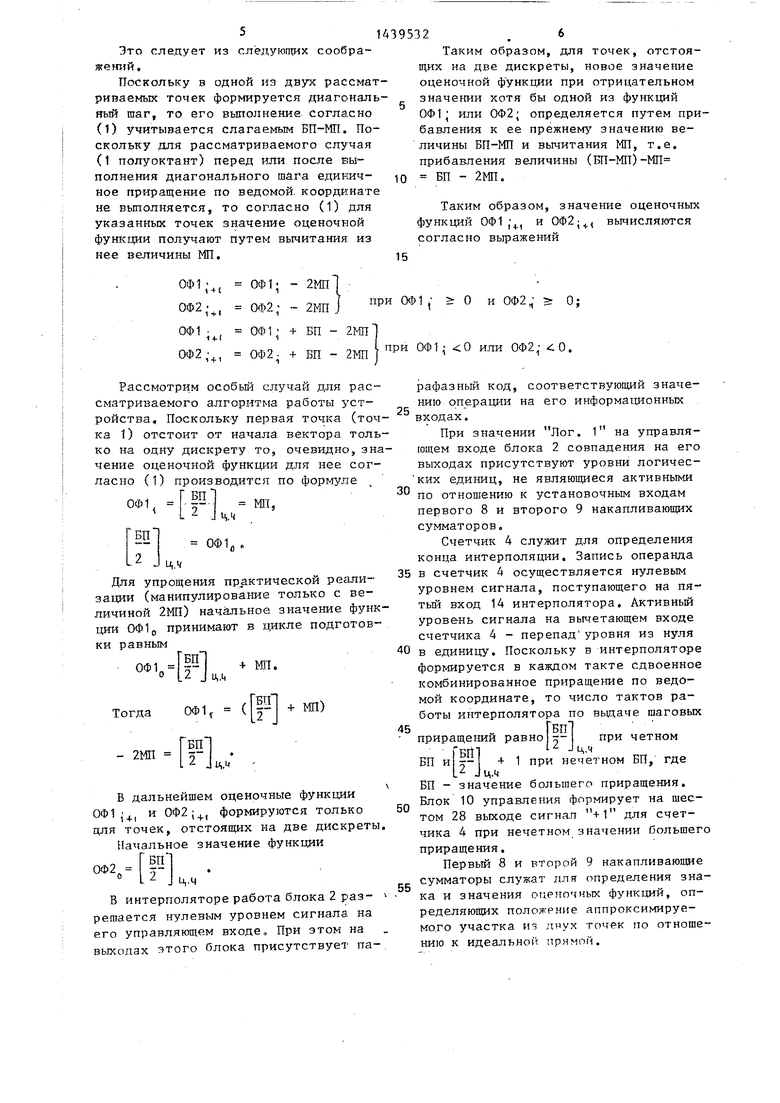

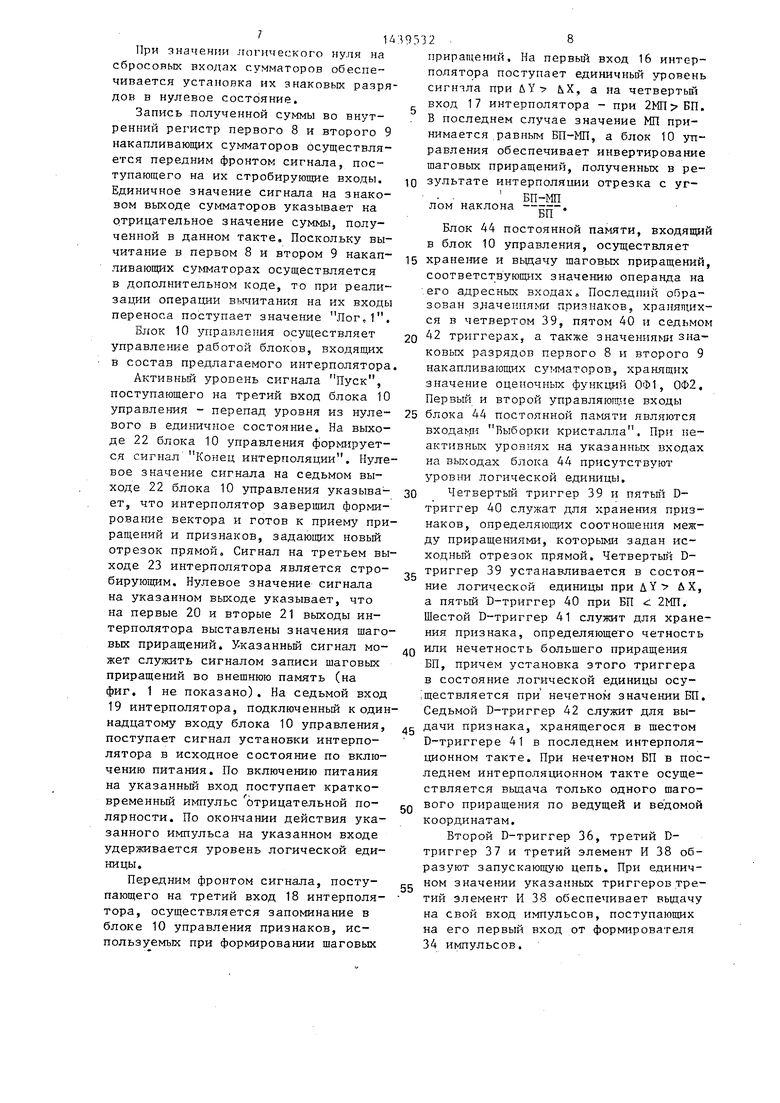

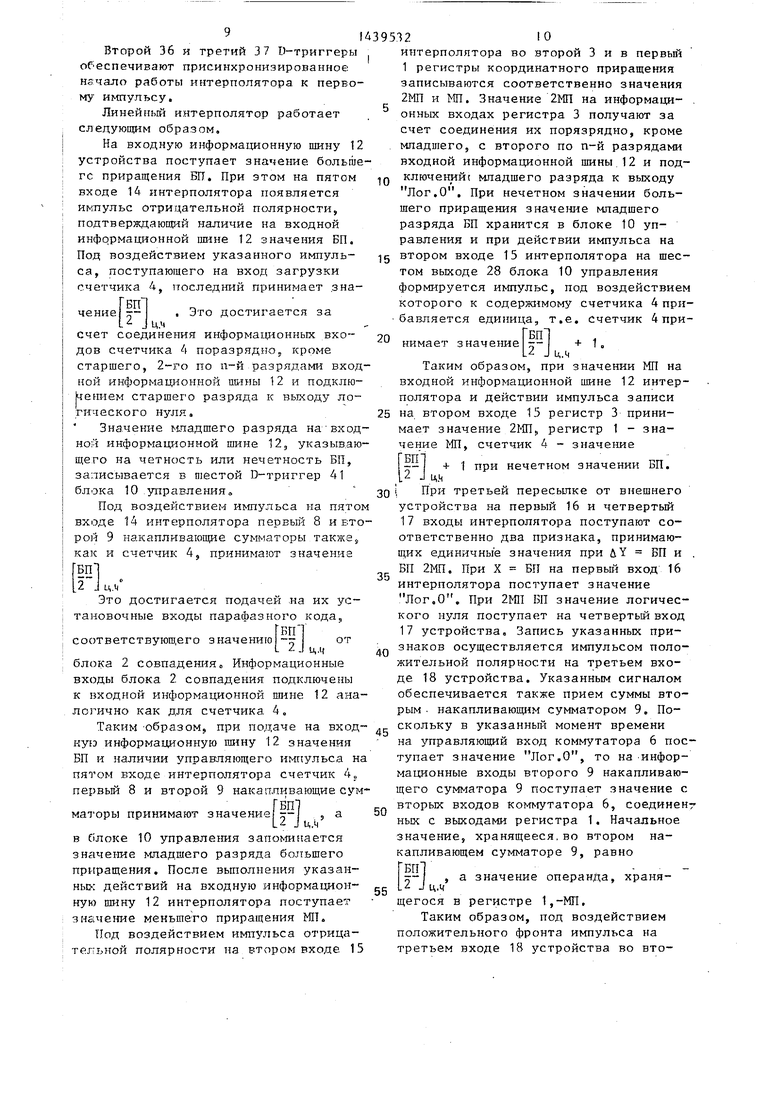

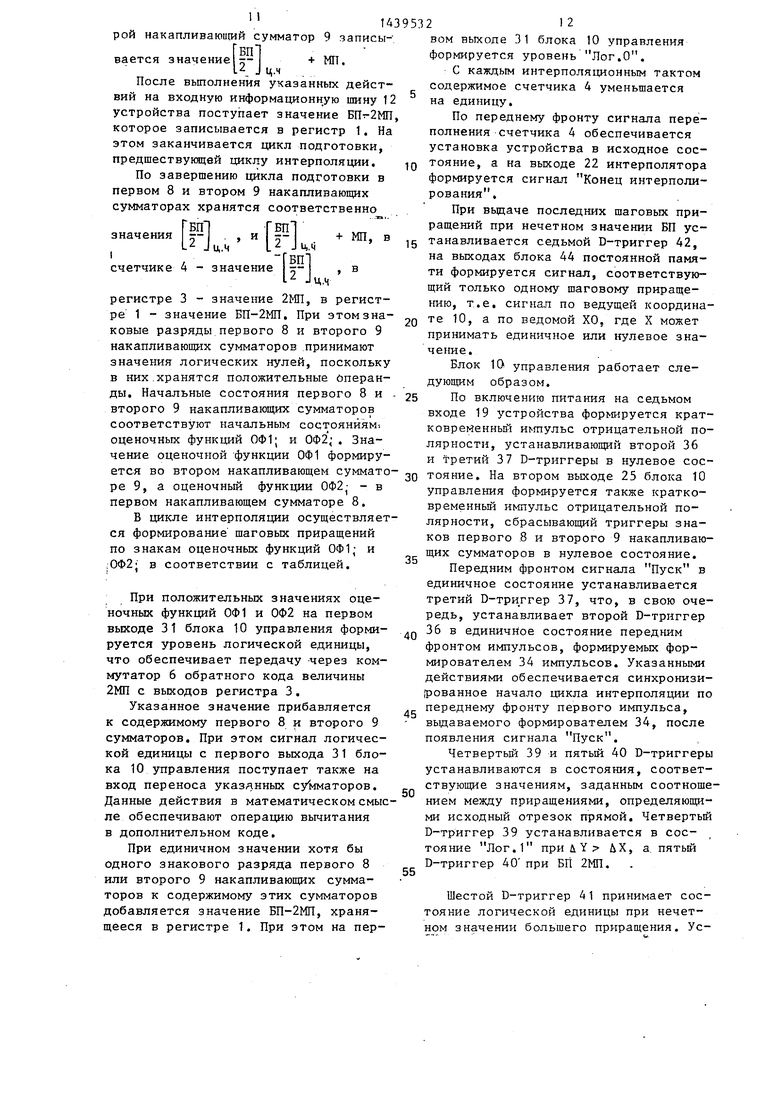

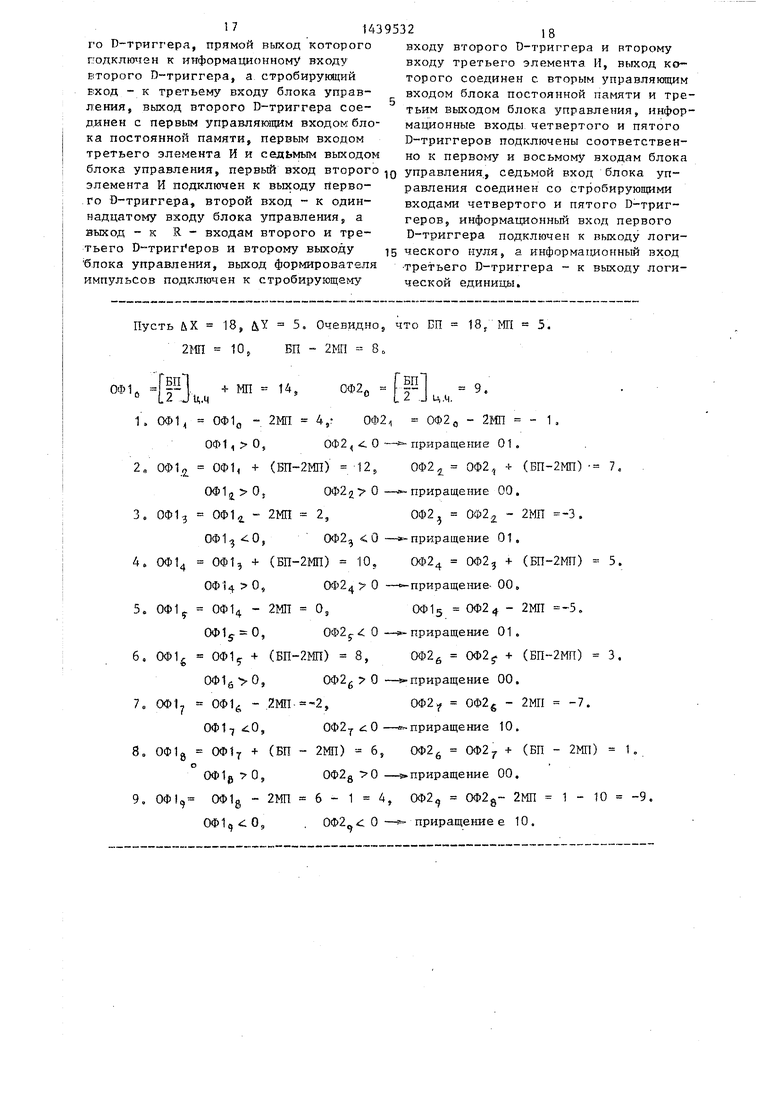

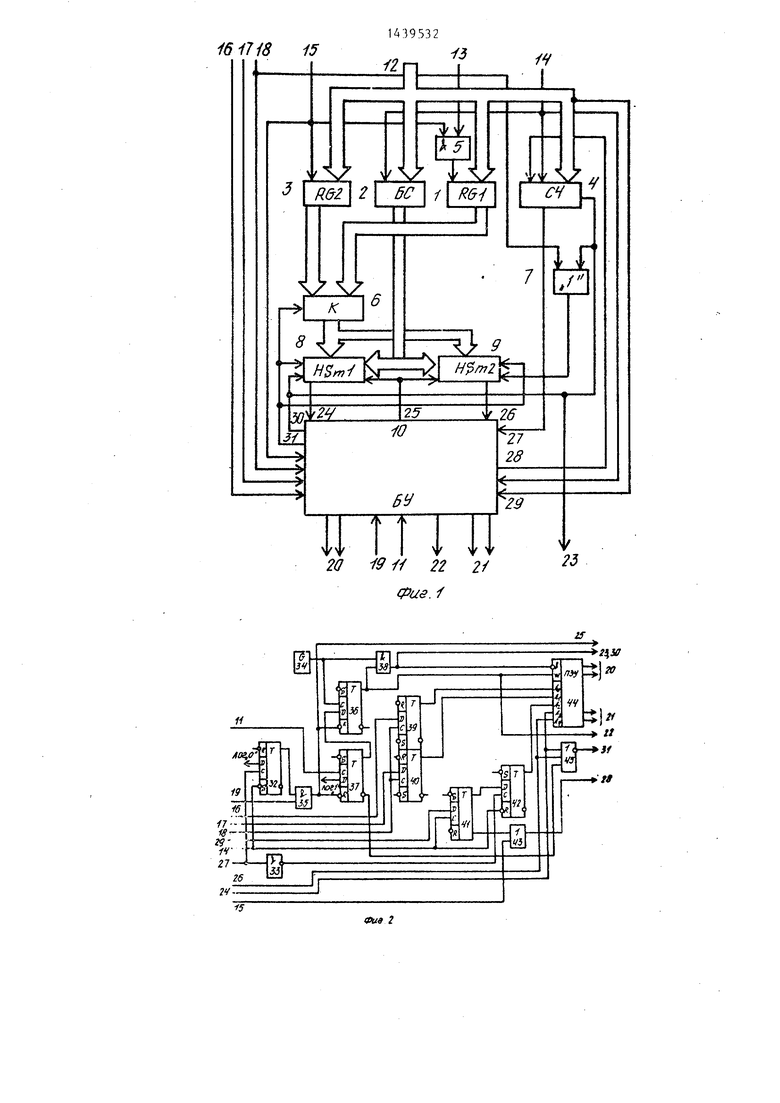

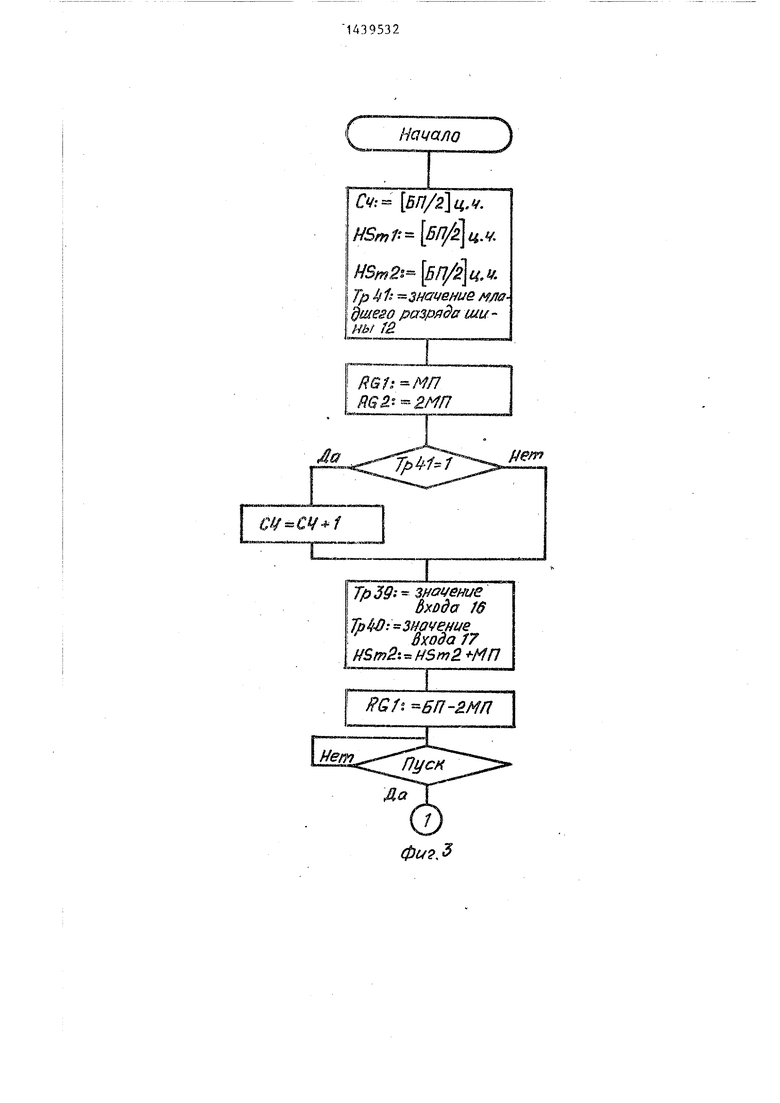

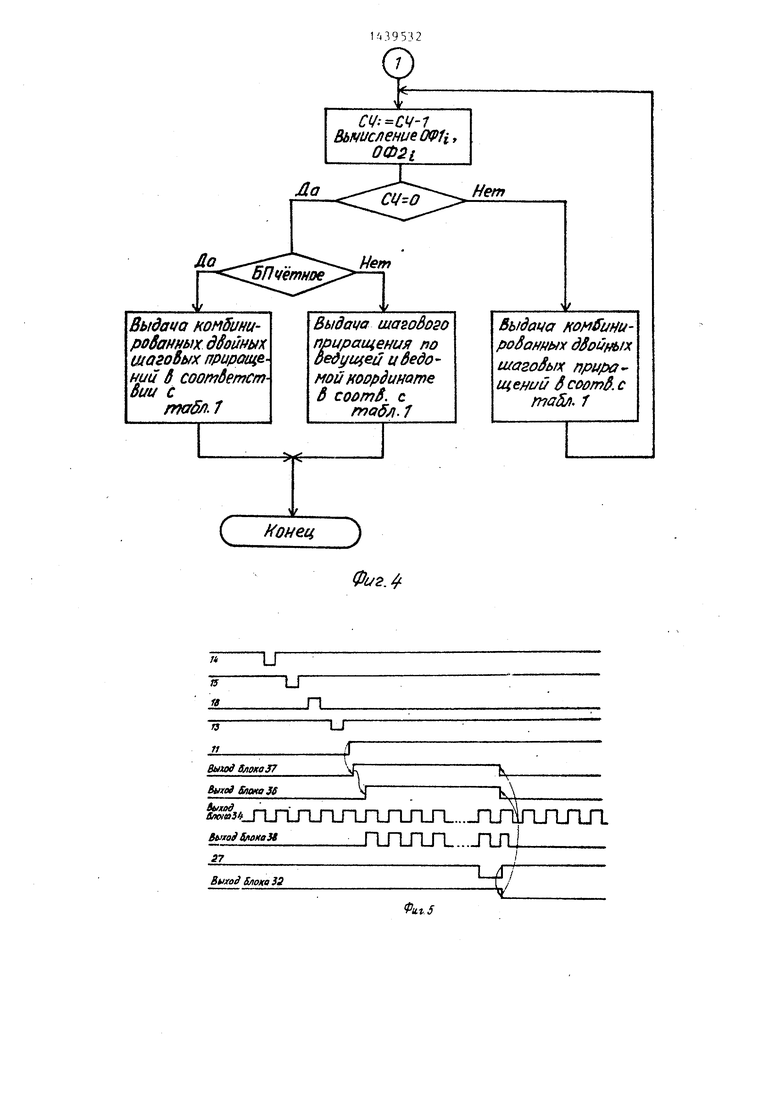

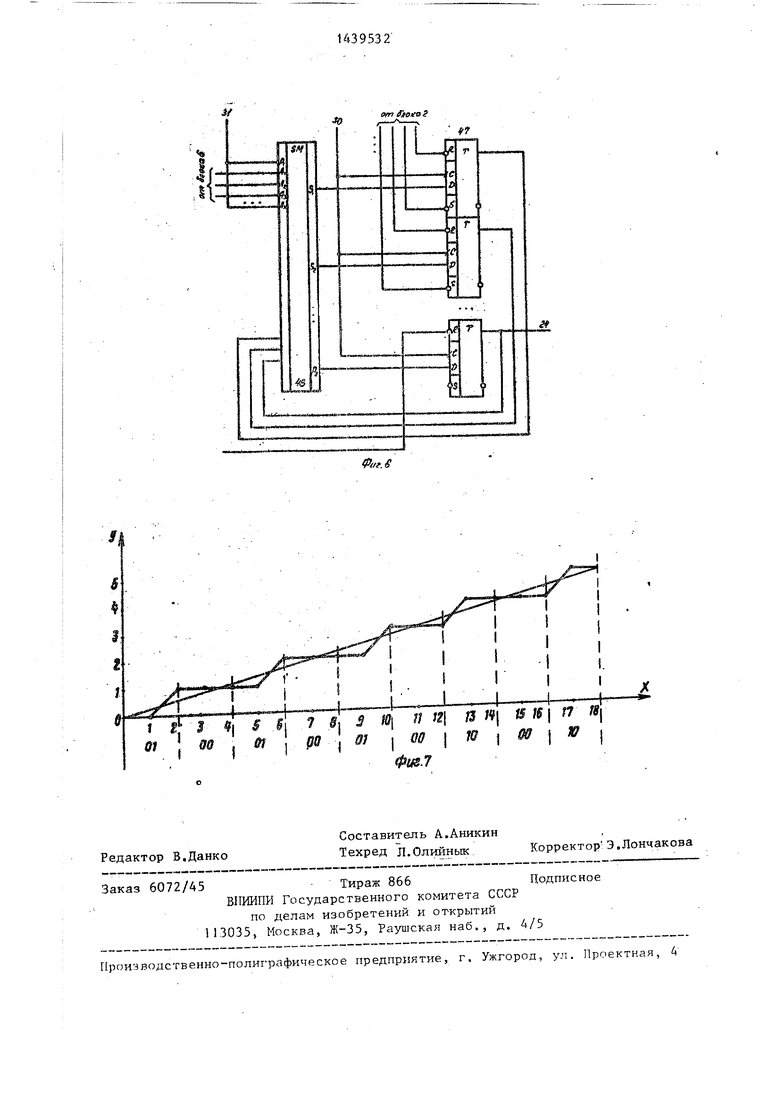

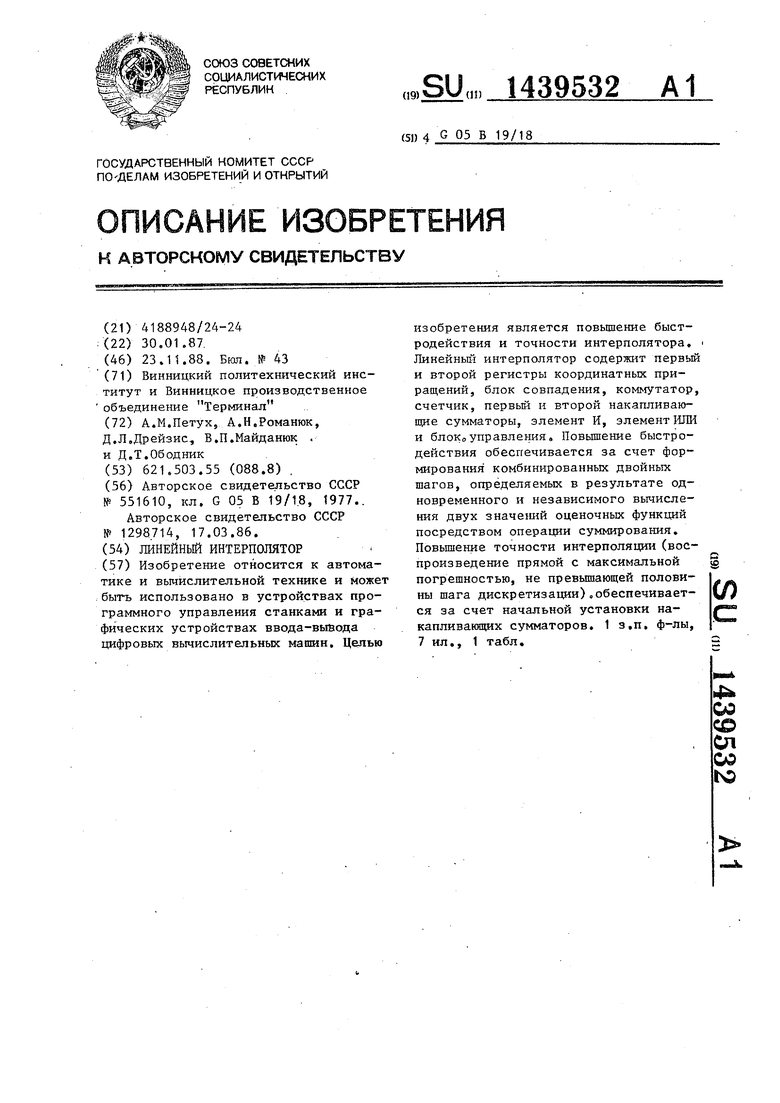

Йа фиг, I представлена структурная схема липеккото интерполятораj на фиг, 2 - функциональная схема блока управленияI на фиг. 3 - граф-схема алгоритма работы интерполятора в цикле подготовки| на фиг, 4 - граф- схема работы интерполятора в цикле интерполяции| на фиг, 5 - временные диаграммы работы устройства на фиг,6 функциональная схема реализации первого и второго накапливающих суммато- .ров, на фнг„ 7 пример аппроксимаг ии интерполятором отрезка прямой.

Линейный интерполятор содержит пер- вьм регистр 1 координатных прираще- ни:й, блок 2 совпадения, второй регист 3 коордийатных приращений, счетчик 4, первый элемент И 5, KOMNiyTaTop б, первый элемент ИЛИ 7, первът 8 и второй

9накапливающие сумматоры, блок 10 управления, вход Пуск 11 интерполя- тора, входную информационную шину 12, шестой 13, пятьй 14, .второй 15, первый 16, четвертьй 17, третий 18 и седьмой 19 входы интерполятора, первые 20 и вторые 21 выходы интерполятора, четвертьй 22 и третий 23 вькоды интерполятора, второй вход 24,блока

10управления, второй выход 25 блока 10 управления, четвертьш 26 и пятьй 27 входы блока 10 управления, шестой выход 28 блока 10 управления, десятьш вход 29 блока 10 управления, третий

Зр и первьй 31 выходы блока 10 управления ,

Блок 10 управления (фиг,2) содер- жит первый D-триггер 32, инвертор 33, формирователь 34 импульсов, второй элемент И 35, второй 36 и третий 37 D-триггеры, третий элемент И 38, чет

вертьй 39, пятый 40, шестой 41 и седьмой 42 D-триггеры, второй элемент ИЛИ 43, блок 44 постоянной памяти, элемент И-ПИ-НЕ 45,

Первый 8 и второй 9 накап.пиваюггдне сумматоры содержат сумматор 46 и триг т еры 47,

Линейный интерполятор формир ет К1 мбинирп;зянгтые двойные шаги рираа(е- ||цГ|, DnpejiPJifeMbie в результяге одно- .

10

15

20

5

0

д

с

5

0

5

ГБП1

rj

временного и независимого вычисления двух значений сцепочных функхшй посредством выполнения операоди суммирования.

Последнее технически достигается наличием двух накапливакщих сумматоров, на информационные входы кото- . рых коммутируются требуемые для вычисления оценочных функций операнды.

Обоснуем математически возможность формирования в каждом интерполяционном такте сразу двух шаговых приращений.

Для обеспечения максимальной точности аппроксимации pj, необходимо начальное значение оценочной функции

ОФ, принять равны ц.ч, - оператор выделения целой части операнда, заключенного в скобки. В дальнейшем шаговые приращения формируются в соответствии со знаком оценочной функции, вычисляемой последующим математическим зависимостям

а

ОФ.( ОФ - МП при ОФ : О;

ОФ;ц, ОФ + (БП - МП) при ОФ : 0.

(1)

В первом случае формируется только шаговое приращение по координате, а во втором - диагональный шаг,, т.е. комбинированное перемещение по ведущей и ведомой координате,

В известном .линейном интерполяторе, вычисление оценочной функции производится только для векторов с первой четверти первого квадранта. Трансформация полученных результатов на остальные четверти производится согласно следуюш;их правил:

Для получения отрезка прямой с уг- Iд

лом наклона - , принадлежащего второму полуоктанту, необходимо проин- вертировать последовательность шаговых приращений, соответствукщих от/in Д

резку --- , принадлежащему первому

D

полуоктанту. Указанное свойство позволяет путем инверсии получить отрезки прямых во второй-четверти квадранта по известным пос.педовательностям приращений соответствующих прямых с первой четверти. При этом достигается совершенно одинаковая точность аппроксимации.

Взаимная п п екоммутлцт1я последовательностей прчр. нцрfiHf i. ф|5рмируем 1х в

первой половине квадранта с координаты X на Y и с Y на X, обеспечивает :симметричное воспроизведение прямой во второй половине квадранта относительно биссектрисы угла по заданному отрезку в первой половине квадранта.

Координатные шаги формируются с учетом знаков исходньк приращений, определяющих все выкладки, производи только отрезками прямых с первого полуоктанта ( , БП 5:2МП).

В интерполяторе 13 каждом такте синхронно формируются две независимые оценочные функции ОФ1, и , причем оценочная функция ОФ1; служит для определения шаговых приращений по ведомой координате в точках, соответствующих нечетным значениям абсцисс формируемого вектора, а оценоч- ная функция ОФ2у -,четным, если начало формируемого вектора можно условно соотнести с началом координат.

Так,- например, при БП 17 оценочная функция ОФ1; определяет шаговые приращения в точках 1,3,5,7,9,11,13, 15,17, а оценочная функция ОФ2;- в точках 2,4,6,8,10,12,14,16.

.Шаговые приращения по ведущей ко

0

0

теризуется преобладанием нулей. Сочетание шагов 11 невозможно.

Действительно,из(1) следует, что при ВП 2МП и отрицательном значении оценочной функции ОФ ; значение ОФ,, всегда больше нуля, поскольку к отрицательному значению ОФ (ОФ( МП) добавляется значение БП-МП МП, т.е. после вьтолнения диагонального шага обязательно, Следует перемещение, характеризуемое большей проекцией. В линейном интерполяторе оценочные функции ОФ1 и ОФ2 вычисляются для

5 точек, отстоящих одна от другой на две дискреты.

Позтому при положительном значении оценочной функции ОФ1, {ОФ2 ) при вычислении значе1Тия ОФ1 J.; (W2,-4., ) из значения ОФ1 (ОФ2 ) вычитается значение 2МП,

При положительном значешп функций ОФ1; и ОФ2; по ведомой координате шаговые приращения не формиру5 ются, т.е. равны 00, Это следует из того,..что aппpoкcимиpye aя прямая находится ниже идеальной и отстоит от нее на расстоянии, меньшем половины шага дискретизации (оценочная

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1462247A1 |

| Цифровой линейный интерполятор с оценочной функцией | 1981 |

|

SU991375A1 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| Линейный интерполятор | 1986 |

|

SU1423984A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Линейный интерполятор | 1985 |

|

SU1272310A1 |

| Цифровой линейный интерполятор | 1990 |

|

SU1805449A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

Изобретение относится к автоматике и вьшислительной технике и может : быт-ь использовано в устройствах программного управления станками и графических устройствах ввода-вьшода цифровых вычислительных машин. Целью изобретения является повьшение быстродействия и точности интерполятора. Линейньш интерполятор содержит первьй и второй регистры координатных приращений, блок совпадения, коммутатор, счетчик, первый и второй накапливающие сумматоры, элемент И, элемент ЮТ и блокоуправления в Повышение быстродействия обеспечивается за счет формирования комбинированных двойных шагов, определяемых в результате одновременного и независимого вычисления двух значешш оценочных функций посредством операции суммирования. Повышение точности интерполяции (воспроизведение прямой с максимальной погрешностью, не превышающей половины шага дискретизации).обеспечивается за счет начальной установки на- капливанищх сумматоров. 1 з.п, ф-лы, 7 ил., 1 табл. i (Л

ординате фop шpyютcя в каждом интер- зо ФУНКЦИЯ определяет расстояние апполяционном такте, а по ведомой - в соответствии с значениями оценочных функций 6Ф1 и ОФ2.

В линейном интерполяторе начальные значения оценочных функций ОФ1

и ОФ2 принимают равными г- .

L2j4.t,.

Это позволяет симметрировать погрешность аппроксимации и достичь максимальной точности аппроксимации, равной половине шага дискретизации.

Для отрезков прямых (известньй интерполятор), принадлежащих первой четверти первого квадранта, возможны следующие сочетания шагов по ведомой координате: 01,10,00, гДе 1 - наличие перемещения, О - отсутствие перемещения. Это следует из того, что посколь35

проксимируемой прямой от идеальной прямой). При отрицательном значе1ши хотя бы одной из функций ОФ1|- или ,ОФ2; в одной из двух рассматриваемых точках формируется единичное переме- )Щение по ведомой координате, т.е. пе ремещения 01 или 10.

Очевидно, что если , а ОФ2; 0, то формируется шаговое пере ,,. .йещение 01. Если же ОФ1 , сО и ОФ2,то формируется перемещение 10. В зтом случае на единичное перемещение указывает отрицательный знак функции

ОФ1:

формируемой для первой из двух

45

рассматриваемых точек, а отрицатель- ньй знак функции ОФ2 указьшает толь ко на то, что в одной из рассматрива емых точках имеет место единичное

ГБП - МПТ :перемещение, поскольку для рассмат- ку БП 2МП, то отношение| --;- --J, р ваемого случая (первьй полуоктант

определяющее число тактовых мЬм ентов времени, когда шаговые приращения по ведомой координате не формируются, к числу тактовых моментов времени, когда шаговые приращения по ведомой координате имеют место, больше или равно 1. Таким образом, последовательность приращений по ведомой координате для рассматриваемого случая харак50

55

первого квадранта и максимальной точ ности аппроксимации) перемещение 11 не имеет смысла.

При отрицательном значении хотя бы одной из оценочных функций ОФ1; или ОФ2; их новое значение определяется по формуле

ОФ1 ОФ2

1+ Ui

ОФ1 + БП - 2Ш; ОФ2; + БП - 2МП.

35

проксимируемой прямой от идеальной прямой). При отрицательном значе1ши хотя бы одной из функций ОФ1|- или ,ОФ2; в одной из двух рассматриваемых точках формируется единичное переме- )Щение по ведомой координате, т.е. перемещения 01 или 10.

Очевидно, что если , а ОФ2; 0, то формируется шаговое пере- ,,. .йещение 01. Если же ОФ1 , сО и ОФ2,, то формируется перемещение 10. В зтом случае на единичное перемещение указывает отрицательный знак функции

ОФ1:

формируемой для первой из двух

45

рассматриваемых точек, а отрицатель- ньй знак функции ОФ2 указьшает только на то, что в одной из рассматриваемых точках имеет место единичное

:перемещение, поскольку для рассмат- р ваемого случая (первьй полуоктант

первого квадранта и максимальной точности аппроксимации) перемещение 11 не имеет смысла.

При отрицательном значении хотя бы одной из оценочных функций ОФ1; или ОФ2; их новое значение определяется по формуле

ОФ1 ОФ2

1+ Ui

ОФ1 + БП - 2Ш; ОФ2; + БП - 2МП.

Это следует из следуюпщх сообра- жеттй.

Поскольку в одной из двух рассмат- pMBaehfbK точек формируется диагональный таг, то его выполнение согласно (1) учитывается слагаемым БП-МП, Поскольку для рассматриваемого случая (1 полуоктант) перед или после выполнения диагонального шага единичное приращение по ведомой, координате не вьшолняется, то согласно (1) для указанных точек значе -ше оценочной функции получают путем вычитания: из нее величины МП.

ОФ1;- 2Мп1 ОФ2,-.- 2Мп Р ОФ1,- О и ОФ2,- 0;

ОФ1--I- БП - 2МП

ОФ2.+ БП - 2Ш Р ™ °

Рассмотрим особый случай для рассматриваемого алгоритма работы устройства. Поскольку первая точка (точка 1) отстоит от начала вектора только на одну дискрету то, очевидно, значение оценочной функции для нее согласно (1) производится по

-.Fir

5Е1 .оФ1..

МП,

- J Ц.4

Для упрощения практической регши- зации (манипулирование только с величиной 2МП) начальное значение функции ОФ1д принимают в цикле подготовки равным

ОФ1

2 JM

f МП.

ОФ1,

. (р-в|3

+ МП)

- 2МП

БП1

rju..;

В дальнейшем оценочные функции ОФ1 , и ОФ2;, формируются только для точек, отстоящих на две дискреты.

Начальное значение функции

ОФ2, . L2 ц,ч

в интерполяторе работа блока 2 разрешается нулевым уровнем сигнала на его управляющем входе. При этом на выходах этого блока присутствует па

Таким образом, для точек, отстоящих на две дискреты, новое значение оценочной функции при отрицательном значении хотя бы одной из функций ОФ1 или ОФ2; определяется путем прибавления к ее прежнему значению величины БП-МП и вычитания МП, т.е. прибавления величины (Ш-МП)-МП БП - 2МП.

Таким образом, значение оценочных

функций ОФ1

и ОФ2;.( вычисляются

-| +

согласно вьфажении

15

5

0

5

0

рафазньм код, соответствующий значению операции на его информационных входах.

При значении Лог. 1 на управляющем входе блока 2 совпадения на его выходах присутствуют уровни логичес- ких еди1шц, не являющиеся активными по отношению к установочным входам первого 8 и второго 9 накапливающих сумматоров.

Счетчик 4 служит для определения конца интерполяции. Запись операнда в счетчик 4 осуществляется нулевым уровнем сигнала, поступающего на пятый вход 14 интерполятора. Активный уровень сигнала на вычетающем входе счетчика 4 - перепад уровня из нуля в единицу. Поскольку в интерполяторе формируется в каждом такте сдвоенное комбинированное приращение по ведомой координате, то число тактов работы интерполятора по выдаче шаговых

5

приращений равно БГ1

БП и

2 j

ГБП

г- при четном

I J Ц.Ч

1 при нечетном БП, где

ц.ч

0

5

БП - значение большего приращения. Блок 10 управления формирует на шестом 28 выходе сигнап +1 для счетчика 4 при нечетном значении большего приращения.

Первый 8 и второй 9 накапливающие сумматоры служат для определения знака и значения оценочных функций, определяющих положение аппроксимируемого участка из лт ух точек по отношению к идеальной прямой.

1А

При значении логического нуля на сбросовых входах сумматоров обеспечивается установка их знаковьк разрядов в нулевое состояние.

Запись полученной суммы во внут- ранний регистр первого 8 и второго 9 накапливающих сумматоров осуществляется передним фронтом сигнала, поступающего на их стробирующие входы. Единичное значение сигнала на знаковом выходе сумматоров указывает на отрицательное значение суммы, полученной в данном такте. Поскольку вычитание в первом 8 и втором 9 накап- ливающих сумматорах осуществляется в дополнительном коде, то при реализации операции вычитания на их входы переноса поступает значение Лог,1.

Блок 10 управления осуществляет управление работой блоков, входящих в состав предлагаемого интерполятора

Активньй уровень сигнала Пуск, поступающего на третий вход блока 10 управления - перепад уровня из нуле- вого в единичное состояние. На выходе 22 блока 10 управления формируется сигнал Конец интерполяции, Нуяе вое значение сигнала на седьмом выходе 22 блока 10 управления указыва- ет, что интерполятор завершил формирование вектора и готов к приему приращений и признаков, задающих новьй отрезок прямой. Сигнал на третьем выходе 23 интерполятора является стро- бирую щм. Нулевое значение сигнала на указанном выходе указывает, что на первые 20 и вторые 21 выходы интерполятора выставлены значения шаговых приращений. Указанньй сигнал может служить сигналом записи шаговых приращений во внешнюю память (на фиг, 1 не показано). На седьмой вход 19 интерполятора, подключенньм к одиннадцатому входу блока 10 управления, поступает сигнал установки интерполятора в исходное состояние по включению питания. По включению питания на указанньш вход поступает кратко- временньй импульс отрицательной по- лярности. По окончании действия указанного импульса на указанном входе удерживается уровень логической единицы.

Передним фронтом сигнала, посту- пающего на третий вход 18 интерполя- тора, осуществляется запоминание в блоке 10 управления признаков, используемых при формировании шаговых

д g

0

5 О g Q

g

5

0

приращений. На первый вход 16 интерполятора поступает единичный уровень сигнала при АУ X, а на четвертый вход 17 интерполятора - при . В последнем случае значение МП принимается равным БП-МП, а блок 10 управления обеспечивает инвертирование шаговых приращений, полученных в результате интерполяции отрезка с уг. - БП-Ш лом наклона -;;;;-« Ы1

Блок 44 постоянной памяти, входящий в блок 10 управления, осуществляет хранение и выдачу шаговых приращений, соответствующих значению операнда на .его адресных входах. Последний образован з aчeнпя и признаков, хранящихся в четвертом 39, пятом 40 и седьмом 42 триггерах, а также значениями знаковых разрядов первого 8 и второго 9 накапливающих сумматоров, храаящих значение оценочных функций ОФ1, ОФ2. Первый и второй управляюгцяе входы блока 44 постоянной памяти являются BXOAENiii Выборки кристалла. При неактивных уровнях на указанных входах на выходах блока 44 присутствуют уровни логической единицы,

Четвертьй триггер 39 и пятьй D- триггер 40 служат для хранения признаков, определяющих соотношения между приращениями, которыми задан ис- ходньй отрезок прямой, Четвертьй D- триггер 39 устанавливается в состояние логической единицы при ДУ &Х, а пятьй D-триггер 40 при БП с 2МП, Шестой D-триггер 41 служит для хранения признака, определяющего четность или нечетность большего приращения БП, причем установка зтого триггера в состояние логической единицы осу- ;ществляется при нечетном значении БП, Седьмой D-триггер 42 служит для выдачи признака, хранящегося в шестом D-триггере 41 в последнем интерполяционном такте. При нечетном БП в последнем интерполящ-юнном такте осуществляется вьщача только одного шагового приращения по ведущей и ведомой координатам.

Второй D-триггер 36, третий D- триггер 37 и третий элемент И 38 образуют запускающую цепь. При единичном значении указанных триггеров третий элемент И 38 обеспечивает выдачу на свой вход импульсов, поступающих на его первый вход от формирователя 34 импульсов.

Второй 36 и третий 37 В-триггеры обеспечивают присинхронизированное нз:чало работы интерполятора к му импульсу.

Линейный интерполятор работает следующим образом.

На входную информационную шину 12 устройства поступает значение больгае гс приращения БП. При этом на пятом входе 14 интерполятора появляется иклульс отрицательной полярности, подтверждающий наличие на входной информационной пшне 12 значения БП, Под воздействием указанного импульса, поступающего на вход загрузки

счетчика 4, последний принимает .значение г- I . Это достигается за

.

2 Ju,4

счет соединения информаидонных входов счетчика 4 поразрядно, кроме старшего, 2-го по п-й разрядами входной информационной айны 12 и подклю- keroieM старшего разряда к выходу логического нуля.

Значение мпадшего разряда на-входной информационной шине 12, указывающего на четность или нечетность БП, записывается в шестой D-триггер 41 блока 10 .управления

Под воздействием имп льса иа пятом входе 14 интерполятора первый 8 и второй 9 накапливающие сумматоры также как и счетчик 4, принимают значение

БП1 и,м

от

Это достигается подачей на их установочные входы парафазного кода,

ГБПТ соответствующего значению -г

L Z. ц,4

блока 2 совпадения. Информационные входы блока 2 совпадения подключены к входной информационной шине 12 аналогично как для счетчика 4„

Таким Образом, при подаче на вход- кую информационную 1лину 12 значения БП и наличии управляющего импульса на пятом входе интерполятора счетчик 4, первьй 8 и второй 9 накапливающие сум

ГБП

(3 -- I

42 Ju.4

маторы принимают значение

в блоке 10 управления запоминается значение мпадшего разряда большего приращения. После выполнения указанны : действий на входную информа1з;ион- ную шину 12 интерполятора поступает зн51чение меньшего приращения МП.

Под воздействием импульса отрицательной полярности на втором входе 15

5

интерполятора во второй 3 и в первьй 1 регистры координатного приращения записываются соответственно значения 2МП и МП. Значение 2МП на информаци- . онных входах регистра 3 получают за счет соединения их порязрядно, кроме младшего, с второго по п-й разрядами входной информационной щины,12 и под- ключений( младшего разряда к выходу Лог.О, При нечетном значении большего приращения значение младшего разряда БП хранится в блоке 10 управления и при действии импульса на втором входе 15 интерполятора на шестом выходе 28 блока 10 управления формируется импульс, под воздействием которого к содержимому счетчика 4 прибавляется единица, т.е. счетчик 4 при

нимает значение

ЕП 2 Ju.

+ 1.

5

0

5

0

g

0

1 при нечетном значении БП.

Таким образом, при значении МП на входной информационной шине 12 интерполятора и действии импульса записи на втором входе 15 регистр 3 принимает значение 2lin,, регистр 1 - значение МП, счетчик 4 - значение

Ш .

, 2 J и.Ц

I При третьей пересылке от внешнего

устройства на первый 16 и четвертый 17 входы интерполятора поступают соответственно два признака, принимающих единичные значения при uY БП и , БП 2МП. При X БП на первьп вход 16 интерполятора поступает значение Лог.О, При 2MII БП значение логического нуля поступает на четвертый вход 17 устройства. Запись указанных признаков осуществляется импульсом положительной полярности на третьем входе 18 устройства. Указанным сигналом обеспечивается также прием суммы вторым . накапливающим сумматором 9. Поскольку в указанный момент времени на управляющий вход коммутатора 6 поступает значение Лог.О, то на Информационные входы второго 9 накапливающего сумматора 9 поступает значение с вторых входов коммутатора 6, соединенг ных с выходами регистра 1. Начальное значение, хранящееся,во втором накапливающем сумматоре 9, равно

БП 2 Ju.4

а значение операнда, хранящегося в регистре 1,-МП.

Таким образом, под воздействием положительного фронта импульса на третьем входе 18 устройства во вто . 143953

рой накапливагоидай сумматор 9 записы-;

вается значениеЬт- + МП, 1- J Ц-ч

После выполнения указанных действий на входную информационную шину 12 устройства поступает значение БП-2МП, которое записывается в регистр 1, На этом заканчивается цикл подготовки, предшествуклцей циклу интерполяции. IQ

По завершению цикла подготовки в первом 8 и втором 9 накапливающих сумматорах хранятся соответственно

ГБП Гш1

г- . , и г- . + МП, L2 Ju,.4 2 Jц.i

ГБП

г

i Ju,4

4 - значение

регистре 3 - значение 2МП, в регистре 1 - значение БП-2МП, При этомзна- ковыа разряды первого 8 и второго 9 накапливающих сумматоров принимают значения логических нулей, поскольку в них.хранятся положительные операнды. Начальные состояния первого 8 и второго 9 накапливающих сумматоров соответствуют начальным состояниям оценочных функций ОФ1; и ОФ2 . Значение оценочной функции ОФ1 формируется во втором накапливающем суммато ре 9, а оценочньй функции ОФ2| - в первом накапливающем сумматоре 8,

В цикле интерполяции осуществляется формирование шаговых приращений по знакам оценочных функций ОФ1,- и ;ОФ2; в соответствии с таблицей.

При положительных значениях оценочных функций ОФ1 и ОФ2 на первом выходе 31 блока 10 управления форми- руется уровень логической единицы, что обеспечивает передачу -через коммутатор 6 обратного кода величины 2МП с выходов регистра 3.

Указанное значение прибавляется к содержимому первого 8 и второго 9 сумматоров. При этом сигнал логической единицы с первого выхода 31 блока 10 управления поступает также на вход переноса указанных сумматоров. Данные действия в математическом смыле обеспечивают операцию вычитания в дополнительном коде.

При единичном значении хотя бы одного знакового разряда первого 8 или второго 9 накапливающих сумматоров к содержимому этих сумматоров добавляется значение БП-2МП, хранящееся в регистре 1. При этом на пер

Q

5

5 ,„

5

.

.

0

5

212

вом выходе 31 блока 10 управления формируется уровень Лог,О.

С каждым интерполяционньм тактом содержимое счетчика 4 уменьшается на единицу.

По переднему фронту сигнала переполнения счетчика 4 обеспечивается установка устройства в исходное состояние, а на выходе 22 интерполятора формируется сигнал Конец интерполирования.

При вьщаче последних шаговых приращений при нечетном значении БП устанавливается седьмой D-триггер 42, на выходах блока 44 постоянной памяти формируется сигнал, соответствующий только одному шаговому приращению, т.е. сигнал по ведущей координате 10, а по ведомой ХО, где X может принимать единичное или 1гулевое значение.

Блок Ш управления работает следующим образом.

По включению питания на седьмом входе 19 устройства формируется крат- коврейенный и myльc отрицательной полярности, устанавливающий второй 36 и третий 37 D-триггеры в нулевое состояние. На втором выходе 25 блока 10 управления формируется также кратко- временньм импульс отрицательной полярности, сбрасывающий триггеры знаков первого 8 и второго 9 накапливающих сумматоров в нулевое состояние.

Передним фронтом сигнала Пуск в единичное состояние устанавливается третий Б-три ггер 37, что, в свою очередь, устанавливает второй D-триггер 36 в единичное состояние передним фронтом импульсов, формируемых формирователем 34 импульсов. Указанными действиями обеспечивается синхронизированное начало цикла интерполяции по переднему фронту первого импульса, вьщаваемого формирователем 34, после появления сигнала Пуск,

Четвертый 39 и пятый 40 D-триггеры устанавливаются в состояния, соответствующие значениям, заданным соотношением между приращениями, определяющими исходный отрезок прямой. Четвертый D-триггер 39 устанавливается в состояние Лог.Г при i Y : ЛХ, а пятый D-триггер 40 при БП 2МП.

Шестой D-триггер 41 принимает состояние логической единицы при нечетном значении большего приращения.

тановка D-трнггеров 39-41 осуществляется в цикле подготовки.

Блоком 44 постоянной памяти в каждом интерполягдионном такте на основе признаков с четвертого 39 и пятого 40 D-триггеров, а также знаков оценочных

фу;нкций ОФ1; и ОФ2; формируются в соответствии с таблицей значения ша- гоаых приращений.

При появлении сигнала переноса

- (и чпульс отрицательной полярности) на вькоце счетчика седьмой П-триггер 42 устанавливается в срстояние логической единицы при нечетном значении большего приращения, поскольку в указанном случае на выходе шестого D- триггера 41 присутствует уровень логической единицы. Это, в свою очеред приводит к изменению значения адресного входа блока 44 постоянной памяти „

В соответствии с таблицей прожига ПЗУ в этом случае по ведущей координате вьщается значение 10, а по ведомой ХО, где X. может принимать значе ние Лог.С или Лог.1. Последнее определяется значениями оценочных функций и значениями признаков.

Передним фронтом сигнала переноса с выхода счетчика 4 устанавливается в нулевое состояние первый D-триггер 32, обеспечивая сброс второго 36 и третьего 37 D-триггеров, что, в свою очередь, приводит к прекращению подачи импульсов на выход третьего элемента И.

Выход третьего элемента И соединен с входом выборки кристалла блока 44 постоянной памяти. При единичном значении на выходе второго D- триггера 36 и нулевом значении на выходе третьего элемента И 38 блок 44 постоянной памяти выбран и обеспечи- BaetT выдачу шаговых приращений.

В основу работы блока 10 управления положен прЯ1нцип единой временной организации, что позволяет полностью

1, Линейный интерполятор, содержащий первьй и второй регистры координатных приращений, коммутатор, блок совпадения, первьй накапливающий сум- 45 матор, блок управления, первьй йход которого соединен с первым входом интерполятора, второй вход соединен со знаковым выходо первого накапливающего сумматора, третий вход соединен с входом Пуск интерполятора, первьй выход подключен к управляющему входу коммутатора, а второй и третий выходы блока управления подклю- ченьг соответственно к сбросовому и

50

ИСКЛЮЧИТЕ явление гонок и состязагдай. При этом передним фронтом сигнала на вьЕсоде третьего элемента И 38 осуще- ртнляется прием суммы регистрами первого 8 и второго 9 накапливающих сумматоров, а также уменьшение на едини- 55 стробирукяцему входам первого накап- цу содержимого счетчика 4. Вьщача ша- ливающего сумматора, выходы второго говых приращений производится в про- регистра координатных приращений под- межутке между импульсами на выходе|ключены к первым информационным вхо- третьего элемента И 38.Дам коммутатора, а четвертые и пятые

14

Формирование отрезка прямой предлагаемым линейным интерполятором представлено в таблице.

Первый накапливающий сумматор 8 содержит комбинационный сумматор 46 и регистр 47. Старший разряд регистра 47 является знаковым. Вьшолнение второго накапливающего сумматора 9

соверщенно аналогично. Таким образом, линейньй интерполятор обеспечивает воспроизведение отрезков прямых с максимальной точностью, равной половине шага дискретизации. Это дости5 гается начальной установкой первого 8 и второго 9 накапливающих сумматоров, что, в свою очередь, обеспечивает симметрирование погрешности. В известном интерполяторе погреш0 ность аппроксимации равна шагу дискретизации, T.ei в два раза вьше, и при определении шаговых приращений последовательно во времени выполнялись операции суммирозания и сра вне5 ния. В предложенном линейном интерполяторе вьшолняется только операция суммирования, что обеспечивает выиг- рьш в быстродействии на значение

0

где Т,

ГШ

2 Ju,

Р L JU,

- время выполнения операции

ср сравнения.

Линейньй интерполятор отличается также расщиренными функциональными g возможностями за счет формирования iir.tiorta Конец интерполяции так-сигнала

же стробирующего сигнала.

а такФррмула изобретения

40

1, Линейный интерполятор, содержащий первьй и второй регистры координатных приращений, коммутатор, блок совпадения, первьй накапливающий сум- 45 матор, блок управления, первьй йход которого соединен с первым входом интерполятора, второй вход соединен со знаковым выходо первого накапливающего сумматора, третий вход соединен с входом Пуск интерполятора, первьй выход подключен к управляющему входу коммутатора, а второй и третий выходы блока управления подклю- ченьг соответственно к сбросовому и

0

5 стробирукяцему входам первого накап- ливающего сумматора, выходы второго регистра координатных приращений под- |ключены к первым информационным вхо- Дам коммутатора, а четвертые и пятые

t 5

выходы блока управления подключены к первым и вторым выходам интерполято.ра, отличающийся тем, что, с целью повышения быстродействия и точности интерполятора, в него введе.ны счетчик, первый элемент И, первый элемент ИЛИ, второй накапливающий сумматор, информационные входы которого соединены с информационными вхо- .р динены поразрядно с входной информа- дами первого накапливающего суммато- ционной пшной интерполятора, первьй

ны поразрядно, кроме старшего разряда, с второго по (п-1)-й разрядами входной информационной шины интерполятора, а старший разряд информацион ных входов счетчика и блока совпаде- |ния соединен с выходом логического нуля, информационные входы первого регистра координатных приращений соера и выходами коммутатора, установочные входы - с установочными входа: т первого накапливающего сумматора и выходами блока совпадения, а сбросо- вьй и стробируюидий входы - соответст в енно с вторым выходом блока управления и выходом первого элемента ИЛИ при этом знаковьш выход второго накапливающего сумматора подключен к четвертому входу блока управления, входы переноса первого и второго накапливающих сумматоров подключены к первому выходу блока управления, пятый вход которого подключен к выходу переноса счетчика, шестой вход - к управляющему входу второго регистра координатных приращений, первому входу первого элемента И и второму входу интерполятора, седьмой вход блока управления подключен к первому входу первого элемента ИЛИ и третьему входу интерполятора, восьмой вход блока управления подключен к четвертому входу интерпорятора, а девятый вход - к управляющему входу блока совпадения, пятому входу интерполятора и входу загрузки счетчика, суммирующий вход счетчика соединен с шестым выходом блока управления, вычитающий вход счетчика соединен с третьим выходом блока управления, вторы входом первого элемента ИЖ и третьи выходом интерполятора, четвертый выход которого соединен с седьмым выходом блока управления, шестой вход интерполятора соединен с вторым входом первого элемента И, выход первог элемента И соединен с управляющим входом первого регистра координатных приращений, выходы которого подключены к вторым информационным входам коммутатора, первый разряд входной информационной шины интерполятора под ключен к десятому входу блока управления, одиннадцатый вход которого соединен с седьмым входом интерполятора, при этом информационные входы счетчика и блока совпадения соединеU39532

6

динены поразрядно с входной информа- ционной пшной интерполятора, первьй

ны поразрядно, кроме старшего разряда, с второго по (п-1)-й разрядами входной информационной шины интерполятора, а старший разряд информационных входов счетчика и блока совпаде- |ния соединен с выходом логического нуля, информационные входы первого регистра координатных приращений сое5

0

разряд информационных входов первого регистра координатных приращений подключен к выходу логического нуля, а остальные разряды соединены с первого по п-й разрядами входной информационной шины интерполятора.

5

0

5

i71439532,8

го D-триггера, прямой выход котороговходу второго D-триггера и второму

подкл№1ен к информационному входувходу третьего элемента И, выход коEiToporo D-триггера, а стробируняцийторого соединен с. вторым управляющим

вход - к третьему входу блока управ- входом блока постоянной памяти и треления, выход второго D-триггера сое- тьим выходом блока управления, инфор- динен с первым управляющим входом: бло- мационные входы четвертого и пятого ка постоянной памяти, первым входомD-триггеров подключены соответствентретьего элемента И и седьмым выходом но к первому и восьмому входам блока блока управления, первый вход второго Q управления, седьмой вход блока уп- элемента И подключен к выходу йерво- равления соединен со стробирующими го О-триггера, второй вход к один- входами четвертого и пятого D-триг- надцатому входу блока управления, агеров, информационный вход первого

выход - к R - входам второго и тре-D-триггера подключен к выходу логитьего П-тригг еров и второму выходу д ческого нуля, а информационный вход блока управления, вькод формирователя -третьего D-триггера - к выходу логи- импульсов подключен к стробирующемуческой единицы.

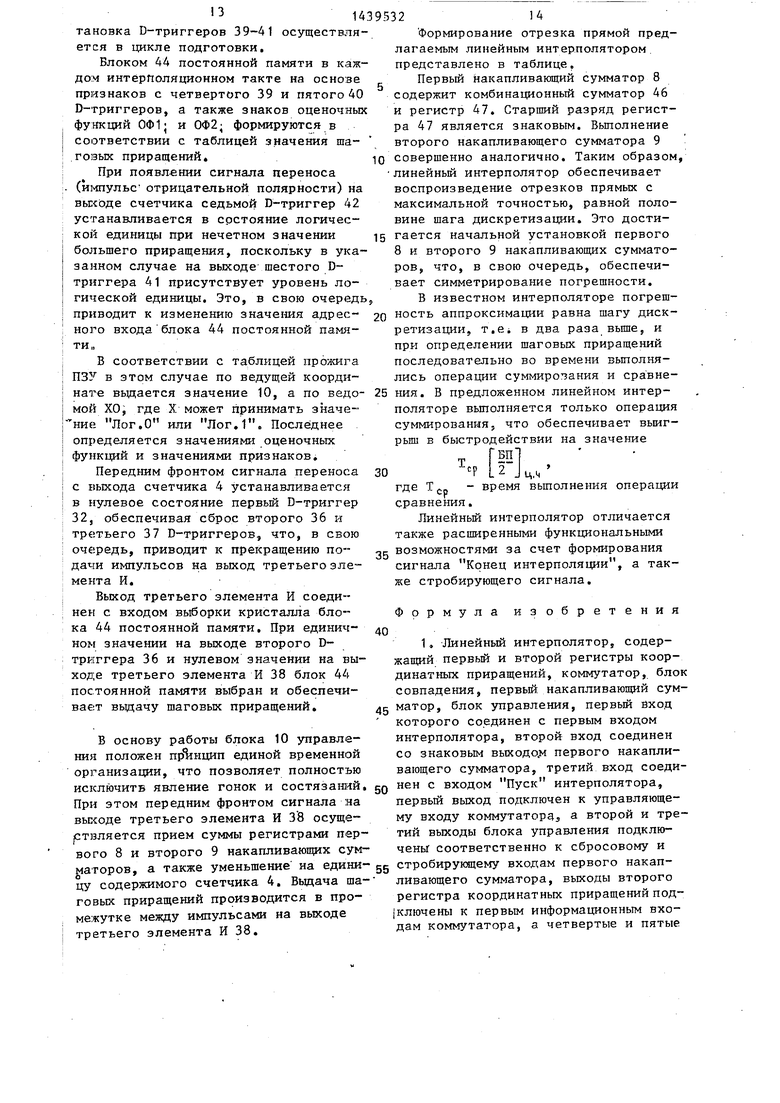

Пусть йХ 18, &Y 5. Очевидно, что БП 18, Ж1 5. 2Ш 10, БП - 2МП 8„

™ « г ц.,

ОФ1,0,ОФ2 -сО- -приращение 01.

2, ОФ12 ОФЬ + (БП-2МП) -125ОФ2 ОФ2,, -5- (БП-2МП) 7.

ОФ 0 ОФ22 0- -приращение 00.

Зо ОФ1з ОФ1,г: - 2Ш 2,ОФ2 002 - 2МП -3.

ОФ1. , - -приращение 01.

ОФЦ 0 ОФ24 О -1-приращение- 00,

ОФ1,. 0,ОФ25. 4 о- -приращение 01.

,С1Ф2 о -s-приращение 00.

ОФ1-, сО,ОФ2 0-fc-приращение 10,

,OO2g 0 -э.приращение 00.

. ОФ2 О -«-приращение е 10.

ГТ1 1 11

2Q 22 2i

i9 // 22 Фаз. /

f

1 1 11

22 2i

i9 // 22 Фаз. /

Ноцало

ГУ.-- Bf//s i,v. HSff}r.,4,

ИЗт21 П/ ц..

3HGWHUQ МЛв

Qiueso разряВа шины 12

fiGfs Mn

yew

Tf)3S: - значение дхода W

значение Входа /7

HSm2 .

. --6П-&МП

С(

ВьиислениеОФ11 002i

Bbidai a шагового

приращения по oedyuf&u ц бедо- мой ноординате б coomS. с табл.7

( kOHQH

«

и

15

ia

г/

п

13

11

Выид SMM37

Btitoi SnutaSS

ъ

o JПJlJlJlJПJ-uтл...-ГLл

П П П П л

ВнжоВ SflOKoiS

Нет

f

Выдача KOf fuHu- poSoHHt i)( dSouf ix шагоЗык прира- U4ewu Scoomd. с maSu) 1

Фи2.

ъ

л

Фиг.5

I &

FT PTTTTir 5 Щ я Щ я Hfj tStS 11 |

т , go 9J 00 w во Ю

| Линейный интерполятор | 1975 |

|

SU551610A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

Авторы

Даты

1988-11-23—Публикация

1987-01-30—Подача