принимают операнды на вторые входы с выхода сумматора 29, на первый вход блока 40 поступает операнд с выхода регистра 32, а на первый вход блока 39 поступает операнд с выхода .. сумматора 26. Операнды на выходе блоков 39 и 40 определяют отношение

д 1628210d

сигнал/помеха на входе и выходе бло- ка 1. Формирователь 3 контрольной последовательности, вычислитель 14 и - блок 1 обработки входного процесса могут иметь вариант выполнения. 3 з.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Генератор периодических колебаний инфразвуковых частот с автоматической калибровкой | 1987 |

|

SU1497722A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Устройство контроля качества канала связи | 1987 |

|

SU1499508A1 |

| Устройство для синхронизации шумоподобных сигналов | 1982 |

|

SU1022326A1 |

| Устройство синхронизации шумоподобных сигналов | 1979 |

|

SU879802A2 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Система передачи и приема информации с многоосновным кодированием | 1989 |

|

SU1642590A1 |

Изобретение относится к технике связи. Целью изобретения является повышение точности контроля и расширение функцицнальных возможностей устройства. Блоки 39 и 40 деления по сигналу с выхода формирователя 13 С/) АягЯ

Изобретение относится к технике связи и может быть использовано для контроля качества каналов связи с шу- мопсдобными сигналами при пассивных и организованных помехах, а также при многолучевом распространении сигналов.

Цель изобретения - повышение точности контроля и расширение функциональных возможностей.

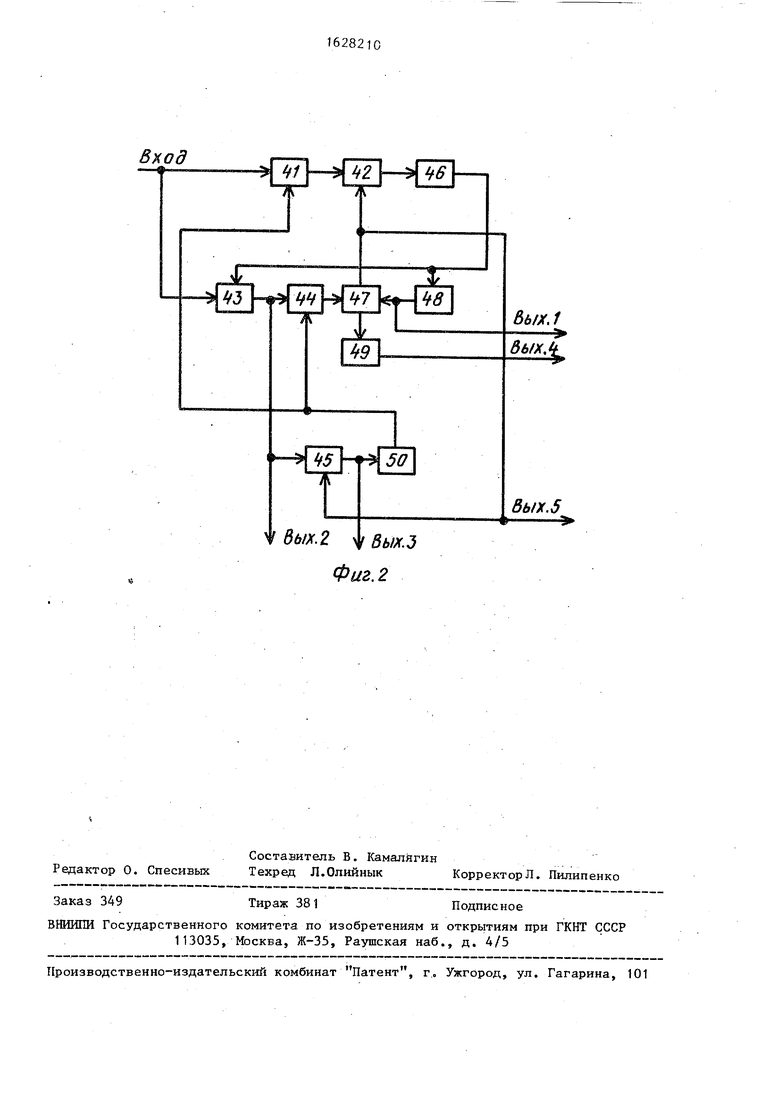

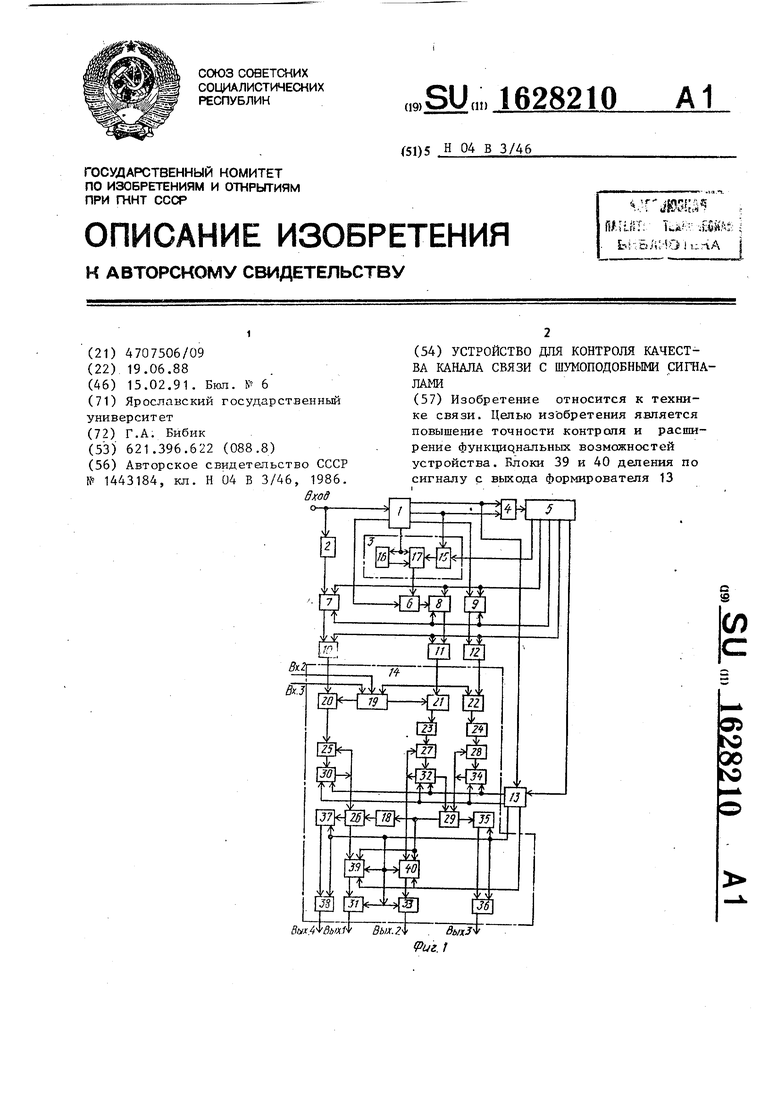

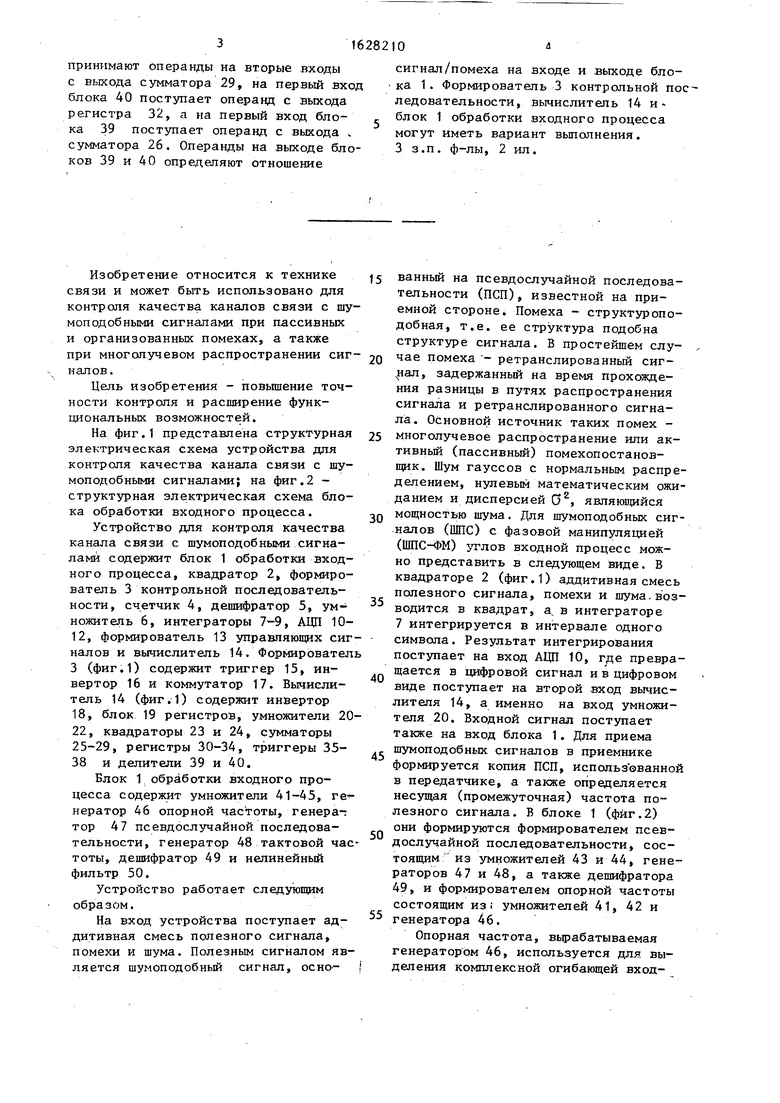

На фиг.1 представлена структурная электрическая схема устройства для контроля качества канала связи с шу- моподобными сигналами; на фиг.2 - структурная электрическая схема блока обработки входного процесса.

Устройство для контроля качества канала связи с шумоподобными сигналами содержит блок 1 обработки входного процесса, квадратор 2, формирователь 3 контрольной последовательности, счетчик 4, дешифратор 5, умножитель 6, интеграторы 7-9, АЦП 10- 12, формирователь 13 управляющих сигналов и вычислитель 14. Формировател 3 (фиг.1) содержит триггер 15, инвертор 16 и коммутатор 17. Вычислитель 14 (фиг.1) содержит инвертор 18, блок 19 регистров, умножители 20 22, квадраторы 23 и 24, сумматоры 25-29, регистры 30-34, триггеры 35- 38 и делители 39 и 40.

Блок 1 обработки входного процесса содержит умножители 41-45, генератор 46 опорной частоты, генератор 47 псевдослучайной последовательности, генератор 48 тактовой частоты, дешифратор 49 и нелинейный фильтр 50.

Устройство работает следующим образом.

На вход устройства поступает аддитивная смесь полезного сигнала, помехи и шума. Полезным сигналом является шумоподобный сигнал, осно--

0

5

0

5

0

5

0

5

ванный на псевдослучайной последовательности (ПСП), известной на приемной стороне. Помеха - структуропо- добная, т.е. ее структура подобна структуре сигнала. В простейшем случае помеха - ретранслированный сиг- лнал, задержанный на время прохождения разницы в путях распространения сигнала и ретранслированного сигнала. Основной источник таких помех - многолучевое распространение или активный (пассивный) помехопостанов- щик. Шум гауссов с нормальным распределением, нулевым математическим ожиданием и дисперсией С2, являющийся мощностью шума. Для шумоподобных сигналов (ШПС) с фазовой манипуляцией (ШПС-ФМ) углов входной процесс можно представить в следующем виде. В квадраторе 2 (фиг.1) аддитивная смесь полезного сигнала, помехи и шума-возводится в квадрат, а. в интеграторе 7 интегрируется в интервале одного символа. Результат интегрирования поступает на вход АЦП 10, где превращается в цифровой сигнал и в цифровом виде поступает на второй вход вычислителя 14, а именно на вход умножителя 20. Входной сигнал поступает также на вход блока 1. Для приема шумоподобных сигналов в приемнике формируется копия ПСП, использованной в передатчике, а также определяется несущая (промежуточная) частота полезного сигнала. В блоке 1 (фиг.2) они формируются формирователем псевдослучайной последовательности, состоящим из умножителей 43 и 44, генераторов 47 и 48, а также дешифратора 49, и формирователем опорной частоты состоящим из; умножителей 41, 42 и генератора 46.

Опорная частота, вырабатываемая генератором 46, используется для выделения комплексной огибающей входного процесса. Эта комплексная огибающая поступает в умножитель 44. В умножителе 45 из комплексной огибающей снимается манипуляция ПСП, и нелинейный .фильтр 50 выделяет сигнал текущей информации, а умножитель 44 из комплексной огибающей снимает манипуляцию сигналом текущей информации и результирующий сигнал поступает на вход управляемого генератора 47 ПСП, охваченного кольцом обратной связи. Выход генератора 47 является выходом блока 1 и соединен с вторыми входами умножителей 42 и 45, которыми снимается манипуляция сигналов ПСП. Снятие информационной манипуляции сигнала осуществляется умножителями 41 и 44 по сигналуti поступающему с выхода нелинейного фильтра 50. Генератор 48 формирует тактовую частоту. Когда тактовая частота кратна несущей, то генератор 48 является делителем несущей частоты. Дешифратор 49 определяет границы символов, поскольку граничные комбинации ПСП известны.

Последовательность с выхода умножителя 43 поступает на БХОД умножителя 45, в котором умножится на ПСП. Сигнал с выхода блока 1 поступает на интегратор 9 (фиг.1), где он интегрируется на интервале одного символа 0-Т. Затем сигнал поступает на АЦП 12, с которого в цифровом виде поступает на четвертый вход вычислителя 14, а именно на вход умножителя 22. С выхода умножителя 43 (фиг.2) последовательность поступает на вход умножителя 6 (фиг.1), на другой вход которого с выхода формирователя 3 поступает контрольная последовательность ортогональная ПСП. С выхода умножителя 6 сигнал поступает в интегратор 8. Далее сигнал преобразуется в цифровой АЦП 11 и поступает на третий вход вычислителя 14. Поме- ховая составляющая сигнала, поступающего на четвертый вход вычислителя статистическом отношении равна сигналу поступающему на его третий вход. Вычислитель 14 работает следующим образом. На его первый вход поступают тактовые импульсы с первого выхода блока 13, а на седьмой вход с этого блока поступают сигналы пуска делителей 39 и 40. На второй -v четвертый входы вычислителя 14 поступают в цифровом виде сигналы с вы0

5

ходов соответствующих АЦП 10-12. Эти сигналы поступают на входы соответствующих умножителей 20-22, где происходит их нормирование. Нормирование коэффициента хранится в блоке 19. С умножителя 20 сигнал поступает на сумматор 25, а с выходов умножителей 21 и 22 сигналы возводятся в квадрат квадраторами 23 и 24, с выхода которых поступают на сумматоры 27 и 28. Сумматоры 25, 27 и 28 вместе с регистрами 30, 32 и 34 накапливают поступающие на них числа и на выходе их в конце периода оценки сигналов запоминаются результирующие сигналы.

Перед началом каждого цикла вычислений, но после того как операнды 0 предыдущего цикла приняты делителями 39 и 40, регистры 30, 32 и 34 обнуляются сигналами, поступающими с второго выхода блока 13. На выходе сумматора 29 получается величина, про- 5 порциональная мощности полезного сигнала. На выходе сумматора 29 подаются результаты накопления в регистрах 32 и 34, причем с регистра 32 операнд выдается с инверсного 0 выхода,.а на вход переноса в младший разряд сумматора 29 подаются единицы, т.е. сумматор 29 работает как вычитатель. Этот операнд в инверсном коде подается на вход сумматора 26, на вход переноса в младший разряд которого подается единица. На другой вход поступает операнд с выхода регистра 30. В результате сумматор 26 работает как вычитатель, 0 операнд на выходе которого пропорционален помехе на входе блока 1. Делители 39 и 40 принимают операнды, с выхода сумматора 29 на вход делителя 40 поступает1 операнд с вы- 5 хода регистра 32, а на вход делителя 39 поступает операнд с выхода сумматора 26. Операнды на выходе делителей 39 и 40 определяют отношение сигнал/помеха на входе и выходе бло- 0 ка 1. По сигналу с блока 13 запускается операция деления в делителях 39 и 40, по этому же сигналу регистры 31 и 33 принимают результаты деления, т.е. отношения сигнал/помеха 5 на входе и выходе блока 1|И выдают их на первый и второй выходы устройства. По этому же сигналу принимают информацию триггеры 35-38. Информационные входы триггеров 35 и 37 сое5

динены с выходами знаковых разрядов сумматоров 26 и через цикл вычисле- ния выдают сигналы знаков на триггеры 36 и 38, с выходов которых они поступают на третий и четвертый выходы устройства. Если знак минус кодируется 1, то единица на выходе триггера 35 означает, что внешнего шума помехи нет, а единица на выходе триг- г ера 36 означает, что сигнала нет.

Формирователь 3 контрольной последовательности может быть выполнен различными способами. Дело в том,

что опорная ПСП на приемном конце известна и нужно сформировать ортогональную ей ПСП. Для этого достаточно пропускать половину элементов . ПСП в прямом коде, а половину в ин- версном. Для этого достаточно триггер 15 поставить в счетный режим и коммутатор 17 будет пропускать элементы ПСП то непосредственно с выхода блока 1, то через инвертор 1. Аналогично можно передавать куски ПСП в прямом и инверсном коде. В этом случае наиболее удобно часть ПСП составляющую половину символа, передавать в прямом коде, а вторую поло- вину в инверсном коде. Законом формирования контрольной последовательности легко управлять синхронизатором. Синхронизатор в простейшем случае - это счетчик 4 числа тактов, поступающих с первого выхода блока 1 и дешифратора 5.

Формула из р е т е н и я

первым входом устройства, последова- тельно соединенные умножитель, второй интегратор и второй аналого-цифровой преобразователь, выход которого подключен к третьему входу вычислителя, последовательно соединенный тре- тий интегратор и третий аналого- цифровой преобразователь, выход которого подключен к четвертому входу

5 Q

5

0

5

5

вычислителя, первый и второй выходы которого являются соответственно первым и вторым выходами устройства, о т- личающееся тем, что, с целью повышения точности контроля, введены формирователь контрольной последовательности, выход которого подключен к первому входу умножителя и последовательно соединенные блок обработки входного процесса, счетчик и дешифратор, выход которого подключен к первому входу формирователя управляющих сигналов, второй вход которого соединен с первым выходом блока обработки входного процесса, второй, третий и четвертый выходы подключены соответственно к пятому, шестому и седьмому входам вычислителя, восьмой и девятый входы которого являются вторым и третьим входами устройства, а третий и четвертый выходы являются соответственно третьим и четвертым выходами устройства, вход блока обработки входного процесса объединен с входом квадратора, второй выход подключен к второму входу умножителя, третий выход подключен к первому входу третьего интегратора, четвертый выход подключен к второму входу счетчика и первому входу формирователя контрольной последовательности, пятый выход подключен к второму входу формирователя контрольной последовательности, третий вход которого соединен с вторым выходом дешифратора, третий выход дешифратора подключен к объединенным вторым входам первого, второго и третьего интеграторов, четвертый выход подключен к объединенным третьим входам первого, второго и третьего интеграторов, пятый выход подключен к объединенным вторым входам первого, второго и третьего аналого- цифровых преобразователей.

10

15

916282

которого подключен к третьему входу коммутатора.

является четвертым выходом вычислителя, первым входом которого являются объединенные вторые входы первого, третьего и пятого регистров, вторым, третьим и четвертым входами являются п соответственно второй вход первого умножителя, первый вход второго умножителя и первый вход третьего умножителя, пятым входом являются объединенные третьи входы первого, третьего и пятого регистров, шестым входом являются объединенные вторые входы первого, второго, третьего и четвертого триггеров, вторые входы первого и второго делителей и вторые входы второго и четвертого регистров, седьмым входом являются объединенные третьи входы первого и второ- го делителей, восьмым и девятым входаи являются соответственно первый и второй входы блока регистров, второй и третий выходы которого подключены соответственно к вторым входам втоого и третьего умножителей, выход

35

40

45

первого регистра подключен к другому

10

10

10

15

5 20 25

п

35

40

5

0

входу первого сумматора, первый выход третьего регистра подключен к другому входу третьего сумматора второй выход подключен к другому входу пятого сумматора, второй выход которого подключен к объединенным третьим входам первого и второго делителей и через инвертор к второму входу второго сумматора, второй выход которого подключен к второму входу третьего триггера, первый выход пятого регистра подключен к другому входу четвертого сумматора.

Вход

9l

.

W

v вых.2 ф вых.3 Фиг. 2

Редактор О. Спесивых

Составитель В. Камалягин

Техред Л.Олийнык Корректор Л. Пилипенко

Заказ 349

Тираж 381

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

&ЫХ.1

&ь/хА

+

Вых.5

Подписное

| Устройство для контроля качества канала связи | 1986 |

|

SU1443184A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| вход о | |||

Авторы

Даты

1991-02-15—Публикация

1989-06-19—Подача