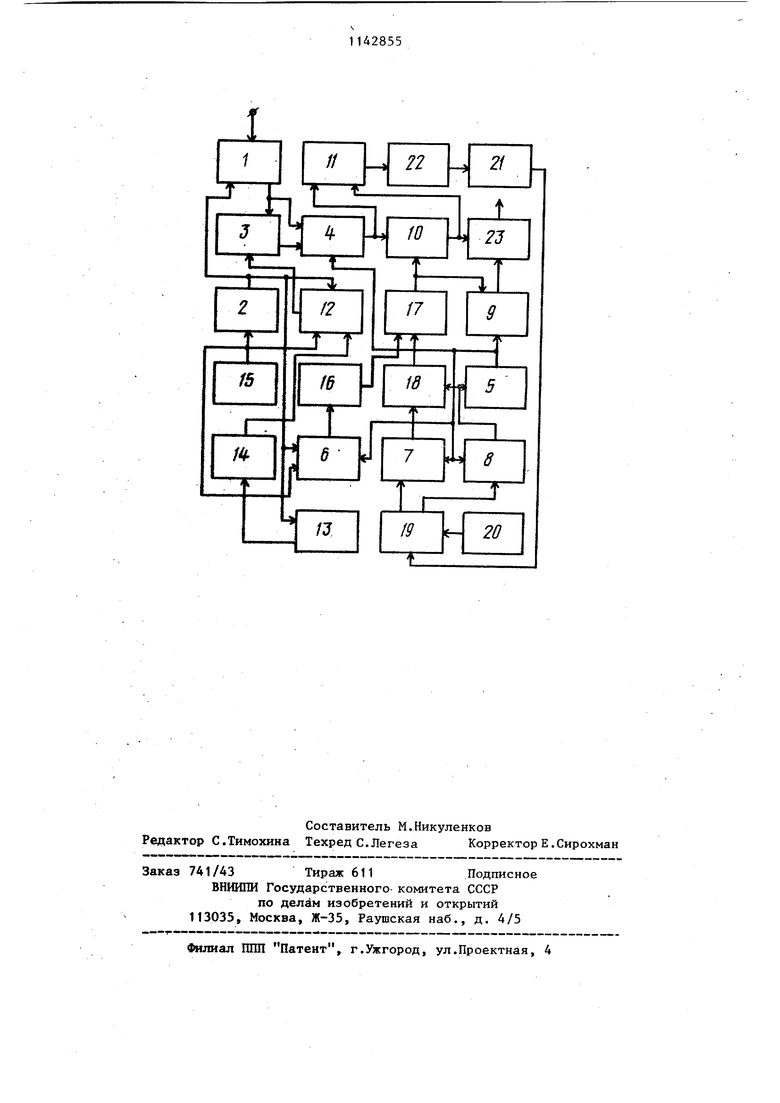

Изобретение относится к электроизмерительной и вычислительной технике и может быть использовано в устройствах передачи и автоматизи рованной обработки информации. Известно устройство для сжатия информации, содержащее коммутатор, аналого-цифровой преобразователь, блок сравнения, блоки, памяти и программно-временной блок t11 Недостатком известного устройств является низкое быстродействие процесса сжатия информации при отсутст вии сведений о свойствах исследуемого сигнала. Наиболее близким по технической сущности к предлагаемому является устройство для сжатия информации, содер жащее аналого-цифровой преобра зователь, первый вход которого явля ется входом устройства, первьй .блок памяти, выход которого соединен с первым входом блока сравнения, первый и второй выходы которого сое динены с первыми входами соответственно первого и второго ключей, выход первого ключа соединен с первым входом сумматора и входом первого триггера, выход первого триггера соединен с первым входом третьего ключа и вторыми входами первого и второго ключей, выход второго ключа соединен с вторым входом сумматора выход которого соединен с первым входом коммутатора j выход коммутато ра соединен с первым входом регистр и вторым входом третьего ключа, выход третьего ключа соединен с первы входом второго блока памяти, выход которого является выходом устройства, генератор импульсов, выход которого соединен с вторым входом аналого-цифрового преобразователя, выход которого соединен с первым входом вьгчитателя и вторым входом регистра, выход регистра соединен с вторыми входами второго блока пам ти и вычитателя, выход вьгчитателя подключен через последовательно соединенные квадратор и усреднитель к второму входу блока сравнения, выходы делителя частоты соединены с соответствующими вторыми входами коммутатора 2, Недостатком этого устройства яв ляется низкое быстродействие адапт ции к параметрам входного сигнала. Цель изобретения - повышение быстродействия процесса установления рабочего режима устройства для сжатия информации. Поставленная цель достигается тем, что в устройство для сжатия информации, содержащее аналого-цифровой преобразователь, первый вход которого является входом устройства, генератор импульсов, первый блок памяти, выход которого соединен с первым входом блока сравнения, первый и второй выходы которого соединены с первыми входами соответственно первого и второго ключей, выход первого ключа соединен с пер вым входом сумматора и входом первого триггера, выход первого триггера соединен с первым входом третьего ключа и вторыми входами первого и второго ключей, выход второго ключа соединен с вторым входом сумматора, выход которого соединен с первым входом коммутатора, вторые входы коммутатора подключены к соответствующим выходам первого делителя частоты, выход коммутатора соединен с первым входом регистра и вторым входом третьего ключа, выход третьего ключа соединен с первым входом второго блока памяти, выход которого является выходом устройства, выход регистра соединен с вторым входом второго блока памяти и первым входом вычитателя, выход вычитателя подключен через последовательно соединенные квадратор и усреднитель к второму входу блока сравнения, введены третий блок памяти, второй делитель частоты, второй триггер, переключатели и счетчик, выход генератора импульсов соединен с первыми входами первого и второго-переключателей и через второй делитель - с входом счетчика и вторыми входами первого, второго переключателей и аналого-цифрового преобразователя, выход счетчика соединен через второй триггер с третьим входом первого переключателя, выход первого переключателя соединен с первьш входом третьего блока памяти, рыход которого соединен с первым входом третьего переключателя, выход аналого-цифрового преобразователя соединен с вторыми входами третьего блока памяти и третьего переключателя, выход третьего перск.пи)чателя соединен с вторыми вхолами вычитателя и регистра, выход первого триг гера соединен с третьими входами второго и третьего переключателей, выход второго переключателя соедине с входом первого делителя частоты. На чертеже представлена структур ная схема предлагаемого устройства, Устройство для сжатия информации содержит аналого-цифровой преобразо ватель 1, делитель 2 частоты, блок буферной памяти, переключатель 4, триггер 5, переключатель 6, ключи 7-9, регистр 10 сдвига, вычитатель 11, переключатель 12, счетчик 13, триггер 14, генератор 15 им пульсов, делитель 16 частоты, коммутатор 17, сумматор 18, блок 19 сравнения, блок 20 постоянной памяти, усреднитель 21, квадратор 22 и блок 23 буферной памяти. Устройство работает следующим образом. При включении устройства его бло ки устанавливаются в исходное состо ние. Обрабатываемый сигнал преобразуется в цифровую форму аналого-циф ровым преобразователем 1 и записывается в блок 3 буферной памяти, в дискретные моменты времени с шаго задаваемым делителем 2 .частоты. Мак симально возможная частота запуска аналого-цифрового преобразователя 1 при этом формируется делением на постоянную величину частоты генератора 15 импульсов в делителе 2 част ты. -С выхода делителя 2 частоты час тота запуска аналого-цифрового преобразователя 1 подаетсяJ кроме того на вход счетчика 13, на вход переключателя 6 частоты и через переключатель 12 частоты-на вход блока 3 буферной памяти для записи в него орди нат несжатого сигнала до заполнения. Триггером 5 второй переключатель устанавливается в положение, при котором на вход делителя 16 частоты поступает частота генератора 15 импульсов. На выходе делителя 16 частоты образуется сетка частот, поступающая на входы коммутатора 17 Сумматор. 18, управляющий коммутатором 17, после установки, блоков устройства в исходное состояние из ука занной сетки частот на выходе делителя 16 позволяет передать на вход регистра 10 самую высокую частоту. При записи ординат сигнала в блок 3 буферной памяти информация на выходе блока 3 отсутствует, так как идет запись ординат. Информация на выходе блока 3 появляется при считывании ординат сигнала из блока 3. По сигналу переполнения счетчика 13, объем которого равен заданному числу слов блока 3 буферной памяти, переключается триггер 14, устанавливая переключатель 12 в положение, при котором на его выходе появляется высокая частота, формируемая генератором 15 импульсов. Частота генератора 15 импульсов выбирается значительно более высокой, чем частота запуска аналогоцифрового преобразователя 1. Она используется для вывода результатов аналого-цифрового преобразования (кодов ординат сигнала) из блока 3 буферной памяти после его заполнения. Перед началом процесса сжатия код сумматора 18 соответствует максимальной частоте, равной, например, частоте генератора 15 импульсов, деленной пополам. После установки узлов устройства в исходное состояние триггер 5 открывает ключи 7 и. 8, закрывает ключ 9 и устанавливает переключатель 4 в положение, при котором данные с выхода блока 3 буферной памяти передаются при выводе данных через переключатель 4 на входы вычитателя 11 и регистра 10. Передача данных на входы блоков 10 и 11 начинается после переключения триггера 14. С этого момента начинается сжатие ординат, запомненных в блоке 3, с высокой тактовой частотой. Для осуществления сжатия ординат сигнала определяются разности между предьздущей и последующей существенными ординатами. Для определения этих разностей на первом цикле усредения в регистр 10 с коммутатора 17 одается вдвое более низкая частота о отношению к частоте вывода даных из блока3. Следовательно-, регистр 10 из блока 3 последоваельно записываются коды каждой втоой ординаты сигнала. Эти коды по- . тупают на вход вычитателя 11, на ругой вход которого поступают коды сех ординат сигнала. Разности межу кодами ординат из вычитателя 11 оступают в квадратор 22 и усредниель 21. Полученное действительное значение среднеквадратической погре ности от сжатия информации на выходе устреднителя 21 сравнивается в блоке 19 сравнения с заданной погрешностью сГ , хранимой в блоке 20 памяти. Приема сГ блок 19 сравнения передает через ключ 7 в сумматор 18 сигнал, разрешая переключение выхода коммутатора 17 на более низкую частоту, поступающую от делителя 16 частоты. На этом .заканчивается первьй цикл усреднени квадратов разностей кодов между существенными ординатами и начинается следующий цикл. В следующем цикле более низкая частота, управляющая регистром 10, позволяет, например, еще вдвое уменьшить количество кодо ординат, записываемых в регистр 10 При этом частота вывода кодов ординат из блока 3 сохраняется, как и н предыдущем цикле значительно более высокой, чем максимальная частота аналого-цифрового преобразования. Объем блока 3 буферной памяти определяет объем усреднения усреднителя 21, Он выбирается из условия мак симального быстродействия аналогоцифрового преобразователя 1 и интер вала корреляции входного сигнала. Интервал усреднения пропорционален величине интервала корреляции сигна ла и обратно пропорционален заданно погрешности от сжатия сигнала. В прототипе циклы усреднения следуют с частотой аналого-цифровог преобразования, что снижает быстродействие известного устройств. На последующих циклах усреднения квадратов разностей кодов ординат сигна г,1 }. па сравниваются величины Од и 0| , а код сумматора 18 корректируется. Циклы усреднения квадратов разностей, получающихся со все более увеличивающимся шагом, следуют друг за другом до тех пор, пока при условии cJq - ° 3 с выхода блока 19 сравнения не поступит сигнал через 6 ключ 8 на вычитающий вход сумматора 18 и на вход триггера 5. Код сумматора 18 уменьшается на единицу, следовательно, возрастает частота, коммутируемая с выхода делителя 16 частоты на управление регистром 10. Такое изменение частоты управления регистром 10 необходимо для того, чтобы вьтолнялось неравенство Од о, при сжатии ординат сигнала. При переключении триггера 5 его сигналом открьгаается ключ 9 и закрываются ключи 7 и 8, переключатель 4 устанавливается в положение, при котором коды аналого-цифрового преобразователя 1, минуя блок 3 буферной памяти, записываются в регистр 10, а переключатель 6 подключает к своему выходу частоту запуска аналого-цифрового преобразователя 1, которая поступает с выхода делителя 2 частоты. Замена тактовой частоты, поступающей на вход делителя 16 частоты, позволяет при дальнейшей работе устройства осуществлять сжатие ординат сигнала с частотой, пропорциональной частоте аналого-цифрового преобразования, на которой бьши записаны несжатые ординаты сигнала в блок 3 буферной памяти, и по которым были определены с высокой скоростью (на высокой тактовой частоте генератора импульсов) параметры сжа тия выходного сигнала. Из регистра 10 коды сжатых ординат поступают в блок 23 памяти. Блок 23 фиксирует ординаты сжатого сигнала с заданной среднеквадратической погрешностью при соотношении , , Сжатая информация снимается с выхода блока 23 памяти. Предложенное устройство позволяет сократить время автоматического выбора частоты вьщачи существенных ординат сигнала с постоянным временным масштабом при сжатии в зависимости от величины заданной среднеквадратической погрешности от сжатия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1986 |

|

SU1365107A1 |

| Устройство для сжатия информации | 1980 |

|

SU930333A1 |

| Устройство для обнаружения сигналов и измерения их параметров | 1987 |

|

SU1478145A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1126993A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1129641A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Устройство для приема и обработки информации | 1979 |

|

SU855715A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

УСТРОЙСТВО ДЛЯ СЖАТИЯ ИНФОРМАЦИИ, содержащее аналого-цифровой преобразователь, первый вход которого является входом устройства, генератор импульсов, первый блок памяти, выход которого соединен с первым вхо.дом блока сравнения, первый и второй ; выходы которого соединены с первыми входами соответственно первого и второго ключей, выход первого ключа соеI дивен с первым входом сумматора и входом первого триггера, выход перi него триггера соединен с первым вхо:дом третьего ключа и вторыми входами первого и второго ключей, выход втоj рого ключа Соединен с вторым входом сумматора, выход которого соединен с первым входом коммутатора, вторые входы коммутатора подключены к соот-. ветствзтощим выходам первого делителя частоты, выход коммутатора соединен с первым входом регистра и вторым входом третьего ключа, выход третьего ключа соединен с первым входом второго блока памяти, выход которого является выходом устройства, выход регистра соединен с вторым входом второго блока памяти и первым входом вычитателя, выход вычитателя подключен через последовательно соединенные квадратор и усреднитель к второму входу блока сравнения, о т л ичающееся тем, что, с целью повьшения быстродействия устройства, в него введены третий блок памяти, второй делитель частоты, второй триггер, переключатели и счетчик, выход генератора импульсов соединен (Л с первыми входами первого и второго переключателей и через второй делитель - с входом счетчика и вторыми входами первого, второго переключателей и аналого-цифрового преобразователя, выход счетчика соединен через второй триггер с третьим входом « первого переключателя, выход первоfO X) го переключателя соединен с первым входом третьего блока памяти, выход которого соединен с первым входом третьего переключателя, выход аналого-цифрового преобразователя соединен с вторыми входами третьего блока памяти и третьего переключателя, выход третьего переключателя соединен с вторыми входами вычитате:Ля и регистра, выход первого триггера соединен с третьими входами второго и третьего переключателей, выход второго переключателя соединен с входом первого делителя частоты.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ольховский Ю.Б | |||

| , Новоселов О.Н., Мановцев А.П Сжатие данМ., ных при телеизмерениях | |||

| Советское радио, 1971, с | |||

| Котел | 1921 |

|

SU246A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сжатия информации | 1980 |

|

SU930333A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-02-28—Публикация

1983-12-26—Подача