Изобретение относится к вычислительной технике и АСУ и может быть использовано в качестве устройства управления диагностированием и восстановлением мажоритарно-резервируемых систем, работающих в реальном масштабе времени.

Цель изобретения - повышение производительности путем обеспечения возможности параллельной реализации алгоритмов управления диагностирования и восстановления каналов.

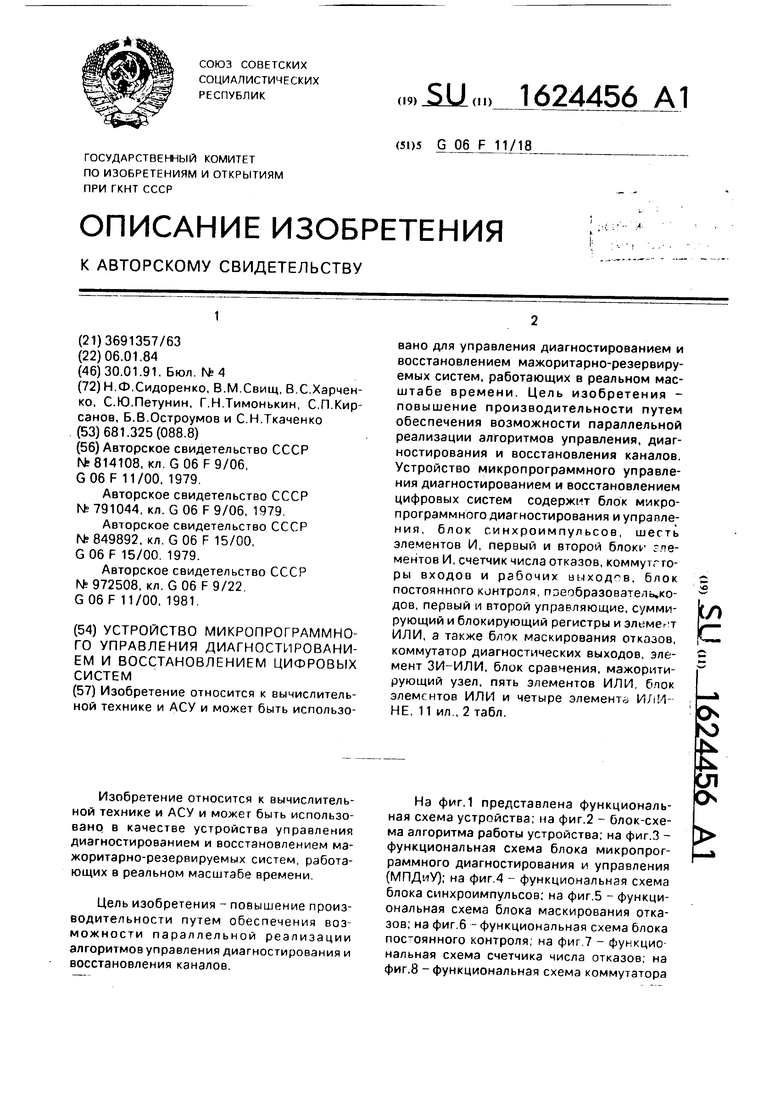

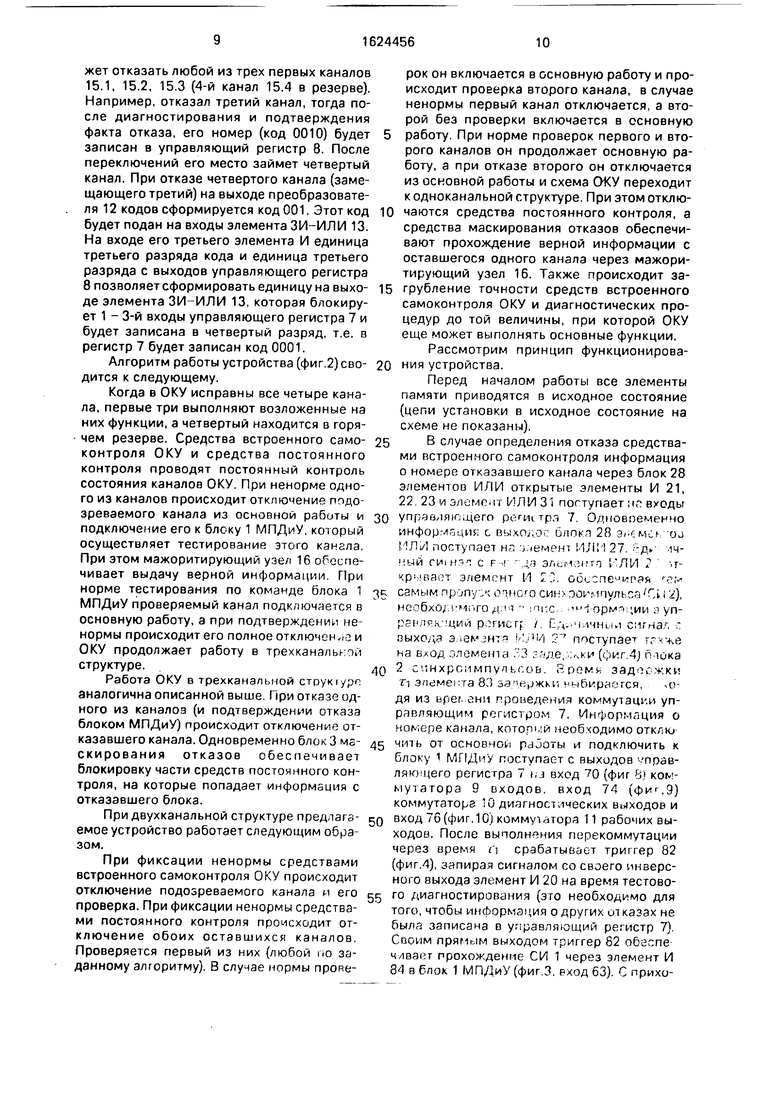

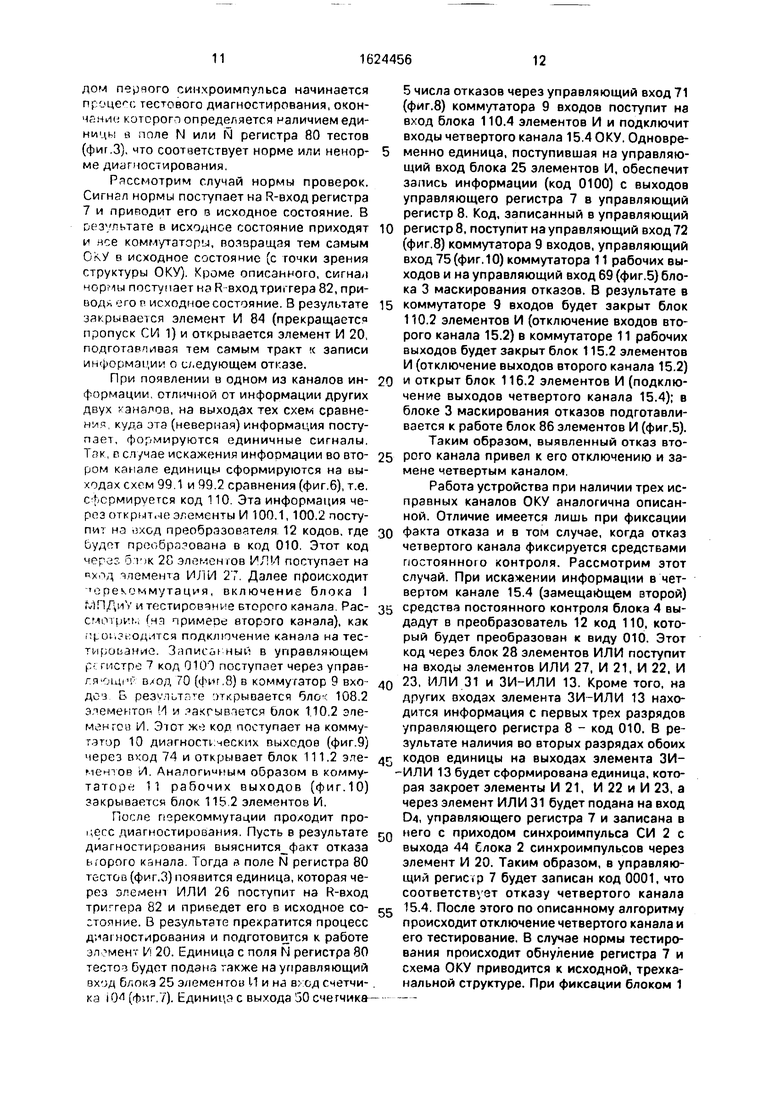

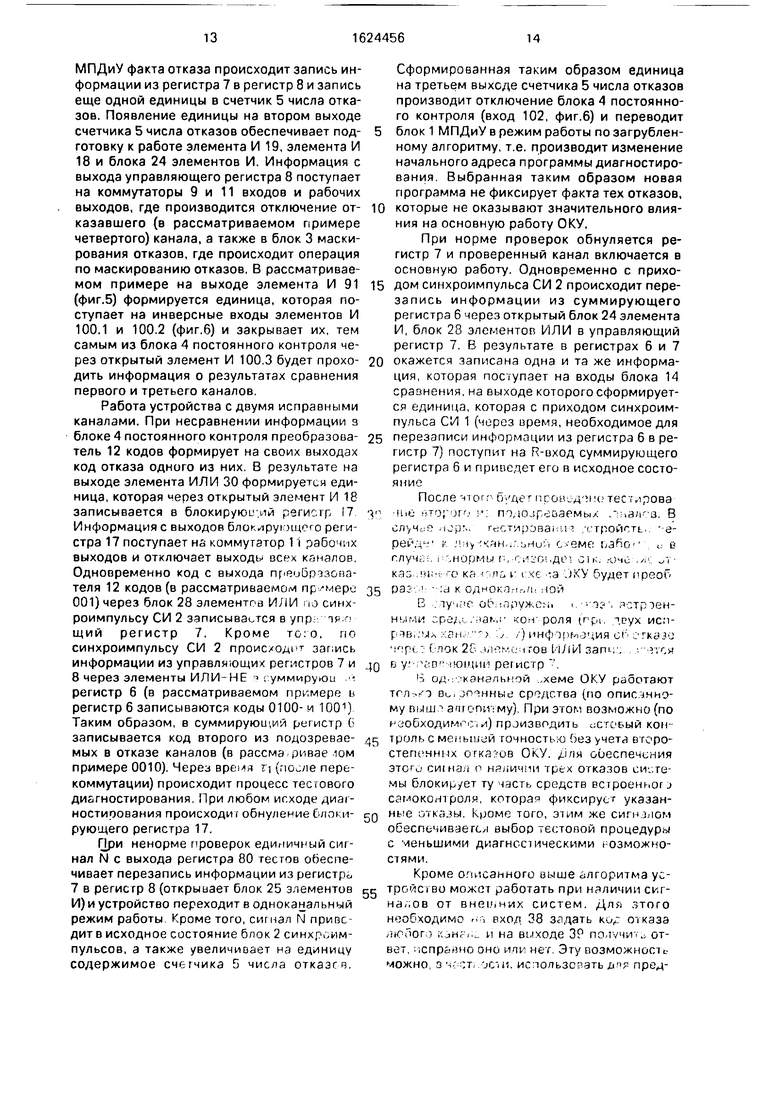

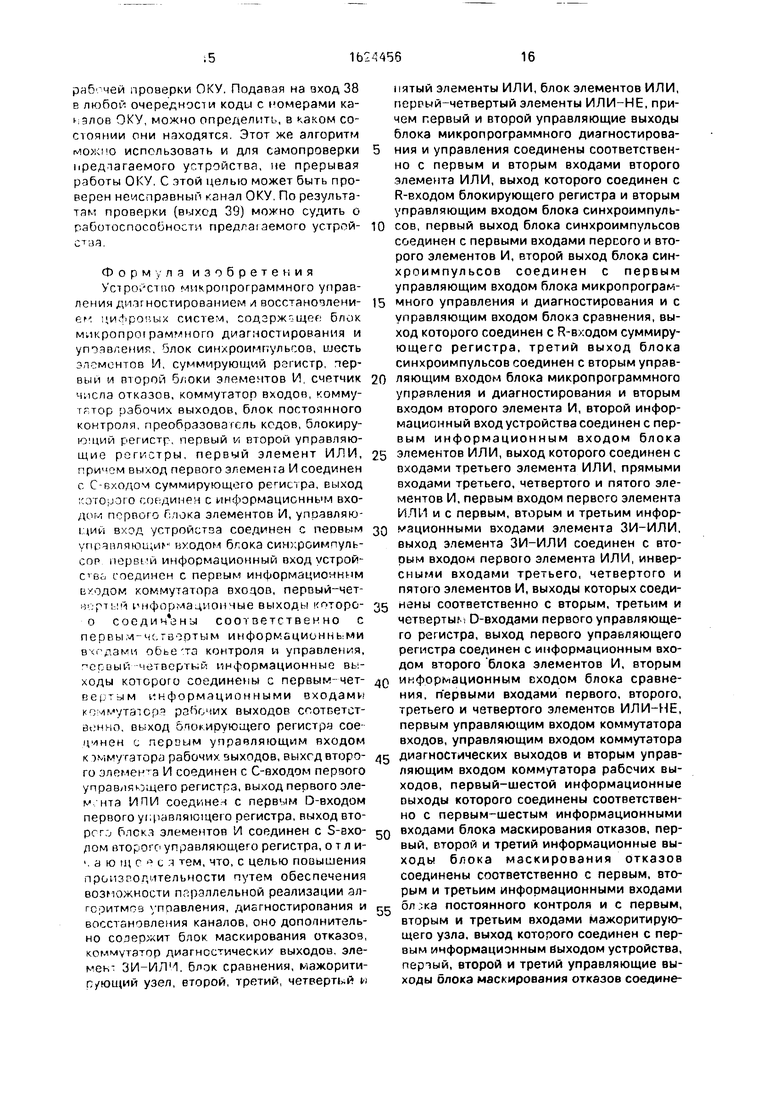

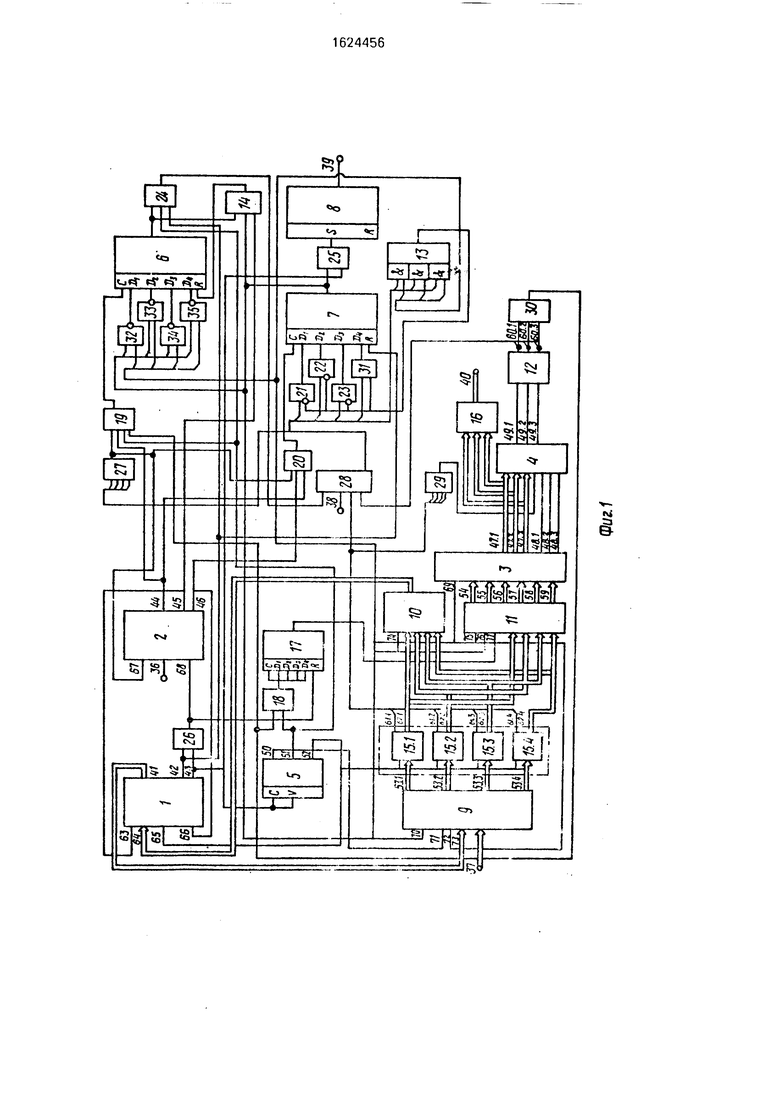

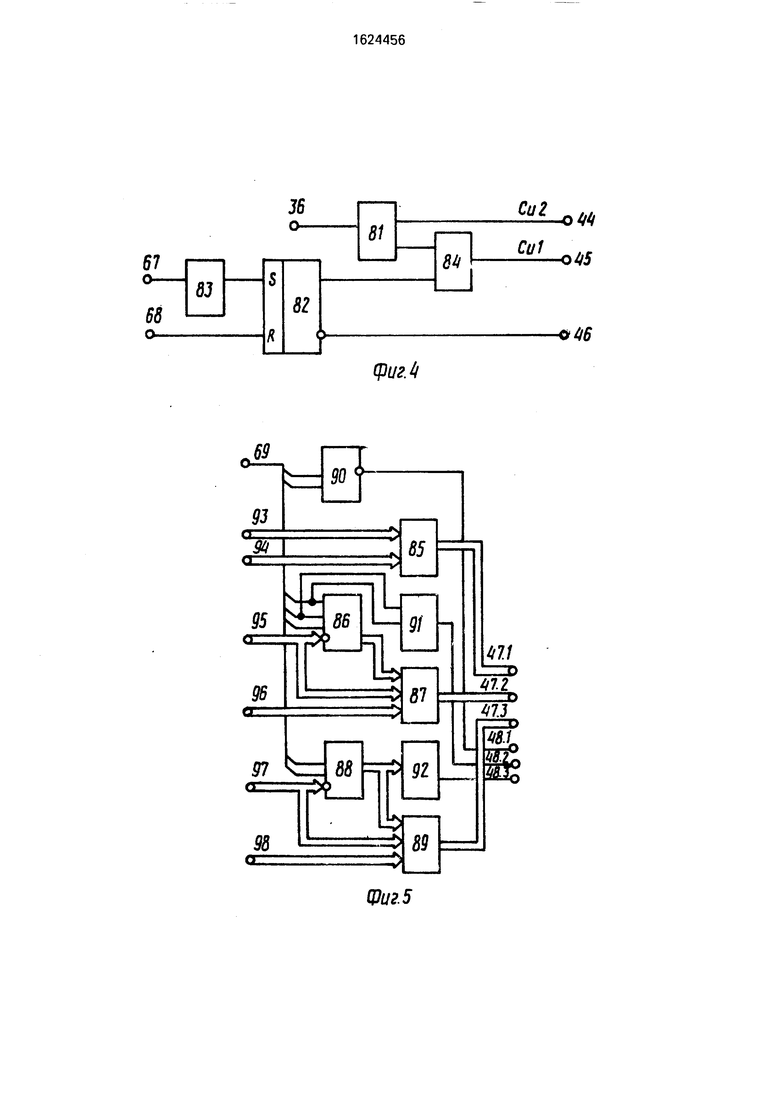

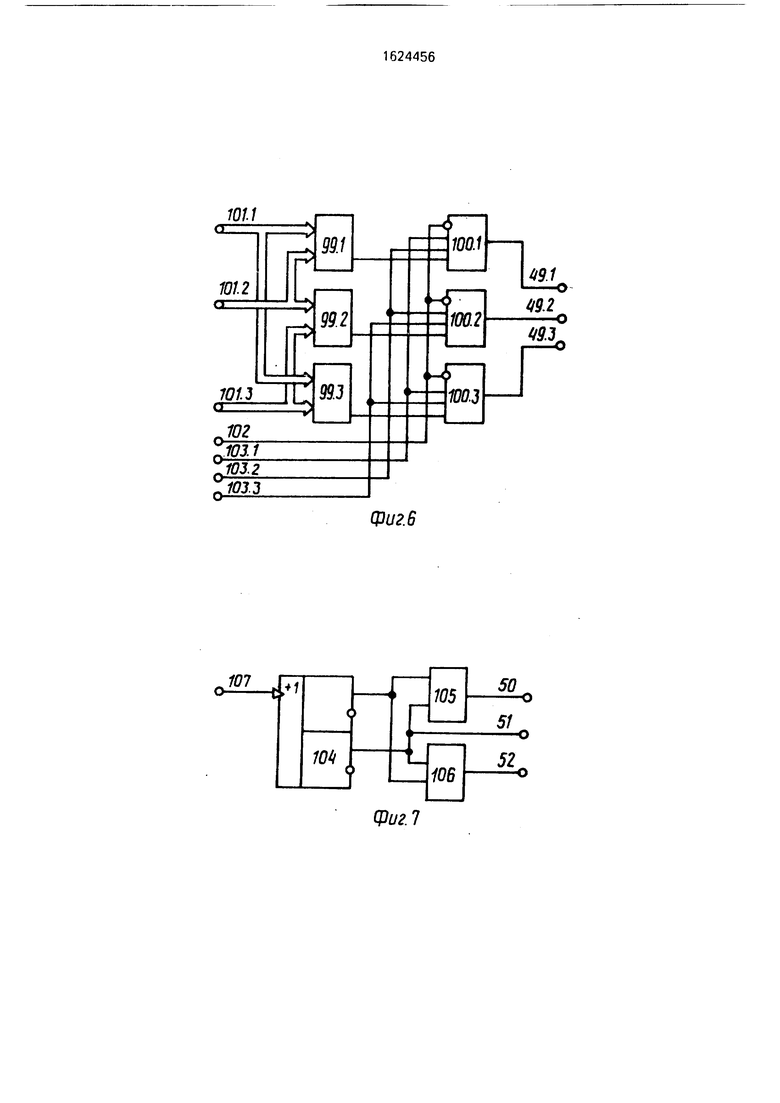

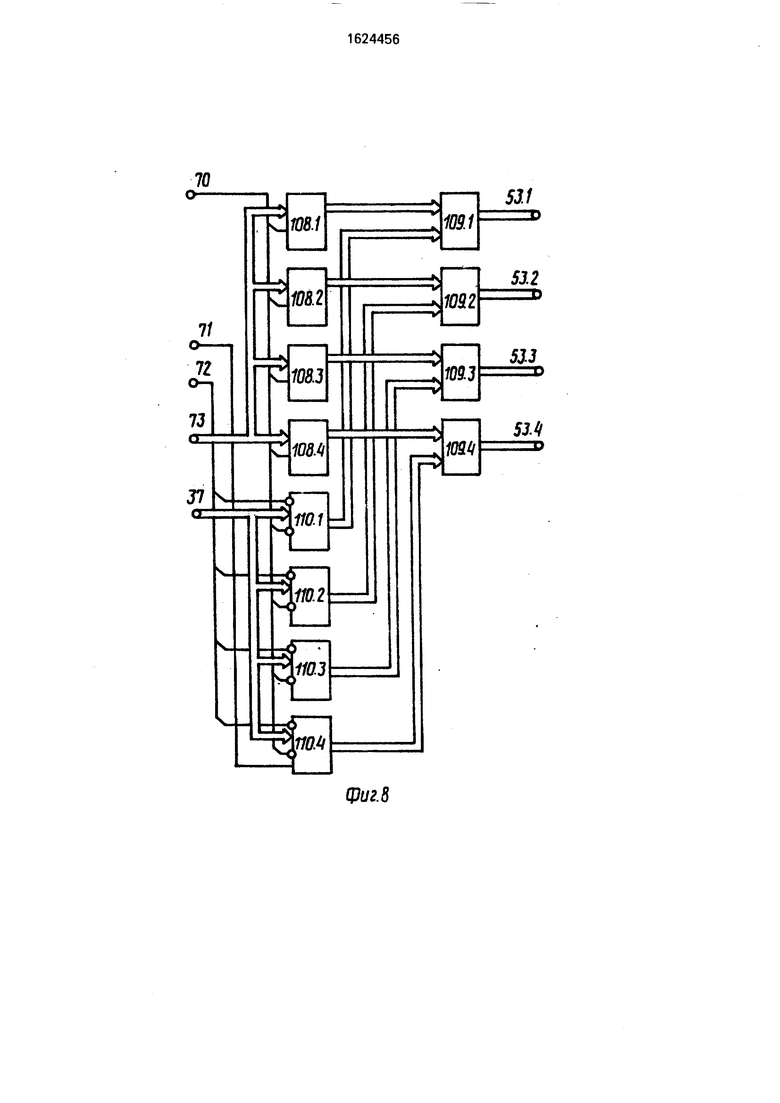

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - блок-схема алгоритма работы устройства; на фиг.З - функциональная схема блока микропрограммного диагностирования и управления (МПДиУ); на фиг.4 - функциональная схема блока синхроимпульсов; на фиг.5 - функциональная схема блока маскирования отказов; на фиг.6 - функциональная схема блока пос оянного контроля; на фиг.7 - функциональная схема счетчика числа отказов; на фиг,8 - функциональная схема коммутатора

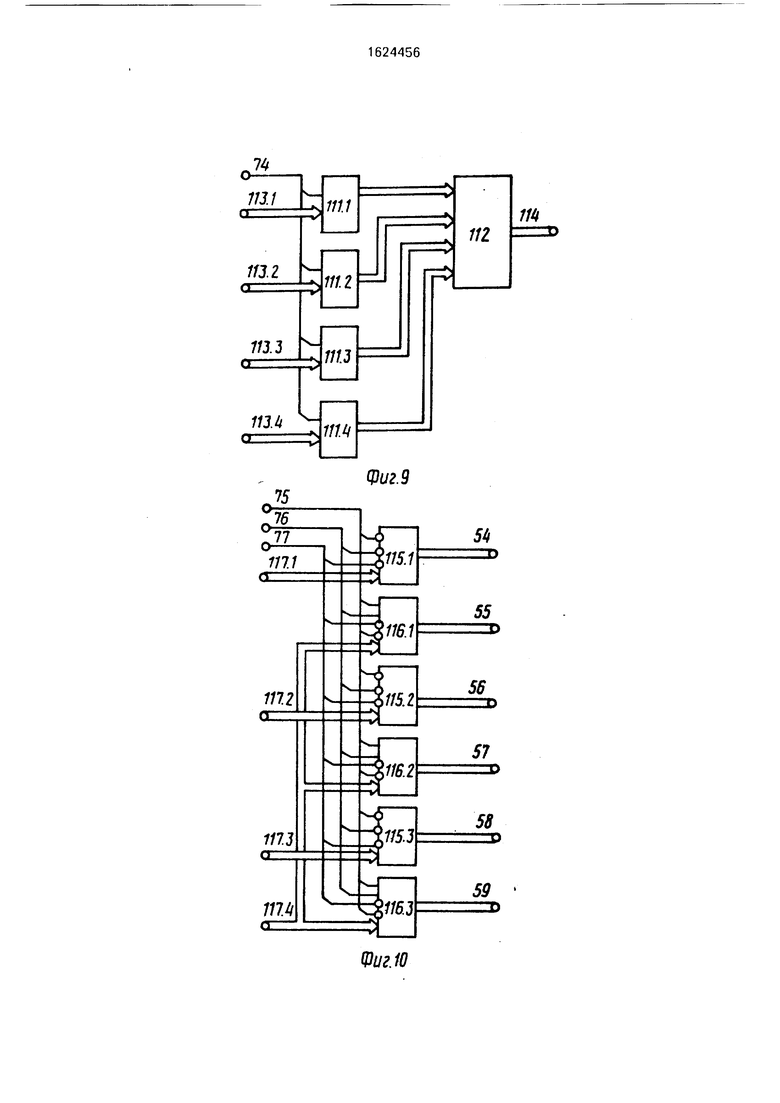

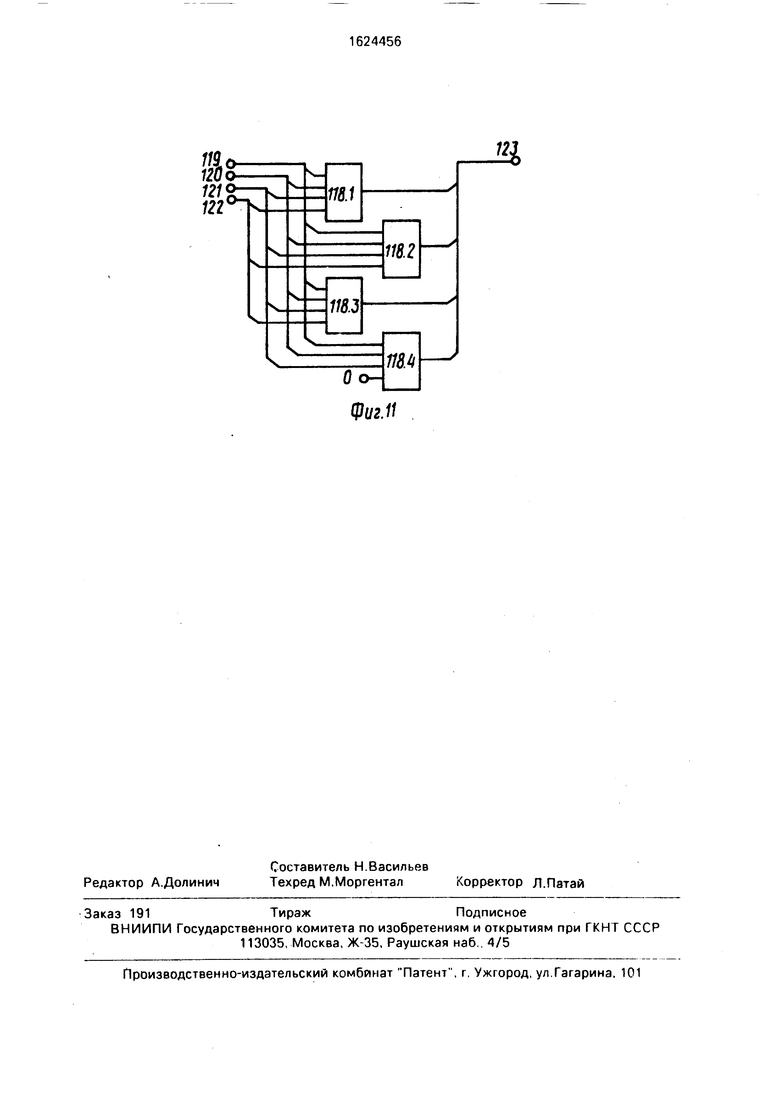

входов; на фиг.9 - функциональная схема коммутатора диагностических выходов; на фиг.10 - Функциональная схема коммутатора рабочих выходов; на фиг. 11 - функциональная схема блока элементов ИЛИ.

Устройство микропрограммного управление диагностированием и восстановлением цифровых систем (фиг.1) содержит блок 1 МПДиУ, блок 2 синхроимпульсов, блок 3 маскирования отказов, блок 4 постоянного контроля, счетчик 5 числ; отказов, суммиру- ющий регистр 6 , первьл управляющий регистр 7, второй управляющий регистр 8, коммутатор 9 входов, коммутатор 10 диагностических выходов, коммутатор 11 рабочих выходов, преобразователь 12 кодов, элемент ЗИ--ИЛИ 13, блок 14 сравнения, обьект контроля и управления (ОКУ), состоящий из четырех идентичных каналов 15.1, 152, 15.2 и 15.4, мэжоритирующий узел 16, блокирующий регистр 17, шестой элемент И 18, первый элемент И 19, второй элемент И 20, третий 21, четвертый 22, пятый 23 элементы И, первый 24, второй 25 блоки элементов 11, второй 26. третий 27 элементы ИЛИ, блок 28 элементов ИЛИ, пятый элемент ИЛИ 29, четвертый 30, первый 31 элементы И ПИ, первый 32, второй 33, третий 34, четвертый 35 элементы ИЛИ-НЕ Кроме того, на фиг.1 использованы следующие обозначения. 35 - первый управляющий вход устройства. 37 - первый информационный вход устоойсгш. 38 - второй информационный вход устройстве, 39 - второй информационный пыход устройства, 40 - первый информационный выход устройства, 41 - информсщионный выход блока 1 МПДиУ, 42 - первый управляющий выход блокг- 1 МПДиУ, 43 - второй управляющий выход блокл 1 МПДиУ, 44, 45, 46 - соответственно пеовый, агорой, третий управляющие вь одь, блока 2 синхроимпульсов. 47.1, 47.2, 47.3 - соо- ветственне первый, зторой, третий информационные выходы блоки 3 маскирования отказов, 48.1, 48.2, 48.J - соответственно первый второй, третий управляющие выходы блока 3 маскирования отказов 49.1, 49.2, 49.3 - соответственно первый, второй, третий выходы блока 4 по- стояннсго контссло, 50, 51. 52 - соответственно первый, второй, третий выходы счетчика 5 числа отказов, 53.1, 53.2, 53.3, 53.4 - соответственно первый, второй, третий, четвертый информационные выходы коммутатора 9 пходов, 54, 55, 56, 57, 58, 59 - coo.DGTCTeenHO первый второй,третий,четвертый, пятый, шестой информационные выходы коммутатора 11 рабочих выходов, 60 1, 60.2. 60.3 - соответственно первый, второй,третий выходы преобразователя 12

кодов, 61.1, 61.2, 61.3, 61.4 -соответственно первый, второй, третий, четвертый управляющие выходы ОКУ 62.1, 62.2, 62.3, 62.4 - соответственно первый, второй, третий, четвертый информационные выходы ОКУ, 63 - первый управляющий вход блока 1 МПДиУ, 64 - информационный вход блока 1 МПДиУ, 65, 66 - соответственно третий и второй управляющие входы блока 1 МПДиУ, 67, 68 0 соответственно третий и второй управляющие входы блока 2 синхроимпульсов, 69 - управляющий вход блока 3 маскирования отказов, 70,71, 72 - соответственно первый, второй, третий управляющие входы комму5 татора 9 входов, 73 - второй информационный вход коммутатора 9 входов, 74 - управляющий вход коммутатора 10 диагностических выходов, 75, 76, 77 - соответственно третий, второй, первый управляющие

0 входы коммутатора 11 рабочих выходов.

Блок 1 МПДиУ (фиг.З) содержит блок 78 памяти, регистр 79 адреса и регистр 80 тестов.

Блок 2 синхроимпульсов (фиг,4) содер5 жит генератор 81 синхроимпульсов, триггер 82 управления, элемент 83 задержки, элемент И 84.

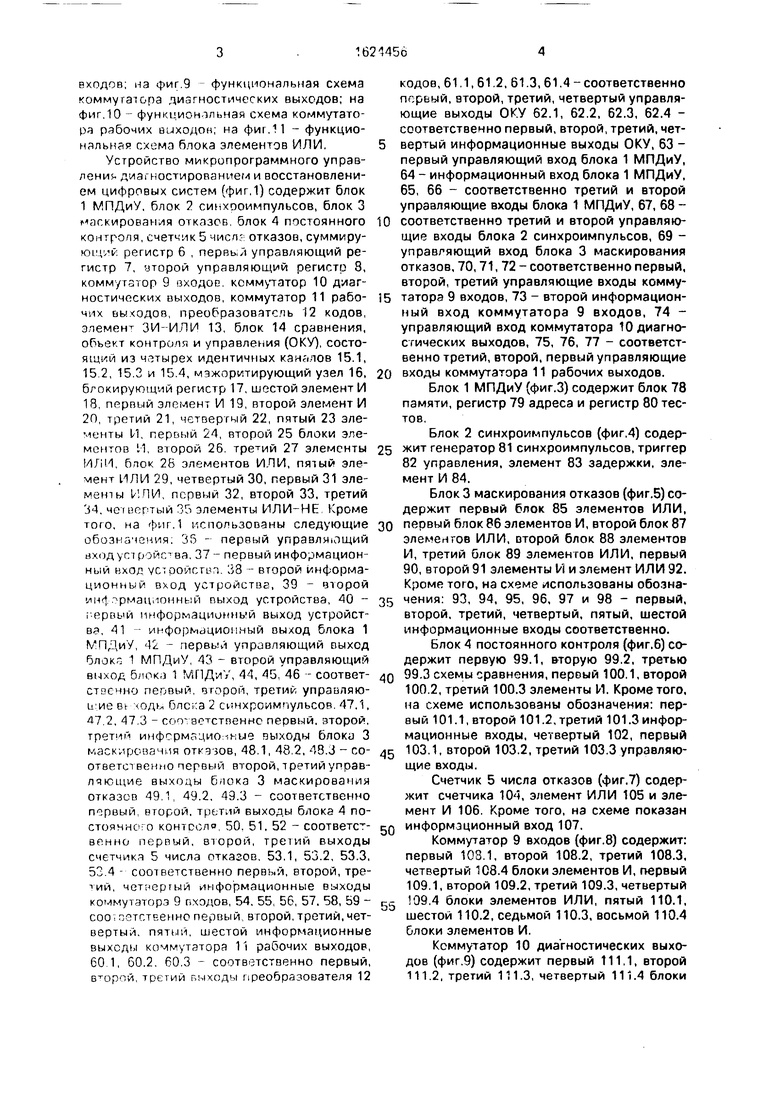

Блок 3 маскирования отказов (фиг.5) содержит первый блок 85 элементов ИЛИ,

0 первый блок 86 элементов И, второй блок 87 элементов ИЛИ, второй блок 88 элементов И, третий блок 89 элементов ИЛИ, первый 90, второй 91 элементы И и элемент ИЛИ 92. Кроме того, на схеме использованы обоэна5 чения: 93, 94, 95, 96, 97 и 98 - первый, второй, третий, четвертый, пятый, шестой информационные входы соответственно.

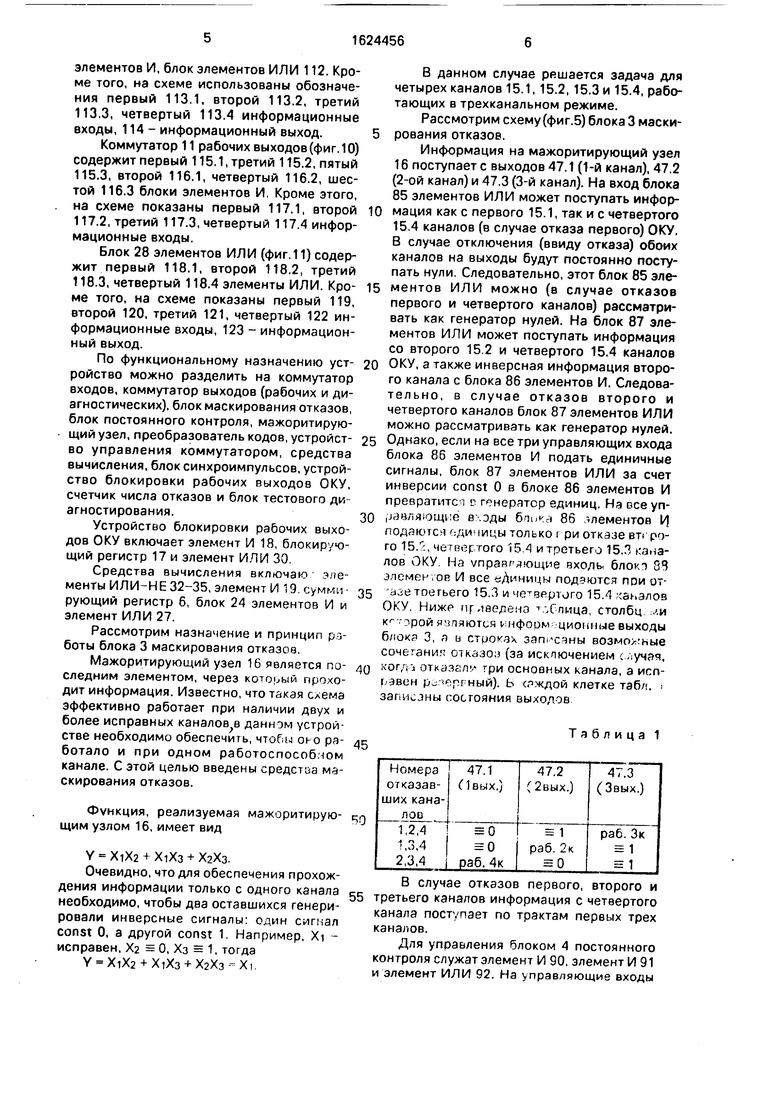

Блок 4 постоянного контроля (фиг.6) содержит первую 99.1, вторую 99.2, третью

0 99.3 схемы сравнения, первый 100.1, второй 100.2, третий 100.3 элементы И. Кроме того, на схеме использованы обозначения: первый 101.1, второй 101.2, третий 101.3 информационные входы, четвертый 102, первый

5 Ю3.1, второй 103.2, третий 103.3 управляющие входы.

Счетчик 5 числа отказов (фиг.7) содержит счетчика 104, элемент ИЛИ 105 и элемент И 106. Кроме того, на схеме показан

0 информационный вход 107.

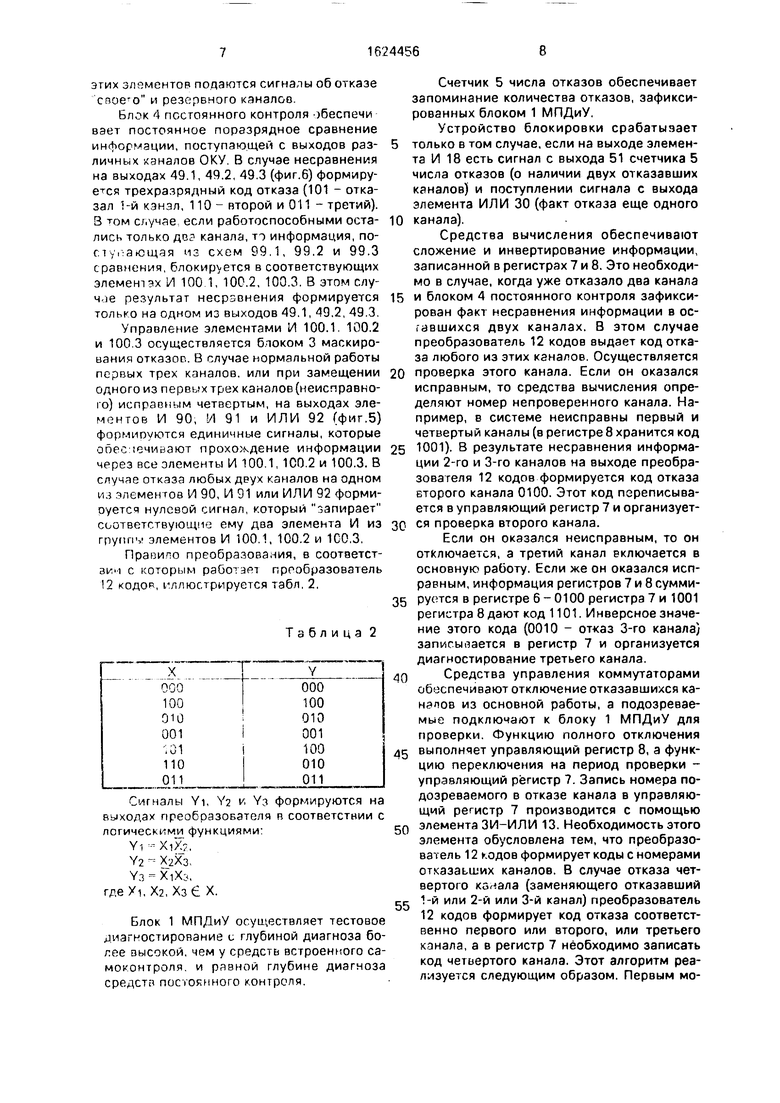

Коммутатор 9 входов (фиг.8) содержит: первый 108.1, второй 108.2, третий 108.3, четвертый 1С8.4 блоки элементов И, первый

109.1,второй 109.2, третий 109.3, четвертый 5 09,4 блоки элементов ИЛИ, пятый 110.1,

шестой 110.2, седьмой 110.3, восьмой 110.4 блоки элементов И.

Коммутатор 10 диагностических выходов (фиг.9) содержит первый 111,1, второй

111.2,третий 111.3, четвертый 111.4 блоки

элементов И, блок элементов ИЛИ 112. Кроме того, на схеме использованы обозначения первый 113.1, второй 113.2, третий 113,3, четвертый 113.4 информационные входы, 114 - информационный выход.

Коммутатор 11 рабочих выходов (фиг. 10) содержит первый 115.1, третий 115.2, пятый 115.3, второй 116.1, четвертый 116.2, шестой 116.3 блоки элементов И. Кроме этого, на схеме показаны первый 117.1, второй

117.2,третий 117.3, четвертый 117.4 информационные входы.

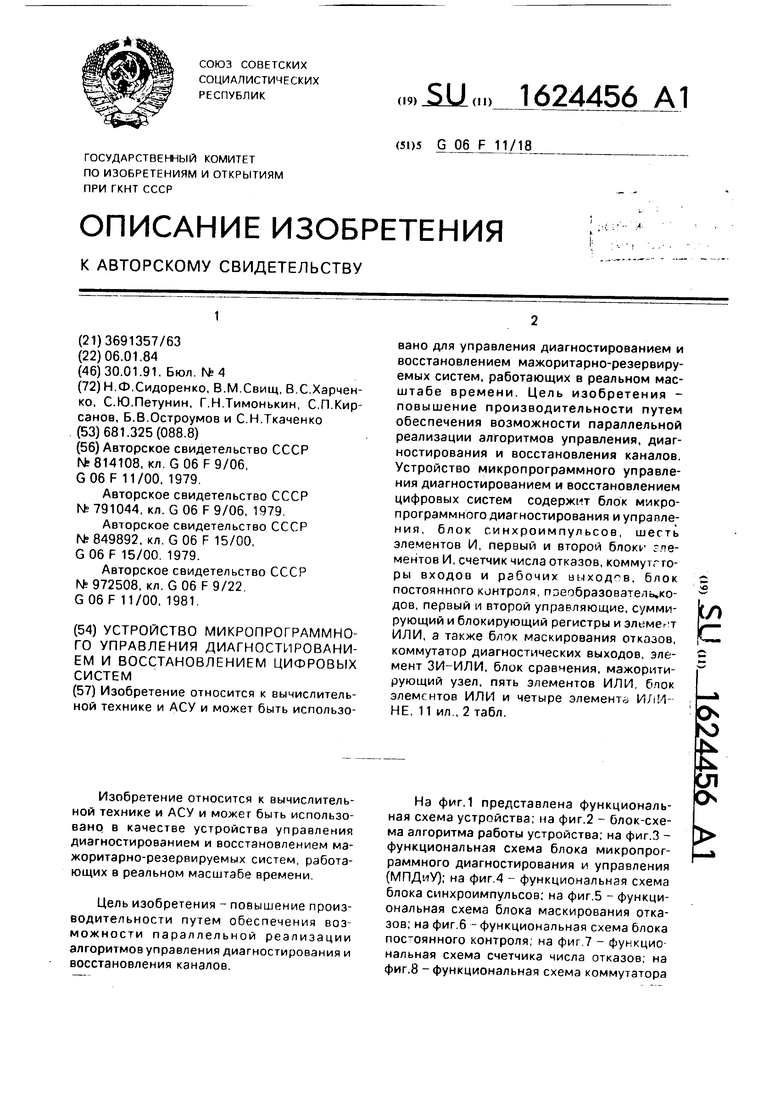

Блок 28 элементов ИЛИ (фиг.11) содержит первый 118.1, второй 118.2, третий

118.3,четвертый 118.4 элементы ИЛИ. Кроме того, на схеме показаны первый 119, второй 120, третий 121, четвертый 122 информационные входы, 123 - информационный выход.

По функциональному назначению устройство можно разделить на коммутатор входов, коммутатор выходов (рабочих и диагностических), блок маскирования отказов, блок постоянного контроля, мажоритирую- щий узел, преобразователь кодов, устройство управления коммутатором, средства вычисления, блок синхроимпульсов, устройство блокировки рабочих выходов ОКУ, счетчик числа отказов и блок тестового диагностирования.

Устройство блокировки рабочих выходов ОКУ включает элемент И 18, блокирующий регистр 17 и элемент ИЛИ 30,

Средства вычисления включаю - элементы ИЛИ-НЕ 32-35, элемент И 19, сумми - рующий регистр 6, блок 24 элементов И и элемент ИЛИ 27.

Рассмотрим назначение и принцип работы блока 3 маскирования отказов.

Мажоритирующий узел 16 является последним элементом, через который проходит информация. Известно, что такая схема эффективно работает при наличии двух и более исправных каналов в данном устройстве необходимо обеспечить, чтобы ою работало и при одном работоспособном канале. С этой целью введены средства маскирования отказов.

Функция, реализуемая мажоритирую- щим узлом 16, имеет вид

Y XiX2 + XiXa + Х2Хз.

Очевидно, что для обеспечения прохождения информации только с одного канала необходимо, чтобы два оставшихся генерировали инверсные сигналы: один сигнал const 0, а другой const 1. Например, Xi - исправен, Ха 0, Хз 1. тогда

Y XiX2 + XiX3 + X2X3-X.

В данном случае решается задача для четырех каналов 15.1, 15.2, 15.3 и 15.4, работающих в трехканальном режиме.

Рассмотрим схему (фиг.5) блока 3 маски5 рования отказов.

Информация на мажоритирующий узел 16 поступаете выходов47.1 (1-й канал), 47.2 (2-ой канал) и 47.3 (3-й канал). На вход блока 85 элементов ИЛИ может поступать инфор0 мация как с первого 15.1, так и с четвертого 15.4 каналов (в случае отказа первого) ОКУ. В случае отключения (ввиду отказа) обоих каналов на выходы будут постоянно поступать нули. Следовательно, этот блок 85 эле5 ментов ИЛИ можно (в случае отказов первого и четвертого каналов) рассматривать как генератор нулей. На блок 87 элементов ИЛИ может поступать информация со второго 15.2 и четвертого 15.4 каналов

0 ОКУ, а также инверсная информация второго канала с блока 86 элементов И. Следова- тельно, в случае отказов второго и четвертого каналов блок 87 элементов ИЛИ можно рассматривать как генератор нулей.

5 Однако, если на все три управляющих входа блока 86 элементов И подать единичные сигналы, блок 87 элементов ИЛИ за счет инверсии const 0 в блоке 86 элементов И превратитс 1 с генератор единиц. На все уп0 (-(сселяющие бтик-1 86 элементов И. подаются г:дичицы только i ри отказе втгро- го 15.г ., четвертого 15.4 и третьего 15.3 каналов ОКУ, На управляющие входь- блокт 84 элемеи.ов И все единицы подаются при от5 азетоегьего 15.3 и четвертого 15.4 каналов ОКУ, Ниже пгиведенз т:Спица, столбц кг -трой являются шфоом ционные выходы блок 3, а в возможные сочетания отказов (за исключением случая,

0 хог/1 -i отказала гри основных канала, а исправен р чергный). Ь клетке таб/s. записдны состояния выходов

45

Таблица 1

В случае отказов первого, второго и третьего каналов информация с четвертого канала поступает по трактам первых трех каналов.

Для управления блоком 4 постоянного контроля служат элемент И 90, элемент И 91 и элемент ИЛИ 92. На управляющие входы

этих элементов подаются сигналы об отказе спое о и резервного каналов.

Блок 4 постоянного контроля обеспечи вает постоянное поразрядное сравнение информации, поступающей с выходов различных каналов ОКУ. В случае несравнения на выходах 49.1, 49.2, 49.3 (фиг.6) формиру- ется трехразрядный код отказа (101 - отказал Ьй кэнэл, 110 - второй и 011 - третий). 3 том случае если работоспособными остались только дсэ канала, т информация, по- глугающая из схем 99.1, 99.2 и 99.3 сравнения, блокируется в соответствующих элементах I/I 100 1, 100.2, 100.3. В этом случае результат несрзвнения формируется только на одном из выходов 49.1, 49,2, 49.3. Управление элементами И 100.1. 100.2 и 100.3 осуществляется блоком 3 маскирования отказог,. В случае нормальной работы первых трех каналов, или при замещении одного из первых трех каналов (неисправного) исправным четвертым, на выходах элементов И 90, И 91 и ИЛИ 92 (фиг.5) формируются единичные сигналы, которые обес ечмвают прохождение информации через все элементы И 100.1, 100.2 и 100.3. В случае отказа любых двух каналов на одном из элементов И 90, И 91 или ИЛИ 92 форми- оуетсч нулевой сигнал, который запирает соответствующие ему два элемента И из группу элементов И 100.1, 100.2 и 1СО.З,

Правило преобразования, в соответствии с которым работает преобразователь 2 кодок, иллюстрируется табл. 2.

Таблица 2

Сигналы YI, N 2 и, УЗ формируются на выходах преобразователя в соответствии с логическим функциями

Yi - XiX.

Y2 - Х2Х3,

Y3 XiX;, гдеУ1,Х2, Хз€ X.

Блок 1 МПДиУ осуществляет тестовое диагностирование и глубиной диагноза более высокой, чем у средств встроенного самоконтроля, и равной глубине диагноза средств постоянного контроля.

Счетчик 5 числа отказов обеспечивает запоминание количества отказов, зафиксированных блоком 1 МПДиУ.

Устройство блокировки срабатыэает

только в том случае, если на выходе элемента И 18 есть сигнал с выхода 51 счетчика 5 числа отказов (о наличии двух отказавших каналов) и поступлении сигнала с выхода элемента ИЛИ 30 (факт отказа еще одного

0 канала).

Средства вычисления обеспечивают сложение и инвертирование информации, записанной в регистрах 7 и 8. Это необходимо в случае, когда уже отказало два канала

5 и блоком 4 постоянного контроля зафиксирован факт несравнения информации в оставшихся двух каналах. В этом случав преобразователь 12 кодов выдает код отказа любого из этих каналов. Осуществляется

0 проверка этого канала. Если он оказался исправным, то средства вычисления определяют номер непроверенного канала. Например, в системе неисправны первый и четвертый каналы (в регистре 8 хранится код

5 1001). В результате несравнения информации 2-го и 3-го каналов на выходе преобразователя 12 кодов формируется код отказа второго канала 0100. Этот код переписывается в управляющий регистр 7 и организуетС ся проверка второго канала.

Если он оказался неисправным, то он отключается, а третий канал включается в основную работу. Если же он оказался исправным, информация регистров 7 и 8 сумми5 руется в регистре 6-0100 регистра 7 и 1001 регистра 8 дают код 1101. Инверсное значение этого кода (0010 - отказ 3-го канала) запиты дается в регистр 7 и организуется диагностирование третьего канала.

9 Средства управления коммутаторами обеспечивают отключение отказавшихся каналов из основной работы, а подозреваемые подключают к блоку 1 МПДиУ для проверки. Функцию полного отключения

5 выполняет управляющий регистр 8, а функцию переключения на период проверки - управляющий регистр 7. Запись номера подозреваемого в отказе канала в управляющий регистр 7 производится с помощью

Q элемента ЗИ-ИЛИ 13, Необходимость этого элемента обусловлена тем, что преобразователь 12 кодов формирует коды с номерами отказаьших каналов. В случае отказа четвертого канала (заменяющего отказавший

е 1-й или 2-й или 3-й канал) преобразователь 12 кодов формирует код отказа соответственно первого или второго, или третьего канала, а в регистр 7 необходимо записать код четвертого канала. Этот алгоритм реализуется следующим образом. Первым может отказать любой из трех первых каналов 15.1, 15.2, 15.3 (4-й канал 15.4 в резерве). Например, отказал третий канал, тогда после диагностирования и подтверждения факта отказа, его номер (код 0010) будет записан в управляющий регистр 8. После переключений его место займет четвертый канал. При отказе четвертого канала (замещающего третий) на выходе преобразователя 12 кодов сформируется код 001. Этот код будет подан на входы элемента ЗИ-ИЛИ 13. На входе его третьего элемента И единица третьего разряда кода и единица третьего разряда с выходов управляющего регистра 8 позволяет сформировать единицу на выходе элемента ЗИ-ИЛИ 13, которая блокирует 1 - 3-й входы управляющего регистра 7 и будет записана в четвертый разряд, т.е. в регистр 7 будет записан код 0001.

Алгоритм работы устройства (фиг.2) сводится к следующему.

Когда в ОКУ исправны все четыре канала, первые три выполняют возложенные на них функции, а четвертый находится в горячем резерве. Средства встроенного самоконтроля ОКУ и средства постоянного контроля проводят постоянный контроль состояния каналов ОКУ. При ненорме одного из каналов происходит отключение подозреваемого канала из основной работы и подключение его к блоку 1 МПДиУ, который осуществляет тестирование этого канала. При этом мажоритирующий узел 16 обеспечивает выдачу верной информации. При норме тестирования по команде блока 1 МПДиУ проверяемый канал подключается в основную работу, а при подтверждении ненормы происходит его полное отключение и ОКУ продолжает работу в трехканалькоп структуре.

Работа ОКУ в трехканальной струк(ург аналогична описанной выше. При отказе одного из каналов (и подтверждении отказа блоком МПДиУ) происходит отключение отказавшего канала. Одновременно блок 3 ма- скирования отказов обеспечивает блокировку части средств постоянного контроля, на которые попадает информация с отказавшего блока.

При двухканальной структуре предлагаемое устройство работает следующим образом.

При фиксации ненормы средствами встроенного самоконтроля ОКУ происходит отключение подозреваемого канала и его проверка. При фиксации ненормы средствами постоянного контроля происходит отключение обоих оставшихся каналов. Проверяется первый из них (любой ио заданному алгоритму). В случае нормы проверок он включается в основную работу и происходит проверка второго канала, в случае ненормы первый канал отключается, а второй без проверки включается в основную 5 работу. При норме проверок первого и второго каналов он продолжает основную работу, а при отказе второго он отключается из основной работы и схема ОКУ переходит к одноканальной структуре. При этом отклю- 10 чаются средства постоянного контроля, а средства маскирования отказов обеспечивают прохождение верной информации с оставшегося одного канала через мажоритирующий узел 16. Также происходит за- 15 грубление точности средств встроенного самоконтроля ОКУ и диагностических процедур до той величины, при которой ОКУ еще может выполнять основные функции.

Рассмотрим принцип функционирова- 0 ния устройства.

Перед началом работы все элементы памяти приводятся в исходное состояние (цепи установки в исходное состояние на схеме не показаны).

5В случае определения отказа средствами встроенного самоконтроля информация о номере отказавшего канала через блок 28 элементов ИЛИ открытые элементы И 21, 22 23 и элимочт ИЛИ 31 поступает по входы 0 управляющего регщтря 7. Одновременно информант, с вухолог илпкт 28 acCMCf oj ИЛИ н-т м IBMPHT ИЛ 1 27. -д -тч- ный ГИ| hm с F - J/з элс,,м 1:г-1 ГЛИ Г н- чр ваот элемент И 2.1, обсспечир я 5 самым пропуск отмсгосш оог.мпульсг Си v), негбхо; i/нг.го /in- тщс 1 орм ;ии л уп- рэнлг.у -ции р,:гисГ| / Сд-. мчнии сигнал выходя э.емзнтя Л1 / 2 поступает гг же на в/од ллемента .3 . (фиг А) г тока Q 2 синхроимпульсов, гремь задос жки TI элемегга 83 задержки пибкраогся, о- дя из ьрег. они проведения коммутации управляющим регистром 7. Информация о номере канала, которой необходимо отклю 5 чить от основной работы и подключить к блоку 1 МПДи поступает с выходов - прав- ляю цего регистра 7 t,j вход 70 (фиг & ыутагора 9 входов, вход 74 (фиг.Э) коммутаторе 10 диагностических выходов и О вход 76(фиг. 10) коммутатора 11 рабочих выходов. После выполнения перекоммутации через время п срабатывает триггер 82 (фиг.4), запирая сигналом со своего инверсного выхода элемент И 20 на время тестово- 5 го диагностирования (это необходимо для того, чтобы информация о других от казах не была записана в управляющий регистр 7). Своим прямым выходом триггер 82 обеспе прохождение СИ 1 через элемент И 84 в блок 1 МПДиУ (фиг 3, вход 63). С приходом перяого синхроимпульса начинается процесс тестового диагностирования, окончание котсроп определяется наличием единицы а поле N или N регистра 80 тестов (фиг.З), что соответствует норме или ненор- ме диагностирования.

Рассмотрим случай нормы проверок. Сигнал нормы поступает на R-вход регистра 7 и приводит его в исходное состояние. В результате в исходное состояние приходят и нее коммутаторы, возвращая тем самым ОгчУ в исходное состояние (с точки зрения структуры ОКУ). Кроме описанного, сигнал нормы поступает на R-вход триггера 82, привод его Р исходное состояние. В результате закрывается элемент И 84 (прекращаетеа пропуск СИ 1) и открывается элемент И 20, подготавливая тем самым тракт к записи информации о с/.едующем отказе.

При появлении в одном из каналов ин- формации, отличной от информации других двух каналов, на выходах тех схем сравнена куда эта (неверная) информация поступает, формируются единичные сигналы. Так, в случае искажения инфоомации во вто- ром канале единицы сформируются на выходах схем 99.1 и 99.2 сравнения (фиг.6), т.е. сформируется код 110. Эта информация через открытые элементы И 100,1, 100.2 поступит на вход преобразователя 12 кодов, где Ьудтг преобразована в код 010. Этот код чррог. о гж 2G элеметов ИЛИ поступает на РХОД -элемента ИЛИ 27. Далее происходит з р е ч о м м у т а ц и я, включение блока I МПДиУ и тестирование второго канала Рас- смотрим Счэ примеос: второго канала), как .,водится подклпчение канала на тес- тироьание. Злпис ный в управляющем р- гистре 7 код 0100 поступает через управ- гп-ощ| Г в/од 70 (фиг,8) в коммутатор 9 вхо- доз В результгле открывается бло с 108.2 этементог И и .акгывтется блок 110.2 элементов И. Этот же кол поступает на коммутатор 10 диагностических выходов (фиг.9) через вход 74 и открывает блок 111.2 эле- И. Аналогичным образом в коммутаторе 11 рабочих выходов (фиг.10) закрывается блок 1152 элементов И.

После перекоммутации проходит про- цегс диагностирования. Пусть в результате диагностирования выяснится факт отказа второго канала. Тогда я поле N регистра 80 тестов (фиг.З) появится единица, которая через элемент ИЛИ 26 поступит на R-вход триггера 82 и приведет его в исходное со- стояние. В результате прекратится процесс диагностирования и подготовится к работе эл мент И 20. Единица с поля N регистра 80 тестоз будет подана также на управляющий вх ;д блока 25 элементов И и на в од счетчика (Фиг,7). Единиц с выхода 50 счетчика

5 числа отказов через управляющий вход 71 (фиг.З) коммутатора 9 входов поступит на вход блока 110.4 элементов И и подключит входы четвертого канала 15.4 ОКУ. Одновременно единица, поступившая на управляющий вход блока 25 элементов И, обеспечит запись информации (код 0100) с выходов управляющего регистра 7 в управляющий регистр 8. Код. записанный в управляющий регистр 8, поступит на управляющий вход 72 (фиг.8) коммутатора 9 входов, управляющий вход 75 (фиг. 10) коммутатора 11 рабочих выходов и на управляющий вход 69 (фиг.5) блока 3 маскирования отказов. В результате в коммутаторе 9 входов будет закрыт блок 110.2 элементов И (отключение входов второго канала 15.2) в коммутаторе 11 рабочих выходов будет закрыт блок 115.2 элементов И (отключение выходов второго канала 15.2) и открыт блок 116.2 элементов И (подключение выходов четвертого канала 15.4); в блоке 3 маскирования отказов подготавливается к работе блок 86 элементов И (фиг,5).

Таким образом, выявленный отказ второго канала привел к его отключению и замене четвертым каналом.

Работа устройства при наличии трех исправных каналов ОКУ аналогична описанной. Отличие имеется лишь при фиксации факта отказа и в том случае, когда отказ четвертого канала фиксируется средствами постоянного контроля. Рассмотрим этот случай. При искажении информации в четвертом канале 15.4 (замещающем второй) средства постоянного контроля блока 4 выдадут в преобразователь 12 код 110, который будет преобразован к виду 010. Этот код через блок 28 элементов ИЛИ поступит на входы элементов ИЛИ 27, И 21, И 22, И 23, ИЛИ 31 и ЗИ-ИЛИ 13. Кроме того, на других входах элемента ЗИ-ИЛИ 13 находится информация с первых трех разрядов управляющего регистра 8 - код 010. В результате наличия во вторых разрядах обоих кодов единицы на выходах элемента ЗИ- -ИЛИ 13 будет сформирована единица, которая закроет элементы И 21, И 22 и И 23, а через элемент ИЛИ 31 будет подана на вход D4, управляющего регистра 7 и записана в него с приходом синхроимпульса СИ 2 с выхода 44 Слока 2 синхроимпульсов через элемент И 20. Таким образом, в управляющий регис.р 7 будет записан код 0001, что соответствует отказу четвертого канала 15.4. После этого по описанному алгоритму происходит отключение четвертого канала и его тестирование, В случае нормы тестирования происходит обнуление регистра 7 и схема ОКУ приводится к исходной, трехка- нальной структуре. При фиксации блоком 1

МПДиУ факта отказа происходит запись информации из регистра 7 в регистр 8 и запись еще одной единицы в счетчик 5 числа отказов. Появление единицы на втором выходе счетчика 5 числа отказов обеспечивает подготовку к работе элемента И 19, элемента И 18 и блока 24 элементов И. Информация с выхода управляющего регистра 8 поступает на коммутаторы 9 и 11 входов и рабочих выходов, где производится отключение отказавшего (в рассматриваемом примере четвертого) канала, а также в блок 3 маскирования отказов, где происходит операция по маскированию отказов. В рассматриваемом примере на выходе элемента И 91 (фиг.5) формируется единица, которая поступает на инверсные входы элементов И 100.1 и 100.2 (фиг.6) и закрывает их, тем самым из блока 4 постоянного контроля через открытый элемент И 100 3 будет проходить информация о результатах сравнения первого и третьего каналов

Работа устройства с двумя исправными каналами. При несравнении информации з блоке 4 постоянного контроля преобразователь 12 кодов формирует на своих выходах код отказа одного из них В результате на выходе элемента ИЛИ 30 формируется единица, которая «ерез открытый элемент И 18 записывается в блокируюи ни регистр 17 Информация с выходов блог npyi ЗЩРГО регистра 17 поступает на коммутатор 1 i рабочих выходов и отключает выходы всех каналов Одновременно код с выхода преибрэчона- теля 12 кодов (в рассматриваемом пр -мери 001) через блок 28 элементов ИЛИ io синхроимпульсу СИ 2 записывается в упр п щий регистр 7. Кроме то о, по синхроимпульсу СИ 2 проис/ОА1 т запись информации из управляющих регистров 7 и 8 через элементы ИЛИ-НЕ , уммируюи регистр 6 (в рассматриваемом примере в регистр 6 записываются коды 0100- и 1001) Таким образом, в суммирующий регистр С- записывается код второго из подозреваемых в отказе каналов (в рассма ривае юм примере 0010). Через т (nouie перекоммутации) происходит процесс тестового диагностирования При любом исходе диа(- ностиоования происходи г обнуление С лги и- рующего регистра 17.

При ненорме проверок единичный сигнал N с выхода регистра 80 тестов обеспечивает перезапись информации из регистра 7 в регистр 8 (открывает блок 25 элементов И) и устройство переходит в одноканальный режим работы Кроме того, сигнал N привс дит в исходное состояние блок 2 синхроимпульсов, а также увеличивает на единицу содержимое счетчика 5 числа отказгв

Сформированная таким образом единица на третьем выходе счетчика 5 числа отказов производит отключение блока 4 постоянного контроля (вход 102, фиг.6) и переводит 5 блок 1 МПДиУ в режим работы по затрубленному алгоритму, т.е. производит изменение начального адреса программы диагностирования Выбранная таким образом новая программа не фиксирует факта тех отказов,

10 которые не оказывают значительного влияния на основную работу ОКУ.

При норме проверок обнуляется регистр 7 и проверенный канал включается в основную работу. Одновременно с прихо15 дом синхроимпульса СИ 2 происходит перезапись информации из суммирующего регистра 6 через открытый блок 24 элемента И, блок 28 элементов ИЛИ в управляющий регистр 7 В результате в регистрах 6 и 7

0 окажется записана одна и та же информация, которая посыпает на входы блока 14 сравнения, на выходе которого сформируется единица, которая с приходом синхроим- пупьса СИ 1 (через время, необходимое для

5 перезаписи информации из регистра 6 в регистр 7) поступит на R-вход суммирующего регистра 6 и приведет его в исходное состояние

После тог б« дег псоьид мч тес гирова

Vv Hit, то; я m,jnjfr aapMbi а В л 0рр гс-сти ова. ч тройгть е- рей.1 к (у . ,ии с еме t e глучс , ноомы ( ,i,.r,i де1 ci -оHI, / кч:, MI -о Kf- п:, i i f -a J,V будет npeof5 Раз d к однокч «-./I юй

В ту , , i ),. г.тр1ен- ными ро/ э -. он роля (г pi -ipyx nc;i- , JA н j ) инф )nf/ij 4Hfl ь( rkdj j ( f пок 2С 1 гов |ЛИ зап1, . ОУ

Q ь у о 1ЮЩИИ регистр

К о& канальной хеме ОКУ работают тгл-о BOJ JP0нныd сродства (по описанному апгопи му) При этом возможно (по

Н ОбхОДИМГС. и) ПРОИЗВОДИТЬ с.СтС ЬЫЙ КОН5 троль с меныией точностью без учета вгсро- степеннил ОкУ. /.i/w оиеспечсния этс о си|на,1 Р н ьиччц трех отказов си. темы блокирует ту сть средств встроенноеj самоконтроля, котора фиксирует указанQ нь е отказы Кроме того, этим же сип-илом оБеспьчиваегсл выбор тестовой процедуры с меньшими диагностическими юзможно- стями

Кроме описанного выше алгоритма усс тройС1ВО может работать при наличии сиг- на/,ов от внеи.иих систем. Для этого нооОходимо -. . вход 38 задать ки,г oiKasa ) ,-jriri „ и на виходе ЗР ПОЛУЧИ от- ьет icnpe-rtno оно ini-1 нег Эту EIOSMOXHUCTL можно з -, :т Jem ис тользспать Х1-1Я предрабочей проверки ОКУ. Подавая на вход 38 в любой очередности коди с номерами ка- элов ОКУ, можно определить, в каком состоянии они находятся. Этот же алгоритм момю использовать и для самопроверки предлагаемого устройства, не прерывая работы ОКУ. С этой целью может быть проверен неисправный канал ОКУ. По результатам проверки (выход 39) можно судить о работоспособности предла аемого устройCTJ3

Формула изобретения У стронет по микропрограммного управления диагностированием лвосстановлением систем, содэрж щог блок микропрограммного диагностирования и упочвг.енип, блок синхроимпульсов, шесть элементов И, суммирующий регистр, первый и торой блоки элементов И, счетчик числа отказов, коммутатор входов, комму- ггтор рабочих выходов, блок постоянного контроля, преобразователь кодов, блокиру- ю ций регистр, первый и второй управляющие регистры, первый элемент ИЛИ, причем выход первого элемента И соединен с С-входом суммирующего регистра, выход ; oro.jDro соединен с информационным входом первого Плока элементов И, упоавляю- i 4ий вход устройства соединен с первым управляющие входом блока синхроимпуль- СОР первой информационный вход устрой- ciBG соединен с первым информационным ьсодом коммутатора входов, первый-чет- в- информационные выходы которо- о соединены соответственно с первым-чс, гвоотым информационными eo vavn оЬье та контроля и управления, ссоый четвертой информационные выходы которого соединены с первым-чет- информационными входами коммутатор3 рабочих выходов соответственно, выход итерирующего регистра сое цинен с первым управляющим входом коммутатора рабочих выходов, выход второго элемента И соединен с С-входом перзого управляющего регистра, выход первого эле- м нта И ПИ соединен с первым D-входом первого yi,равняющею регистра, выход вторе го блекл элементов И соединен с S-вхо- лом второго управляющего регистра, о т л и- 1 а ю щ с с ч тем, что, с целью повышения производительности путем обеспечения возможности параллельной реализации эл- гсритмоэ управления, диагностирования и восстановления каналов, оно дополнительно солеолит блок маскирования отказов, коммутатор диагностических выходов, эле- меь- ЗИ-ИЛ 1. блок сравнения, мажорити- с/ющий узел, второй, третий, четверть-й и

пятый элементы ИЛИ, блок элементов ИЛИ, перрый-четвертый элементы ИЛИ-НЕ, причем первый и второй управляющие выходы блока микропрограммного диагностирования и управления соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с R-входом блокирующего регистра и вторым управляющим входом блока синхроимпуль0 сов, первый выход блока синхроимпульсов соединен с первыми входами персого и второго элементов И, второй выход блока син- хроимпульсов соединен с первым управляющим входом блока микропрограм5 много управления и диагностирования и с управляющим входом блока сравнения, выход которого соединен с R-входом суммирующего регистра, третий выход блока синхроимпульсов соединен с вторым управ0 ляющим входом блока микропрограммного управления и диагностирования и вторым входом второго элемента И, второй информационный вход устройства соединен с пер- вым информационным входом блока

5 элементов ИЛИ, выход которого соединен с входами третьего элемента ИЛИ, прямыми входами третьего, четвертого и пятого элементов И, первым входом первого элемента ИЛИ и с первым, вторым и третьим инфор0 мационными входами элемента ЗИ-ИЛИ, выход элемента ЗИ-ИЛИ соединен с вторым входом первого элемента ИЛИ, инверсными входами третьего, четвертого и пятого элементов И, выходы которых соеди5 иены соответственно с вторым, третьим и четвертые D-входами первого управляющего регистра, выход первого управляющего регистра соединен с информационным входом второго блока элементов И, вторым

Q информационным сходом блока сравнения, первыми входами первого, второго, третьего и четвертого элементов ИЛИ-НЕ, первым управляющим входом коммутатора входов, управляющим входом коммутатора

5 диагностических выходов и вторым управляющим входом коммутатора рабочих выходов, первый-шестой информационные выходы которого соединены соответственно с первым-шестым информационными

0 входами блока маскирования отказов, первый, второй и третий информационные выходы блока маскирования отказов соединены соответственно с первым, вторым и третьим информационными входами

с бллка постоянного контроля и с первым, вторым и третьим входами мажоритирую- щего узла, выход которого соединен с первым информационным выходом устройства, пертый, второй и третий управляющие выходы блока маскирования отказов соединены соответственно с первым, вторым и третьим управляющими входами блока постоянного контроля, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами преобразователя кодов, первый, второй и третий выходы преобразователя кодов соединены с вторым информационным входом блока элементов ИЛИ и с первым, вторым и третьим входами четвертого элемента ИЛИ, выход которого соединен с. первым входом шестого элемента И и вторым входом первого элемента И, выход второго управляющего регистра соединен с первым, вторым и третьим управляющими входами элемента ЗИ-ИЛИ, вторым информационным выходом устройства, первым управляющим входом блока маскирования отказов, третьим управляющим входом коммутатора рабочих выходов , третьим управ- ляющим входом коммутатора входов и вторыми входами первого, второго, третьего и четвертого элементов ИЛИ-НЕ, инверсные выходы которых соединены соответственно с первым-четвертым D-вхо- дами суммирующего регистра, выход суммирующего регистра соединен с вторым информационным входом блока сравнения, первый управляющий выход блока микропрограммного диагностирования и управле- ния соединен с R-входом первого управляющего регистра и первым управляющим входом первого блока элементов И, выход которого соединен с третьим информационным входом блока элементов ИЛИ, второй управляющий выход блока микропрограммного диагностирования и управления соединен с управляющим входом

второго блока элементов И и входом счетчика числа отказов, первый управляющий выход которого соединен с третьим управляющим входом коммутатора входов, второй управляющий выход счетчика числа отказов соединен с третьим входом первого элемента И, вторым управляющим входом первого блока элементов И и вторым входом шестого элемента И, выход которого соединен с С-входом и с первым-четвертым D- входами блокирующего регистра, третий управляющий выход счетчика числа отказов соединен с третьим управляющим входом блока микропрограммного диагностирования и управления и управляющим входом объекта контроля и управления, первый- четвертый управляющие выходы которого соединены с четвертым информационным входом блока элементов ИЛИ и с первым- четвертым входами пятого элемента ИЛИ, выход пятого элемента ИЛИ соединен с четвертым управляющим входом блока постоянного контроля, первый-четвертый информационные выходы объекта контроля и управления соединены соответственно с первым-четвертым информационными входами коммутатора диагностических выходов, выход которого соединен с информационным входом блока микропрограммного диагностирования и управления, информационный выход блока микропрограммного диагностирования и управления соединен с вторым информационным входом коммутатора входов, выход третьего элемента ИЛИ соединен с третьим управляющим входом блока синхроимпульсов, с третьим входом второго элемента И и с четвертым входом первого элемента И.

«О

in т «т

CN (О

W-) Щ

70

:u

ЮВ.1

5J/

109.1

JD

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1233155A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Система для программного управления резервированными объектами и их диагностирования | 1989 |

|

SU1741295A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройствоупРАВлЕНия C КОНТРОлЕМ | 1979 |

|

SU798836A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

Изобретение относится к вычислительной технике и АСУ и может быть использовано для управления диагностированием и восстановлением мажоритарно-резервируемых систем, работающих в реальном масштабе времени. Цель изобретения - повышение производительности путем обеспечения возможности параллельной реализации алгоритмов управления, диагностирования и восстановления каналов. Устройство микропрограммного управления диагностированием и восстановлением цифровых систем содержит блок микропрограммного диагностирования иупрапле- ния, блок синхроимпульсов, шесть элементов И, первый и второй блоки элементов И, счетчик числа отказов, коммутг горы входов и рабочих выходов, блок постоянного контроля, пзеобразователь.ко- дов, первый и второй управляющие, суммирующий и блокирующий регистры и элемент ИЛИ, а также блок маскирования отказов, коммутатор диагностических выходов, элемент ЗИ-ИЛИ, блок сравнения, мажорити- рующий узел, пять элементов ИЛИ, блок элементов ИЛИ и четыре элементе ИЛИ- НЕ. 11 ил., 2 табл.

ш.г

о.

-Q

0

5J2

/052

JD

«ftj

5JJ

и

ш

5J.

т. г

Они

о.

1Ш

о

т

Фиг. 9

Фиг. 10

S

Фиг.11

| Авторское свидетельство СССР М 814108, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 791044, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР Ne 849892, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Микропрограммное устройство с контролем переходов | 1981 |

|

SU972508A2 |

Авторы

Даты

1991-01-30—Публикация

1984-01-06—Подача