(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ формирования трехуровневого управляющего сигнала в релейных системах управления динамическим объектом и релейный регулятор для механизации этого способа | 1989 |

|

SU1777119A1 |

| Релейный регулятор | 1989 |

|

SU1742786A1 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2008 |

|

RU2396586C1 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2008 |

|

RU2385480C1 |

| Многопороговый релейный элемент с опережающей характеристикой | 1989 |

|

SU1629977A1 |

| Частотно-импульсный регулятор | 1985 |

|

SU1278806A1 |

| Релейный регулятор | 1979 |

|

SU857929A1 |

| Релейный регулятор | 1989 |

|

SU1695263A1 |

| Релейный регулятор | 1990 |

|

SU1836658A3 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 1999 |

|

RU2150726C1 |

Изобретение относится к технике автоматического управления. Способ формирования управляющего сигнала и релейный регулятор позволяют исключить влияние ограничения сигнала регулируемой координаты на процесс управления, уменьшить перерегулирование и время переходного процесса Для этого с момента изменения знака скорости регулируемой координаты формируют дополнительный релейный управляющий сигнал до момента рлвенсг ва нулю вспомог и гелыюге сигнала. Образование вспомогательного сигнала осуществляют путем интегрирования сигнала скорости регулируемой координаты в течение времени действия основного и дополнительного релейных управляющих сигналов . 3 ил.

Изобретение относится к технике автоматического управления, в частности, к технике формирования управляющих сигналов о

Известен способ формирования трехуровневых управляющих сигналов в ре- лейно-импульсных системах управления динамическим объектом, основанный на том, что в зависимости от опибки управления формируют импульсный и релейный управляющие сигналы путем создания скользящего рехнма.

Недостаток этого способа состоит в сложности его реализации, а также в том, что при ограничении входного сигнала рассогласования возрастают время переходного процесса и перерегулирование .

Известен релейио-нмпульсный регулятор, реализующий указанный способ

и содержащий сравнивающее устройство, фильтр, инерционное звено, многопороговый импульсный преобразователь, трех позиционный релейный элемент и суммирующий усилитель.

Недостаток этого регулятора состоит в сложности его реализации, а также в том, что при ограничении входного сигнала рассогласования возрастают время переходного процесса и перерегулирование .

Наиболее близким технп оским решением к способу формирования трехуровневого управляющего гтч IM тг явтяетгя способ, вклюающнй измерите i игнатоя рассогласования и скор in т ,мс-мения рассогласования и при гоь. ЬПЧРШ их знаков формирова ие ре.ь г1 о; о vn,in- ляющего сигнала 5 нл с гит о промгvg

СЛ 00 О

СО

СО

всшоложен знаку сигнала рассогласования .

Недостаток этого способа состоит в том, что при ограничении сигнала рассогласования возрастают время переходного процесса и перерегулировани

Наиболее близким техническим решением к релейному регулятору является устройство, содержащее первый и вто- рой интеграторы, первый, второй и третий компараторы, при этом входы первого и второго компараторов являются входом устройства.

Недостаток этого устройства состо- ит в том, что при ограничении сигнала рассогласования возрастают время переходного процесса и перерегулирование.

Цель изобретения - уменьшение пере20 вторым входом устройства, и соединен

регулирования и времени переходного процесса.

Сущность изобретения состоит в том, что способ формирования трехуровневого управляющего сигнала, включающий 25 ционным входом второго интегратора,

измерение сигналов рассогласования и скорости изменения рассогласования и при совпадении их знаков формирование релейного управляющего сигнала, знак которого противоположен знаку сигнала рассогласования, предполагает с момента начала формирования релейно го управляющего сигнала формирование вспомогательного сигнала путем интегрирования от нуля сигнала скорости изменения рассогласования, при этом формирование вспомогательного и релейного управляющего сигналов прерываетс при уменьшении абсолютного значения вспомогательного сигнала до нуля, а крутизну интегрирования К при уменьшении абсолютного значения сигнала рассогласования и крутизну интегрирования Кг при нарастании абсолютного значения сигнала рассогласования выбирают одинакового знака из условия

IM |кг|.

В релейный регулятор, содержащий первый и второй интеграторы, первый, второй и третий компараторы, при этом входы первого и второго компараторов являются входом устройства, введены шесть элементов И, пять элементов ИЛИ, два ключа, двухпироговый компаратор, два блока масштабирования и четвертый компаратор, при этом выход первого компаратора соединен с пер- выми входами первого, четвертого и пятого элементов И„ выход второго

компаратора соединен с первыми входами второго, третьего и шестого элементов И, выход третьего компаратора соединен со вторыми входами первого и третьего элементов И, выход четвертого компаратора соединен со вторыми входами второго и четвертого элементов И, выход первого элемента И соединен с первыми входами первого и треть- его элементов ИЛИ, выход второго элемента И соединен с вторым входом первого элемента ИЛИ и с первым входом четвертого элемента ИЛИ, выходы третьего и четвертого элементов И соединены с первым и вторым входами второго элемента ИЛИ, выход которого соединен с управляющим входом первого ключа, информационный вход которого является

с информационными входами первого интегратора и второго ключа, выход первого ключа через первый блок масшта- бирования соединен с первым информа

5

выход которого соединен с входом двухнорогового компаратора, соединенного своим выходом со вторыми входами пятого и шестого элементов И, выходы которых соединены соответственно с вторыми входами третьего и четвертого элементов ИЛИ, соединенных своими выходами соответственно с первым и втс рым входами пятого элемента ИЛИ, инверсный выход которого соединен с входом обнуления второго интегратора, второй информадаонный вход которого соединен через второй блок масштаб; - роьания с выходом второго ключа, управляющий вход которого соединен с выходом первого элемента ИЛИ, выход первого интегратора соединен со входами третьего и четвертого компараторов, а выход третьего элемента ИЛИ является первым выходом устройства, выход четвертого элемента ИЛИ являет™ ся вторым выходом устройства.

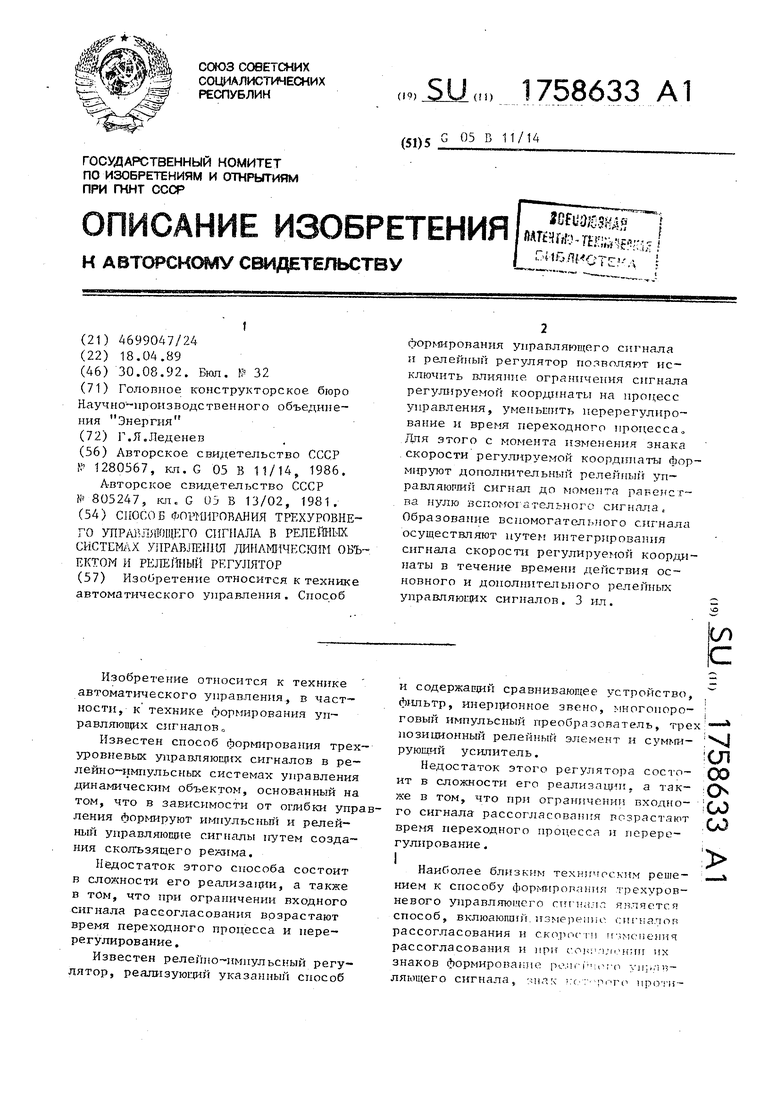

На фиг. 1 представлена схема релейного регулятора, реализующего епособ форкирования трехуровневого управляющего сигнала; на фиг. 2 - фазовые траектории системы управления, использующей релейный регулятор фиг, 1.

Изобретение выполняется следующим 5 образом. Вход устройства 1 соединен со входом первого 3 и второго 4 ком™ параторов, а второй вход устройства 2 соединен с информационным входом

5

0

первого интегратора 5, первого ключа 19 и второго ключа 20. Выход первого интегратора 5 соединен со входами третьего 6 и четвертого 7 ком- параторов. Выход первого конпарато- ра 3 соединен с первыми входами первого 8, четвертого 11 и пятого 12 элементов И, выход второго компаратора 4 соединен с первыми входами второго 9 третьего 10 и шестого 13 элементов И, выход третьего компаратора 6 соединен со вторыми входами первого 8 и третьего 10 элементов И, выход четвертого компаратора 7 соединен со вторыми входами второго 9 и четвертого 11 элементов И. Выход первого элемента И 8 подключен к первым входам первого 14 и третьего 16 элеметов ИЛИ, выход второго элемента И 9 подключен ко второму входу первого элемента ИЛИ 14 и первому входу четвертого элемента ИЛИ 17, выход третьего 10 и четвертого 11 элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ 15, выход которого подключен к управляющему входу первого ключа 19, выход которого через первый блок масшта

бирования 25 соединен с первым инфор- зд ходит после изменения знака сигнала

мационным входом второго интегратора 21, соединенного своим выходом с входом двухпорбгового компаратора 22, выход которого подключен ко вторым входам пятого 12 и шестого 13 элементов И. Выход пятого элемента И соединен со вторым входом третьего элемента ИЛИ 16, выход шестого элемента И 13 соединен со вторым входом четвертого элемента ИЛИ 17.Выход третьего элемента ИЛИ 16 соединен с первым входом пятого элемента ИЛИ 18 и является первым выходом 23 устройства, выход четвертого элемента ИЛИ 17 соединен со вторым входом пятрго элемента ИЛИ 17 и является вторым выходом 24 устройства. Инверсный выход пятого элемента ИЛИ 18 соединен со входом обнуления второго интегратора 21, второй информационный вход которого через второй блок масштабиро-- вания 26 подключен к выходу второго ключа 20, управляющий вход которого соединен с выходом первого элемента ИЛИ-14.

I. S

На фиг.2 X - сигнал рассогласования, X - скорость изменения сигнала

рассогласования, L0, L, L2, L, L

A

0

L,

Ь Хд от сигнала

5

, 4, ь, ь з линии переключения на фазовой плоскости X, Х„

Релейный регулятор работает следующим образом. Пусть на вход релейного регулятора 1 поступает сигнал Х0 - сигнал рассогласования и на второй вход 2 поступает сигнал X - сигнал скорости изменения рассогласования. Считаем, что сигнал Хр имеет ограничение в некоторой точке X ц (в этом состоит отличие рассогласования X).

Предположим, что выходной сигнал первого интегратора 5 имеет ограничение, такое, что $ С I с о, где 8 - заданная величина. Рассмотрим работу такого интегратора. Пусть X 0. Через некоторое время выходной сигнал I станет равным о„ В этом случае первый интегратор 5 будет сохранять свое состояние I о до тех пор, пока X 0. Пусть в некоторый момент времени tQ X 0, а затем этот сигнал начал уменьшаться (X 0) . С этого момента времени начнет уменьшаться и сигнал I. Через некоторое время Дй сигнал I станет равным -о, т.е. изменение состояния первого интегратора 5 проис5

0

5

0

5

X, при этом за время изменения состояния этого интегратора от I о до I - -0 сигнал рассогласования X изменяется на величину ДХ 2о, т.к. ДХ

t04-b.i Xdt 2&. Аналогичные рассужto

дения можно провести и для случая

X 0.

Таким образом, изменение состояния первого интегратора 5 от I о до I - 0 и наоборот происходит после изменения знака сигнала X. За время этого изменения сигнал рассогласования изменяется на величину ДХ 2о. Если 8 выбрать достаточно малой величиной, то можно считать, что изменение состояния первого интегратора 5 происходит при изменении знака сигнала X.

Пусть сигнал Х увеличивается от нуля (X 0). При Хо, h (h - уровень срабатывания и отпускания второго компаратора 4) выходные сигналы первого 3 и второго 4 компараторов соответственно равны Rt 0, и R2 О (О обозначает низкий уровень выходного сигнала) . Вьг:однь е сигналы первого 8, второго 9, треного Ю и четвертого 11 элементов И гоотпетстешто равны Rg О, R 0, R10 0 и R 0. Выходной сигнал третьего элемента ИЛИ 16 U 0 (первый выход устройства 23), выходной сигнал чет- , вертого элемента ИЛИ 17 U 0 (второй выход устройства 24), вследствие чего инверсный выходной сигнал пятого элемента ИЛИ 18 R-, 1(t обозначает высокий уровень выходного сигнала) 10 и этот сигнал производит обнуление второго интегратора 21 (выходной сигнал этого интегратора ),

При X 0 выходной сигнал первого интегратора 5 I 6. В этом случае 15 срабатывает четвертый компаратор 7 (его уровень срабатывания и отпускания выбирается равным б) и его выходной сигнал R d 1. Этот сигнал разрешает прохождение сигналов R1 и R2 20 через второй 9 и четвертый 11 элементы И. При Xq h второй компаратор 4 срабатывает и его выходной сигнал Так как Rd 1, то и R,

Отметим, если ХП1- максимальное значение сигнала рассогласования, то Х,- h j Xtd Sm/K2 (2)

о

В момент времени ц выходной сигнал первого интегратора 5 I начинает умень шаться (выключаются четвертый компа- ратор 7) и по истечении небольшого времени Д t сигнал I станет равным -Ј , В этот момент времени срабатывает третий компаратор 6 уровень срабатывания и отпускания этого компаратора равен - &}° Выходные сигналы третьего 6 и четвертого 7 компараторов соответственно равны R 1 и RA О, Сигнал R-з 1 разрешает прохождение сигнала R2 1 через третий элемент И 10 на вход второго элемента ИЛИ 15, выходной сигнал которого R 5 от крывает первый ключ 19, подключая тем самым сигнал X к первому информационному входу второго интегратора 21 через первый блок масштабирования

. fj i «icir - i j ri - I

Выходные сигналы первого 14 и второго 2525 с коэффициентом передачи К . Сиг17 элементов ИЛИ будут соответствен-нал R j. О запрещает прохождение сигно равны Rj|4. 1 HlJ 1. С этогонала RЈ 1 через второй элемент И 9

момента времени формируется положителъ-и его выходной сигнал К„ 0. значит ный выходной сигнал U 1 и одновре-

30

менно выходной сигнал первого ИЛИ 14 R 4Ц. 1 открывает второй ключ 20, а выходной сигнал пятого элемента ИЛИ 18 R О (U 1) снимает обнуление второго интегратора 21,, Открытый второй ключ 20 с этого момента времени t 10 подает на вход второго интегратора 21 через второй масштабирующий блок 26tс коэффициентом передачи Kg сигнал X, При достижении выходным сигналом второго интегратора 21 S значения Д. срабатывает двухпороговый компаратор 22 (ЈГ уровень срабатывания и отпускания этого компаратора при S О, & - малая величина) и его выходной сигнал R 1 подается на входы пятого 12 и шестого 13 элементов И. Так как R( О, R2 1, то выходные сигналы пятого 12 и шестого 13 элементов И равны соответственно R Ј 0 и R 4з 1 Сигнал R 13 1 через четвертый элемент ИЛИ 17 поддерживает высокий уровень сигнала и.

Состояние схемы не будет изменяться до тех пор, пока не изменится знак сигнала X. Пусть это произойдет в момент времени t|, За время от tp до t сигнал второго интегратора, 21 S

и его выходной сигнал RQ О,

и R |ф 0. Этот сигнал закрывает ключ 20 и с момента времени t( выходной сигнал второго интегратора 21 S начинает уменьшаться /X 0./ „ При достижении сигналом S значения Д выключается двухпороговый компаратор

35 22 и его выходной сигнал Rg 0 запрещает прохотодение сигнала R2 1 через шестой элемент И 13 на вход четвертого элемента ИЛИ 17 и ее выходной сигнал U становится равным

4Q нулю Одновременно выходной сигнал пятого элемента ИЛИ 18 R 1 производит обнуление второго интегратора 21 .

Пусть S U в момент времени t

45 Для этого момента времени имеем

50

55

S & 8т- К, J

t,

Введем обозначение

±г Xt Xdt

t, Тогда

u sm Ktx2. .

Xdt

(3)

(4)

будет равен

S

Sttl K1 |/dt d)

Так как & близка к нулю, то с учетом (2) имееп

(5)

K2(Xm- h)

К1хг

Отметим, если ХП1- максимальное значение сигнала рассогласования, то Х,- h j Xtd Sm/K2 (2)

о

В момент времени ц выходной сигнал первого интегратора 5 I начинает уменшаться (выключаются четвертый компа- ратор 7) и по истечении небольшого времени Д t сигнал I станет равным -Ј , В этот момент времени срабатывает третий компаратор 6 уровень срабатывания и отпускания этого компаратора равен - &}° Выходные сигналы третьего 6 и четвертого 7 компараторов соответственно равны R 1 и RA О, Сигнал R-з 1 разрешает прохождение сигнала R2 1 через третий элемент И 10 на вход второго элемента ИЛИ 15, выходной сигнал которого R 5 от крывает первый ключ 19, подключая тем самым сигнал X к первому информационному входу второго интегратора 21 через первый блок масштабирования

нала RЈ 1 через второй элемент И 9

и его выходной сигнал К„ 0. значит

и его выходной сигнал RQ О,

и R |ф 0. Этот сигнал закрывает ключ 20 и с момента времени t( выходной сигнал второго интегратора 21 S начинает уменьшаться /X 0./ „ При достижении сигналом S значения Д выключается двухпороговый компаратор

22 и его выходной сигнал Rg 0 запрещает прохотодение сигнала R2 1 через шестой элемент И 13 на вход четвертого элемента ИЛИ 17 и ее выходной сигнал U становится равным

нулю Одновременно выходной сигнал пятого элемента ИЛИ 18 R 1 производит обнуление второго интегратора 21 .

Пусть S U в момент времени t

Для этого момента времени имеем

S & 8т- К, J

t,

Введем обозначение

±г Xt Xdt

t, Тогда

u sm Ktx2. .

Xdt

(3)

(4)

как & близка к нулю, то с учетом имееп

(5)

K2(Xm- h)

К1хг

Таким образом, формирование выходного управляющего сигнала (J+ 1 начинается с момента времени t0, при котором Ха h, С этого момента вре- мени до момента времени t( , т0е„ в течение времени, пока знаки сигналов iXQ и X совпадают, формируется релейный управляющий сигнал U+ 1. Одноврменно с момента времени tQ до момен- та времени t формируется вспомогательный сигнал S путем интегрирования скорости изменения сигнала рассогласования X /выражения (1) и (3)/ Прерывание релейного управляющего сигнала U 1 производится в момент равенства нулю вспомогательного сигнала S

Аналогично схема работает и при уменьшении Х от нуля (X Ј 0) . в этом случае срабатывает первый 3 и третий 6 компараторы, первый 8, третий 10 и пятый 12 элементы И и второй 15 и третий 16 элементы ИЛИ формируют релейный управляющий сигнал U 1 на первом выходе устройства 23.

Рассмотрим процесс управления на фазовой плоскости X, X на примере управления инерционным объектом второго порядка с передаточной функцией W0(P) 1/Р2. Состояние объекта управления определим сигналами X и X. Если управляющий сигнал U 0 (и+ О, U 0), то фазовые траектории - линии, параллельные оси X. Если управляющий сигнал U 1 (U4 1) или U -1 (U 1), то фазовые траектории-параболы, симметричные относительно оси X,

Уравнения линий переключения имеют вид

X h () X -h ()

}

ЛИНИИ

включения

(6)

- х

)

Ј-

2Хц(-Х - h)

( S - iP

кг

линии

выключения

(7)

где Хц - значение ускорения сигнала рассогласования X, возникающего при формировании управляющего сигнала U+ 1 или U 1. Уравнения линий переключения L, иЦ могут быть получены на фазовой плоскости X, X с учетом равенства (5) , определяющего уровень сигнала X (Х,- Х), при котором проис5

, Q

0

5

0

5

0

5

0

ходит отключение управляющего сигнала U ( О, U 0).

Как следует из (7), цля достижения устойчивого управления необходимо выбирать коэффициент передачи К больше коэффициента передачи К.

Рассмотрим движение изображающей точки А(0, Xj на фазовой плоскости X, X фиг. 2. Система управления с рассматриваемым релейным регулятором, реализующим способ формирования управляющего сигнала, имеет фазовую траекторию А (точки принадлежат линиям переключения

ния

1-0

L,

,, L,O, L() . Система управле- эстным регулятором имеет фазовую траекторию A -«-A - --A - -A j,- Ag-«-A - -Aj0 „ Предполаq имеет ог- В соответ5

гаем, что входной сигнал X

раничение в точке Хд Х,|. ствии со структурной схемой известного регулятора линии переключения имеют вид

X -m(X + h), h УЈ:ХН

L2- X -m(X - h) - -h (8)

L fc X X,i, X X H

L -i X -X , X - - X ц

где m - заданный коэффициент.

Оценим перерегулирование Р и время переходного процесса Т, Под перерегулированием Р будем понимать отношение , где Хт1 - максимальное значение сигнала рассогласования X при управляющем сигнале U одного знака, ХП12 максимальное значение сигнала рассогласования X при управляющем (очередном) сигнале U другого знака. Как следует из фазовых траекторий фиг. 2 перерегулирование Р и время переходного процесса Т системы с расг сматриваемым релейным регулятором меньше перерегулирования и времени переходного процесса системы с известным релейным регулятором.

В одних и тех же условиях, например, при Х0 10 В/сек, X н Ю В, h 1 В, Ха 0,3 В/сек, Ху 2 В/сек2 , m 0,3 1/сек, К 10, К 1 перерегулирование в системе с известным регулятором равно 64%, а в системе с рассматриваемым регулятором равно 9%, время переходного процесса(время вхождения изображающей точки в область Ь, Х„) соответственно равны 30 сек, и 21 сек. Формула изобретения

системах управления динамическим объектом, включающий измерение сигналов рассогласования и скорости изменения рассогласования и при совпадении их знаков-формирование релейного управляющего сигнала, знак которого противоположен знаку сигнала рассогласования , отличающийся тем, что, с целью уменьшения перерегулирования и времени переходного процесса, с момента начала формирования релейного управляющего сигнала формируют вспомогательный сигнал путем интегрирования от нуля сигнала скорости изменения рассогласования, при этом формирование вспомогательного и релейного управляющих сигналов прерывают при уменьшении абсолютного значения вспомогательного сигнала до нуля, а крутизну интегрирования К f при уменьшении абсолютного значения сигнала рассогласования и крутизну интегрирования при нарастании абсолютного значения сигнала рассогласования выбирают одинакового знака из условия |К, | | К2).

2о Релейный регулятор, содержащий первый и второй интеграторы, первый,

второй и третий компараторы, при этом on ментов ИЛИ, соединенных своими выхо-

входы первого и второго компараторов являются входом регулятора, отличающийся тем, что, с целью уменьшения перерегулирования и времени переходного процесса, в него введены шесть элементов И, пять элементов ИЛИ, два ключа, двухпороговый компаратор, два блока масштабирования и четвертый компаратор, при этом выход первого компаратора соединен с первыми входами первого, четвертого и пятого элементов И, выход второго компаратора соединен с первыми входами второго, третьего и шестого элементов И, выход третьего компара35

40

дами с первым и вторым входами пятого элемента ИЛИ, инверсный выход которого соединен с входом обнуления второго интегратора, второй информационный вход которого соединен через второй блок масштабирования с выходом второго ключа, управляющий вход которого соединен с выходом первого элемента ИЛИ, выход первого интегратора соединен с входами третьего и четвертого компараторов, выход третьего элемента ИЛИ является первым выходом регулятора, а вьпяод четвертого элемента ИЛИ является его вторым выходом

45

5

тора соединен с вторыми входами первого и третьего элементов И, выход четвертого компаратора соединен с вторыми входами второго и четвертого элементов И, выход первого элемента И соединен с первыми входами первого и третьего элементов ИЛИ, выход второго элемента И соединен с вторым входом первого элемента ИЛИ и с первым входом четвертого элемента ИЛИ, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с управляющим входом первого ключа, информационный вход которого является вторым входом регулятора, и с информационными входами первого интегратора и второго ключа, выход первого ключа через первый блок масштабирования соединен с первым информационным входом второго интегратора, выход которого соединен с входом двух- порогового компаратора, соединенного своим выходом с вторыми входами пятого и шестого элементов И, выходы которых соединены соответственно с вторыми входами третьего и четвертого эле5

0

дами с первым и вторым входами пятого элемента ИЛИ, инверсный выход которого соединен с входом обнуления второго интегратора, второй информационный вход которого соединен через второй блок масштабирования с выходом второго ключа, управляющий вход которого соединен с выходом первого элемента ИЛИ, выход первого интегратора соединен с входами третьего и четвертого компараторов, выход третьего элемента ИЛИ является первым выходом регулятора, а вьпяод четвертого элемента ИЛИ является его вторым выходом.

La

MJ

1г

Основной релейный сигнал

Xi

Йопоямщ релейный сигнал

Вспамог. ,сигнал

U ts

хг

/

| Релейно-импульсный регулятор | 1984 |

|

SU1280567A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Способ управления | 1975 |

|

SU805247A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-08-30—Публикация

1989-04-18—Подача