Предлагаемое изобретение относится к импульсной технике, в частности к автоматике и вычислительной технике, и может быть использовано в цепях фазовой автоподстройки.

Наиболее близким по технической сущности к предлагаемому устройству является устройство для добавления и вычитания импульсов, содержащее первый и второй элементы И, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с выходной шиной, с первого по третий триггеры, делитель частоты вход которого соединен с шиной опорных импупьсов, а выход - с первым входом второго элемента И и С-вход третьего триггера D-вход которого соединен с выходом второго триггера, а также шину управления и шину корректирующих импульсов, причем первый вход первого элемента И соединен с шиной опорных импульсов и С-входом первого триггера, D-вход которого соединен с шиной управления, а выход - со вторым входом первого элемента И, третий вход которого соединен с инверсным выходом третьего триггера, прямой выход которого соединен со вторым входом второго элемента И, первый вход которого соединен с С-входом второго триггера, S-вход которого соединен с шиной корректирующих импульсов, а D-вход - с шиной потенциала лог. О.

Известное устройство позволяет формировать импульсную последовательность, количество и время появления импульсов в которой зависят от сигналов на шинах управления устройства

Однако наличие импульсных помех на шине ввода опорных импульсов приводит к срабатыванию второго и третьего триггеров, что приводит к искажениям выходной импульсной последовательности Таким образом, недостатком известного устройства

VI

сл

00 00

сл ю

является низкая помехозащищенность устройства.

Целью предлагаемого устройства до- бтвления-вычитания импульсов является пооышение помезохозащищенности устройства, которая достигается тем, что наличие коротких импульсов на управляющих входах в предлагаемом устройстве в отличие от прототипа не приводит к срабатыванию устройств.

Для достижения цели в известное устройство добавления-вычитания импульсов, содержащее последовательно соединенные первый и второй триггеры, С-входы которых объединены и подключены к шине тактовых импульсов, элемент И и элемент ИЛИ, введены три инвертора и четыре элемента И- НЕ. причем вход первого инвертора и первый вход элемента И объединены и подключены к входу Вычитание, второй вход элемента И и вход второго инвертора объединены и подключены к входу Добавление устройства, выход элемента И подключен к D-входу первого триггера, инверсный выход которого подключен к вторым входам первого и второго элементов И-НЕ, первые входы которых объединены и подключены к прямому выходу второго триггера, третьи входы первого и второго элементов И-НЕ подключены к выходам первого и второго инверторов соответственно. Выход первого элемента И-НЕ подключен к второму входу третьего элемента И-НЕ, первый вход которого подключен через инвертор к входу Вычитание устройства. Выход второго элемента И-НЕ подключен к третьему входу третьего элемента И-НЕ и к второму входу элемента ИЛИ, первый вход элемента ИЛИ подключен к шине заполнения устройства. Выход элемента ИЛИ и выход третьего элемента И-НЕ подключены к первому и второму оходзм четвертого элемента И-НЕ соответственно.

Все элементы устройства добавления- вычитания импульсов могут быть реализованы на стандартных интегральных микросхемах, например серий 155, 533.

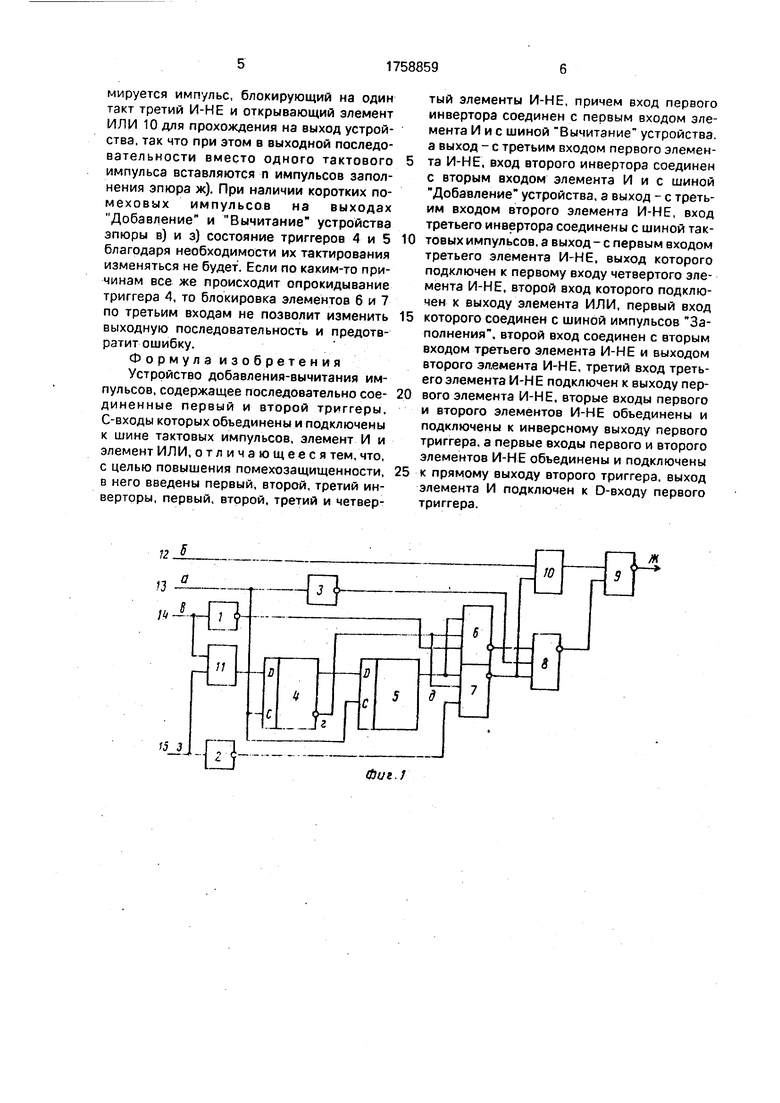

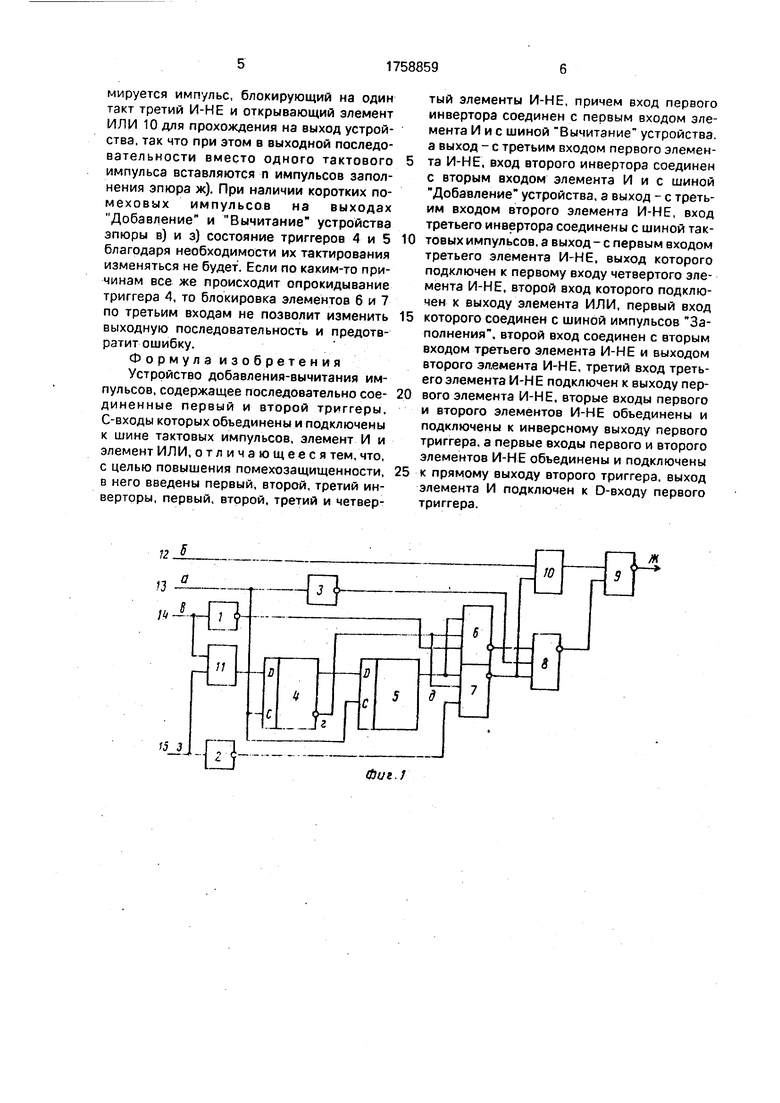

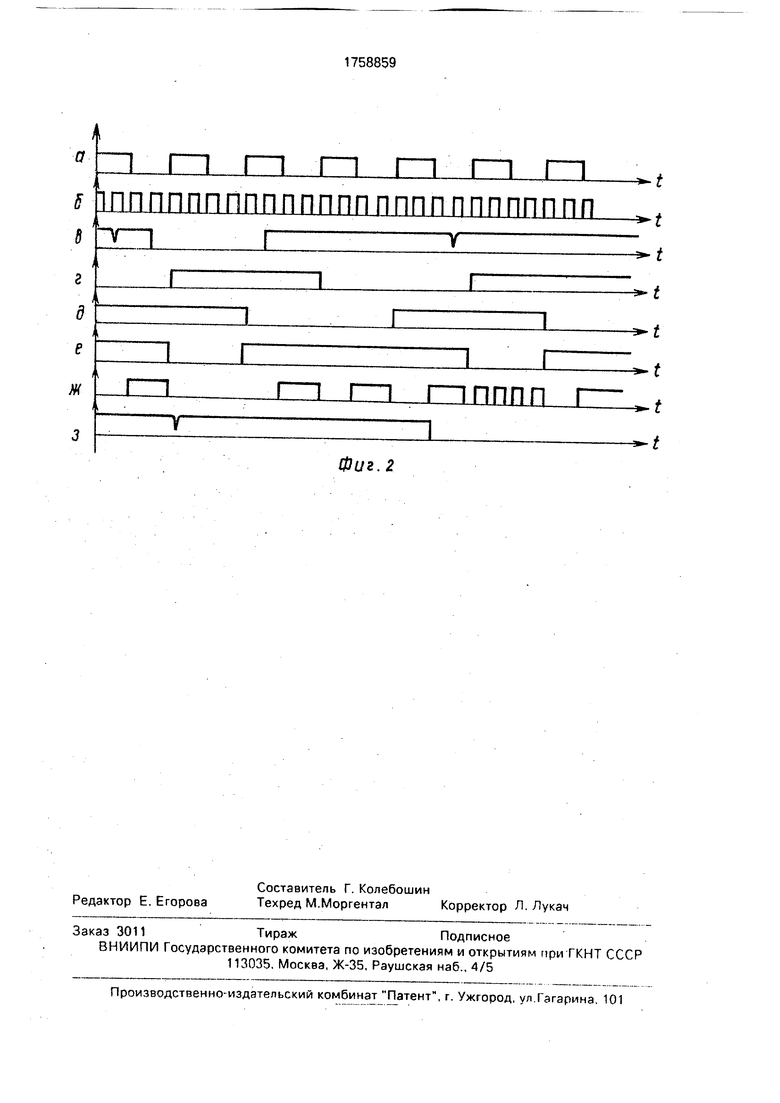

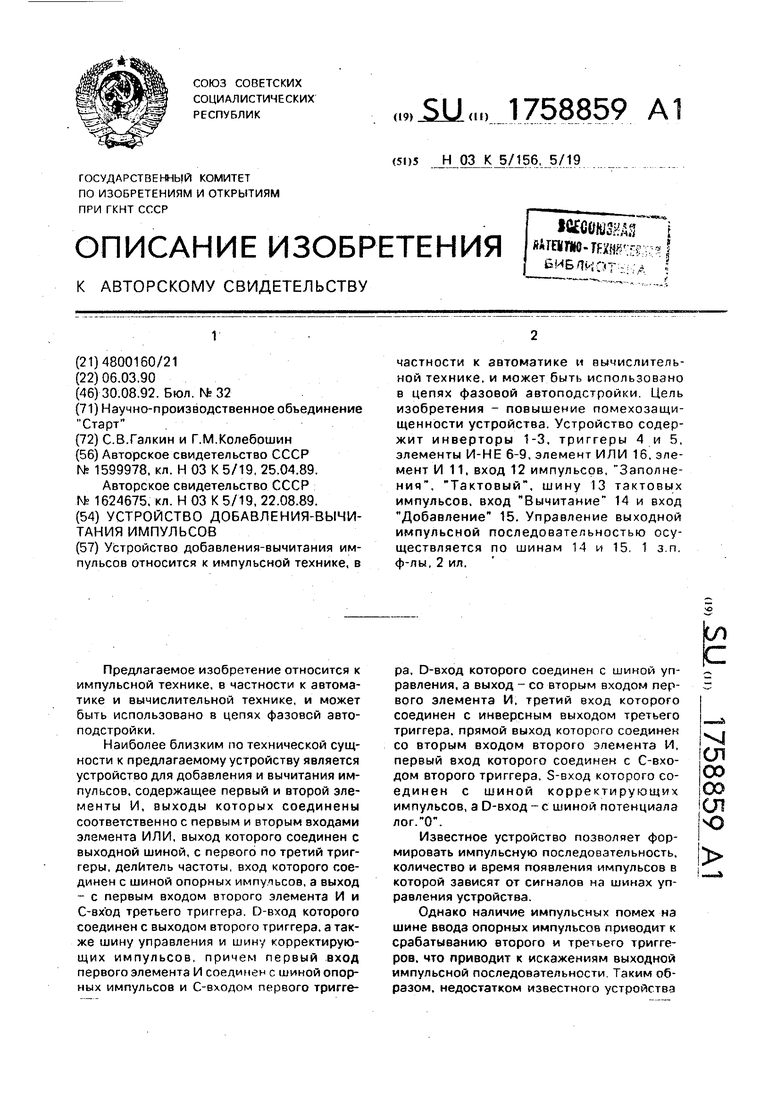

На фиг. 1 представлена структурная схема предполагаемого устройства добавления-вычитания импульсов; на фиг. 2 - эпюры, поясняющие работу устройства.

Устройство добавления-вычитания импульсов (фиг.1) включает: первый 1, второй 2 и третий 3 инверторы, первый 4, второй 5 триггеры, первый б, второй 7, третий 8 и четвертый 9 элементы И-НЕ. элемент ИЛИ 10, элемент И 11, шина импульсов Заполнена 12, шина тактовых импульсов 13, вход Вычитание 14 и вход Добавление 15, причем первый вход элемента 11 объединен с входом инвертора 1, а второй вход элемента 11 объединен с входом инвертора 2 и подключены к входам 14 и 15 устройства соответственно выход элемента 11 подклю- чен к D-входу триггера 4. прямой выход которого подключен к D-входу триггера 5, выход которого подключен к первым входам элементов б и 7. Инверсный выход триггера 4 подключен к вторым входам элементов 6 0 и 7. Третьи входы элементов б и 7 подключены к выходам инверторов 1 и 2 соответственно. Тактовые входы триггеров 4 и 5 объединены с входом инвертора 3 и подключены к шине 13 устройства. Выход элемента 5 7 подключен к второму входу элемента 10 и к третьему входу элемента 8. Первый и второй входы элемента 8 подключены к выходам инвертора 3 и элемента 6 соответственно. Первый вход элемента 10 0 подключен к шине 12 устройства. Первый и второй входы элемента 9 подключены к выходам элементов 10 и 8 соответственно.

Устройство добавления-вычитания импульсов (фиг.1) работает следующим обра- 5 зом.

В исходном состоянии на входах управления (входы Добавление 15 и Вычитание 14 импульсов) присутствует сигнал лог.1 эпюра в) (фиг.2) и оба триггера (4, 5)( 0 находятся в состоянии соответствующем лог.1 на прямом выходе. Лог.О с инверсного выхода второго триггера (5) блокирует первый и второй элементы И-НЕ, на выходах которых присутствует сигнал лог.1, что по- 5 зволяет блокировать элемент ИЛИ 10, пройти тактовой последовательности с тактового входа, через третий инвертор 3, третий 8 и четвертый 9 элементы И-НЕ на выход устройства. При поступлении сигнала 0 на вход Вычитание 14 устройства эпюры в) лог.1 на первом входе разблокируются первый элемент И-НЕ 6, тактовым импульсом опрокидывается первый триггер 4 эпюра г), что вызывает появление лог.О на 5 выходе первого б элемента И-НЕ и блокирование третьего 8 элемента И-НЕ, следующим тактовым импульсом переключается второй триггер 5 и вновь блокируется первый элемент И-Н Е эпюра д). Таким образом, 0 при поступлении сигнала лог.О на вход Вычитание на выходе первого элемента И-НЕ формируется импульс эпюра е), длительностью равной тактовому периоду, блокирующий тактовую последовательность и на 55 выходе устройства происходит выпадение одного тактового импульса из последовательности эпюра ж).

При поступлении лог.О на вход добавление эпюра з) на выходе второго элемента аналогично описанному выше формируется импульс, блокирующий на один такт третий И-НЕ и открывающий элемент ИЛИ 10 для прохождения на выход устройства, так что при этом в выходной последовательности вместо одного тактового импульса вставляются п импульсов заполнения эпюра ж). При наличии коротких по- меховых импульсов на выходах Добавление и Вычитание устройства эпюры в) и з) состояние триггеров 4 и 5 благодаря необходимости их тактирования изменяться не будет. Если по каким-то причинам все же происходит опрокидывание триггера А, то блокировка элементов б и 7 по третьим входам не позволит изменить выходную последовательность и предотвратит ошибку.

Формула изобретения Устройство добавления-вычитания импульсов, содержащее последовательно сое- диненные первый и второй триггеры, С-входы которых объединены и подключены к шине тактовых импульсов, элемент И и элемент ИЛИ, отличающееся тем, что, с целью повышения помехозащищенности, в него введены первый, второй, третий инверторы, первый, второй, третий и четвертый элементы И-НЕ, причем вход первого инвертора соединен с первым входом элемента И и с шиной Вычитание устройства. а выход - с третьим входом первого элемента И-НЕ, вход второго инвертора соединен с вторым входом элемента И и с шиной Добавление устройства, а выход - с третьим входом второго элемента И-НЕ, вход третьего инвертора соединены с шиной тактовых импульсов, а выход - с первым входом третьего элемента И-НЕ, выход которого подключен к первому входу четвертого элемента И-НЕ, второй вход которого подключен к выходу элемента ИЛИ, первый вход которого соединен с шиной импульсов Заполнения, второй вход соединен с вторым входом третьего элемента И-НЕ и выходом второго элемента И-НЕ, третий вход третьего элемента И-НЕ подключен к выходу первого элемента И-НЕ, вторые входы первого и второго элементов И-НЕ объединены и подключены к инверсному выходу первого триггера, а первые входы первого и второго элементов И-НЕ объединены и подключены к прямому выходу второго триггера, выход элемента И подключен к D-входу первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания и добавления импульсов | 1988 |

|

SU1599978A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1524178A1 |

| "Устройство для декодирования кода "Манчестер-2" | 1990 |

|

SU1809536A1 |

| Устройство для измерения шума квантования дельта-кодека | 1987 |

|

SU1450121A1 |

| Устройство для измерения динамической погрешности аналого-цифровых преобразователей | 1987 |

|

SU1529453A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1989 |

|

SU1667214A1 |

| Устройство для контроля состояния распределенных объектов | 1990 |

|

SU1742841A1 |

| Фазовый синхронизатор | 1990 |

|

SU1739491A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Устройство для измерения частоты и периода гармонического сигнала | 1991 |

|

SU1797714A3 |

Устройство добавления-вычитания импульсов относится к импульсной технике, в частности к автоматике и вычислительной технике, и может быть использовано в цепях фазовой автоподстройки Цель изобретения - повышение помехозащищенности устройства. Устройство содержит инверторы 1-3. триггеры 4 и 5, элементы И-НЕ 6-9, элемент ИЛИ 16. элемент И 11, вход 12 импульсов, Заполнения, Тактовый, шину 13 тактовых импульсов, вход Вычитание 14 и вход Добавление 15. Управление выходной импульсной последовательностью осуществляется по шинам 14 и 15 1 з п ф-лы, 2 ил.

и4

Фиг.}

Фиг. 2

| Устройство для вычитания и добавления импульсов | 1988 |

|

SU1599978A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для вычитания и добавления импульсов | 1989 |

|

SU1624675A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-08-30—Публикация

1990-03-06—Подача