Изобретение относится к вычислительной технике и предназначено для использования в сетях передачи и приема данных, в частности, с аварийных радиобуев с космической системы связи Коспас-Сарсат.

Целью изобретения является повышение достоверности декодирования за счет исключения потерь информации до первого интервала, равного 2 Т.

На фиг.1 представлена блок-схема устройства для декодирования кода Манче- стёр-2 ; на фиг.2,3 - временные диаграммы, поясняющие работу устройства, на фиг.4 раскрыты принципиальные схемы узлов, входящих в состав устройства.

Устройство для декодирования кода Манчестер-2 содержит вход 1, детектор 2 перехода, формирователь 3 импульсов, распределитель 4 импульсов, элемент ИЛИ 5, триггеры 6...8, блок 9 оперативной памяти, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, элементы 11, 12 задержки, элемент ИЛИ 13, элемент И 14, счетчик 15 импульсов, генератор

16 импульсов, формирователь 17 импульсов, выходы 18,..20.

Вход 1 устройства подключен к информационному входу блока 9 оперативной памяти и ко входу детектора 2 переходов, выход которого подключен ко входу формирователя 3 импульсов и ко входу распределителя 4 импульсов. Выходы формирователя 3 и детектора 2 подключены ко входам логического элемента ИЛИ 5, выход которого подключен к импульсному входу триггера 6, ко входу установки в О которого подключен первый выход распределителя 4. Выход Триггера 6 подключен к D-входу триггера 7 и через формирователь

17 к первому входу элемента ИЛИ 13, выход которого подключен к тактирующему входу блока 9 оперативной памяти и через элемент задержки 12 к тактирующему входу счетчика 15 адресов, Выходы счетчика 15 адресов подключены к адресным входам блока 9 оперативной памяти, а выход разряда переполнения счетчика 15 адресов подключен к своему входу переноса CI и является выходом 20 устройства. Второй выход распределителя 4 подключен ко входу выбора режима блока 9 оперативной памяти, ко входу установки в 0 триггера 8 и ко входу генератора 16 импульсов, выход которого подключен ко второму входу элемента ИЛИ 13 и является выходом 18 устройства. Третий выход распределителя 4 подключен ко входу установки в 0 счетчика 15 адресов. К С-входу триггера 8, а также к первому входу элемента И 14 подключен выход формирователя 3, к D-входу триггера 8 подключен источник уровня логической 1.

Инверсный выход триггера 8 через элемент задержки 11 подключен ко второму входу элемента И 14, выход которого подключен к С-входу триггера 7, выход которого подключен к первому входу элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ, ко второму входу которого подключен выход блока 9 оперативной памяти. Выход элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ является выходом 19 устройства.

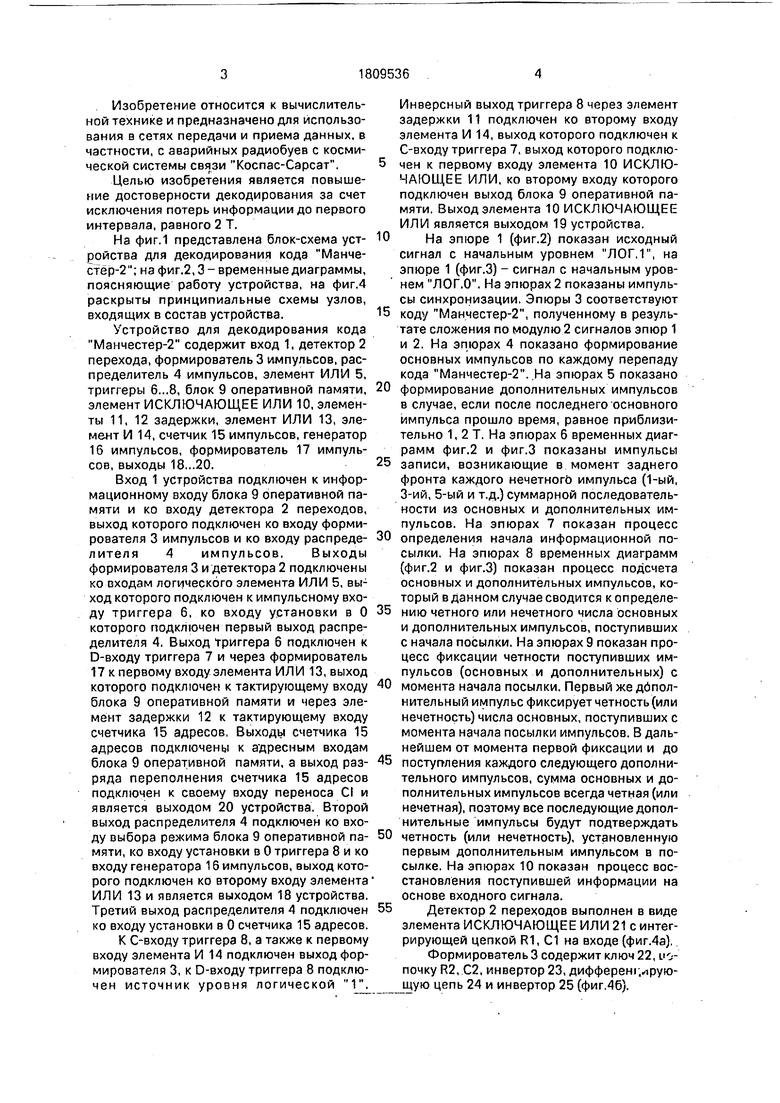

0 На эпюре 1 (фиг.2) показан исходный сигнал с начальным уровнем ЛОГ.1, на эпюре 1 (фиг.З) - сигнал с начальным уровнем ЛОГ.О. На эпюрах 2 показаны импульсы синхронизации. Эпюры 3 соответствуют

5 коду Манчестер-2, полученному в результате сложения по модулю 2 сигналов эпюр 1 и 2. На эпюрах 4 показано формирование основных импульсов по каждому перепаду кода Манчестер-2..На эпюрах 5 показано

0 формирование дополнительных импульсов в случае, если после последнего основного импульса прошло время, равное приблизительно 1, 2 Т. На эпюрах 6 временных диаграмм фиг.2 и фиг.З показаны импульсы

5 записи, возникающие в момент заднего фронта каждого нечетного импульса (1-ый, 3-ий, 5-ый и т.д.) суммарной последовательности из основных и дополнительных импульсов. На эпюрах 7 показан процесс

0 определения начала информационной посылки, На эпюрах 8 временных диаграмм (фиг.2 и фиг.З) показан процесс подсчета основных и дополнительных импульсов, который в данном случае сводится копределе5 нию четного или нечетного числа основных и дополнительных импульсов, поступивших с начала посылки. На эпюрах 9 показан процесс фиксации четности поступивших импульсов (основных и дополнительных) с

0 момента начала посылки. Первый же дбпол- нительный импульс фиксирует четность (или нечетность) числа основных, поступивших с момента начала посылки импульсов. В дальнейшем от момента первой фиксации и до

5 поступления каждого следующего дополнительного импульсов, сумма основных и дополнительных импульсов всегда четная (или нечетная), поэтому все последующие дополнительные импульсы будут подтверждать

0 четность (или нечетность), установленную первым дополнительным импульсом в посылке. На эпюрах 10 показан процесс восстановления поступившей информации на основе входного сигнала.

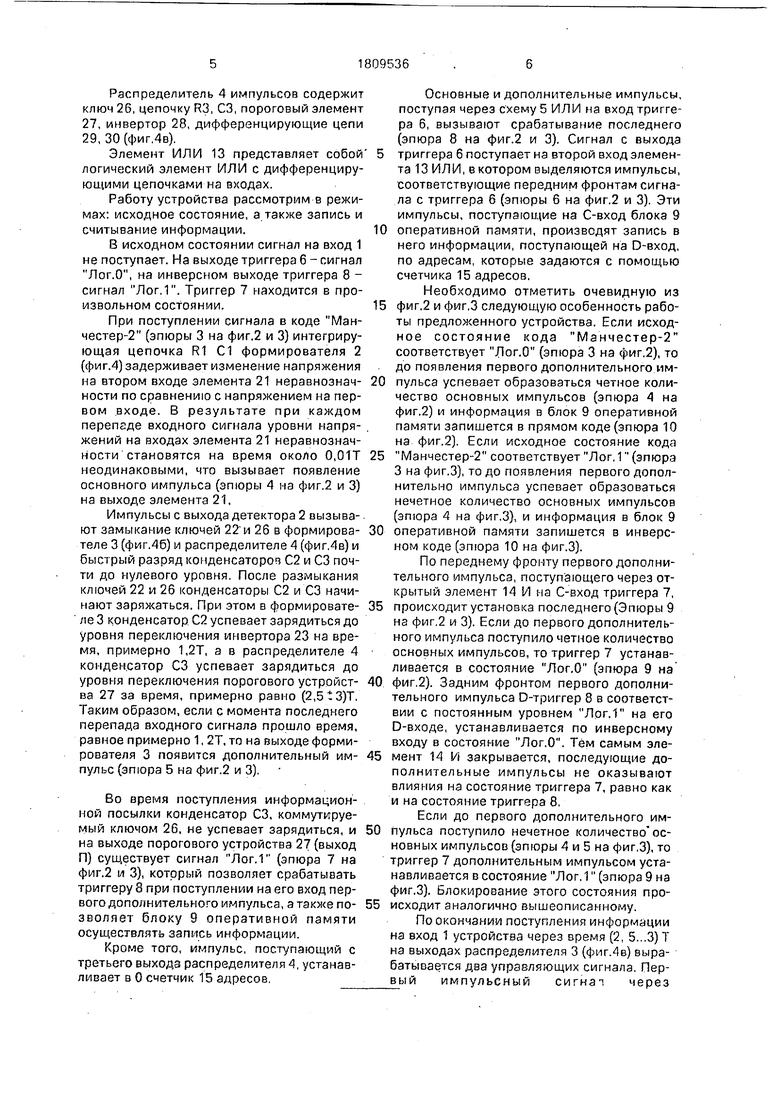

5 Детектор 2 переходов выполнен в виде элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21 с интегрирующей цепкой R1, С1 на входе (фиг.4а), Формирователь 3 содержит ключ 22, vfj- почку R2, С2, инвертор 23, дифференг.ирую- щую цепь 24 и инвертор 25 (фиг,46).

Распределитель 4 импульсов содержит ключ 26, цепочку R3, СЗ, пороговый элемент 27, инвертор 28, дифференцирующие цепи 29, 30 (фиг,4в).

Элемент ИЛИ 13 представляет собой логический элемент ИЛИ с дифференцирующими цепочками на входах.

Работу устройства рассмотрим в режимах: исходное состояние, а также запись и считывание информации.

В исходном состоянии сигнал на вход 1 не поступает. На выходе триггера 6 - сигнал Лог.О, на инверсном выходе триггера 8 - сигнал Лог.1. Триггер 7 находится в произвольном состоянии.

При поступлении сигнала в коде Манчестер-2 (эпюры 3 на фиг.2 и 3) интегрирующая цепочка R1 С1 формирователя 2 (фиг.4) задерживает изменение напряжения на втором входе элемента 21 неравнознач- ности по сравнению с напряжением на первом входе. В результате при каждом перепаде входного сигнала уровни напряжений на входах элемента 21 неравнозначности становятся на время около 0,017 неодинаковыми, что вызывает появление основного импульса (эпюры 4 на фиг.2 и 3) на выходе элемента 21,

Импульсы с выхода детектора 2 вызыва- ют замыкание ключей 22 и 26 в формирова- теле 3 (фиг.4б) и распределителе 4 (фиг.4в) и быстрый разряд конденсаторов С2 и СЗ почти до нулевого уровня. После размыкания ключей 22 и 26 конденсаторы С2 и СЗ начинают заряжаться. При этом в формировате- ле 3 конденсатор. С2 успевает зарядиться до уровня переключения инвертора 23 на время, примерно 1,2Т, а в распределителе 4 коиден.сатор СЗ успевает зарядиться до уровня переключения порогового устройст- ва 27 за время, примерно равно (2,5i3)T. Таким образом, если с момента последнего перепада входного сигнала прошло время, равное примерно 1, 2Т, то на выходе формирователя 3 появится дополнительный им- пульс (эпюра 5 на фиг.2 и 3).

Во время поступления информационной посылки конденсатор СЗ, коммутируемый ключом 26, не успевает зарядиться, и на выходе порогового устройства 27 (выход П) существует сигнал Лог.1 (эпюра 7 на фиг.2 и 3), который позволяет срабатывать триггеру 8 при поступлении на его вход первого дополнительного импульса, а также по- зволяет блоку 9 оперативной памяти осуществлять запись информации.

Кроме того, импульс, поступающий с третьего выхода распределителя 4, устанавливает в 0 счетчик 15 адресов.

Основные и дополнительные импульсы, поступая через схему 5 ИЛИ на вход триггера 6, вызывают срабатывание последнего (эпюра 8 на фиг.2 и 3). Сигнал с выхода триггера 6 поступает на второй вход элемента 13 ИЛИ, в котором выделяются импульсы, соответствующие передним фронтам сигнала с триггера 6 (эпюры 6 на фиг.2 и 3). Эти импульсы, поступающие на С-вход блока 9 оперативной памяти, производят запись в него информации, поступающей на D-вход, по адресам, которые задаются с помощью счетчика 15 адресов.

Необходимо отметить очевидную из фиг,2 и фиг.З следующую особенность работы предложенного устройства. Если исходное состояние кода Мзнчестер-2 соответствует Лог.О (эпюра 3 на фиг.2), то до появления первого дополнительного импульса успевает образоваться четное количество основных импульсов (эпюра 4 на фиг.2) и информация в блок 9 оперативной памяти запишется в прямом коде (эпюра 10 на фиг.2). Если исходное состояние кода Манчестер-2 соответствует Лог, 1 (эпюра 3 на фиг.З), то до появления первого дополнительно импульса успевает образоваться нечетное количество основных импульсов (эпюра 4 на фиг.З), и информация в блок 9 оперативной памяти запишется в инверсном коде (эпюра 10 на фиг.З).

По переднему фронту первого дополнительного импульса, поступающего через открытый элемент 14 И на С-вход триггера 7, происходит установка последнего (Эпюры 9 на фиг.2 и 3). Если до первого дополнительного импульса поступило четное количество основных импульсов, то триггер 7 устанавливается в состояние Лог.О (эпюра 9 на фиг.2). Задним фронтом первого дополнительного импульса D-триггер 8 в соответствии с постоянным уровнем Лог.1 на его D-входе, устанавливается по инверсному входу в состояние Лог.О. Тем самым элемент 14 И закрывается, последующие дополнительные импульсы не оказывают влияния на состояние триггера 7, равно как и на состояние триггера 8,

Если до первого дополнительного импульса поступило нечетное количество основных импульсов (эпюры 4 и 5 на фиг.З), то триггер 7 дополнительным импульсом устанавливается в состояние Лог. 1 (эпюра 9 на фиг.З). Блокирование этого состояния происходит аналогично вышеописанному.

По окончании поступления информации на вход 1 устройства через время (2, 5...3) Т на выходах распределителя 3 (фиг.4в) вырабатывается два управляющих сигнала. Первый импульсный сигнач через

дифференцирующую цепь 30 (выход 1) устанавливает в состояние Лог.О триггер 6, второй потенциальный (выход П) устанавливает в состояние Лог.О триггер 8. Устройство приходит в исходное состояние.

Считывание информации из блока 9 оперативной памяти происходит после окончания поступления информации путем запуска генератора 16 импульсов сигналом со второго выхода распределителя 4. Блок 9 оперативной памяти при этом переходит в режим считывания. На тактирующий вход блока 9, а также через элемент задержки 12 на счетный вход счетчика 15 адресов поступают импульсы с выхода элемента 13, в результате чего с выхода блока 9 осуществляется считывание записанной информации через элемент 10 ИСКЛЮЧАЮЩЕЕ ИЛИ.

В зависимости от состояния триггера 7 происходит выдача данных с элемента 10 либо в прямом коде, как они записаны в блоке 9, либо в обратном. Последний случай соответствует записи данных в блок 9 в обратном коде (эпюра 10 на фиг.З). После двойного .преобразования информация на выходе устройстве появляется в прямом ко- Де.

На выходы 18 и 20 устройства поступают также соответственно импульсы с выхода генератора 16, необходимые для стробирования считанной из блока 9 оперативной памяти информации для последующей ее обработки, а также сигнал переполнения счетчика 15 адресов, служащий для определения начала многократно считываемой из блока 9 инфбрмации,

Таким образом, независимо от того, с какого начального уровня стала поступать информация в коде Манчестер-2, предлагаемое устройство обеспечивает выдачу без потерь в полном объеме в прямом коде передаваемую информацию. В этом заключается технико-экономические преимущества предлагаемого устройства для декодирования кода Манчестер-2 по сравнению с прототипом и другими аналогичными решениями.

Формула изобретения Устройство для декодирования кода Манчестер-2, содержащее первый-третий триггеры, выход третьего триггера соединен

с входом первого элемента задержки, второй элемент задержки, элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и счетчик, отличающееся тем, что, с целью повышения

достоверности декодирования за счет уменьшения потерь информации, в устройство введены блок оперативной памяти, распределитель импульсов, генератор импульсов, формирователи импульсов, элементы ИЛИ и детектор переходов, вход которого объединен с информационным входом блока оперативной памяти и является.входом устройства, выход детектора переходов подключен к первому входу

первого элемента ИЛИ, входу распределителя импульсов и входу первого формирователя импульсов, выход которого соединен с вторым входом первого элемента ИЛИ, первым входом элемента И и С-входом третьего

триггера, D-вход которого подключен к источнику логической единицы,выход первого элемента задержки соединен с вторым входом элемента И, выход которого подключен к С-входу второго триггера, выход которого

соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента ИЛИ соединен с С-входом первого триггера, первый выход распределителя импульсов подключен к R-входу первого

триггера/выход которого соединен с D-вхо- дом второго триггера и входом второго формирователя импульсов, выход которого подключен к первому входу второго элемента ИЛИ, выход которого непосредственно и

через второй элемент задержки соединен соответственно с тактовым входом блока оперативной памяти и счетным входом счетчика, второй выход распределителя импульсов подключен к входу выбора режима

блока оперативной памяти и входу генератора импульсов, выход которого соединен с вторым входом второго элемента ИЛИ и является тактовым выходом устройства, третий выход распределителя импульсов

подключен к входу обнуления счетчика, разрядные выходы которого соединены с адресными входами блока оперативной памяти, выход которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,

выход которого является информационным выходом устройства, выход переполнения счетчика является выходом синхронизации устройства.

p#&3

fi + Угге/т W

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения изображения на матричном экране | 1987 |

|

SU1596487A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| Устройство для контроля блоков оперативной памяти | 1989 |

|

SU1689994A2 |

| Устройство для селекции изображений объектов | 1989 |

|

SU1777651A3 |

| Устройство для записи информации в оперативную память | 1990 |

|

SU1751811A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| Устройство для контроля программ | 1987 |

|

SU1418720A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Способ передачи-приема информации и устройство для его осуществления | 1989 |

|

SU1783630A1 |

Изобретение относится к вычислительной технике. Его использование в сетях передачи и приема данных позволяет повысить достоверность декодирования за счет исключения потерь информации. Устройство содержит триггеры 6-8, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10; элементы 11,12 задержки, элемент И 14 и счетчик 15. Благодаря введению детектора 2 переходов, формирователей 3,17 импульсов, распределителя 4 импульсов, элементов ИЛИ 5, 13, блока 9 оперативной памяти и генератора 16 импульсов в устройстве обеспечивается исключение потерь информации до первого интервала длительностью 2Т во входном сигнале.4 ил.

Редактор

Составитель Л.Олышевская

Техред М.МоргенталКорректор Л.Ливринц

JTffi X.

фие.Ь

| Устройство для декодирования манчестерского кода | 1986 |

|

SU1383510A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 4862482, кл.Н 03 М 5/12, олублик | |||

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1993-04-15—Публикация

1990-11-23—Подача