Изобретение относится к электроизмерительной и вычислительной технике и може т использоваться в информационно-измерительных системах, системах передачи информации и т.п.

Цель изобретения - повьшгение быст- родействия при сохранении высокой точности преобразования.

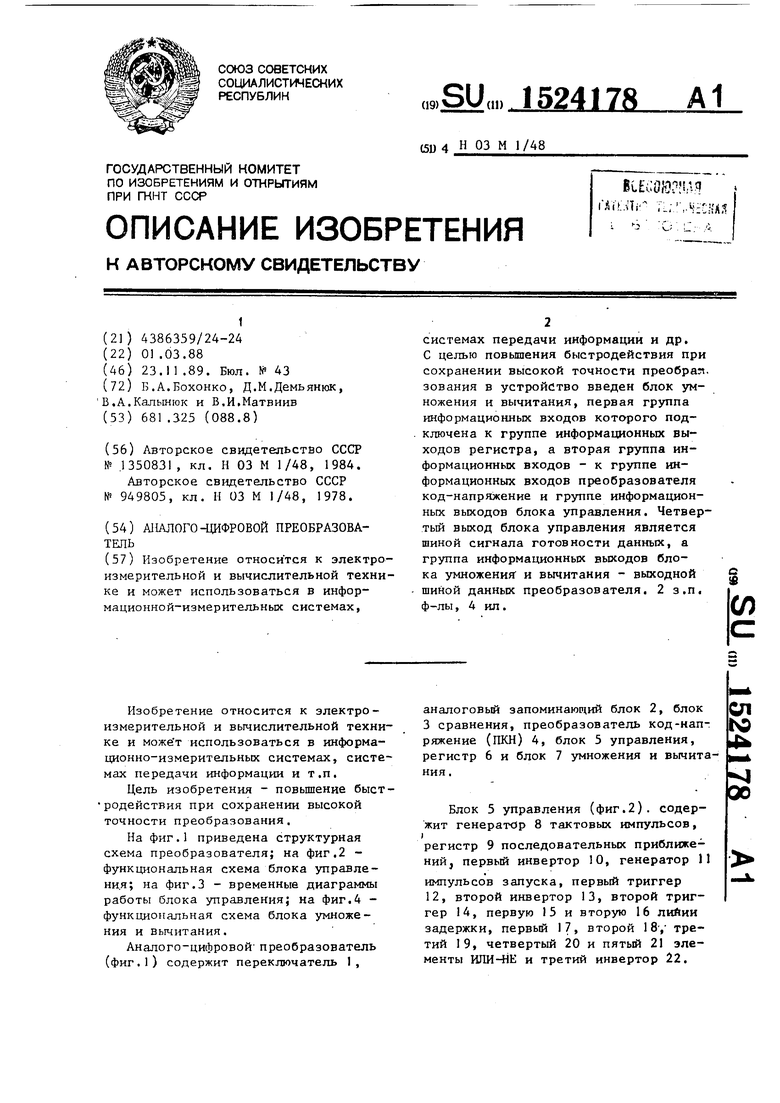

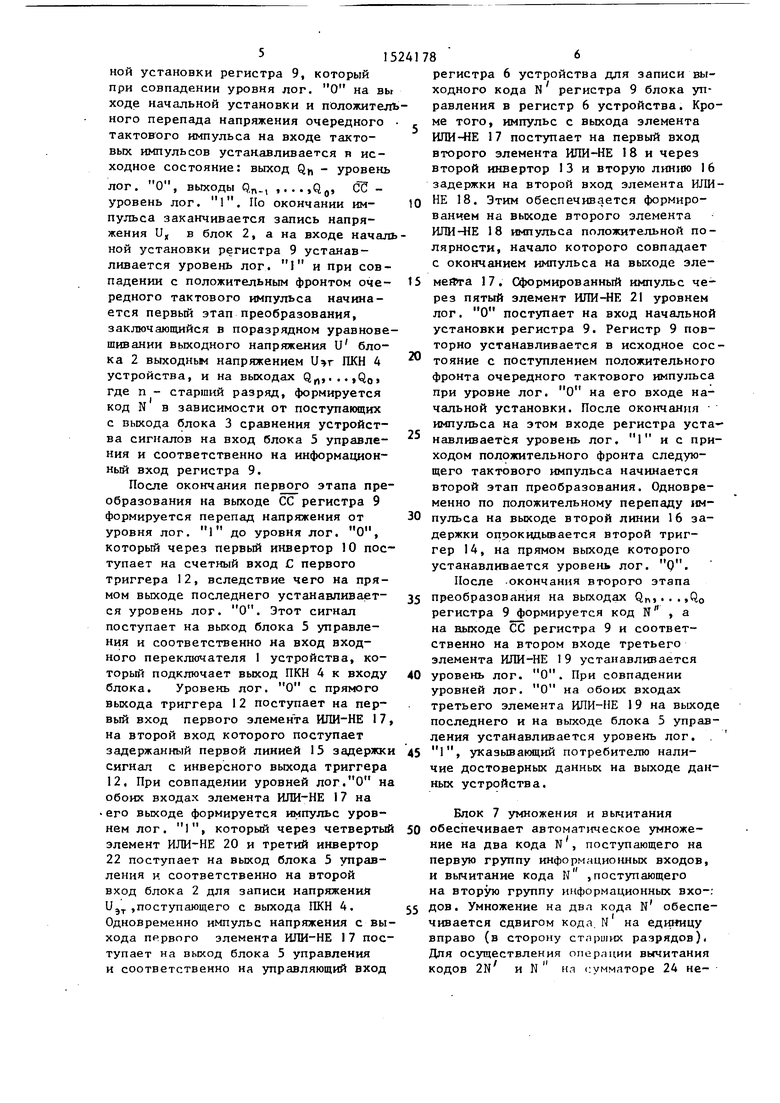

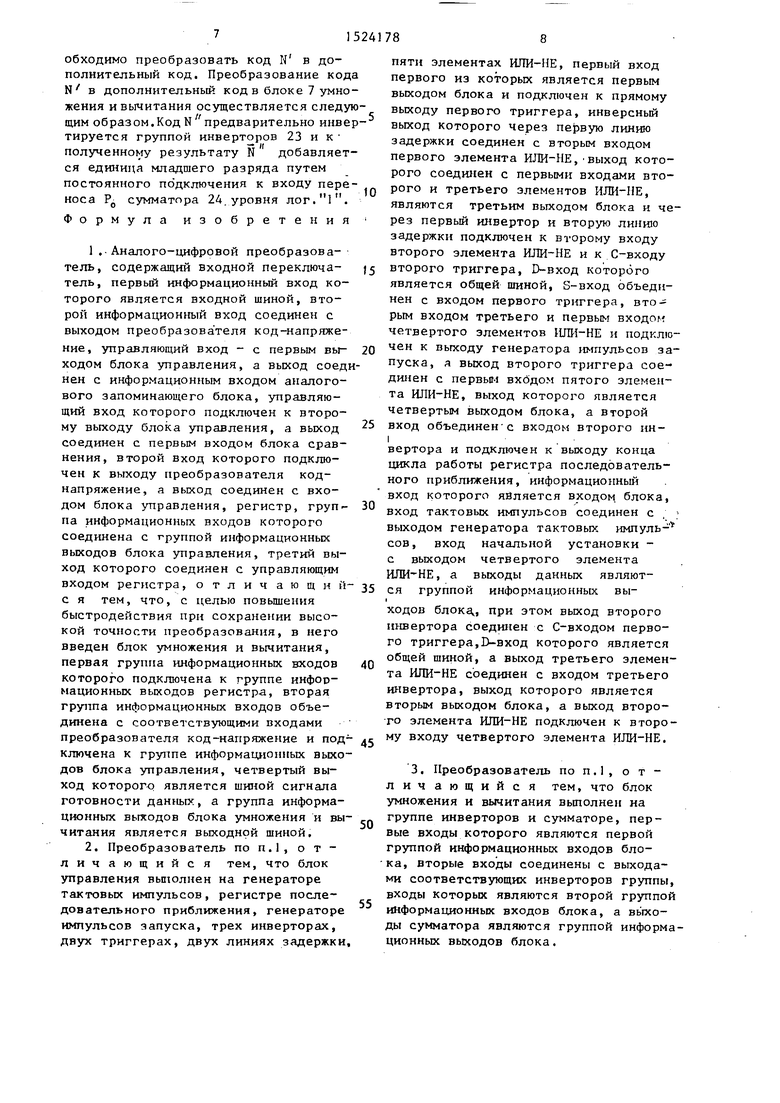

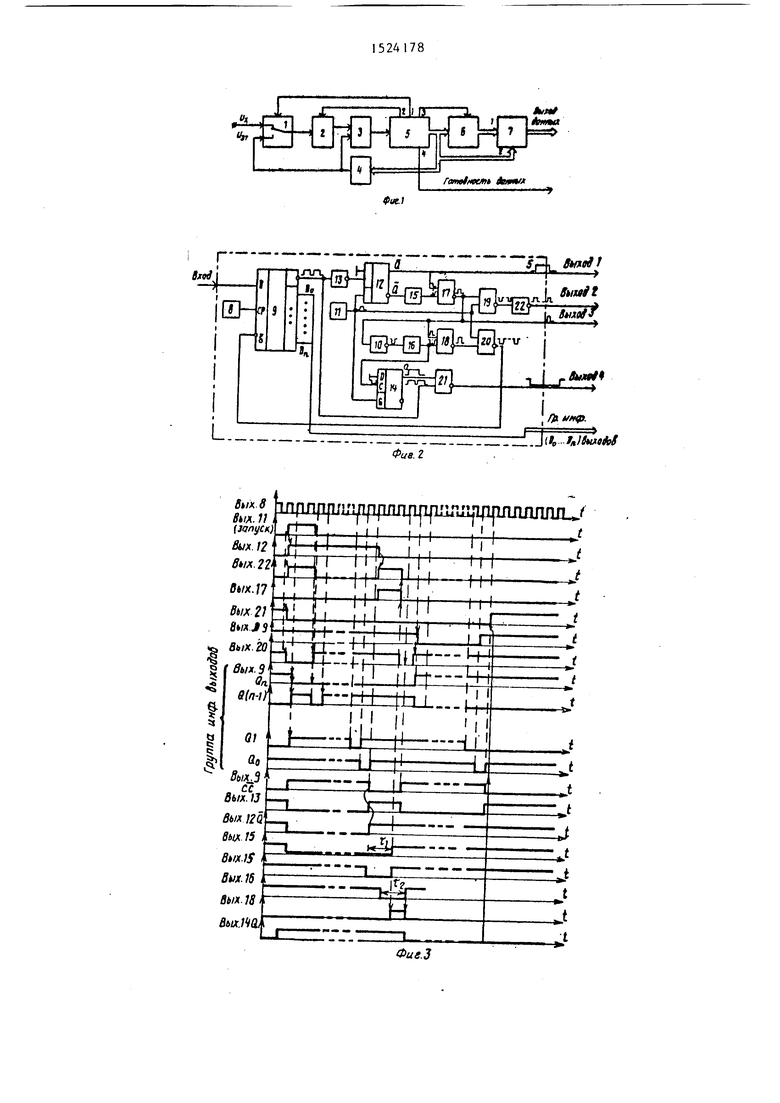

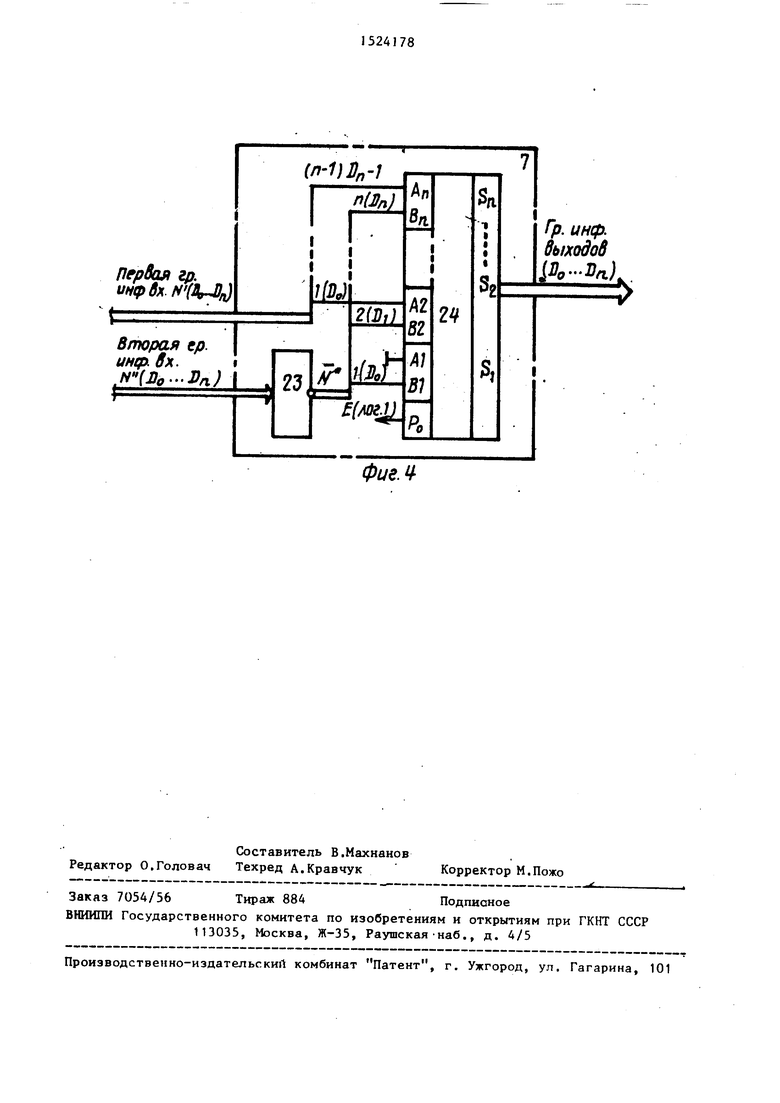

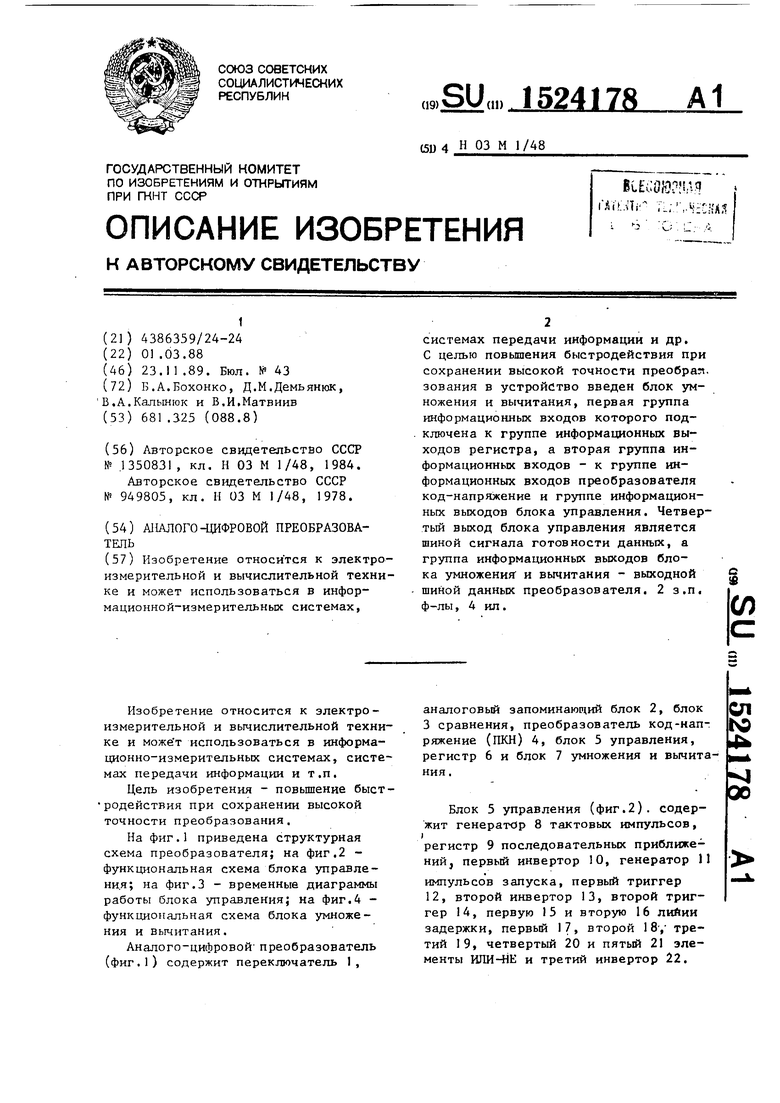

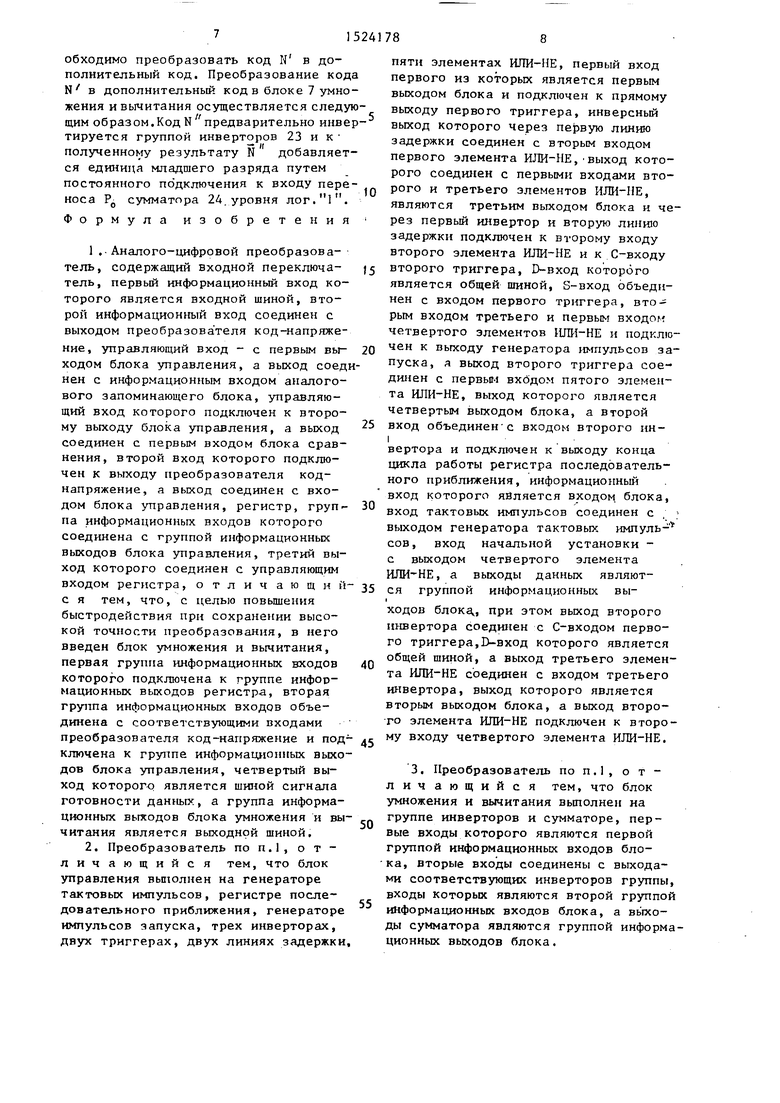

На фиг.1 приведена структурная схема преобразователя; на фиг.2 - функциональная схема блока управления; на фиг.З - временные диаграммы работы блока управления} на фиг.4 - функциональная схема блока умножения и вычитания.

Аналого-цифровой преобразователь (фиг.1) содержит переключатель 1,

аналоговый запоминаюп ий блок 2, блок 3 сравнения, преобразователь код-напряжение (ПКН) 4, блок 5 управления, регистр 6 и блок 7 умножения и вычитания.

Блок 5 управления (фиг.2). содержит генератор 8 тактовых импульсов, регистр 9 последовательных приближений, первый инвертор 10, генератор 11

импульсов запуска, первый триггер 12, второй инвертор 13, второй триггер 14, первую 15 и вторую 16 лийии задержки, первый 17, второй 18,- третий 19, четвертый 20 и пятый 21 элементы ИЛИ-НК и третий инвертор 22.

Блок 7 умножения и вычитания (фиг.4) содержит группу инверторов 23 и сумматор 24.

Преобразователь работает следующим образом.

В начале цикла преобразования по команде блока 5 управления в аналоговом запоминающем блоке 2 производится

запоминание напряжения

и (и, + ли.)(к + &к),

На втором этапе цикла кодирования осуществляется процесс поразрядного уравновешивания выходного напряжения и блока, в результате которого на выходе регистра блока 5 управления устанавливается код N . Его эквивалентное значение равно

II И

и.кб

+ ли и,

+ 2-Лил +

+ 2 к Ux + 2 ьи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1589395A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2005 |

|

RU2286012C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2003 |

|

RU2240651C1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2004 |

|

RU2270519C1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1125643A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Устройство для телединамометрирования глубинно-насосных скважин | 1990 |

|

SU1797131A1 |

| Преобразователь напряжение-код сКОНТРОлЕМ | 1979 |

|

SU822342A1 |

Изобретение относится к электроизмерительной и вычислительной технике и может использоваться в информационно-измерительных системах, системах передачи информации и др. С целью повышения быстродействия при сохранении высокой точности преобразования в устройство введен блок умножения и вычитания, первая группа информационных входов которого подключена к группе информационных выходов регистра, а вторая группа информационных входов - к группе информационных входов преобразователя код-напряжение и группе информационных выходов блока управления. Четвертый выход блока управления является шиной сигнала готовности данных, а группа информационных выходов блока умножения и вычитания - выходной шиной данных преобразователя. 2 з.п. ф-лы, 4 ил.

- мгновенное значение входного сигнала;15 - напряжение смещения блока 2; - коэффициент передачи блока 2; - погрешность коэфф1щиента

передачи блока 2. 20 К 1, то

и и + uUft ч- ЬК и, .

Результат запоминания поступает на первый сход блока 2 сравнения, где сравнивается с выходным напряжением.U. ПКН4, поступающим на вход блока 3 сравнения, в процессе поразрядного уравновешивания. После завершения процесса поразрядного уравновешивания код N с регистра блока 5 управления переписьюается в регистр 6, в котором до конца цикла преобразования сохраняется код N . Одновременно входной переключатель подключает к входу блока 2 выходное напряжение ИКН 4, эквивалентное коду N и равное (без учета погрешности ПКН)

эт и

ли с

где MJ{. - напряжение смещения блока сравнения.

(

По команде блока 5 управления производится запоминание выходного напряжения ПКН 4 в аналоговом запоми- нающем блоке 2, на вькоде которого устанавливается напряжение

и (иэт + &Uft)(l+uK) и,+ Л.ид + &К UjT

или

и - Ux + 2uUft + 2 &К и + AUe .

в блоке 7 умножения и вычитания осуществляется умножение на два выходного кода N регистра 6 и вычитание выходного кода N регистра блока 5 управления. На выходе данных блока 7 умножения и вычитания устанав ливается код N 2н - N , эквивалентное значение

U5K6 2 - и,.6 - Ux

5

0

5

0

5

0

5

Блок 5 управления работает следующим образом (фиг.3)|

С выхода генератора 8 тактовых импульсов на вход регистра 9 постоянно поступают тактовые импульсы. гистр 9 находится в режиме ожидания до поступления от генератора I1 импульса запуска положительной полярности. При поступлении импульса запус ка по его переднему фронту на прямых выходах первого 12 и второго 14 триггеров вырабатьшаются напряжения уровнем лог.1. Сигнал уровнем лог. М с прямого выхода первого триггера, являющегося первым выходом блока 5 управления, поступает на вход входного переключателя 1 устройства (фиг.2), который подключает к входу блока 2 напряжение U. Сигнал уровнем лог. 1 с выхода второго триггера 14 поступает на первый вход третьего элемента ИЛИ-НЕ 19,на выходе которого и на выходе блока 5 управления вьфабатьшается напряжение уровнем лог.О, информирующем потребителя о начале нового цикла преобразования. Одновременно импульс запуска через элемент ИЛИ-НЕ 20 и инвертор 22 поступает на выход блока 5 управления и на второй вход блока 2 устройства для записи мгновенного значения в блок.

Кроме того, импульсы запуска через пятый элемент 21 уровнем лог. О поступает на вход начальной установки регистра 9, который при совпадении уровня лог. О на вы ходе начальной установки и положителного перепада напряжения очередного тактокого импульса на входе тактовых импульсов устанавливается в исходное состояние: выход Qj, - уровень лог. О, выходы Q, ,...,Q|j, СС - уровень лог. 1. По окончании импульса заканчивается запись напряжения и в блок 2, а на входе началной установки регистра 9 устанавливается уровень лог. I и при совпадении с положительным фронтом очередного тактового импульса начинается первый этап преобразования, заключающийся в поразрядном уравновешивании выходного напряжения U блока 2 выходньм напряжением ПКН 4 устройства, и на выходах Qrt,...,Qo. где п - старший разряд, формируется код N в зависимости от поступающих с выхода блока 3 сравнения устройства сигналов на вход блока 5 управления и соответственно на информационный вход регистра 9.

После окончания первого этапа преобразования на выходе СС регистра 9 формируется перепад напряжения от уровня лог. 1 до уровня лог. О, которьй через первый инвертор 10 поступает на счетный вход С первого триггера 12, вследствие чего на прямом выходе последнего устанавливается уровень лог. О. Этот сигнал поступает на выход блока 5 управления и соответственно на вход входного переключателя 1 устройства, ко- торьй подключает выход ПКН 4 к входу блока. Уровень лог. О с прямого выхода триггера 12 поступает на первый вход первого элемента ИЛИ-НЕ 17 на второй вход которого поступает задержанный первой линией 15 задержки сигнал с инверсного выхода триггера 12. При совпадении уровней лог.О на обоих входах элемента ИЛИ-НЕ 17 на его выходе формируется импульс уровнем лог. 1, который через четвертьй элемент ИЛИ-НЕ 20 и третий инвертор 22 поступает на выход блока 5 управления и соответственно на второй вход блока 2 для записи напряжения и, ,поступающего с вьпсода ПКН 4. Одновременно импульс иапряжения с выхода первого элемента ИЛИ-НЕ 17 поступает на выход блока 5 управления и соответственно на управляющий вход

0

регистра 6 устройства для записи выходного кода N регистра 9 блока управления в регистр 6 устройства. Кроме того, импульс с выхода элемента ИЛИ-НЕ 17 поступает на первый вход второго элемента ШШ-НЕ 18 и через второй инвертор 13 и вторую линию 16 задержки на второй вход элемента ИЛИ- 0 НЕ 18. Этим обеспечивается формированием на выходе второго элемента Rra4iE 18 импульса положительной полярности, начало которого совпадает с окончанием импульса на выходе эле5 меЯ1та 17. Сформированный импульс через пятый элемент ИЛИ-НЕ 21 уровнем лог. О поступает на вход начальной установки регистра 9. Регистр 9 повторно устанавливается в исходное состояние с поступлением положительного фронта очередного тактового импульса при уровне лог. О на его входе начальной установки. После окончания импульса на этом входе регистра уста-

навливается уровень лог. 1 и с приходом положительного фронта следующего тактового импульса начинается второй этап преобразования. Одновременно по положительному перепаду им0 пульса на выходе второй линии 16 задержки опрокидьшается второй триггер 14, на прямом выходе которого устанавливается уровень лог. О. После .окончания второго этапа

5 преобразования на выходах ..,Qo регистра 9 формируется код N , а на выходе СС регистра 9 и соответственно на втором входе третьего элемента ИЛИ-НЕ 19 устанавливается

0 уровень лог. О. При совпадении уровней лог. О на обоих входах третьего элемента ИЛИ-НЕ 19 на выходе последнего и на выходе блока 5 управления устанавливается уровень лог, .

5 1, указьшающий потребителю наличие достоверных данных на выходе данных устройства.

Блок 7 умножения и вычитания 0 обеспечивает автоматическое умножение на два кода N , поступающего на первую группу информацио1шых входов, и вычитание кода N ,поступающего на вторую группу информационных вхо-; 5 дов. Умножение на дал кода N обеспечивается сдвигом кода. N на единицу вправо (в сторону стпрших разрядов), Для осуществления операции вычитания кодов 2N и N на сумматоре 24 необходимо преобразовать код N в дополнительный код. Преобразование кода N в дополнительный код в блоке 7 умножения и вычитания осуществляется следующим образом.Код N предварительно инвертируется группой инверторов 23 и к полученному результату N добавляется единица младшего разряда путем постоянного по дключения к входу пере

носа Рд сумматора 2А уровня лог. М.

Формула изобретения

му выходу блока управления, а выход

соединен с первым входом блока сравнения, второй вход которого подключен к выходу преобразователя код- напряжение, а выход соединен с входом блока управления, регистр, груп- па информационных входов которого соединена с т руппой информационных выходов блока управления, третий выход которого соединен с управляющим входом регистра, о т л и ч а ю щ и й с я тем, что, с целью повьшения быстродействия при сохранении высокой точности преобразования, в него введен блок умножения и вычитания, первая группа информационных входов которого подключена к группе информационных выходов регистра, вторая группа информационных входов объединена с соответствующими входами преобразователя код-напряжение и под ключена к группе информационных выходов блока управления, четвертый выход которого является шиной сигнала готовности данных, а группа информационных выходов блока умножения и вычитания является выходной шиной.

0

5 0

5

0 5 0 5

0

5

пяти элементах ШТИ-НЕ, первый вход первого из которых является первым выходом блока и подключен к прямому выходу первого триггера, инверсный выход которого через линию задержки соединен с вторым входом первого элемента ИЛИ-НЕ,выход которого соединен с первьми входами второго и третьего элементов ИЛИ-НЕ, являются третьим выходом блока и через первьй инвертор и вторую линию задержки подключен к второму входу второго элемента ИЛИ-НЕ и к С-входу второго триггера, D-вход которого является общей шиной, S-вход объединен с входом первого триггера, вторым входом третьего и первым входом четвертого элементов ИЛИ-НЕ и подключен к выходу генератора импупъсоп запуска, я выход второго триггера соединен с первьп- вхбдом пятого элемента ИЛИ-НЕ, выход которого является четвертым выходом блока, а второй вход объединен с входом второго ин- I

вертора и подключен к выходу конца

цикла работы регистра последовательного приближения, информационный вход которого является входом, блока, вход тактовьк импульсов соединен с . выходом генератора тактовых импуль- сов, вход начальной установки - с выходом четвертого элемента ИЛИ-НЕ, а выходы данных являются группой информационных выходов блок, при этом выход второго и шертора соединен с С-входом первого триггера,D-вход которого является общей шиной, а выход третьего элемента ИЛИ-НЕ соединен с входом третьего инвертора, выход которого является вторым выходом блока, а выход второго элемента ИЛИ-НЕ подключен к второму входу четвертого элемента ИЛИ-НЕ.

Вил 8

Л/л. 7/ {мпуси

Sux.t2 вш. 22

Вых.П

Л/х7/

g .20

гЛ/х5 «а S(a-i)

f ч

I

б/

fle

А%5

Bi/xKQ Вьщ15

Bt/x.Jf BM.JS Выи-18 ВЫХ.1Ч&,

1ым

AwtKt

ewrit

/ J(I,...A/AM# /

фиеЛ

| Авторское свидетельство СССР № ,1350831, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU949805A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-23—Публикация

1988-03-01—Подача