Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных вычислительных устройств, предназначенных для сортировки массивов данных в реальном масштабе времени.

Известно устройство для выделения экстремельного из N m-разрядных двоичных чисел, содержащее матрицу ячеек, каждая из которых содержит элементы И, ИЛИ, элементы запрета 1.

Недостатком данного устройства является его сложность.

Другое устройство для выделения экстремального из N m-разрядных двоичных чисел содержит N m-разрядных регистров, групп элементов И, m-входовых элементов

ИЛИ, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. триггеров, N-входовый элемент ИЛИ, шины управления поразрядным сравнением 2.

Недостатком устройства является его сложность.

Наиболее близким является устройство

для сортировки чисел, содержащее }-г яче2

ек анализа i-ro типа (N - количество сортируемых чисел, i 1,2 log2N, Х ближайшее целое, не меньшее X), счетчик, log2N -1 формирователей импульсов, вход начальной установки, тактовый вход, информационные входы, выходы отсортированных чисел, выход окончания работы, ячейка анализа i-ro типа содержит две группы регистров, элементы сравнения, коммуVI

о. ю

CJ

2

таторы, входы управления записью, информационные входы и выходы 3.

Недостатком этого устройства является его сложность.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что устройство, содержащее r log2N ступеней ячеек анализа (N - количество сравниваемых чисел, Х - ближайшее целое, не меньшее X), i-ая группа ячеек анализа (1 1,2

г) содержит 1-г ячеек анализа, вход j-ro 2

числа устройства (j.1, 2,..., N) соединен с (2 - mod2J)-biM информационным входом| -ой ячейки анализа первой ступени, выход -ой ячейки анализа k-ой ступени (I 1, 2

-г, k 1,2г-1) соединен с (2-mod2l)-biM

2k

информационным входом } -ой ячейки

анализа (к+1)-ой ступени, входы начальной установки ячеек анализа первой ступени соединены с первым управляющим входом устройства, тактовый вход устройства соединен с тактовыми входами всех ячеек анализа нечетных ступеней, выход r-ой ступени ячеек анализа является выходом устройства, каждая ячейка анализа содержит два триггера и коммутатор, отличающееся тем, что, с целью упрощения устройства, оно содержит элемент НЕ, а каждая ячейка анализа - третий триггер, элемент ИЛИ и три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем (к+1)-ый управляющий вход устройства соединен со входами начальной установки всех ячеек анализа (к+1)-ой ступени, тактовый вход устройства через элемент НЕ соединен с тактовыми входами всех ячеек анализа четных ступеней, i-ый вход синхросигнала передачи знаков чисел соединен со входами синхронизации первых триггеров всех ячеек анализа i-ой ступе- ни, вход выбора режима устройства соединен с первыми входами первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ всех ячеек анализа, в каждой ячейке анализа ее вход начальной установки соединен со входом установки в единичное состояние первого триггера и со входом установки в нулевое состояние второго триггера, выход которого соединен со входом синхронизации третьего триггера, выход которого соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с управляющим входом коммутатора, выход которого является выходом ячейки анализа, первый и второй информационные входы ячейки анализа соединены соответственно

с первым и вторым информационными входами коммутатора, первым и вторым входами элемента ИЛИ и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен со входом установки в единичное состояние второго триггера, информационный вход третьего триггера соединен с выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены соответственно с первым информационным входом ячейки анализа и инверсным выходом первого триггера, информационный вход которого соединен с выходом элемента ИЛИ.

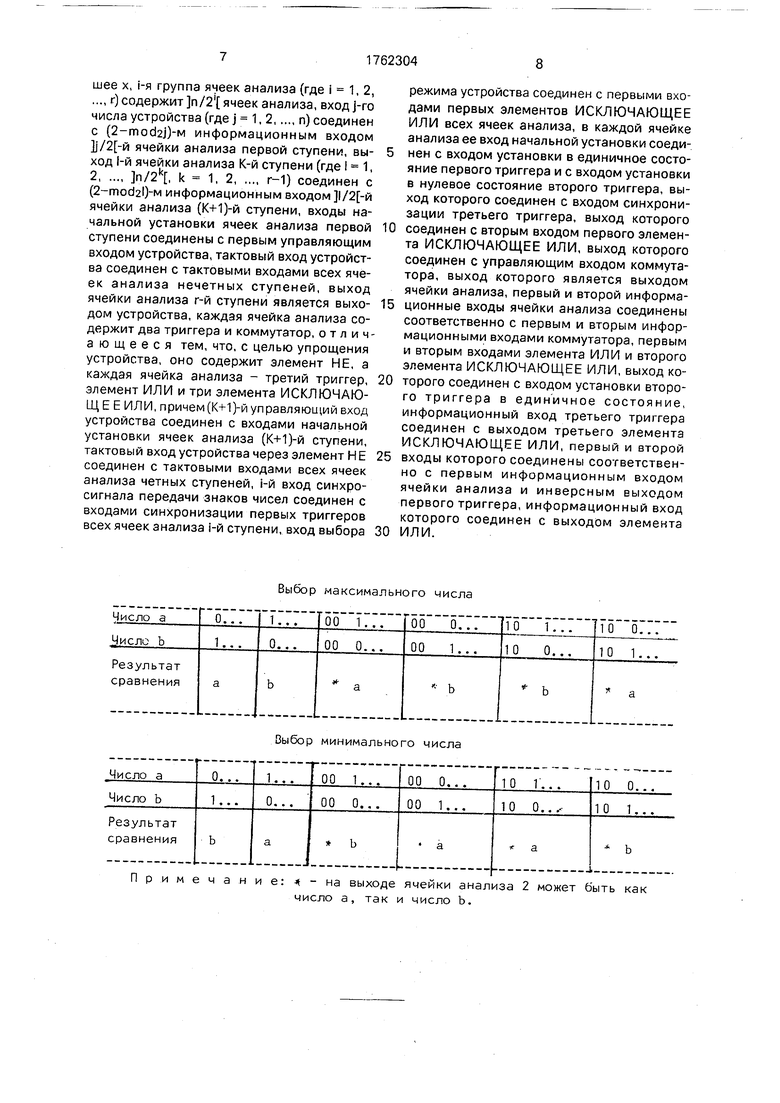

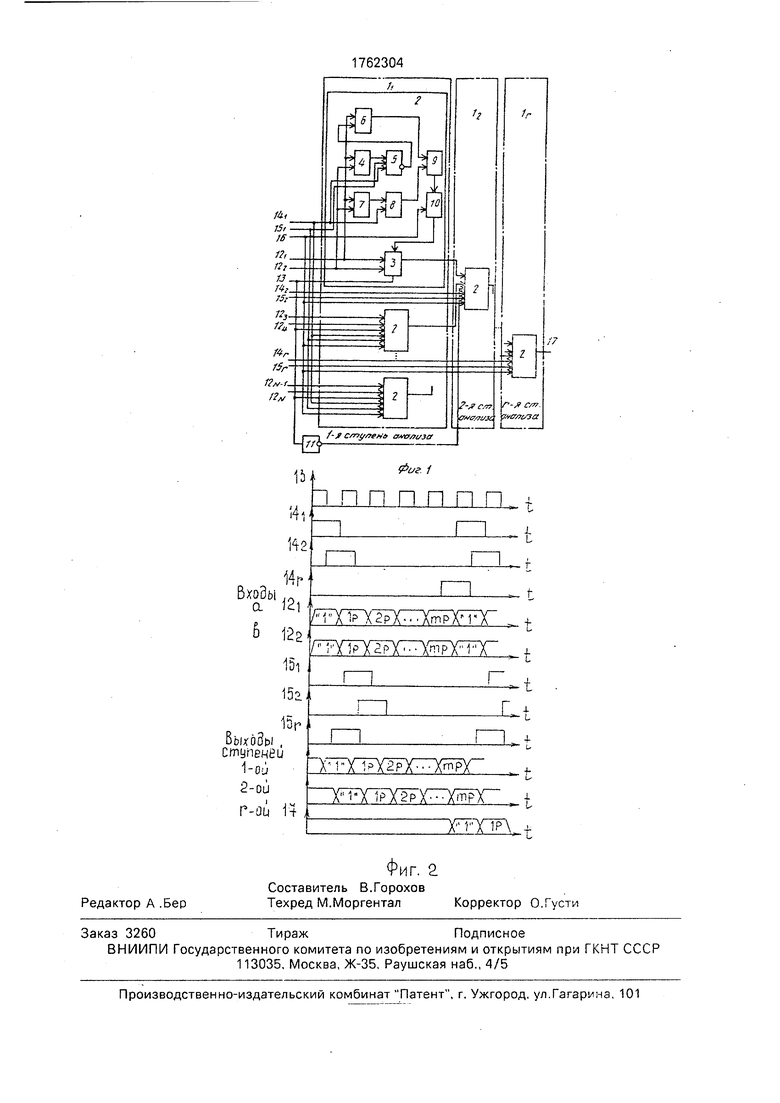

На фиг.1 представлена функциональная схема устройства; на фиг.2 - временные диаграммы его работы.

Устройство для выделения экстремального числа содержит г log2N ступеней 1

ячеек анализа (N - количество сравниваемых чисел, Х - ближайшее целое, не меньшее X), i-ая группа ячеек анализа (, 2

г) содержит }-т ячеек анализа 2, каждая

ячейка анализа 2 содержит коммутатор 3, элемент ИЛИ 4, первый триггер 5, третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, второй триггер 8, третий триггер 9, первый элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ 10, кроме того, устройство содержит элемент НЕ 11, N входов чисел 12, тактовый вход 13, управляющие входы 14, входы синхросигнала передачи знаков чисел 15, вход выбора режима 16,

выход 17 устройства.

Устройство работает следующим образом.

На входы чисел 12 устройства сравниваемые m-разрядные числа поступают прямым последовательным кодом, начиная со старших разрядов, старший разряд - знаковый.

Каждая ячейка анализа 2 производит выделение экстремального из пары чисел а

и b в соответствии с табл.

Рассмотрим работу ячейки анализа 2 для режима выделения максимального числа (на вход выбора режима 16 устройства подается О).

Перед началом сравнения пары т-раз- рядных чисел импульсом единичного уровня, поступающим с соответствующего управляющего входа 14, устройства, триггер 5 устанавливается в О), триггер 8 устанавливается в О. В это время на первом и втором информационных входах 12i и 122 ячейки анализа 2 соответственно присутствует единичный уровень и на тактовом входе 13 устройства также единичный уровень.

Триггер 9 сохраняет предыдущее состояние. Сигнал с выхода триггера 9 через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10 без изменения поступает на управляющий вход коммутатора 3. На выход коммутатора 3 будет передаваться 1 либо с первого, либо со второго информационного входа коммутатора 3 (в зависимости от предыдущего .состояния триггера 9) по отрицательному перепаду сигнала, поступающего с тактового входа 13 устройства. При появлении сравниваемых чисел а и b на первом и втором информационных входах 12i и 12а соответственно (при этом на тактовом входе 13 устройства - единичный уровень) производится, начиная со старшего разряда, последовательный поразрядный анализ исследуемых чисел, Пусть в старшем разряде чисел имеется неравенство. При этом на выходе элемента ИЛИ 4 устанавливается 1, которая поступает на информационный вход триггера 5. Во время анализа старших (знаковых) разрядов сравниваемых чисел а и b на вход синхронизации триггера 5 поступает импульс единичного уровня с соответствующего входа синхросигнала передачи знаков чисел 15i устройства. По положительному перепаду синхросигнала передачи знаков чисел, поступающего на вход синхронизации триггера 5 со входа 15ч устройства, триггер 5 на инверсном выходе сохраняет О, который поступает на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6. При этом на выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 передается число а с первого информационного входа 12.,. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 устанавливается 1, которая поступает на вход установки в единичное состояние триггера 8, на выходе которого появляется 1. По этому положительному перепаду в триггер 9 производится запись знакового разряда числа а. Сигнал с выхода триггера 9 через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10 без изменения поступает на управляющий вход коммутатора 3. Если значение знакового разряда числа а равно 0, триггер 9 устанавливается в О и на выход коммутатора 3 по отрицательным перепадам сигнала, поступающего с тактового входа 13 устройства на тактовый вход коммутатора 3, передается число а; если в старшем разряде числа 1 - то число Ь.

В случае, если значения знаковых разрядов чисел а и b равны 1, на инверсном выходе триггера 5 также сохраняется О, при этом выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 повторяет число а. При равенстве значений разрядов чисел а и b триггер 9 сохраняет предыдущее состояние. На выход коммутатора 3 будет передаваться либо число а, либо число b (в зависимости от предыдущего состяония триггера 9). В момент несовпадения разрядов чисел а и b

триггер 8 переключается в 1 по сигналу с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. При переключении триггера 8 из О в 1 производится запись значения разряда числа а в триггер 9. Если значение этого разряда чис0 ла а равно 0, на выход коммутатора 3 передается число а в соответствии с сигналами на управляющем и тактовом входах коммутатора 3; если значение разряда числа а равно 1 - число Ь.

5 В случае, если значения знаковых разрядов чисел а и b равны 0, на выходе элемента ИЛИ 4 устанавливается О, который поступает на информационный вход триггера 5. По положительному перепаду сигнала,

0 поступающего на вход синхронизации триггера 5 со входа 15i устройства, на инверсном выходе триггера 5 устанавливается 1 и на выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 передается инверсное значение числа а.

5 При равенстве значений разрядов чисел а и b триггер 9 сохраняет предыдущее состояние. При этом на выход коммутатора 3 будет передаваться либо число а, либо число b (в зависимости от предыдущего состояния

0 триггера 9). В момент несовпадения разрядов чисел а и b триггер 8 переключается в . 1 по сигналу с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. При переключении триггера 8 из О в 1 производится запись инверсного зна5 чения числа а в триггер 9. Если сигнал на управляющем входе коммутатора 3 - 0, на его выход передается число а, если 1 -число Ь.

Если сравниваемые числа а и b равны,

0 то триггер 9 будет сохранять предыдущее состояние на протяжении всего времени анализа чисел и на выход коммутатора 3 будет передаваться либо число а, либо число Ь.

5Если требуется выделить минимальное

из исследуемых чисел, то на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 со входа выбора режима 16 устройства поступает последовательный поразрядный анализ

0 сравниваемых чисел производится аналогично. Тогда на управляющий вход коммутатора 3 поступает инверсное значение выхода триггера 9, что соответствует передаче на выход коммутатора 3 минимального

5 числа.

Формула изобретения Устройство для выделения экстремального числа, содержащее г log2n ступеней ячеек анализа, где п - количество сравниваемых чисел, х - ближайшее целое, не меньшее х, i-я группа ячеек анализа (где 1 1,2, ..., г) содержит п/2 ячеек анализа, вход j-ro

числа устройства (где j 1, 2п) соединен

с (2-mod2J)-M информационным входом ячейки анализа первой ступени, вы- ход 1-й ячейки анализа К-й ступени (где 1 1,

2 n/2k, k 1, 2 г-1) соединен с

(2-mod2l)-M информационным входом ячейки анализа (К+1)-й ступени, входы начальной установки ячеек анализа первой ступени соединены с первым управляющим входом устройства, тактовый вход устройства соединен с тактовыми входами всех ячеек анализа нечетных ступеней, выход ячейки анализа r-й ступени является выхо- дом устройства, каждая ячейка анализа содержит два триггера и коммутатор, отличающееся тем, что, с целью упрощения устройства, оно содержит элемент НЕ, а каждая ячейка анализа - третий триггер, элемент ИЛИ и три элемента ИСКЛЮЧАЮ- ЩЕ Е ИЛИ, причем(К-И)-й управляющий вход устройства соединен с входами начальной установки ячеек анализа (К+1)-й ступени, тактовый вход устройства через элемент НЕ соединен с тактовыми входами всех ячеек анализа четных ступеней, i-й вход синхросигнала передачи знаков чисел соединен с входами синхронизации первых триггеров всех ячеек анализа i-й ступени, вход выбора

режима устройства соединен с первыми входами первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ всех ячеек анализа, в каждой ячейке анализа ее вход начальной установки соединен с входом установки в единичное состояние первого триггера и с входом установки в нулевое состояние второго триггера, выход которого соединен с входом синхронизации третьего триггера, выход которого соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с управляющим входом коммутатора, выход которого является выходом ячейки анализа, первый и второй информационные входы ячейки анализа соединены соответственно с первым и вторым информационными входами коммутатора, первым и вторым входами элемента ИЛИ и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом установки второго триггера в единичное состояние, информационный вход третьего триггера соединен с выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены соответственно с первым информационным входом ячейки анализа и инверсным выходом первого триггера, информационный вход которого соединен с выходом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Устройство для сортировки двоичных чисел | 1983 |

|

SU1104504A1 |

| Устройство для сортировки чисел | 1988 |

|

SU1644128A1 |

| Устройство для вычисления порядковых статистик последовательностей из @ - @ -разрядных чисел | 1987 |

|

SU1434424A1 |

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - упрощение устройства. Устройство содержит г log2n ступеней 1 ячеек анализа (ЯА) 2, где х - ближайшее целое, не меньшее х, каждая ячейка анализа содержит коммутатор 3, элемент ИЛИ 4, триггеры 5, 8, 9, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 6,7,10, кроме того, устройство содержит элемент НЕ 11, входы чисел 12, тактовый вход 13, управляющие входы 14, входы синхросигнала передачи знаков чисел 15, вход выбора режима 16, выход 17. ЯА 2 соединены в виде бинарного дерева, на входы каждого ЯА подаются два числа прямым последовательным кодом, начиная со старшего разряда, старший разряд - знаковый, из которых ЯА передает на свой выход максимальное или минимальное (в зависимости от режима). В следующем (1+1)-м такте ЯА первой ступени анализируют (1+1)-й разряд всех чисел, а ЯА второй ступени - i-й разряд чисел, выбранных на предыдущем такте ЯА, первой ступени и т. д. 2 ил, 1 табл. сл С

Выбор максимального числа

Выбор минимального числа

Примечание: - на выходе ячейки анализа 2 может быть как

число а, так и число Ь.

| Устройство для сортировки двоичных чисел | 1974 |

|

SU526888A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Устройство для выделения экстремального из @ @ -разрядных двоичных чисел | 1981 |

|

SU966690A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сортировки чисел | 1988 |

|

SU1520509A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-09-15—Публикация

1990-02-28—Подача