единены с тактовым входом блока управления, первый и второй входы анализа режима работы которого соединены с первыми входами первого элемента И и объединены с первыми входами второго, третьего и четвертого элементов И, вторые входы которых и второй вход первого элемента И соединены с выходом первого триггера и являются выходом занятости блока управления, вход знака которого соединен с -входом второго триггера и через первый элемент НЕ с первым входом первого элемента ИЛИ, второй вход Которого соединен с выходом второго элемента И и является выходом сдвига блока управления, вход знака порядка которого соединен через второй элемент НЕ с 5-входом третьего триггера и с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента И и является выходом инкремента блока управления, выход разрешения выдачи которого соединен с выходом четвертого элемента И, третий и четвертьш входы которого соединены соответственно с инверсными входами второго и третьего триггеров, h -входы которых . соединены соответственно с выходами первого и второго элементов ИЛИ, а прямые выходы соединены соответственно с третьими входами второго и третьего элементов И, S - и R -входы первого триггера соединены соответственно с входами разрешения приема и окончания приема блока управления, выход нормализации которого соединен с выходом третьего элемента ИЛИ.

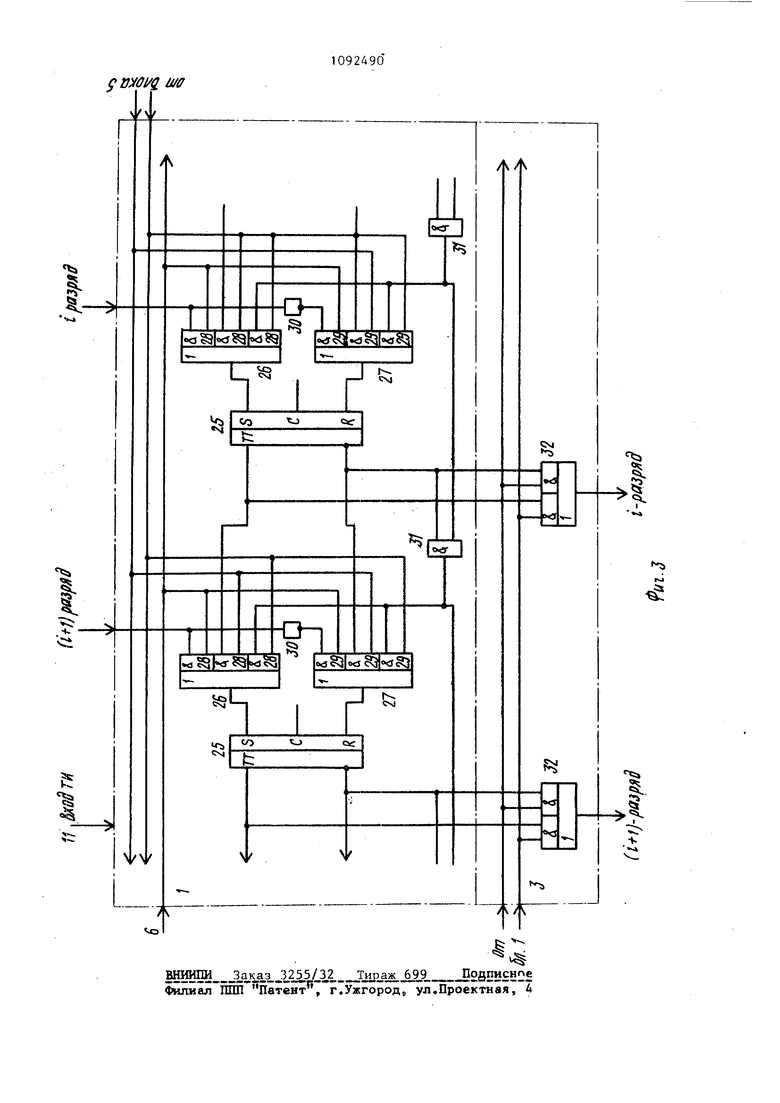

2. Преобразователь по п,1, о т личающийся тем, что в нем блок нормализации мантиссы состоит

из разрядов, первый и второй информационные входы И вход переноса каждого из которых, кроме младшего, соединены с первым и вторым информационными выходами и выходом переноса соседнего младшего разряда, причем каждый разряд блока нормализации мантиссы содержит RS-триггер, два элемента ИЛИ, две группы по три элемента И, элемент НЕ и элемент И,первый вход которого является входом переноса разряда блока нормализации мантиссы, разрядный вход которого соединен с первым входом первого элемента И первой группы и через элемент НЕ с первым входом первого элемента И второй группы, вторые входы первых элементов И первой и второй групп соединены с входом разрешения приема блока нормализации мантиссы, первые входы вторых элементов И первой и второй групп являются прямыми инверсным информационными входами разряда блока нормализации мантиссы, вторые входы вторых элементов И первой и второй групп соединены с входом сдвига блока нормализации мантиссы, вход инкремента которого соедине с первыми входами третьих элементов первой и второй групп, вторые входы которых соединены с выходом элемента И, второй вход которого соединен с последовательным инверсным информационным входом разряда блока нормализации мантиссы, выходы элементов И первой и второй групп соединены с входа1Ш соответствующих элементов ИЛИ, выходы которых соединены соответственно с S- и R -входами триггера, прямой и инверсный выходы которого и выход элемента И являются соответственно последовательными прямым и инверсными информационными выходами и выходом переноса разряда блока нормализации мантиссы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь форматов данных | 1985 |

|

SU1290535A1 |

| Преобразователь форматов данных | 1986 |

|

SU1466012A1 |

| Преобразователь форматов данных | 1985 |

|

SU1418909A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для вычисления функции синуса | 1987 |

|

SU1474642A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

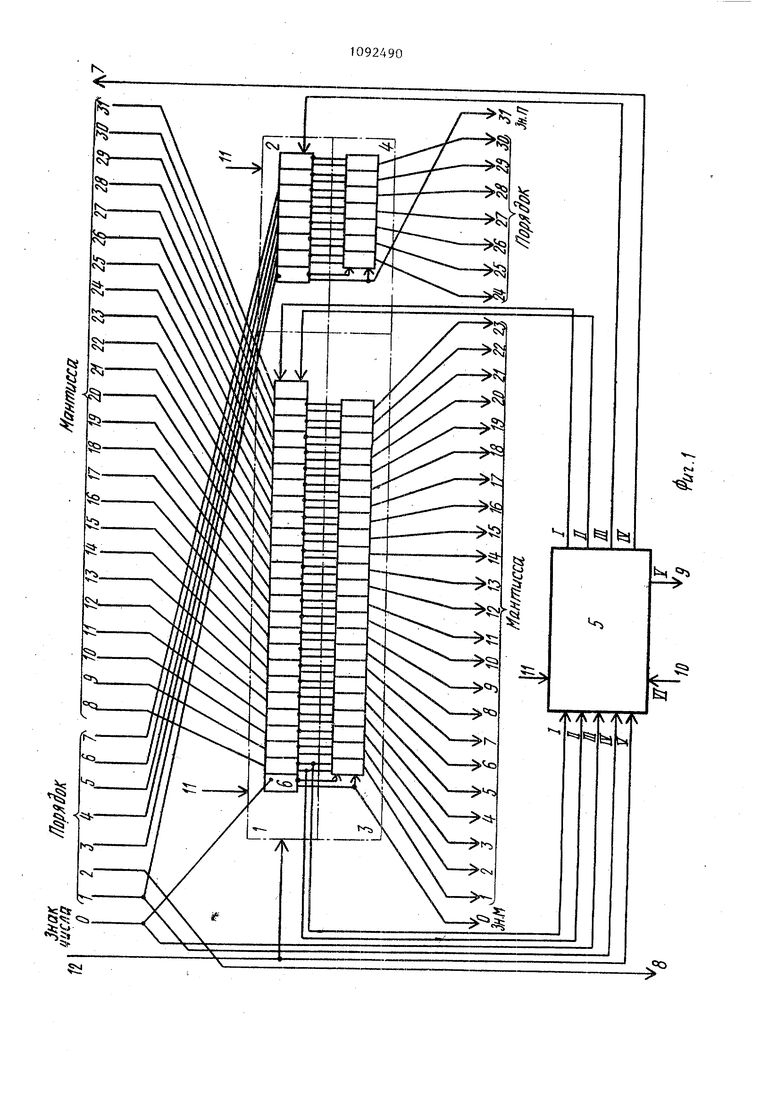

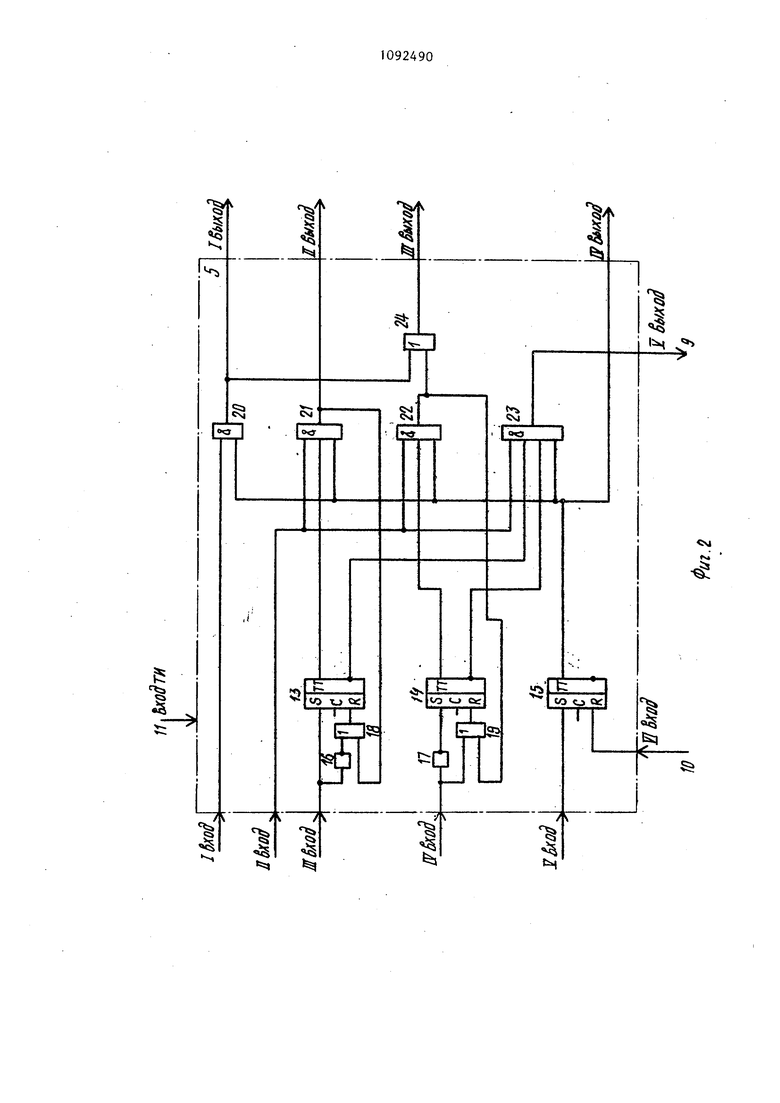

1. ПРЕОБРАЗОВАТЕЛЬ ФОРМАТОВ ДАННЫХ, содержащий блок нормализации мантиссы, счетчик порядка, триггер знака мантиссы и блок управления,тактовый вход которого соединен с тактовыми входами блока нормализации мантиссы и счетчика порядка и является тактовым входом преобразователя, входы мантиссы которого соединены с информационными входами блока нормализации мантиссы, вход триггера знака мантиссы соединен с входом знака преобразователя, входы порядка которого соединены с разрядными входами счетчика порядка, отличающийся тем, что, с целью повьшения быстродействия преобразователя, в него введены коммутатор мантиссы и коммутатор порядка, выходы которых являются выходами мантиссы и выходами порядка преобразователя соответственно, первый и второй управляющие входы коммутатора мантиссы и коммутатора порядка соединены с прямыми и инверсными выходами триггера знака мантиссы и соответственно старшего разряда счетчика порядка, выходы всех, кроме старшего, разрядов которого соединены с разрядными входами коммутатора порядка, разрядные входы коммутатора мантиссы соединены соответственно синформационными выходами всех, кроме младшего, разрядов блока нормализации мантиссы, вход разрешения приема которого соединен с входом разрешения приема блока управления и является входом разрешения приема преобразователя, выходы знака и знака порядка которого соединены соответственно с прямыми выходами триггера знака порядка и старшего разряда счетчика порядка, счетный вход которого соеди нен с выходом нормализации блока уп(Л равления, первый и второй входы анализа режима которого соединены соответственно с прямым и инверсным выходами старшего разряда блока нормализации мантиссы, входы сдвига и инкреfe мента которого соединены соответственно с выходами сдвига и инкременСО та блока управления, выходы заняю тости и разрешения выдачи которого 4: являются соответственно выходами занятости и разрешения вьщачи преобразователя, вход окончания приема которого соединен с входом окончания приема блока управления, входы знака и знака порядка которого соединены соответственно с входами знака и первого разряда порядка преобразователя, вход второго разряда порядка которого является выходом переполнения преобразователя, причем блок управления содержит два элемента НЕ, три элемо.и та ИЛИ, четыре элемента И и три RS-триггера, синхровходы которьк со

1

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении устройств согласования ЭВМ с различными форматами представления данных.

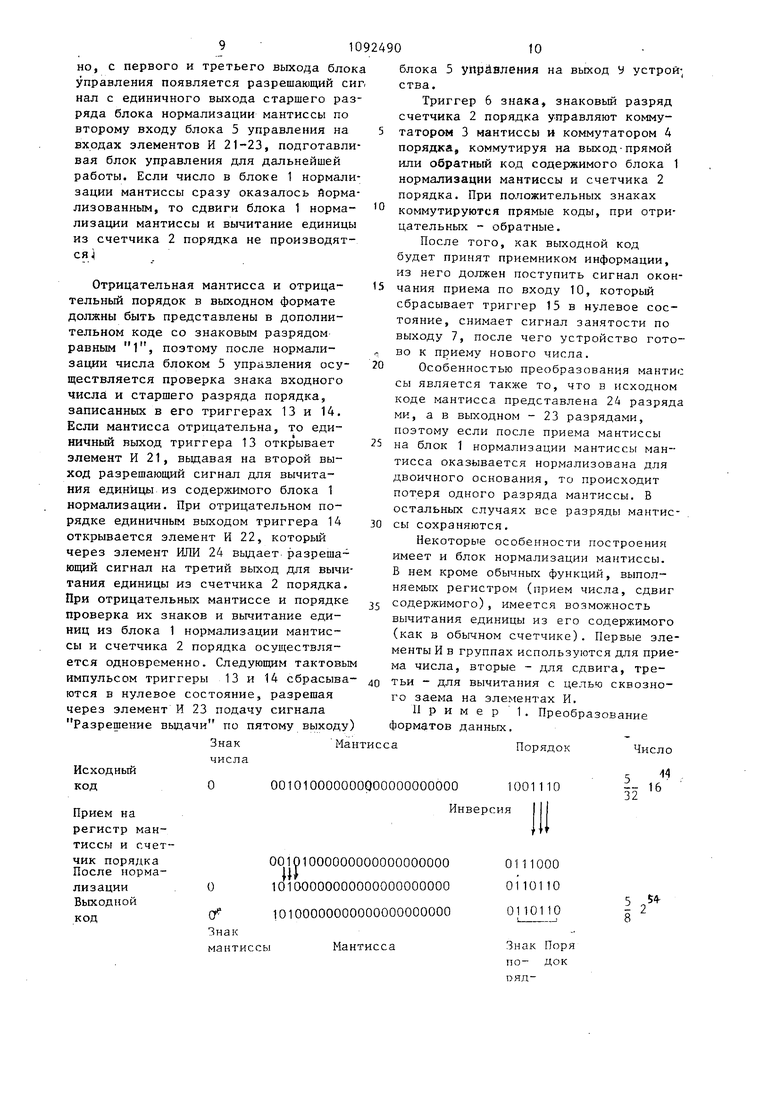

Известен преобразователь форматов данных ,содержаш й регистр мантиссы,регистр порядка,счетчик порядка и сумматор СПНедостатками известного устройст5 ва является невозможность преобраЗования чисел с шестнадцатиричным основанием и большой объем аппаратуры Наиболее близким к предлагаемому является преобразователь форматов данных, содержащий двоичный и десятичный регистры мантиссы, старшую и младшие тетрады десятичного регистра мантиссы, блок коррекции, двоичный и десятичный реверсивные счетчики порядка, дешифраторы нуля двоичного и десятичного реверсивных счетчиков по рядка, дешифраторы нуля двоичного и десятичного регистров мантиссы, дешифраторы прямого и обратного преобразования, блок управления, триггер направления преобразования, генератор тактовых импульсов, выход которого соединен с входами дешифра тора прямого и обратного преобразования, причем тактовый вход блока управления соединен с тактовыми вхо дами регистра мантиссы и счетчика порядка, входы мантиссы преобразова теля соединены с разрядными входами регистра мантиссы 2j.. Недостатками известного преобразователя являются низкое быстродействие и большие аппаратурные затраты Цель изобретения - повышение быст родействия и сокращение аппаратурных затрат. Поставленная цель достигается тем, что в преобразователь форматов данных, содержащий блок нормализации мантиссы, счетчик порядка, триггер знака мантиссы и блок управления, тактовый вход которого соединен с тактовыми входами блока нормализации мантиссы и счетчика порядка и является тактовым входом преобразователя входы мантиссы которого соединены с информационными входами блока нормализации мантиссы, вход триггера знака мантиссы соединен с входом знака преобразователя, входы порядка которого соединены с разрядными входами счетчика порядка, введены коммутатор мантиссы и коммутатор порядка, выходы которых являются выходами мантиссы и выходами порядка преобразователя соответственно, первый и второй управляющие входы коммутатора мантиссы и коммутатора порядка соединены с прямыми и инверсными выхода ми триггера знака мантиссы и соотцртственно старшего разряда счетчика поррлка, выходы всех, кроме старшего разрядов которого соединены с разрядными входами коммутатора порядка, разрядные входы коммутатора мантиссы соединены соответственно с икформа- , ционными выходами всех, кроме младшего, разрядов блока нормализации мантиссы, вход разрешения приема которого соединен с входом разрешения приема блока управления и является входом разрешения приема преобразователя, выходы знака и знака порядка которого соединены соответственно с прямыми выходами триггера знака порядка и старшего разряда счетчика порядка, счетный вход которого соединен с выходом нормализации блока управления, первый и второй входы анализа режима .которого соединены соответственно с прямым и инверсным выходами старшего разряда блока нормализации мантиссы, входы сдвига и инкремента которого соединены соответственно с выходами сдвига и инкремента блока управления, выходы занятости и разрешения выдачи которого являются соответственно выходами занятости и разрешения вьщачи преобразователя, вход окончания приема которого соединен с входом окончания приема блока управления, входы знака и знака порядка которого соединены соответственно с входами знака и первого разряда порядка преобразователя, вход второго разряда порядка которого является выходом переполнения преобразователя, причем блок управления содержит два элемента НЕ, три элемента ИЛИ,четыре элемента И и три RS -триггера, синхровходы которых соединены с тактовым входом блока управления, первый и второй входы анализа режима работы которого соединены с первыми входами первого элемента И и объединены с первыми входами второго, третьего и четвертого элементов И, вторые входы которых и второй вход первого элемента И соединены с выходом перв.ого триггера и являются выходом занятости блока упрайления, вход знака которого соединен с 5-входом второго триггера и через первый элемент НЕ с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и является выходом сдвига блока управления, вход знака порядка которого соедршен через второй элемент НЕ с 5-входом третьего триггера и с первым входом второго элемеита ИЛИ, второй вход которого соедин с выходом третьего элемента И и пер вым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента И и является выходом инкремента блока управления выход разрешения выдачи которого сое динен с выходом четвертого элемента И, третий и четвертый входы кото,рого соединены соответственно с инверсными входами второго и третьего триггеров, R -входы которых соединены соответственно с выходами первого и второго элементов ИХШ, а прямь е выходы соединены соответственно с третьими входами второго и третьего элементов И,5 - и R -входы первого триггера соединены соответственно с входами разрешения приема и окончани приема блока управления, выход нормализации которого соединен с выходом третьего элемента ИЛИ. В преобразователе блок нормализации мантиссы состоит из разрядов, первый и второй информационные входы и вход переноса каждого из которых, кроме младшего, соединены с первым и вторым информационными выходами и выходом переноса соседнего младшего разряда, причем каждый разряд блока нормализации мантиссы содержит RS -триггер, два элемента ИЛИ, две группы по три элемента И, элемент НЕ и элемент И, первый вход которого, является входом переноса разряда блока нормализации мантиссы, разрядный вход которого соединен с первым входом первого элемента И пер вой группы и через элемент НЕ с первым входом первого элемента И второй группы, вторые входы первых элементов И первой и второй групп соединен с входом разрешения приема блока нор мализации мантиссы, первые входывторых элементов И первой и второй групп являются прямым и инверсным информационными входами разряда блока нормализации мантиссы, вторые входы вторых элементов И первой и второй групп соединены с входо сдвига блока нормализации мантиссы, вход инкремента которого соединен с nepBbnvoi входами третьих элементов И первой и второй групп, вторые входы которых соединены с выходом элемента И, второй вход которого соединен последовательным инверсным информационным входом разряда блока нормали зации мантиссы, выходы элементов И первой и второй групп соединены с входами соответствующих элементов ИЛИ выходы которых соединены соответственно с S- иR-вxoд a ш триггера, прямой и инверсный выходы которого и выход элемента И являются соответственно последовательными прямым и инверсными информационными выходами и выходом переноса разряда блока нормализации мантиссы. На фиг.1 приведена блок-схема предлагаемого преобразователя, на фиг,2 - схема блока управления, на фиг.З - схема двух разрядов блока нормализации мантиссы и коммутатора мантиссы. Преобразователь (фиг.1) содержит блок 1 нормапизации мантиссы, счетчик 2 порядка, коммутатор 3 мантиссы, коммутатор 4 порядка и блок 5 управления, триггер 6 знака мантиссы, выход 7 занятости, выход 8 переполнения, выход 9 разрешения выдачи, вход 10 окончания приема, тактовый вход 11 преобразователя, вход 12 разрешения приема. Блок 5 управления (фиг.2) содержит триггеры 13-15, элементы НЕ 16-17, элементы ИЛИ 18-19, элементы И 20-23, элемент ИЛИ 24. Калодый разряд блока 1 нормализации мантиссы и коммутатора 3 мантиссы (фиг.З) содержит RS -триггер 25, элементы ИИ 26-27, две группы элементов И 28-29, элемент НЕ 30, элемент И 31, элемент И-ИЛИ 32. Принцип построения и работу предлагаемого преобразователя рассмотрим на примере преобразования формата данных ЕС ЭВМ в формат СМ ЭВМ. Двоичные числа с плавающей запятой в формате ЕС ЭВМ представляются следующим образом: 1 разряд - знак числа, 7 разрядов - порядокJ 24 разряда - мантисса. Основание счисления в этом формате принято равным 2 16, поэтому нормализация чисел осуществляется с точное тью до тетрады. Порядок чисел представляется увеличенным на 2 64, т.е. смещенным на числовой оси в положительном направлении на 6 разрядов, в результате чего все порядки являются положительными. Положительные и отрицательные числа с плавающей запятой (их порядки и мантиссы) во всех моделях ЭВМ Единой системы В оперативной памяти хранятся в прямом коде. Знак числа определяется по значению двоичной циф ры в знаковом разряде. Диапазон представления нормгшизс ванньсс шестнадцатиричных чисел (по абсолютному значению) определяется пределами от 6 до . Двоичные числа с плавающей запят в формате СМ ЭВМ (модели СМ-1, СМ-2 представляются следующим образом: 1 разряд - знак мантиссы; 23 разряда - мантисса, 7 разрядов - порядок 1 разряд - знак порядка. Основание системы счисления в формате СМ ЭВМ принято равным 2, поэтому нормализация чисел осуществляется с точностью до 1 разряда. Положительная мантисса и положительный порядок представляются в пр мом коде со знаковыми разрядами рав ными 0. Отрицательная мантисса и отрицательный порядок представляются в дополнительном коде со знаковыми разрядами равными 1. Предполагается, что запятая в ма тиссе фиксируется непосредственно слева от ее старшей цифры. Диапазон представления нормализо ванных чисел (по абсолютному значению) находится в пределах от 2 до 2 , т.е. значительно уже, диапазон представления чисел в форм те ЕС ЭВМ. Преобразователь работает следующим образом. При подключении входного кода и подаче сигнала Разрешение П1 |иема по входу 12 (фиг.1) осуществляется запись нулевого разряда (знак числа в нулевой (знаковый) разряд блока 1 нормализации мантиссы, 8-31 разрядо в 24-разрядный блок 1 нормализации мантиссы, первого разряда порядка с инверсией в знаковый разряд счетчи ка 2 порядка, 3-7 разрядов порядка 1-5 разряды счетчика 2 порядков, в 6-7 разряды счетчика 2 порядка пр этом записывается О. Нулевой и пе вый разряды входного кода записываются также в триггерах 13 и 1.4 блок 5 управления в прямом и инверсном коде соответственно (фиг.2). Сигнал Разрешение приема, поступивший также в блок 5 управления по пятому входу, устанавливает триггер 15 в единичное состояние, который подготавливает блок 5 управления к работ и вьщает по четвертому выходу сигна Занято на выход 7, предупреждая источник входной информации о занятости устройства. Знак мантиссы по выходу совпадает со знаком входного числа, поэтому он однозначно отображается через знаковый разряд мантиссы на выход. Порядок числа в исходном формате представляется смещенным в положительном направлении и все порядки являются по ложительными, при этом 1 в старшем (первом) разряде порядка свидетельствует о положительном порядке, а О об отрицательном. Поэтому знак порядка в преобразованном формате определяется как инверсия старшего (первого) разряда порядка входного числа. Диапазон .представления чисел в исходном формате с шестнадцатиричным основанием значительно шире, чем возможное представление чисел в формате с двоичным основанием, при этом наличие 1 во втором разряде порядка входного числа свидетельствует о том, что данное число не может быть преобразовано в выходной формат, поэтому в такой ситуации по выходу 8 выдается сигнал Переполнение. Число, нормализованное во входном формате с шестнадцатиричным основанием, может оказаться не нормализованным в выходном формате с двоичным основанием, поэтому по триггеру 6 знака осуществляется контроль нормализации. Если он находится в нуле, то единица на нулевом (инверсном) выходе этого триггера, заведенная на первый вход блока 5 управления, открывает элемент И 20 (фиг.2), которьм дает разрешение на первый выход блока 5 управления для сдвигов (без знака) блока 1 нормализации мантиссы влево и через элемент ИЛИ 24 на третий выход блока 5 управления для вычитания единиц из счетчика 2 порядка. Сдвиги в блоке 1 нормализации мантиссы и вычитание единиц в счетчике 2 порядка осуществляются под воздействием тактовых импульсов по входу 11 до тех пор, пока в старшем (первом) разряде блока нормализации мантиссы не появится 1. Количество возможных сдвигов, которые должны быть сделаны для нормализации, равно 0-3. При появлении 1 в старшем (первом) разряде блока нормализации мантиссы снимается разрешающий сигнал с входа элемента И 20 и, соответствен9 1 но, с первого и третьего выхода бло управления появляется разрешающий си нал с единичного выхода старшего раз ряда блока нормализации мантиссы по второму входу блока 5 управления на входах элементов И 21-23, подготавли вая блок управления для дальнейшей работы. Если число в блоке 1 нормали зации мантиссы сразу оказалось йорма лизованным, то сдвиги блока 1 нормализации мантиссы и вычитание единицы из счетчика 2 порядка не производятсяОтрицательная мантисса и отрицательный порядок в выходном формате должны быть представлены в дополнительном коде со знаковым разрядом равным 1, поэтому после нормализации числа блоком 5 управления осуществляется проверка знака входного числа и старшего разряда порядка, записанных в его триггерах 13 и 14, Если мантисса отрицательна, то единичный выход триггера 13 открывает элемент И 21, вьщавая на второй выход разрешающий сигнал для вычитания единицы из содержимого блока 1 нормализации. При отрицательном порядке единичным выходом триггера 14 открывается элемент И 22, который через элемент ИЛИ 24 выдает разрешающий сигнал на третий выход для вычи тания единицы из счетчика 2 порядка. При отрицательных мантиссе и порядке проверка их знаков и вычитание единиц из блока 1 нормализации мантиссы и счетчика 2 порядка осуществляется одновременно. Следующим тактовы импульсом триггеры 13 и 14 сбрасыва ются в нулевое состояние, разрешая через элемент И 23 подачу сигнала Разрешение выдачи по пятому выходу Исходный код Прием на регистр мантиссы и счет чик порядка После нормализацииВьсходной код Мантисса 01010000000000000000000 1001110 0101000000000000000000 10100000000000000000000 10100000000000000000000 Мантисса 0 блока 5 управления на выход У устройства. Триггер 6 знака, знаковый разряд счетчика 2 порядка управляют коммутатором 3 мантиссы и коммутатором 4 порядка, коммутируя на выход-прямой или обратньш код содержимого блока 1 нормализации мантиссы и счетчика 2 порядка. При положительных знаках коммутируются прямые коды, при отрицательных - обратные. После того, как выходной код будет принят приемником информации, из него должен поступить сигнал окончания приема по входу 10, который сбрасывает триггер 15 в нулевое состояние, снимает сигнал занятости по выходу 7, после чего устройство готово к приему нового числа. Особенностью преобразования мантис сы является также то, что в исходном коде мантисса представлена 24 разряда ми, а в выходном - 23 разрядами, поэтому если после приема мантиссы на блок 1 нормализации мантиссы мантисса оказывается нормализована для двоичного основания, то происходит потеря одного разряда мантиссы. В остальных случаях все разряды мантиссы сохраняются. Некоторые особенности построения имеет и блок нормализации мантиссы. В нем кроме обычных функций, выполняемых регистром (прием числа, сдвиг содержимого), имеется возможность вычитания единицы из его содержимого (как в обычном счетчике). Первые элементы И в группах используются для приема числа, вторые - для сдвига, третьи - для вычитания с целью сквозного заема на элементах И. Пример 1. Преобразование форматов данных. Порядок Инверсия 0111000 0110110 0110110 Знак Поря по- док

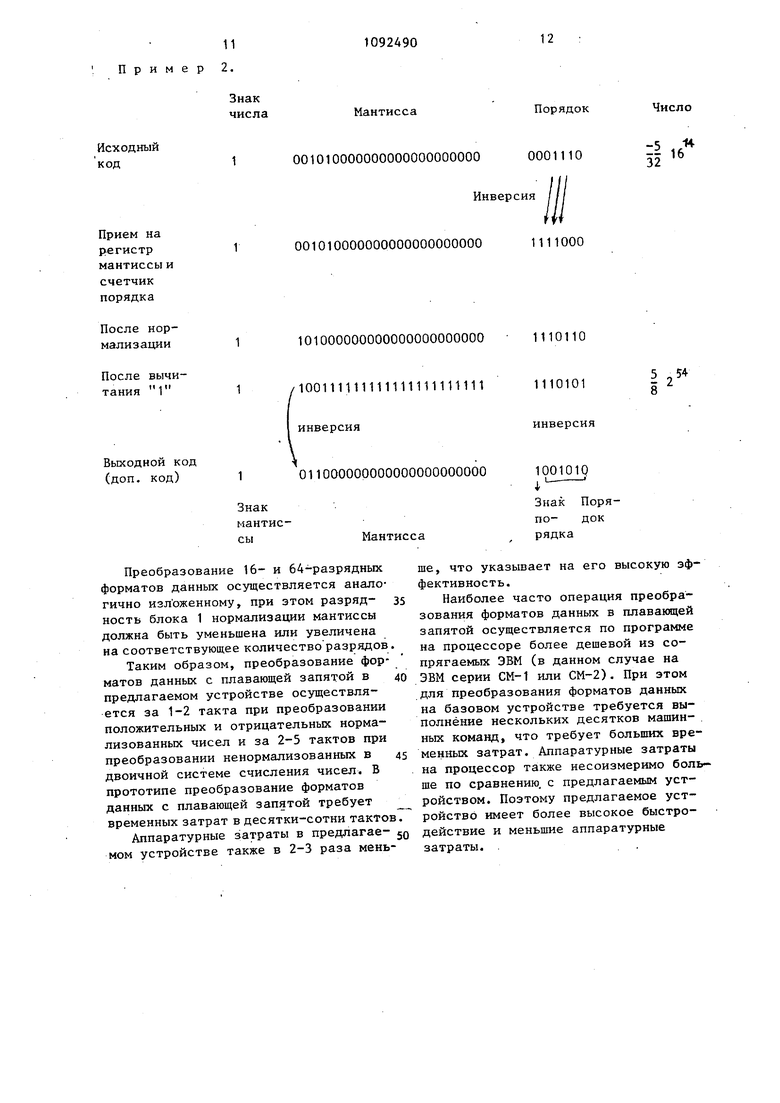

Пример 2.

Знак числа Исходный код1

001010000000000000000000

101000000000000000000000

100111111111111111111111

инверсия Выходной код (доп. код) 011000000000000000 Знак мантиссы

Преобразование 16- и 64-разрядных форматов данных осуществляется аналогично изложенному, при этом разряд- 35 ность блока 1 нормализации мантиссы должна быть уменьшена или увеличена на соответствующее количестворазрядов.

Таким образом, преобразование форматов данных с плавающей запятой в 40 предлагаемом устройстве осуществляется за 1-2 такта при преобразовании положительных и отрицательных нормализованных чисел и за 2-5 тактов при преобразовании ненормализованных в 45 двоичной системе счисления чисел. В прототипе преобразование форматов данных с плавающей запятой требует временных затрат в десятки-сотни тактов.

Аппаратурные затраты в предлагае- JQ MOM устройстве также в 2-3 раза меньМантиссаПорядок

Число

51-

Инверсия

1111000

1110110

1

1110101

инверсия Мантисса

ше, что указывает на его высокую эффективность.

Наиболее часто операция преобразования форматов данных в плавающей запятой осуществляется по программе на процессоре более дешевой из сопрягаемых ЭВМ (в данном случае на ЭВМ серии СМ-1 или СМ-2). При этом для преобразования форматов данных на базовом устройстве требуется выполнение нескольких десятков мащинных команд, что требует больших временных затрат. Аппаратурные затраты на процессор также несоизмеримо больше по сравнению, с предлагаемым устройством. Поэтому предлагаемое устройство имеет более высокое быстродействие и меньшие аппаратурные затраты. . 001010000000000000000000 0001110 000000 1001010 I L . Знак Поряпо- док рядка

S ,

IVl

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| Наука, 1969, с | |||

| Устройство для дозирования сыпучих материалов | 1975 |

|

SU543551A2 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

Авторы

Даты

1984-05-15—Публикация

1982-09-17—Подача