Изобретение относится к вычислительной технике и может быть использовано для реализации передачи информации между цифровой вычислительной машиной и периферийными устройствами

Известны способ и устройство дня передачи данных, по которому передаются синхронные биты первого и второго противоположных видов внутри блока, причем число синхробитов, относящихся ко второму виду, соответствует условию 2NM-N-12- 1 и M-Msf 1 Недостатком их является большая сложность.

Известно устройство для управления передачей данных, содержащее генератор импульсов, два дешифратора, четыре элемента задержки, три регистра, восемь элементов И, три элемента ИЛИ, блок памяти. Недостатком этого устройства является большая сложность устройства.

Целью изобретения является упрощение устройства. В устройстве за счет новых

связей исключены блок памяти, дешифратор, элементы ИЛ И, два элемента задержки, четыре элемента И.

Сущность изобретения заключается в том, что передаваемый код преобразуется в последовательный и к нему присоединяется в конце кодовой посылки импульс, а синхроимпульс в конце кодовой посылки не передается.

Отличительными признаками устройства являются наличие двух формирователей импульса, элемента НЕ и триггера, которые соединены с остапьными элементами устройства определенными связями и служат для преобразования параллельного кода в последовательный, передачи кода и преобразования с последовательного кода в параллельный.

Предлагается устройство для передачи информации, содержащее генератор импульсов, дешифратор, элемент задержки три регистра, четыре элемента И и две лисо С

х| о

ю

%

VI

нии связи, причем информационный вход первого регистра соединен с информационным входом устройства, выход первого регистра соединен с первым входом первого элемента И, которое дополнительно содержит два формирователя импульсов, элемент НЕ, триггер, причем информационные входы дешифратора соединены с адресными входами устройства к шине логического нуля которого подключена группа информационных входов второго регистра, выход которого соединен с первым входом второго элемента И, выход дешифратора соединен с входом записи первого и второго регистров и с входом пуска генератора импульсов, выход которого соединен с входами синхронизации первого и второго регистров, с вторыми входами первого и второго элементов И, выход первого элемента И соединен с входом первого форми- рователя импульсов, выход которого соединен через первую линию связи с первыми входами третьего и четвертого элементов И, выход второго элемента И соединен через вторую линию связи со вторым входом третьего элемента И, с инверс- ным входом сброса триггера и через элемент НЕ со вторым входом четвертого элемента И и входом второго формирователя импульсов, выход которого соединен со входом сдвига третьего регистра, выходы которого соединены с информационными входами четвертого регистра, выходы которого являются выходами устройства, выход третьего элемента И соединен с входом установки триггера, выход которого через элемент задержки соединен с информационным входом третьего регистра, синхровход четвертого регистра соединен с выходом четвертого элемента И.

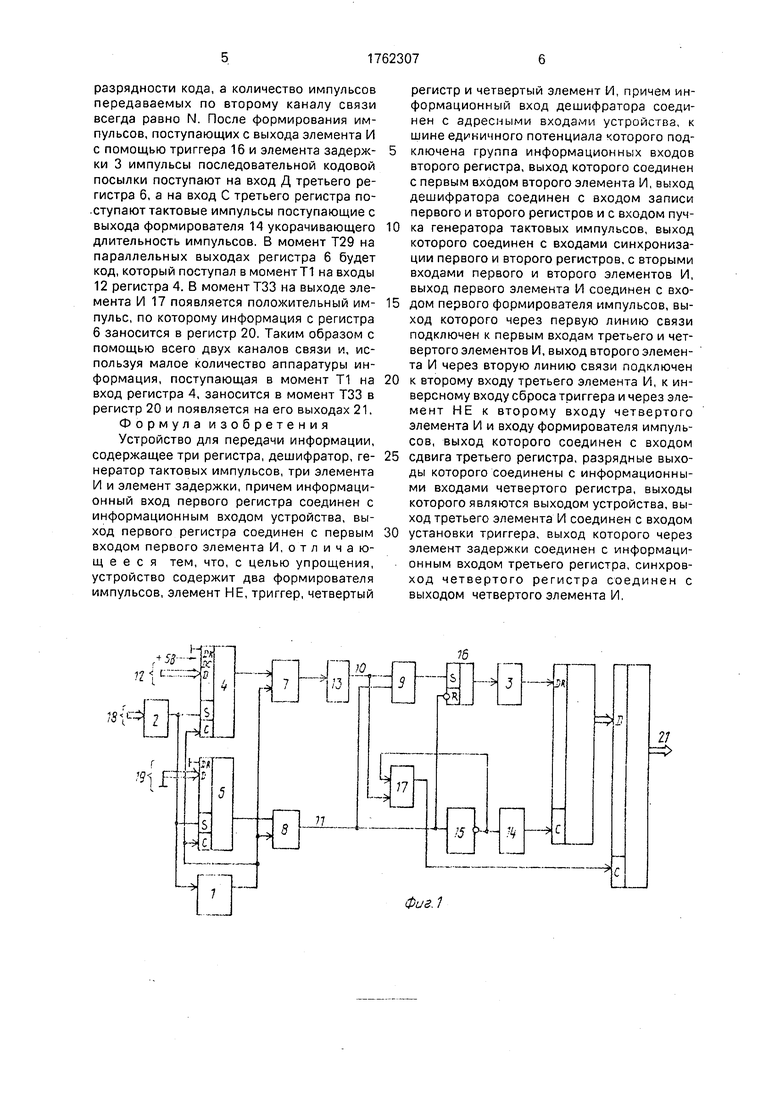

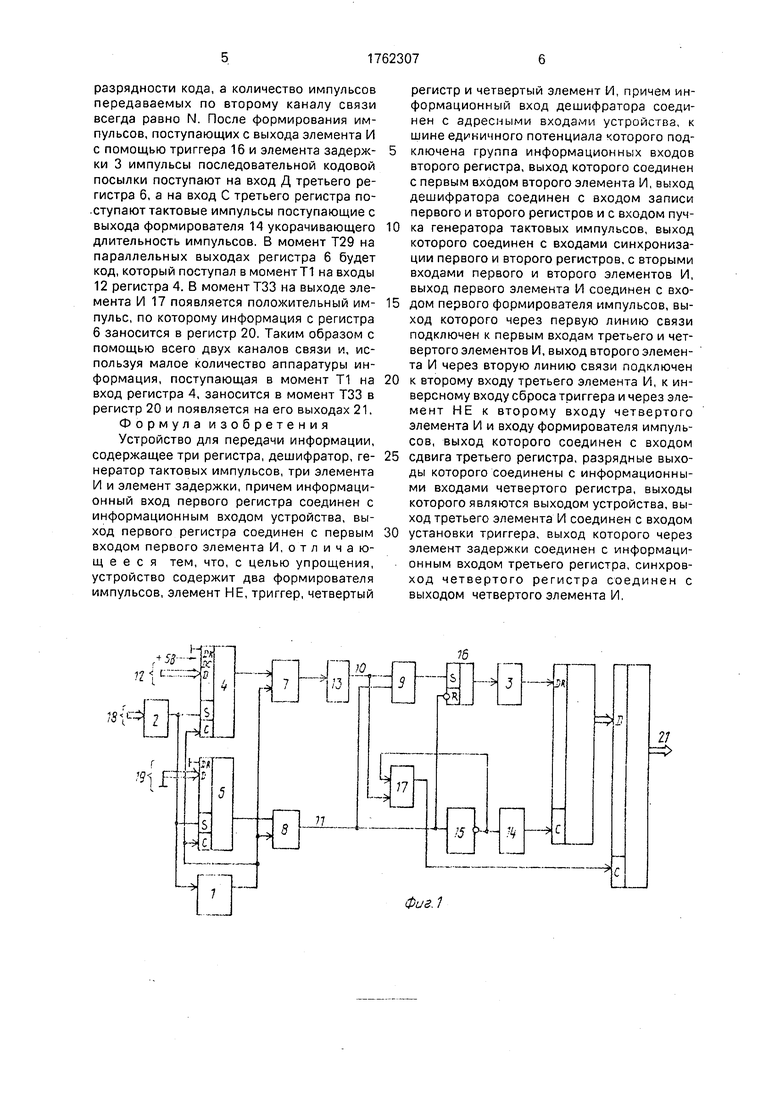

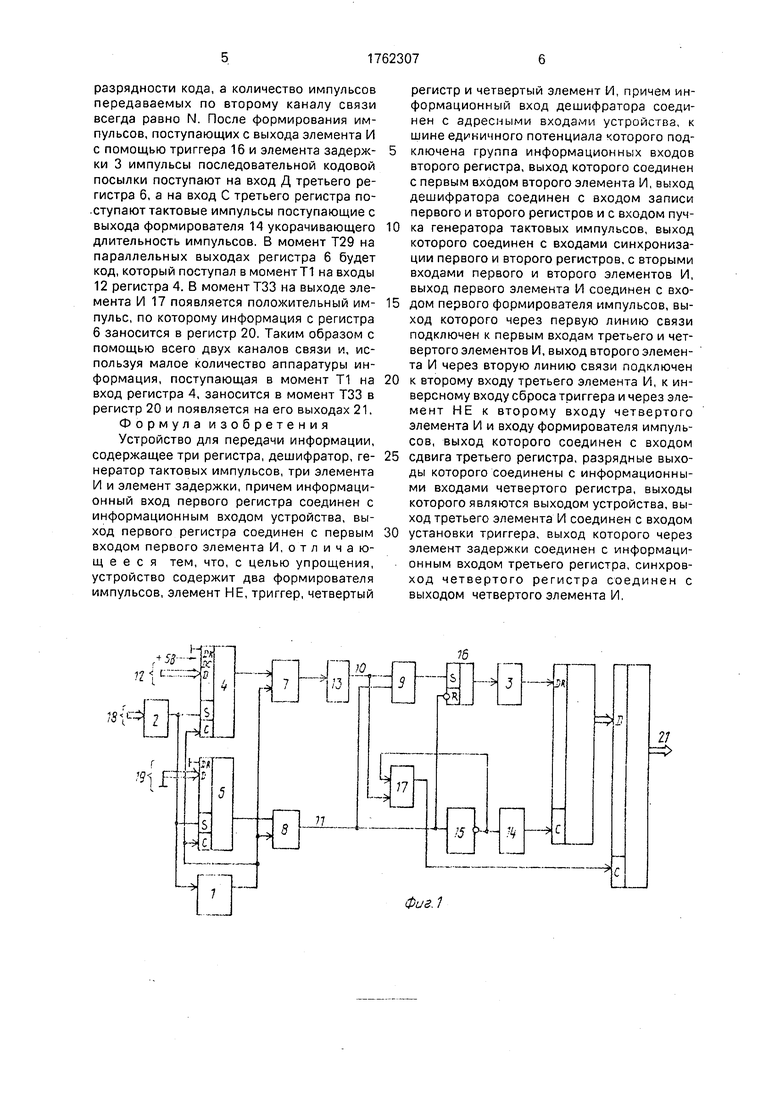

На фиг.1 изображена схема устройства; на фиг.2 - его временная диаграмма.

Устройство для передачи информации содержит генератор импульсов 1, дешифратор 2, элемент задержки 3, три регистра 4, 5, 6, три элемента И 7, 8, 9, две линии связи 10,11, причем информационные входы первого регистра 4 соединены с информационными входами устройства 12, выход первого регистра соединен с первым входом первого элемента И 7. Устройство также содержит два формирователя импульсов 13, 14 элемент НЕ 15, триггер 16, четвертый элемент И 17, причем информационные входы дешифратора соединены 2 соединены с адрес- ными входами 18 устройства к шине логического нуля которого подключена группа информационных входов 19 второго регистра 5, выход которого соединен с первым входом второго элемента И 8. Выход

дешифратора 2 соединен с входом записи первого и второго регистров 4, 5 и с входом пуска генератора импульсов 1, выход которого соединен с входами синхронизации

первого и второго регистров 4, 5 со вторыми входами первого и второго элементов И 7, 8, Выход первого элемента И 7 соединен с входом первого формирователя импульсов 13, выход которого соединен через первую

0 линию связи с первыми входами третьего и четвертого элементов И 9, 17. Выход второго элемента И 8 соединен через вторую линию связи 11 со вторым входом третьего элемента И 9, с инверсным входом сброса

5 триггера 16 и через элемент НЕ 15 со вторым входом четвертого элемента И 17 и входом второго формирователя импульсов 14, выход которого соединен с входом сдвига третьего регистра 6, выходы которого соеди0 нены с информационными входами четвертого регистра 20, выходы 21 которого являются выходами устройства. Выход третьего элемента И9 соединен с входом S установки в 1 триггера 16, выход которого

5 через элемент задержки 3 соединен с информационным входом третьего регистра 6. Синхровход четвертого регистра 18 соединен с выходом четвертого элемента И 17. Предположим, в первоначальный мо0 мент времени ТО схема (см. фиг.1) находится в исходном состоянии. При передаче данных в порт периферийного устройства по сигналам на входе дешифратора 2 вырабатывается сигнал на выходе элемента 2 в

5 момент Т1, который разрешает прием N+1 разрядного кода в регистр 1, причем старший разряд этого кода должен быть всегда равен 1, а также разрешает прием всех 1 в N разрядный регистр 5, в-третьих устанав0 ливает в первоначальное состояние генератор 1 На выходе генератора 1 начинают появляться импульсы. Первый импульс в момент Т2 приходит на вход регистров 4, 5 и сдвигает код в этих регистрах на один раз5 ряд. Код с выхода регистров 4, 5 стробиру- ется на элементах И 7, 8 сигналами генератора 1.

Код с выхода элемента И 7 поступает через формирователь 13, который представ0 ляет собой последовательно включенный элемент задержки и схему укорочения длительности импульса, например, 133АГЗ, на первый канал связи, а код с выхода элемента И 8 поступает на второй канал связи по

5 первому каналу связи передаются импульсы, соответствующие 1 передаваемого кода, причем в старшем разряде кода всегда имеется 1, а количество импульсов при 1 во всех разрядах передаваемого N разрядного кода равно N+1, т.е. на один больше

разрядности кода, а количество импульсов передаваемых по второму каналу связи всегда равно N. После формирования импульсов, поступающих с выхода элемента И с помощью триггера 16 и элемента задерж- ки 3 импульсы последовательной кодовой посылки поступают на вход Д третьего регистра 6, а на вход С третьего регистра поступают тактовые импульсы поступающие с выхода формирователя 14 укорачивающего длительность импульсов. В момент Т29 на параллельных выходах регистра 6 будет код, который поступал в моментТ1 на входы 12 регистра 4. В момент ТЗЗ на выходе элемента И 17 появляется положительный им- пульс, по которому информация с регистра 6 заносится в регистр 20. Таким образом с помощью всего двух каналов связи и, используя малое количество аппаратуры информация, поступающая в момент Т1 на вход регистра 4, заносится в момент ТЗЗ в регистр 20 и появляется на его выходах 21. Формула изобретения Устройство для передачи информации, содержащее три регистра, дешифратор, ге- нератор тактовых импульсов, три элемента И и элемент задержки, причем информационный вход первого регистра соединен с информационным входом устройства, выход первого регистра соединен с первым входом первого элемента И, о т л и ч а ю- щ е е с я тем, что, с целью упрощения, устройство содержит два формирователя импульсов, элемент НЕ, триггер, четвертый

регистр и четвертый элемент И, причем информационный вход дешифратора соединен с адресными входами устройства, к шине единичного потенциала которого подключена группа информационных входов второго регистра, выход которого соединен с первым входом второго элемента И, выход дешифратора соединен с входом записи первого и второго регистров и с входом пучка генератора тактовых импульсов, выход которого соединен с входами синхронизации первого и второго регистров, с вторыми входами первого и второго элементов И, выход первого элемента И соединен с входом первого формирователя импульсов, выход которого через первую линию связи подключен к первым входам третьего и четвертого элементов И, выход второго элемента И через вторую линию связи подключен к второму входу третьего элемента И, к инверсному входу сброса тоиггера и через эле- мент НЕ к второму входу четвертого элемента И и входу формирователя импульсов, выход которого соединен с входом сдвига третьего регистра, разрядные выходы которого соединены с информационными входами четвертого регистра, выходы которого являются выходом устройства, выход третьего элемента И соединен с входом установки триггера, выход которого через элемент задержки соединен с информационным входом третьего регистра, синхров- ход четвертого регистра соединен с выходом четвертого элемента И.

ТО

720

ТЗО T3S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для телеконтроля промежуточных станций системы связи | 1989 |

|

SU1674385A1 |

| Устройство для телеконтроля промежуточных станций системы связи | 1990 |

|

SU1757108A1 |

| Устройство для управления вводом информации | 1988 |

|

SU1566337A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Устройство для передачи и приема дискретной информации | 1979 |

|

SU1099321A1 |

| СПОСОБ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2453906C2 |

| Устройство для моделирования каналов передачи дискретной информации | 1982 |

|

SU1049915A1 |

| Устройство управления коммутацией сообщений | 1980 |

|

SU955018A1 |

| Устройство для моделирования процесса передачи информации | 1989 |

|

SU1777149A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

Изобретение относится к автоматике и вычислительной технике и м.б. использовано для реализации передачи информации между цифровой вычислительной машиной и периферийными устройствами. Целью изобретения является упрощение устройства. Устройство содержит генератор импульсов 1, дешифратор 2, элемент задержки 3, регистры 4, 5, 6, элементы И 7-9, линии связи 10, 11, информационные входы устройств 12, формирователи импульсов 13, 14, элемент НЕ 15, триггер 16, элемент И 17, адресные входы 18, информационные входы 19, регистр 20, выходы 21 устройства. 2 ил.

Фиг г

| Устройство для приема и передачи информации | 1984 |

|

SU1203569A1 |

| Устройство для управления передачей данных | 1986 |

|

SU1381569A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1992-09-15—Публикация

1989-10-06—Подача