1

(21)4874997/21 (22) 12.09.90 (46)23.09.92. Б юл. №35

(71)Научно-исследовательский центр физики и технологии

(72)ААКураев

(56) 1. Авторское свидетельство СССР Nfe 1295512, кл. Н 03 К 19/094. 1985.

2. Авторское свидетельство СССР Мг 1480116, кл. Н 03 К 19/094. 1987.

(54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП- ТРАНЗИСТОРАХ

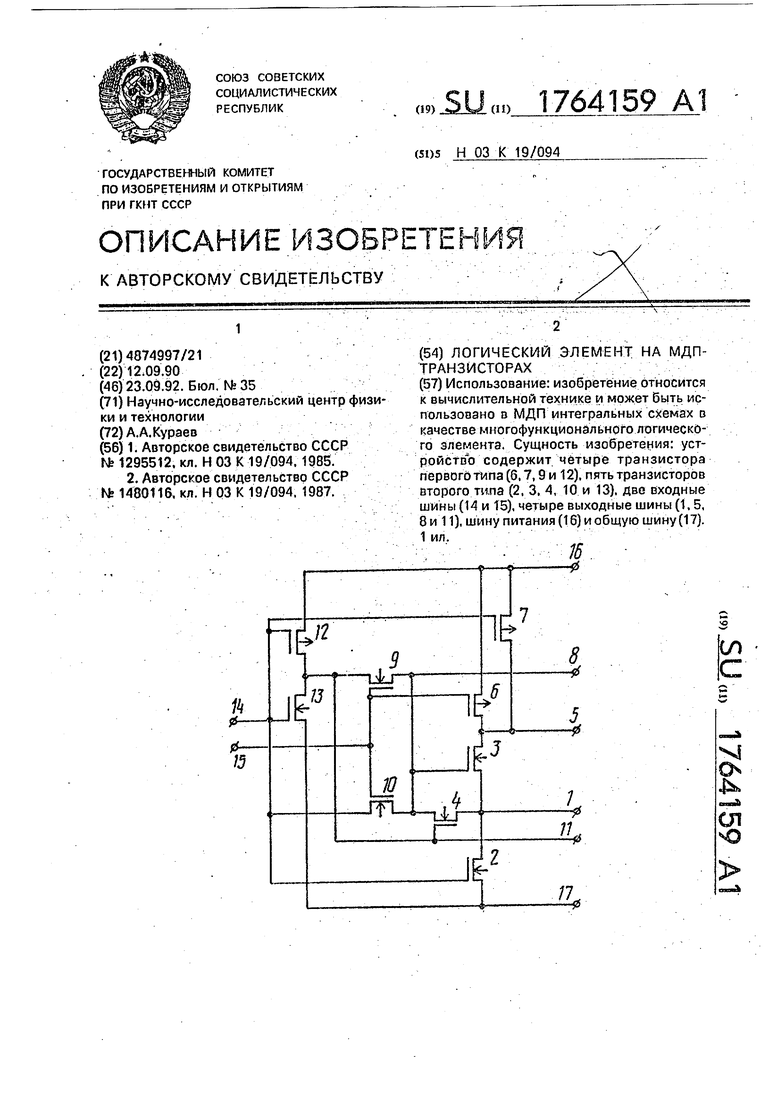

(57) Использование: изобретение относится к вычислительной технике и может быть использовано в МДП интегральных схемах в качестве многофункционального логического элемента. Сущность изобретения: уст- ройствЪ содержит четыре транзистора первого типа (6,7,9 и 12), пять транзисторов второго типа (2, 3, 4, 10 и 13). две входные шины (14 и 15), четыре выходные шины(1,5, 8 и 11), шину питания (16) и общую шину (17). 1 ил.

16

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент на МДП-транзисторах | 1990 |

|

SU1734206A1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2011 |

|

RU2449469C1 |

| Логический элемент на МДП-транзисторах | 1987 |

|

SU1480116A1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2012 |

|

RU2496227C1 |

| Формирователь с тремя состояниями на выходе | 1983 |

|

SU1149399A1 |

| Преобразователь уровней сигналов на МДП-транзисторах | 1988 |

|

SU1538246A1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2010 |

|

RU2438234C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2013 |

|

RU2541854C1 |

xi О 4

СП

ю

Изобретение относится к вычислительной технике и может быть использовано в МДП интегральных схемах в качестве многофункционального логического элемента.

Известен логический элемент на МДП- транзисторах, содержащий семь транзисторов пераого типа и семь транзисторов второго типа.

Недостатком такого устройства является значительное число транзисторов.

Известен также логический элемент на МДП-транзисторах, содержащий шесть транзисторов первого типа и пять транзисторов второго типа.

Недостат1 ом такого устройства являет- ся также значительное число транзисторов, Наиболее близким по технической сущности к заявляемому устройству является выбранный в качестве прототипа логический элемент на ШДП-трзнзисторах, со- держащий четыре трензистора первого типа и пять транзисторов второго типа.

Недостатком известного устройства является увеличение количества транзисторов при необходимости получения инверсной функции сравнения F XiX2 XiX2 вместо функции F XiX2 н ХтХз на третьей выходной шине, иными словами потребуется подключить КМДП-инвертор, -содержащий один транзистор первого типа и один транзистор второго типа Устройство теперь будет иметь уже пять транзисторов первого типа и шесть транзисторов второго типа.

Целью изобретения является изменение логической функции элемента при со- хранении количества транзисторов

Указанная цель достигается тем, что в логический элемент на МДП-транзисторах, содержащий четыре транзистора первого типа и пять транзисторов второго типа, ис- токи первого и третьего транзисторов первого типа подключены к ш же питания, а истоки первого и третьего транзисторов второго типа подключены к общей шине, затворы первого и третьего транзисторов первого типа и первого и третьего транзисторов второго типа подключены к первой входной шине, затвор второго транзистора первого типа и затвор второго транзистора второго типа подключены к второй входной шине, стоки третьего, четвертого и пятого транзисторов второго типа подключены к первой выходной шине, стоки второго и третьего транзисторов первого типа подключены к второй выходной шине, сток чет- вертого транзистора первого типа и сток второго транзистора второго типа подключены к третьей выходной шине, сток первого транзистора первого типа и сток первого транзистора второго типа подключены к

четвертой выходной шине, введены исток второго транзистора второго типа, подключенный к первой входной шине, затвор второго транзистора второго типа, подключенный к второй входной шине, исток четвертого транзистора второго типа, подключенный к второй выходной шине, затвор четвертого транзистора второго типа, подключенный к третьей выходной шине, исток четвертого транзистора первого типа, подключенный к четвертой выходной шине, исток второго транзистора первого типа, подключенный к шине питания

Сопоставительный анализ с прототипом позволяет сделать вывод, что заявляемый логический элемент на МДП-транзисторах отличается тем, что в него введены исток второго транзистора второго типа подключенный к первой входной шине, затвор второго транзистора второго типа, подключенный ко второй входной шине, исток четвертого транзистора второго типа, подключенный к второй выходной шине, затвор четвертого транзистора второго типа, подключенный к третьей выходной шине, исток четвертого транзистора первого типа, подключенный к четвертой выходной шине, исток второго транзистора первого типа подключенный к шине питания

Таким образом, описываемое техническое решение соответствует критерию новизна.

Анализ известных технических решений позволяет сделать вывод об отсутствии в них признаков, сходных с существенными отличительными признаками в заявленном логическом элементе на МДП-транзисторах, и признать заявляемое техническое решение соответствующим критерию существенные отличия.

На чертеже представлена принципиальная схема логического элемента на МДП- транзисторах.

Логический элемент на МДП-траизисто- рах содержит первую выходную шину 1. к которой подключены стоки третьего 2, четвертого 3 и пятого 4 транзисторов второго типа, вторую выходную шину 5, к которой подключены стоки второго б и третьего 7 транзисторов первого типа, исток четвертого транзистора 3 второго типа, третью выходную шину 8, к которой подключены сток четвертого 9 транзистора первого типа, за- трор четвертого 3, исток пятого 4, сток второго 10 транзисторов второго типа, четвертую выходную шину 11, к которой подключены сток первого 12, исток четвертого 9 транзисторов первого типа, сток первого 13, затвор пятого 4 транзисторов второго типа, первую входную шину 14, к

которой подключены затворы первого 12, третьего 7 транзисторов первого типа, за- тооры первого 13, третьего 2, исток второго 10 транзисторов второго типа, вторую входную шину 15, к которой подключены затворы второго 6, четвертого 9 транзисторов первого типа, затвор второго 10 транзистора второго типа, шину питания 16, к которой подключены истоки первого 12, второго 6 и третьего 7 транзисторов первого типа, общую шину 17, к которой подключены истоки первого 13 и третьего 2 транзисторов второго типа.

Логический элемент работает следующим образом.

На входные шины 14 и 15 подаются логические сигналы. На первой выходной шине 1 реализуется функция конъюнкции дополняющих входных логических сигналов Y1 Х1 Х2. На второй выходной шине 5 реализуется функция дизъюнкции тех же сигналов Y2 Х1 + Х2. На третьей выходной реализуется функция сравнения Y3 Х1 Х2 + Х1 Х2, а на четвертой выходной шине 11 - функция отрицания Y4 Х1.

При подаче на входные шины набора 0,0 соответственно, первый 12, второй б, третий 7, четвертый 9 транзисторы первого типа и четвертый 3, пятый 4 транзисторы второго типа открыты, а первый 13, второй 10, третий 2 транзисторы второго типа закрыты. При этом на первой 1, второй 5, третьей 8 и четвертой 11 выходных шинах устанавливается сигнал 1.

При подаче на входные шины набора 1,1 соответственно, первый 12, второй 6, третий 7, четвертый 9 транзисторы первого типа и пятый 4 транзистор второго типа закрыты, а первый 13, второй 10, третий 2, четвертый три транзисторы второго типа открыты. При этом на первой 1, второй 5, четвертой 11 быходных шинах устанавливается сигнал О, а на третьей выходной шине устанавливается сигнал.

При подаче на входные шины набора 0,1 соответственно, первый 12. третий 7 транзисторы первого типа и второй 10, пятый 4 транзисторы второго типа открыты, а второй 6, четвертый 9, транзисторы первого типа и первый 13, третий 2, четвертый 3 транзисторы второго типа закрыты. При этом на первой 1 и третьей 8 выходных шинах устанавливается сигнал О, а на второй 5 и четвертой 11 выходных шинах устанавливается сигнал 1,

При подаче на входные шины набора 1,0 соответственно, первый 12, третий 7 транзисторы первого типа и второй 10, четвертый 3, пятый 4 транзисторы второго типа

закрыты, а второй 6, четвертый 9 транзисторы первого типа и первый 13, третий 2 транзисторы второго типа открыты. При этом на первой 1, третьей 8, четвертой 11 выходных

5 шинах устанавливается сигнал О, а на второй 5 выходной шине устанавливается сигнал 1.

Изменение логической функции на инверсную при сохранении числа транзисто10 ров позволит отказаться от введения в схему - прототип инвертора и использовать предложенный логический элемент на КМДП-транзисторах, в противном случае увеличение количества транзисторов в дис15 кретном исполнении понизит надежность устройства, а в интегральном - увеличение площади кристалла уменьшит процент выхода годных ИС.

0 Формула изобретения

Логический -лемент на МДП-транзисто- рах. содержащий четыре транзистора первого типа и пять транзисторов второго типа, истоки первого, второго, третьего транзи5 сторов первого типа подключены к шине питания, а истоки первого, третьего транзисторов второго типа подключены к общей шине, затворы первого, третьего транзисторов первого типа и первого, третьего тран0 зисторов второго типа подключены к первой входной шине, затворы второго, четвертого транзисторов первого типа и затвор второго транзистора второго типа подключены к второй входной шине, стоки третьего, пято5 го транзисторов второго типа подключены к первой выходной шине, стоки второго, третьего транзисторов первого типа, исток четвертого транзистора второго типа подключены к второй выходной шине, сток чет0 вертого транзистора первого типа и исток пятого транзистора второго типа подключены к третьей выходной шине, сток первого, исток четвертого транзисторов первого типа и сток первого транзистора второго типа

5 подключены к четвертой выходной шине, отличающийся тем, что, с целью увеличения процента выхода годных интегральных схем в случае интегрального исполнения и увеличения надежности в случае

0 дискретного исполнения логического элемента на МДП-транзисторах, исток второго транзистора второго типа подключен к первой входной шине, сток четвертого транзистора второго типа подключен к перв ой

5 выходной шине, исток второго, затвор четвертого транзисторов второго типа подключены к третьей выходной шине, затвор пятого транзистора второготипа подключен к четвертой выходной шине.

Авторы

Даты

1992-09-23—Публикация

1990-09-12—Подача