Изобретение относится к цифровой вычислительной технике и может быть использовано в МДП интегральных схемах при реализации устройств логической обработки многоразрядных двоичных данных.

Известна реализация каскадных логических цифровых устройств на основе динамических КМДП схем с предзарядом (Патент США 4780626, H 03 K 19/096, НКИ 307-448 от 25.10.88). Они требуют меньших затрат по числу транзисторов на одну функцию по сравнению с традиционными КМДП элементами статического типа и обладают более высоким быстродействием. Но их недостаток - функциональная ограниченность возможность реализации только элементарных логических функций типа И-ИЛИ/НЕ. Более сложные логические операции на уровне одного каскада не могут выполняться вследствие отсутствия логических парафазных сигналов.

Наиболее близким техническим решением к предлагаемому является каскадное логическое устройство на КМДП транзисторах (Патент РФ 2132591, фиг.1, H 03 K 19/00 от 24.04.1998). Это устройство, принятое за прототип, содержит последовательно включенные каскады с использованием парафазных входных и выходных сигналов, которые работают под общим однофазным тактированием с асинхронной последовательной передачей логического сигнала через разделительные инверторы. В каскаде используются две пары логических ключевых цепей и триггер-фиксатор для запоминания промежуточных результатов.

Недостатком этого устройства является функциональная ограниченность, что обусловлено тем, что в каждом каскаде одна пара логических ключевых цепей реализует функцию, парафазное значение которой фиксируется в триггере, а другая пара ключевых цепей независимо от первой реализует другую функцию, значение которой в виде парафазных сигналов передается всегда на логические входы последующего каскада, и таким образом устройство может выполнять только последовательные многоуровневые операции типа арифметических.

Технической задачей, решаемой в изобретении, является расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что парафазное каскадное логическое устройство на КМДП транзисторах, содержащее в каждом каскаде первый и второй инверторы, три транзистора p-типа и логический блок, содержащий прямые, инверсные и дополнительные ключевые цепи, которые состоят из последовательно соединенных транзисторов n-типа, затворы которых подключены к соответствующим входам каскада, на которые подаются парафазные сигналы входных переменных, в каждом каскаде прямые и инверсные ключевые цепи своим первым выводом подключены непосредственно к входам соответственно первого и второго инверторов и дополнительно соединены с шиной питания соответственно через первый и второй транзисторы p-типа, а вторым выводом подключены к общему выводу логического блока, дополнительные ключевые цепи в первом каскаде первым выводом соединены через третий транзистор p-типа с шиной питания, а вторым подключены к общему выводу логического блока, дополнительные ключевые цепи во всех других каскадах своим первым выводом соединены со стоком соответствующего третьего транзистора p-типа, затворы первых и вторых транзистров p-типа в каждом каскаде объединены, а в первом каскаде дополнительно подключены к затвору третьего транзистора p-типа, к тактовой шине и затвору тактового транзистора n-типа, который включен между общим выводом логического блока и шиной земли, дополнительно содержит выходной блок, в каждом каскаде, кроме первого проходной транзистор n-типа, который включен между общим выводом логического блока и шиной земли, и в каждом каскаде - третий инвертор, вход которого соединен с первым выводом дополнительных ключевых цепей, а выход - с объединенными затворами проходного транзистора n-типа и транзисторов p-типа последующего каскада, вторые выводы дополнительных ключевых цепей, истоки третьих транзисторов p-типа, как и в первом каскаде, подключены соответственно к общему выводу логического блока и к шине питания, в каждом логическом блоке только одна ключевая цепь является замкнутой при любом наборе парафазных сигналов входных переменных данного каскада, а выходной блок выполнен в виде парафазного элемента ИЛИ-НЕ и содержит первый и второй транзисторы p-типа, которые включены между шиной питания и соответственно первым и вторым выходами устройства, затворы которых подключены к тактовой шине и затвору транзистора n-типа, включенному между общим выводом выходного блока и шиной земли, между первым и вторым выходами устройства с одной стороны и общим выводом выходного блока с другой включены две группы параллельно соединенных логических транзисторов n-типа, число которых в каждой группе соответствует числу каскадов устройства, затворы логических транзисторов n-типа первой группы подключены к выходам первых инверторов, а затворы логических транзисторов n-типа второй группы подключены к выходам вторых инверторов, выход третьего инвертора последнего каскада является третьим выходом устройства.

Существенными отличительными признаками в указанной совокупности признаков является наличие в каждом каскаде третьего инвертора и связанного с ним проходного транзистора n-типа с соответствующими связями с транзисторами p-типа в последующем каскаде, использование в логическом блоке каскада трех типов ключевых цепей, из которых только одна цепь может находиться в замкнутом состоянии, а также введение в устройство выходного блока, фиксирующего работу устройства под общим тактированием и его выполнение в виде парафазного элемента ИЛИ-НЕ с соответствующими связями с логическими выходами каскадов.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - расширения функциональных возможностей за счет реализации различных логических операций в каждом каскаде одновременно с несколькими многоразрядными операндами, за счет дополнительной логической выборки значений функции в каждом каскаде по заданному критерию и возможности фиксации результата в выходном блоке. Действительно, использование в логическом блоке каскада трех типов ключевых цепей, из которых только одна может находиться в проводящем состоянии, позволяет в одной логической ситуации сформировать на прямых и инверсных ключевых цепях парафазный выходной сигнал соответствующей функции и зафиксировать результат в выходном блоке с дизъюнктивной формой взаимодействия с каждым каскадом. Дополнительные ключевые цепи в совокупности с третьим инвертором и связанными с его выходом транзисторами позволяют сформировать тактирование последующего каскада в другой логической ситуации только тогда, когда прямые и инверсные ключевые цепи одновременно находятся в нейтральном разомкнутом состоянии и соответствующая функция в данном каскаде не реализуется.

Таким образом, последовательное тактирование каскадов или опрос значений функций, реализуемых в каждом каскаде, производится по логическому признаку, а в качестве входных переменных могут быть один или несколько одноименных разрядов двух и большего числа переменных или операндов. Реализация логической функции, соответствующей одной из трех типов ключевых цепей, всегда приводит к изменению исходного логического состояния одного из трех выходов устройства, что может использоваться как индикатор завершения цикла работы устройства. В результате расширяются комбинационные возможности как на уровне одного каскада, так и на уровне устройства в целом.

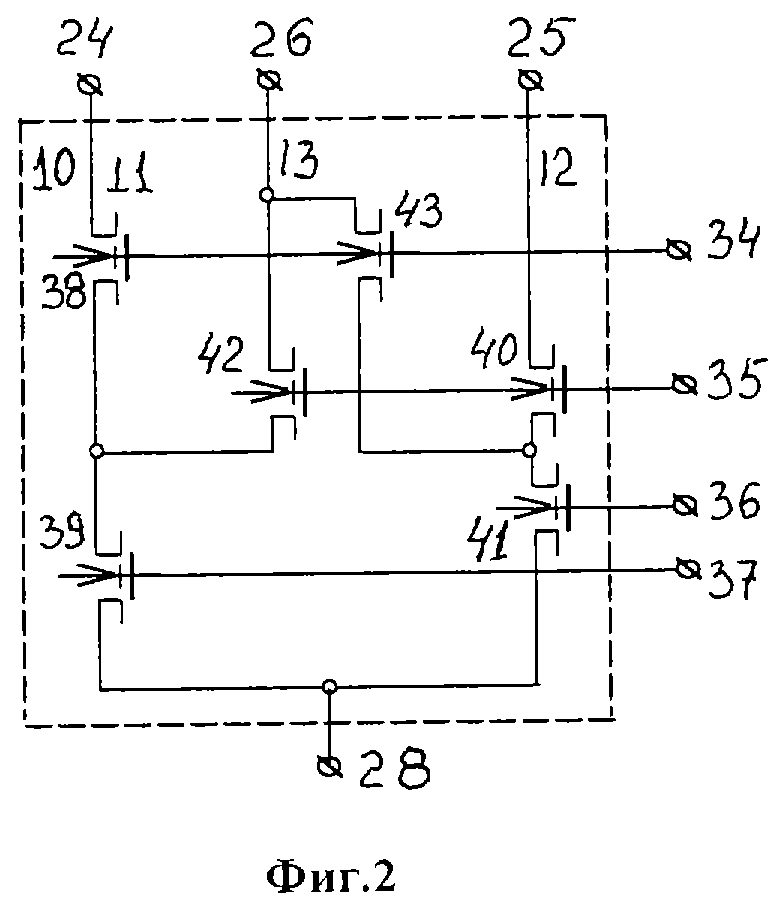

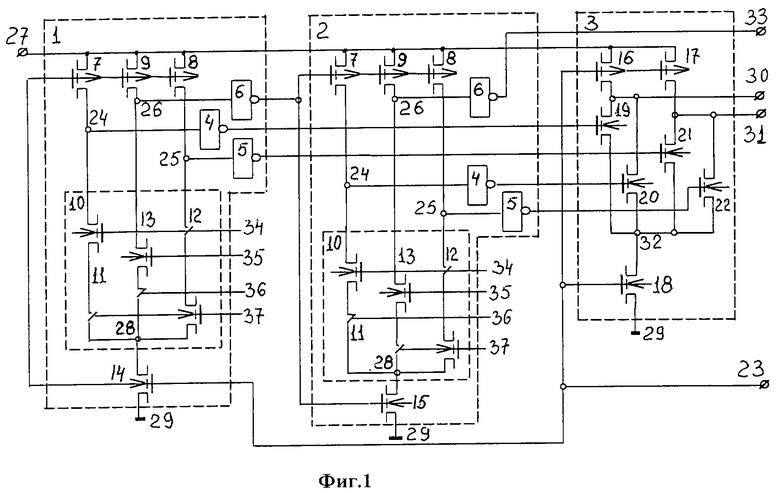

На фиг.1 приведена принципиальная схема заявляемого устройства, представленного в виде первого и второго (последнего) каскадов. На фиг.2 приведен пример выполнения логического блока, идентичного для всех каскадов, при реализации устройства поразрядного сравнения на равенство и неравенство двух операндов.

Парафазное каскадное логическое устройство на КМДП транзисторах (фиг.1) содержит первый 1 и второй 2 каскады, выходной блок 3. Каждый каскад содержит первый 4, второй 5 и третий 6 инверторы, а также первый 7, второй 8 и третий 9 транзисторы p-типа, логический блок 10, который содержит прямые 11, инверсные 12 и дополнительные 13 ключевые цепи. Первый каскад 1 содержит тактовый транзистор 14 n-типа, а второй 2 - проходной транзистор 15 n-типа.

Выходной блок 3 содержит первый 16 и второй 17 транзисторы p-типа, транзистор 18 n-типа и логические транзисторы n-типа первой группы 19, 20 и второй группы 21,22.

Затворы транзисторов 7-9 p-типа и тактового транзистора 14 n-типа первого каскада, а также затворы транзисторов 16 и 17 p-типа и 18 n-типа выходного блока 3 подключены к тактовой шине 23.

В каждом каскаде первые выводы 24-26 соответственно прямых 11, инверсных 12 и дополнительных 13 ключевых цепей подключены непосредственно к входам соответственно первого 4, второго 5 и третьего 6 инверторов и соединены дополнительно с шиной питания 27 соответственно через первый 7, второй 8 и третий 9 транзисторы p-типа. Вторые выводы тех же цепей подключены к общему выводу 28 логического блока 10 соответствующего каскада. Тактовый транзистор 14 n-типа и проходной транзистор 15 n-типа включены между общим выводом 28 логического блока 10 соответственно первого 1 и второго 2 каскадов и шиной земли 29. Выход третьего инвертора 6 первого каскада 1 подключен к объединенным затворам транзисторов 7-9 p-типа и проходного транзистора 15 n-типа второго каскада 2.

В выходном блоке 3 первый 16 и второй 17 транзисторы p-типа включены соответственно между первым 30 и вторым 31 выходами устройства и шиной питания 27. Между первым выходом 30 устройства и общим выводом 32 выходного блока 3 включены логические транзисторы первой группы 19, 20 n-типа, затворы которых подключены к выходам первых инверторов 4 каскадов 1 и 2. Между вторым выходом 31 устройства и общим выводом 32 выходного блока 3 включены логические транзисторы второй группы 21, 22 n-типа, затворы которых подключены к выходам вторых инверторов 5 тех же каскадов. Выход третьего инвертора 6 второго каскада 2 является третьим выходом 33 устройства.

Ключевые цепи 11-13 состоят из последовательно включенных транзисторов n-типа, затворы которых подключены к входам 34-37 каскада, на которые подаются парафазные сигналы входных переменных.

Логический блок 10 каскадов 1 и 2 устройства поразрядного сравнения на равенство и неравенство двух операндов (фиг.2) выполнен на шести 38-43 транзисторах n-типа. Прямая ключевая цепь 11 состоит из первого 38 и второго 39 транзисторов, инверсная 12 - из третьего 40 и четвертого 41 транзисторов, дополнительные ключевые цепи 13 содержат пятый 42, второй 39 и соответственно шестой 43, четвертый 41 транзисторы. Причем истоки второго 39 и четвертого 41 транзисторов являются общим выводом 28 логического блока 10.

На первый 34 и второй 35 входы первого 1 каскада, которые подключены к затворам первого 38, шестого 43 и соответственно третьего 40, пятого 42 транзисторов, подаются парафазные сигналы, соответствующие старшему разряду первого операнда, а на третий 36 и четвертый 37 входы того же каскада, которые подключены к затворам четвертого 41 и соответственно второго 39 транзисторов, подаются парафазные сигналы, соответствующие старшему разряду второго операнда. На одноименные входы второго каскада 2 подаются парафазные сигналы, соответствующие младшим разрядам первого и второго операндов. Причем первый 34 и третий 36 входы соответствуют прямому значению двоичного разряда, а второй 35 и четвертый 37 входы - логически дополняющему значению того же разряда. Двоичному значению логической 1 соответствует высокий уровень напряжения шины питания, а значению логического 0 - низкий уровень напряжения шины земли. Открытому или замкнутому состоянию транзистора n-типа соответствует сигнал логической 1, поданный на затвор транзистора.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при нулевом сигнале на тактовой шине 23 транзисторы 14 и 18 n-типа закрыты, а транзисторы p-типа первого каскада 7-9 и выходного блока 16-17 - открыты. От шины питания 27 через указанные транзисторы p-типа происходит процесс предзаряда узловых емкостей, связанных с входами первого, второго и третьего 4-6 инверторов первого каскада 1 и с первым 30, вторым 31 выходами устройства до уровня логической 1. При этом на выходах инверторов 4-6 первого каскада поддерживаются состояния логического 0. Поэтому проходной транзистор 15 n-типа закрыт, а транзисторы 7-9 p-типа второго каскада 2 открыты и на выходах инверторов 4-6 этого каскада, и на третьем выходе 33 устройства - также состояния логического 0. На первом полутакте на входах 34-37 каскадов 1 и 2 устанавливаются соответствующие парафазные сигналы. В данном примере устройства полного сравнения (больше-меньше-равно) двухразрядных (по числу каскадов) операндов А=Х2Х1 и В=У2У1 на входы 34-37 первого каскада 1 подаются сигналы, соответствующие старшим разрядам Х2 и У2, а на одноименные входы второго каскада 2 - сигналы, соответствующие младшим разрядам X1 и Y1 операндов.

На втором полутакте после подачи положительного сигнала на тактовую шину 23 тактовый транзистор 14 n-типа первого каскада 1 и транзистор 18 n-типа выходного блока 3 открываются, а транзисторы p-типа первого каскада и выходного блока закрываются.

Прямые ключевые цепи 11 в обоих каскадах реализуют функцию Х>У, поскольку указанная цепь может находиться в замкнутом состоянии только тогда, когда первый 38 и второй 39 транзисторы n-типа логического блока 10 открыты. Это возможно в том случае, когда в соответствующем логическом блоке Х=1, а У= 0. Другие ключевые цепи 12 и 13 при этом разомкнуты. Аналогично инверсные ключевые цепи 12 реализуют функцию Х<У, поскольку они могут быть в замкнутом состоянии при Х=0 и У=1, когда третий 40 и четвертый 41 транзисторы n-типа логического блока 10 открыты. Если эти логические ситуации реализуются уже в первом каскаде 1 (Х2>У2, или Х2<У2), то благодаря тому, что в одном случае - замкнутой является прямая ключевая цепь 11, а в другом случае инверсная ключевая цепь 12, соответствующие нагрузочные емкости разряжаются и на выходе первого 4 или второго 5 инверторов первого каскада формируется сигнал логической 1. Логический транзистор первой группы 19 или второй группы 21 n-типа выходного блока 3 при этом открывается, и на первом 30 или втором 31 выходах устройства формируется выходной сигнал логического 0, т.к. транзистор 18 n-типа выходного блока также открыт. Появление сигнала логического 0 на первом 30 или втором 31 выходах устройства свидетельствует о том, что по результату сравнения старших разрядов операндов А>В или А<В соответственно. Выход третьего инвертора 6 первого каскада при этом сохраняет состояние логического 0, т.к. один из транзисторов n-типа дополнительных ключевых цепей 13 логического блока 10 при поданных сигналах на входы 34-37 - закрыт и второй каскад 2 в дальнейшей работе устройства не участвует, а результат сравнения операндов уже формируется по старшим разрядам.

В случае равенства старших разрядов (Х2=У2=1 или Х2=У2=0) прямая 11 и инверсная 12 ключевые цепи первого каскада разомкнуты и на выходах первого 4 и второго 5 инверторов сохраняются значения логического 0, а выходы 30 и 31 устройства сохраняют свое исходное логическое значение. Одна из дополнительных ключевых цепей 13 в первом каскаде (например, при Х2=У2=1 - транзисторы 43 и 41) является замкнутой и на выходе третьего инвертора 6 первого каскада формируется сигнал логической 1. Проходной транзистор 15 открывается и второй каскад 2 работает точно также, как и первый в случае подачи на тактовую шину 23 положительного сигнала. Если входным переменным второго каскада соответствует состояние X1>У1 (или X1<У1) на выходе первого 4 (или второго 5) инверторов второго каскада формируется сигнал логической 1 и открываются соответствующие логические транзисторы n-типа выходного блока 3. На одном из выходов 30 или 31 устройства при этом формируется сигнал логического 0 как результат неравенства А>В (или А<В) по совокупности сравнения двух разрядов операндов А и В. Если во втором каскаде так же, как в первом, имеет место равенство X1=Y1, замкнутой оказывается одна из дополнительных ключевых цепей 13 логического блока 10 и на третьем выходе 33 устройства формируется сигнал логической 1 как признак равенства двухразрядных операндов (А=В).

Аналогично работает многоразрядное устройство, в котором число каскадов соответствует разрядности операндов и числу логических транзисторов в каждой из групп выходного блока. Включение в первую группу логических транзисторов выходного блока 3 дополнительного транзистора n-типа, затвор которого подключен к выходу третьего инвертора 6 последнего каскада, позволяет реализовать дополнительную функцию А≥В.

Каждому функциональному назначению устройства в логическом блоке 10 каждого каскада соответствует три типа ключевых цепей, соответствующих трем логическим функциям (две из которых могут быть взаимодополняющими). Каждая цепь реализует единичное множество состояний входных переменных (состояние замкнутости цепи), которые не должны логически пересекаться, т.е. при любом наборе входных переменных замкнутой может быть только одна из ключевых цепей. Ключевые цепи строятся из последовательно соединенных транзисторов по таблицам истинности соответствующих функций. При этом дополнительная ключевая цепь 13 в логическом блоке каждого каскада формирует условие включения последующего каскада, когда другие ключевые цепи и соответствующие им функции сохраняют нейтральное состояние.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| УСТРОЙСТВО СРАВНЕНИЯ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2236696C1 |

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2258303C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2515225C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2007 |

|

RU2355104C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в МДП интегральных схемах в качестве устройства логической обработки многоразрядных двоичных данных. В каждом каскаде К 1, 2 используются парафазные входы 34-37. Логический блок 10 содержит три типа ключевых цепей КЦ 11-13, выполненных на транзисторах Т n-типа, из которых замкнутой может быть только одна. В К введен третий инвертор 6 с соответствующими связями по входу с дополнительной КЦ 13 и по выходу - с проходным Т 15 и Т р-типа 7-9 последующего К. Устройство содержит выходной блок 3, выполненный в виде парафазного элемента ИЛИ-НЕ, входами которого являются выходы первого 4 и второго 5 инверторов каждого К. Технический результат: расширение функциональных возможностей устройства. 2 ил.

Парафазное каскадное логическое устройство на КМДП транзисторах, содержащее в каждом каскаде первый и второй инверторы, три транзистора р-типа и логический блок, содержащий прямые, инверсные и дополнительные ключевые цепи, которые состоят из последовательно соединенных транзисторов n-типа, затворы которых подключены к соответствующим входам каскада, на которые подаются парафазные сигналы входных переменных, в каждом каскаде прямые и инверсные ключевые цепи своим первым выводом подключены непосредственно к входам соответственно первого и второго инверторов и дополнительно соединены с шиной питания соответственно через первый и второй транзисторы р-типа, а вторым выводом подключены к общему выводу логического блока, дополнительные ключевые цепи в первом каскаде первым выводом соединены через третий транзистор р-типа с шиной питания, а вторым подключены к общему выводу логического блока, дополнительные ключевые цепи во всех других каскадах своим первым выводом соединены со стоком соответствующего третьего транзистора р-типа, затворы первых и вторых транзисторов р-типа в каждом каскаде объединены, а в первом каскаде дополнительно подключены к затвору третьего транзистора р-типа, к тактовой шине и затвору тактового транзистора n-типа, который включен между общим выводом логического блока и шиной земли, отличающееся тем, что устройство содержит выходной блок, в каждом каскаде, кроме первого - проходной транзистор n-типа, который включен между общим выводом логического блока и шиной земли, и в каждом каскаде - третий инвертор, вход которого соединен с первым выводом дополнительных ключевых цепей, а выход - с объединенными затворами проходного транзистора n-типа и транзисторов р-типа последующего каскада, вторые выводы дополнительных ключевых цепей, истоки третьих транзисторов р-типа, как и в первом каскаде подключены соответственно к общему выводу логического блока и к шине питания, в каждом логическом блоке только одна ключевая цепь является замкнутой при любом наборе парафазных сигналов входных переменных данного каскада, а выходной блок выполнен в виде парафазного элемента ИЛИ-НЕ и содержит первый и второй транзисторы р-типа, которые включены между шиной питания и соответственно первым и вторым выходами устройства, затворы которых подключены к тактовой шине и затвору транзистора n-типа, включенному между общим выводом выходного блока и шиной земли, между первым и вторым выходами устройства с одной стороны и общим выводом выходного блока - с другой включены две группы параллельно соединенных логических транзисторов n-типа, число которых в каждой группе соответствует числу каскадов устройства, затворы логических транзисторов n-типа первой группы подключены к выходам первых инверторов, а затворы логических транзисторов n-типа второй группы подключены к выходам вторых инверторов, выход третьего инвертора последнего каскада является третьим выходом устройства.

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| US 4780626, 25.10.1988 | |||

| ШАРНИРНЫЙ ОТКЛОНИТЕЛЬ КОМПОНОВКИ БУРИЛЬНОЙ КОЛОННЫ | 1992 |

|

RU2082864C1 |

| DE 3047222 А1, 15.07.1982. | |||

Авторы

Даты

2003-07-27—Публикация

2002-05-13—Подача