Изобретение относится к устройствам генерирования и/или/ распределения синхронизирующих импульсов и может быть использовано при построении вычислительных систем на базе нескольких однотипных цифровых вычислительных машин.

Известно устройство для синхронизации вычислительной системы, содержащее генератор, делители частоты, триггеры, элементы ИЛИ-НЕ 1.

Устройство используется для групповой синхронизации, обеспечивая сходимость временных диаграмм синхронизирующих схем блоков к общей системе отсчета времени, не прерывая их работы. Устройство спо- собно обеспечивать синхронную работу пространственно разобщенных схем синхронизации или блоков без разделения на ведущие или ведомые.

Недостатками этого устройства явля- ются низкая надежность и большой объем оборудования, необходимого для его реализации.

Известно устройство для синхронизации вычислительной системы, содержащее генератор тактовых импульсов /К - число каналов синхронизации/, К блоков управления, первую и вторую группы из К элементов И, группу из К элементов ИЛИ, элементы ИЛИ-НЕ, НЕ, триггер и элемент задержки

2.

Устройство позволяет осуществить синхронизацию однотактных распределителей импульсов, а также применимо для синхронизации двухтактных распределителей им- пульсов.

Целью изобретения является повышение быстродействия устройства для синхронизации.

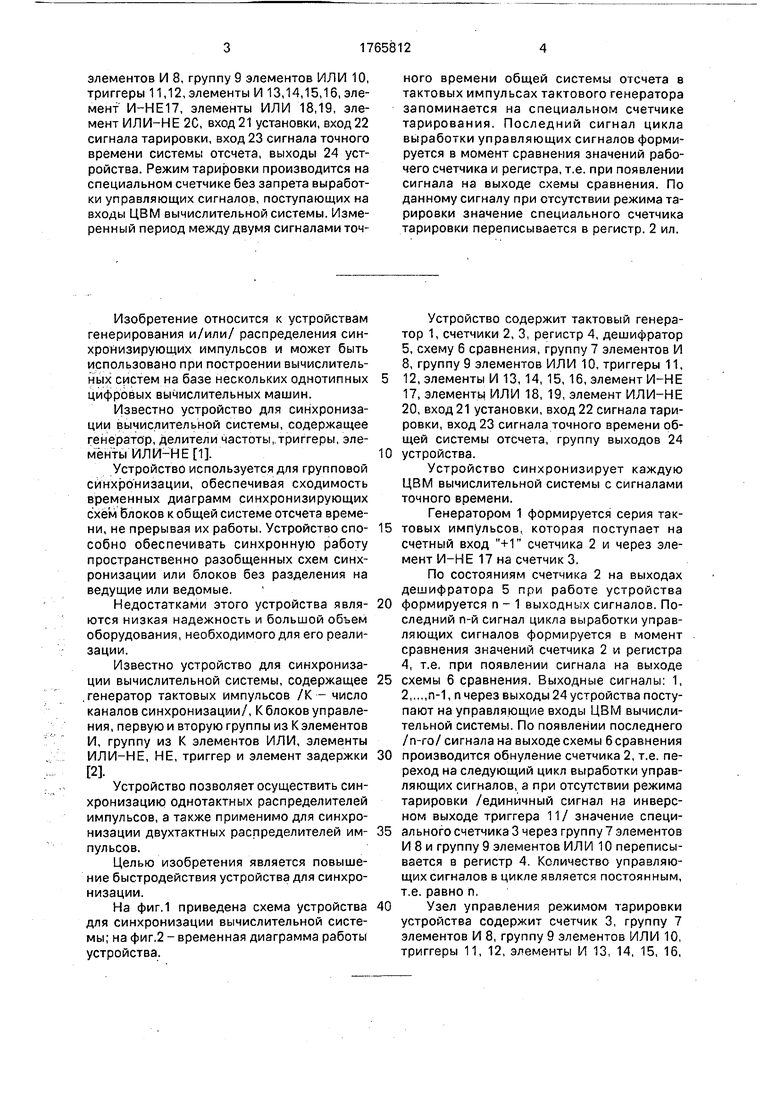

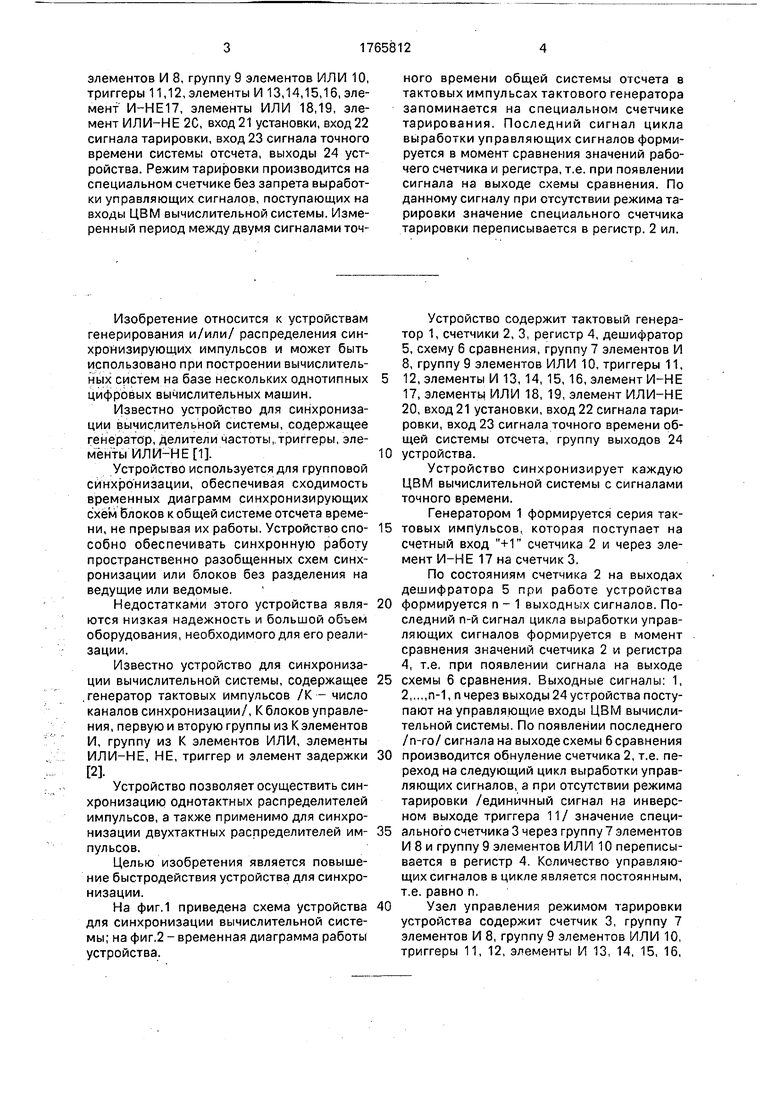

На фиг.1 приведена схема устройства для синхронизации вычислительной системы; на фиг.2 - временная диаграмма работы устройства.

Устройство содержит тактовый генератор 1, счетчики 2, 3, регистр 4, дешифратор 5, схему 6 сравнения,группу 7 элементов И 8, группу 9 элементов ИЛИ 10, триггеры 11, 12, элементы И 13,14, 15, 16, элемент И-НЕ 17, элементы ИЛИ 18, 19, элемент ИЛИ-НЕ 20, вход 21 установки, вход 22 сигнала тарировки, вход 23 сигнала точного времени общей системы отсчета, группу выходов 24 устройства.

Устройство синхронизирует каждую ЦВМ вычислительной системы с сигналами точного времени.

Генератором 1 фбрмируется серия тактовых импульсов, которая поступает на счетный вход +1 счетчика 2 и через элемент И-НЕ 17 на счетчик 3.

По состояниям счетчика 2 на выходах дешифратора 5 при работе устройства формируется п - 1 выходных сигналов. Последний n-й сигнал цикла выработки управляющих сигналов формируется в момент сравнения значений счетчика 2 и регистра 4, т.е. при появлении сигнала на выходе схемы 6 сравнения. Выходные сигналы: 1, 2п-1, п через выходы 24 устройства поступают на управляющие входы ЦВМ вычислительной системы. По появлении последнего /n-го/ сигнала на выходе схемы 6 сравнения производится обнуление счетчика 2, т.е. переход на следующий цикл выработки управляющих сигналов, а при отсутствии режима тарировки /единичный сигнал на инверсном выходе триггера 11/ значение специального счетчика 3 через группу 7 элементов И 8 и группу 9 элементов ИЛИ 10 переписывается в регистр 4. Количество управляющих сигналов в цикле является постоянным, т.е. равно п,

Узел управления режимом тарировки устройства содержит счетчик 3, группу 7 элементов И 8, группу 9 элементов ИЛИ 10, триггеры 11, 12, элементы И 13, 14, 15, 16,

элемент И-НЕ 17, элемент ИЛИ 18, 19, элемент ИЛИ-НЕ 20.

В начале работы вычислительной системы и устройства для синхронизации осуществляется приведение в исходное состояние всех счетчиков, регистров и триггеров, т.е. по сигналу установки по входу 21 обнуляется счетчик 2 и триггеры 11, 12. При этом в регистр 4 и счетчик 3 заносится фиксированная расчетная /номинальная/ величина, эквивалентная периоду между двумя сигналами точного времени общей системы отсчета в тактовых импульсах генератора 1. Затем после прохождения всех этапов тестовых проверок вычислительной системы проводится контроль наличия сигналов точного времени по входу 23 из смежной общей системы отсчета.

При отсутствии сигналов точного времени устройство работает автономно.

При наличии сигналов точного времени из ЦВМ по входу 22 устройства поступает сигнал разрешения тарировки.

Сигнал разрешения тарировки может поступать многократно за время работы устройства. Режим тарировки определяется двумя последовательно поступающими сигналами точного времени по входу 23. Пра,ч- тически сигнал тарировки формируется из ЦВМ очень родко, т.е. по мере накопления максимальней допустимой величины рае- синхронизации канала вычислительной системы от сигналов точного времени общей системы отсчета.

Величина несинхронности вызвана нестабильностью генератора 1.

Рассмотрим работу устройства при выполнении режима тарировки на временной диаграмме /см.фиг.2/.

В момент времени ц, во время появления сигнала тарировки по входу 22, сигнал поступает на С-вход триггера 12. При этом триггер 12 устанавливается в единичное состояние.

В момент времени t2, во время появления первого сигнала точного времени общей системы отсчета по входу 23, сигнал через элементы И 15, 14 поступает на С- вход триггера 11 и на вход обнуления счетчика 3. Единичный сигнал с прямого выхода триггера 11 поступает на вход элемента И- НЕ 17.

При этом тактовые импульсы из генератора 1 начинают поступать на счетный вход +1 счетчика 3.

В момент времени t4, во время появления второго сигнала точного времени общей системы отсчета по входу 23, сигнал через элементы И 15,13, ИЛИ-НЕ 20 поступает на входы триггеров 11,12. При этом прекращается поступление тактовых импульсов из генератора 1 на счетный вход +1 счетчика 3. Измеренная величина периода междудвумя сигналами точного времени общей системы

отсчета в тактовых импульсах генератора 1 хранится в счетчике 3 до следующего режима тарировки.

На этом режим тарировки прекращается.

0 Во время режима тарировки устройство использует только два последовательно покупающих сигнала точного времени по входу 23, а в остальное время данные сигналы не используются.

5 По состояниям счетчика 2 на выходах дешифратора 5 формируется п - 1 выходных сигналов.

В моменты времени ta-ts (моменты сравнения текущего значения счетчика 2 и вели0 чины на регистре 4, полученной в режиме тарировки или занесенной в начале работы вычислительной системы) на выходе схемы 6 сравнения формируется n-й выходной сигнал, который через элемент ИЛИ 18 посту5 пает на вход обнуления счетчика 2, т.е. переход на следующий цикл выработки управляющих сигналов. При этом количество управляющих сигналов в цикле является постоянным, т.е равно п. Выходные сигналы:

0 1, 2 п - 1, п через выходы 24 устройства

поступают на управляющие входы ЦВМ вычислительной системы.

В момент времени ts, при отсутствии режима тарировки (единичный сигнал на ин5 версном выходе триггера 11) по сигналам с выходов элементов И 16, ИЛИ 19 результат режима тарировки из счетчика 3 через группу 7 элементов И 8 и группу 9 элементов ИЛИ 10 переписывается на регистр 4.

0 Экспериментальные исследования устройства для синхронизации вычислительной системы в составе опытного образца вычислительного пробора показали, что по сравнению с устройством аналогичного

5 назначения /прототип/ заявляемое устройство обеспечивает повышение быстродействия, т.е. повышение эффективности вычислительной системы путем совмещения рабочего режима тарировки, т.е. прове0 дение режима тарировки на отдельном счетчике без запрета выработки управляющих сигналов, поступающих на входы ЦВМ вычислительной системы.

Формула изобретения

5Устройство для синхронизации вычислительной системы, содержащее тактовый генератор, первый счетчик, регистр, дешифратор, схему сравнения, группу элементов И, два IK-триггера, три элемента И, первый элемент ИЛИ, причем инверсный выход тактового генератора соединен со счетным входом счетчика, группа выходов которого соединена с группой входов дешифратора и с первой группой входов схемы сравнения, группа выходов регистра соединена с вто- рой группой входов схемы сравнения, прямой выход первого триггера соединен с первым входом первого элемента И, а инверсный выход первого триггера - с первым входом второго элемента, вход сигнала том- ного времени общей системы отсчета устройства соединен с первым входом третьего элемента И, выход которого соединен с вторыми входами первого и второго элементов И, прямой выход второго триггера соединен с третьим входом второго элемента И и вторым входом третьего элемента И, выход второго элемента И соединен с С-входом первого триггера, вход сигнала тарировки устройства соединен с С-входом второго триггера, выход первого элемента ИЛИ соединен с входом обнуления первого счетчика, вход единичного потенциала устройства соединен с 1-входами первого и второго триггеров, вход нулевого потенциала уст- ройства соединен с К-входами триггеров, отличающееся тем, что, с целью повышения быстродействия, в устройство введены второй счетчик, группа элементов ИЛИ, четвертый элемент И, второй элемент ИЛИ, элемент И-НЕ и элемент ИЛИ-НЕ, причем прямой выход тактового генератора соединен с первым входом элемента И-НЕ,

второй вход которого соединен с прямым выходом первого триггера, выход элемента И-НЕ соединен со счетным входом второго счетчика, выходы которого соединены с первыми входами элементов И группы, выход схемы сравнения соединен с первыми входами четвертого элемента И и первого элемента ИЛИ, инверсный выход первого триггера соединен с вторым входом четвертого элемента И, выход которого соединен с вторыми входами элементов И группы и первым входом второго элемента ИЛИ, выход второго элемента И соединен с входом обнуления второго счетчика, выход первого элемента И соединен с первым входом элемента ИЛИ-НЕ, вход установки устройства соединен с вторыми входами второго элемента ИЛИ, элемента ИЛИ-НЕ и с входом записи второго счетчика, выход второго элемента ИЛИ соединен с входом записи регистра, выход элемента ИЛИ-НЕ соединен с R-входами первого и второго триггеров, выходы элементов И группы соединены с первыми входами элементов ИЛИ группы, входы которых соединены с информационными входами регистра, вход установки устройства соединен с информационными входами второго счетчика и вторыми входами элементов ИЛИ группы, группа выходов дешифратора и выход схемы сравнения образуют группу выходов устройства для подключения к группе управляющих входов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1991 |

|

SU1830527A1 |

| Устройство для синхронизации вычислительной системы | 1986 |

|

SU1363172A1 |

| Устройство для синхронизации вычислительной системы | 1985 |

|

SU1291953A1 |

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1149235A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ МАГИСТРАЛЕЙ | 1990 |

|

RU2017210C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ АБОНЕНТОВ С ЦВМ | 1991 |

|

RU2018942C1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Многоканальное устройство для сопряжения абонентов с ЦВМ | 1990 |

|

SU1777146A1 |

| Устройство ввода информации | 1991 |

|

SU1784988A1 |

| Устройство для сопряжения электронной вычислительной машины с магнитофоном | 1989 |

|

SU1711169A1 |

Изобретение относится к устройствам генерирования и/или/ распределения синхронизирующих импульсов и может быть испспьзовано при построении вычислительных систем на базе нескольких однотипных цифровых вычислительных машин. Цель изобретения - повышение быстродействия устройства. Устройство содержит тактовый генерзтср 1, счетчики 2,3, регистр 4, дешифратор 5, схему 6 сравнения, группу 7

| Устройство для синхронизации вычис-лиТЕльНОй СиСТЕМы | 1978 |

|

SU809132A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1263172, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-09-30—Публикация

1990-12-25—Подача