Изобретение относится к вычисли тельной технике и может быть исполь зовано при построении вычислительных систем на базе нескольких однотипных цифровых вычислительных машин.

Цель изобретения - сокращение времени подсинхронизации.

На фиг. 1 приведена схема устройства для синхронизации вычислительной ю явления первого сигнала точного вре

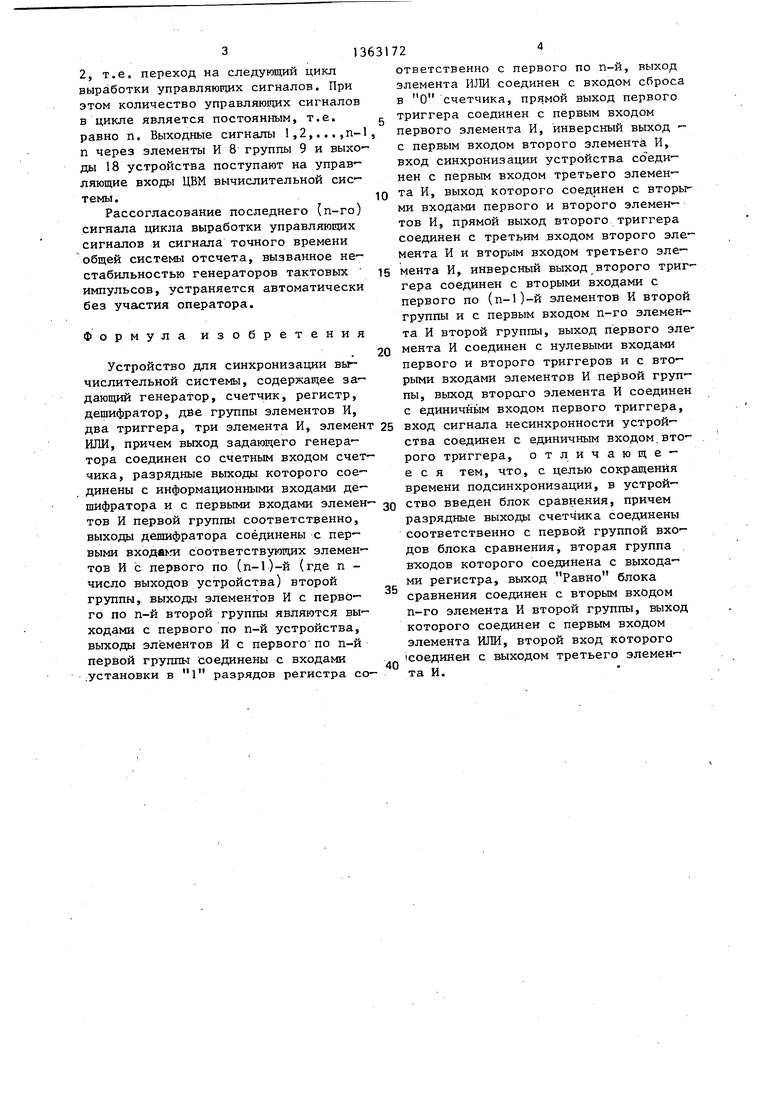

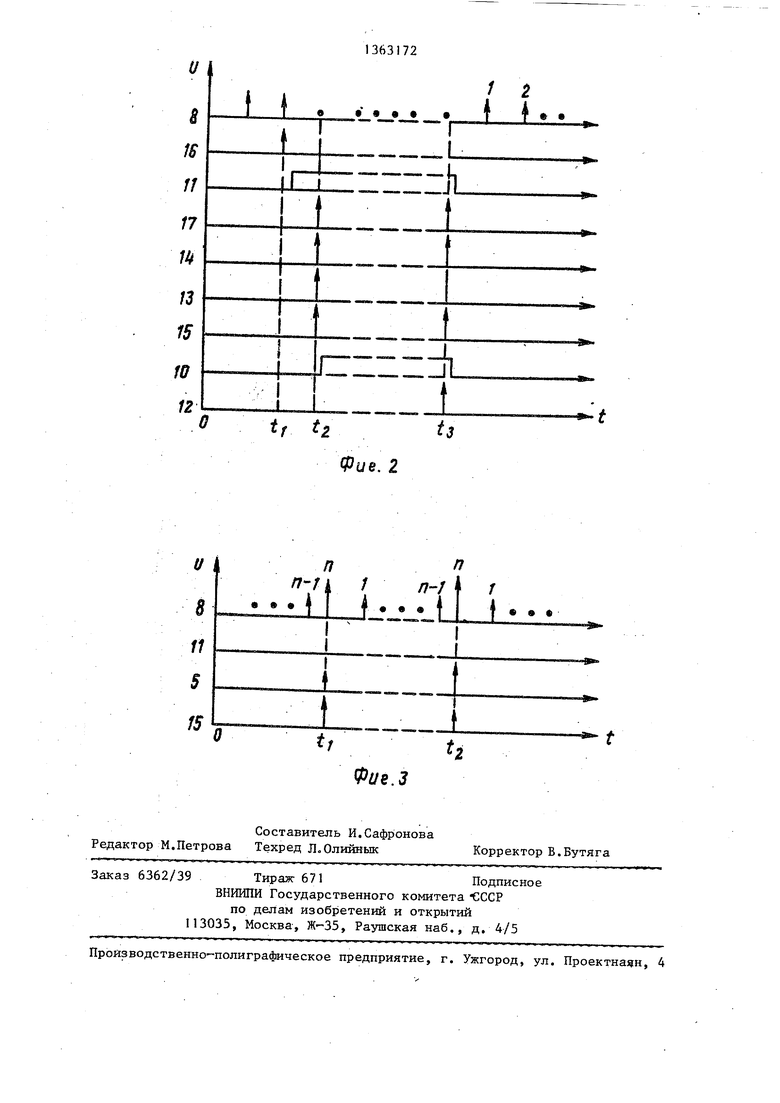

системы; на фиг. 2 - временная диаграмма работы устройства в режиме тарировки; на фиг. 3 - то же, в .рабочем режиме.

Устройство содержит задающий гене- ратор 1, счетчик 2, регистр 3, дещиф- ратор 4, блок 5 сравнения, элементы И 6 первой группы 7, элементы И 8 второй группы 9, триггеры 10 и 11, элементы И 12-14, элемент ИЛИ 15, вход 16 сигнала несинхронности, вход 17 сигнала точного времени общей системы отсчета и выходы 18 устройства.

Устройство работает следующим образом.

Задающим генератором 1 формируется серия тактовых импульсов, которая поступает на счетный вход счетчика 2. По состояниям последнего на выходах дешифратора 4 при работе устройства формируется (п-1) выходных сигналов. В рабочем режиме вычислит.ель- ной системы последний (п-й) сигнал цикла выработки управляющих сигналов формируется в момент сравнения значе

НИИ счетчика 2 и регистра 3,.е. при появлении сигнала на выходе блока 5 сравнения.

Выходные сигналы 1,2...п-1,п через выходы I а устройства поступают на управляющие входы ДВМ вычислительной системы. По появлении последнего (п-1го) сигнала на выходе элемента ИЛИ 15 производится сброс счетчика 2 в О, т.е. переход на следующий цикл выработки управляющих сигналов. При этом количество -управляющих сигналов в цикле является постоянным, т.е. равно п.

Элементы И 6 группы 7, триггеры 10 и 11, элементы И 12-14 осуществляют управление режимом тарировки.

В исходном состоянии триггеры 10 и 1j обнулены.

Рассмотрим работу устройства при выполнении режима тирировки на временной диаграмме (фиг. 2).

В момент времени t, (во время появления сигнала несинхроннрсти по

входу 16) сигнал поступает на единичный вход триггера 11. При этом триггер 11 устанавливается в единичное состояние, инверсный выход которого запрещает выработку управляющих сигналов на выходах элементов И 8 группы 9.

В момент времени

tj (во время помени общей системы отсчета по строби- рующему входу 17) сигнал через элементы И 14 и 13 поступает на единичный вход триггера 10 и через элемент ИЛИ 15 - на вход сброса в О счетчика 2, т.е. переход на следующий цикл выработки управляющих сигналов.

В момент времени t4 (во время по

явления второго сигнала точного времени общей системы отсчета по входу 17) сигнал через элементы И 14 и 12 поступает на нулевые входы триггеров 10 и 11.

По данному сигналу измеренная ве- личина периода между двумя сигналами точного времени общей системы отсчета в тактовых импульсах задающего ге нератора 1 из счетчика 2 через элементы И 6 Группы 7 переписывается на регистр 3 и хранится там до следующего режима тарировки. Сигнал с выхода элемента И 14 поступает также через элемент ИЛИ 15 на вход сброса в О счетчика 2, т.е. переход на следующий цикл выработки управляющих сигналов. Снимается запрет на выработку управляющих сигналов на выходах элементов И 8 группы 9. На этом режим тарировки прекращается.

Во время режима тарировки устройство использует только два последова- тельно поступающих сигнала точного времени по входу 17, а в остальное время данные сигналы не используются.

Рассмотрим работу устройства в

рабочем режиме (фиг. 3).

В данном режиме триггеры 10 и 11 обнулены. По состояниям счетчика 2 на выходах дешифратора 4 формируются (п-1) выходных сигналов.

В момент времени t,-tg (момент сравнения текзщего значения счетчика 2 и величины на регистре 3, полученной в режиме тарировки) на выходе блока 5 сравнения формируется п-й ходной сигнал, который через элемент И 8 группы 9 и элемент ИЛИ 15 поступает на вход сброса в О счетчика

313631

2, т.е. переход на следующий цикл выработки управляющих сигналов. При этом количество управляющих сигналов в цикле является постоянным, т.е. равно п. Выходные сигналы 1,2,.,.,п-1, п через элементы И 8 группы 9 и выходы 18 устройства поступают на управляющие входы ЦВМ вычислительной системы.10

Рассогласование последнего (п-го) сигнала цикла выработки управляющих сигналов и сигнала точного времени общей системы отсчета, вызванное нестабильностью генераторов тактовых 15 импульсов, устраняется автоматически без участия оператора.

Формула изобретения

Устройство для синхронизации вычислительной системы, содержащее задающий генератор, счетчик, регистр, дешифратор, две грзтгпы элементов И, два триггера, три элемента И, элемент ИЛИ, причем выход задающего генератора соединен со счетным входом счетчика, разрядные выходы которого соединены с информационными входами дешифратора и с первыми входами элемен- тов И первой группы соответственно, выходы дешифратора соединены с первыми входит соответствующих элементов И с первого по (п-1)-й (где п - число выходов устройства) второй группы, выходы элементов И с первого по п-й второй группы являются выходами с первого по п-й устройства, выхода элементов И с первого по п-й первой группы соединены с входами

.установки в 1 разрядов регистра со-

0

15

0

25 Q

40

724

ответственно с первого по п-й, выход элемента ИЛИ соединен с входом сброса в О счетчика, прямой выход первого триггера соединен с первым входом первого элемента И, инверсный выход - с первым входом второго элемента И, вход синхронизации устройства со еди- нен с первым входом третьего элемента И, выход которого соединен с вторьр- ми входами первого и второго элементов И, прямой выход второго триггера соединен с третьим входом второго элемента И и вторым входом третьего элемента И, инверсный выход второго триггера соединен с вторыми входами с первого по (п-1)-й элементов И второй группы и с первым входом п-го элемента И второй группы, выход первого эле- мента И соединен с нулевыми входами первого и второго триггеров и с вторыми входами элементов И первой группы, выход втораго элемента И соединен с единичным входом первого триггера, вход сигнала несинхронности устройства соединен с единичным входом.второго триггера, отличающееся тем, что, с целью сокращения времени подсинхронизации, в устройство введен блок сравнения, причем разрядные выходы счетчика соединены соответственно с первой группой входов блока сравнения, вторая группа . входов которого соединена с выходами регистра, выход Равно блока сравнения соединен с вторым входом п-го элемента И второй группы, выход которого соединен с первым входом элемента ИЖ, второй вход которого соединен с выходом третьего элемента И.

tr 2

Фие. 2

j

/7

n-r k1/7-/ f /

f If , f I I

ч-J «O bWCTI AlTT JIILJ Lt J .П111 1111 , ГПI ILI 1

г

Фие.З

Составитель И.Сафронова Редактор М.Петрова Техред ЛоОлийнык

Заказ 6362/39 Тираж- 671Подписное

ВНИШИ Государственного комитета ССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектна)н, 4

t3

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1985 |

|

SU1291953A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1149235A1 |

| Устройство для синхронизации вычислительной системы | 1987 |

|

SU1495773A1 |

| Устройство для синхронизации вычислительной системы | 1990 |

|

SU1765812A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1226428A1 |

| Устройство для синхронизации вычислительной системы | 1988 |

|

SU1529205A1 |

| Устройство для синхронизации вычислительной системы | 1991 |

|

SU1830527A1 |

| Многоканальное устройство синхронизации | 1987 |

|

SU1539759A1 |

| Многоканальное устройство синхронизации | 1988 |

|

SU1642473A1 |

Изобретение относится к вычис лительной технике и может быть ис пользовано при построении вычислительных систем на базе нескольких однотипных цифровых вычислительных машин. Целью изобретения является сокращение времени подсннхронизации. Отличительной особенностью устройства является то, что оно позволяет сократить время подсинхронизации вычислительной системы путем проведения режима тарировки с измерением периода выработки управляющих сигналов с учетом величины несинхронности, вызванной нестабильностью задающего генератора. Поставленная цель достигается за счет введения блока 5 сравнения. 3 ил. 35

| Устройство для синхронизации вычис-лиТЕльНОй СиСТЕМы | 1978 |

|

SU809132A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-04-28—Подача