Известен способ задержки в регистрах сдвига случайных импульсных сигналов, интервалы между которыми не меньше периода сдвига в медленном регистре. В устройствах, построенных по известному способу, точность задания задержек определяется частотой сдвига и возможно получение набора задержек, линейно зависящих от номера переключаемого элемента. В случае больших задержек и высокой точности для построения этих устройств требуется большое количество аппаратуры.

Предложенный способ отличается от известного тем, что задерживаемый сигнал одновременно подают в мед.ченный и скоростной регистры, сдвиговые частоты которых кратны и синфазны, причем продвижение сигнала в скоростном регистре прекраш;ают при первом сдвиге в медленном регистре, а вышедший из медленного регистра сигнал вновь пропускается через оставшееся число ячеек скоростного регистра. При этом основная задержка происходит в медленном регистре, а точность определяется скоростным регистром. Это приводит к существенному упрощению получения линейного набора длительных точных задержек случайного сигнала.

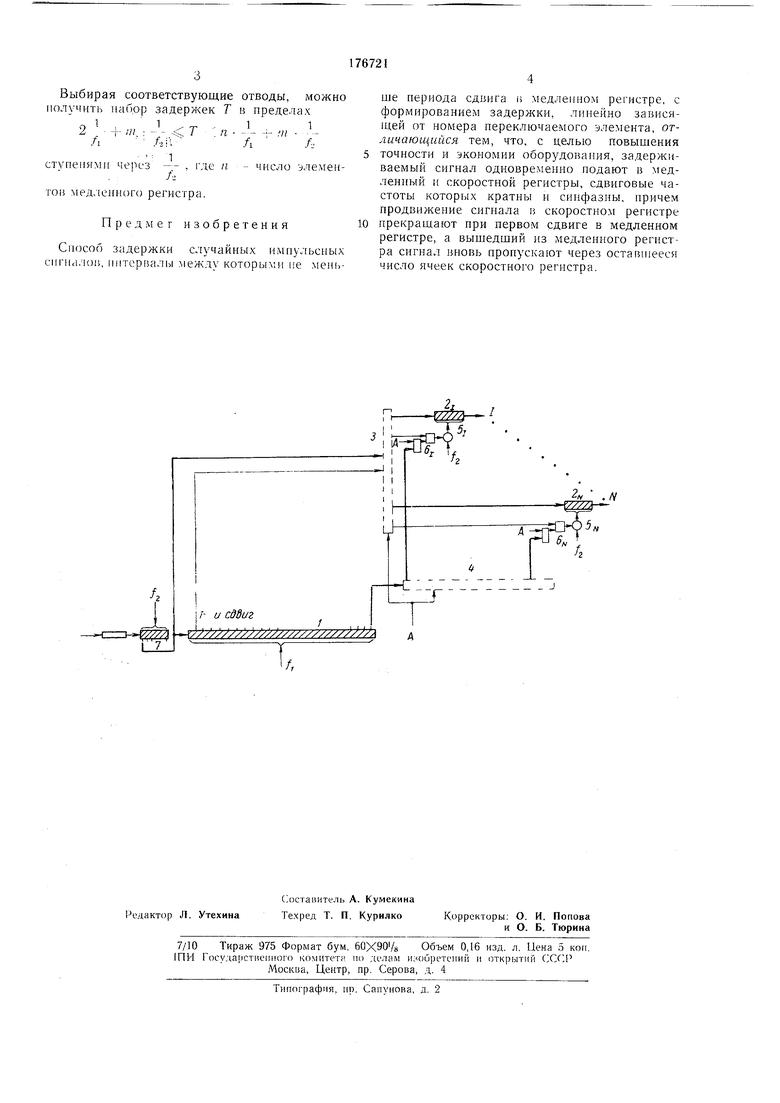

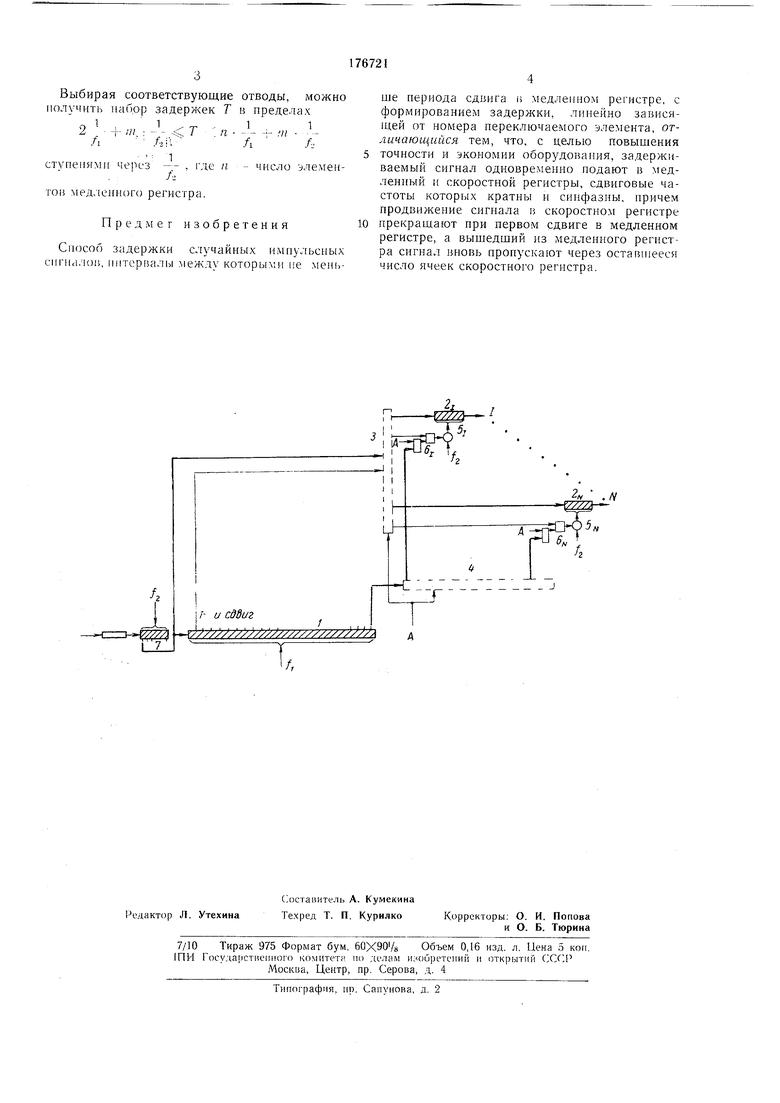

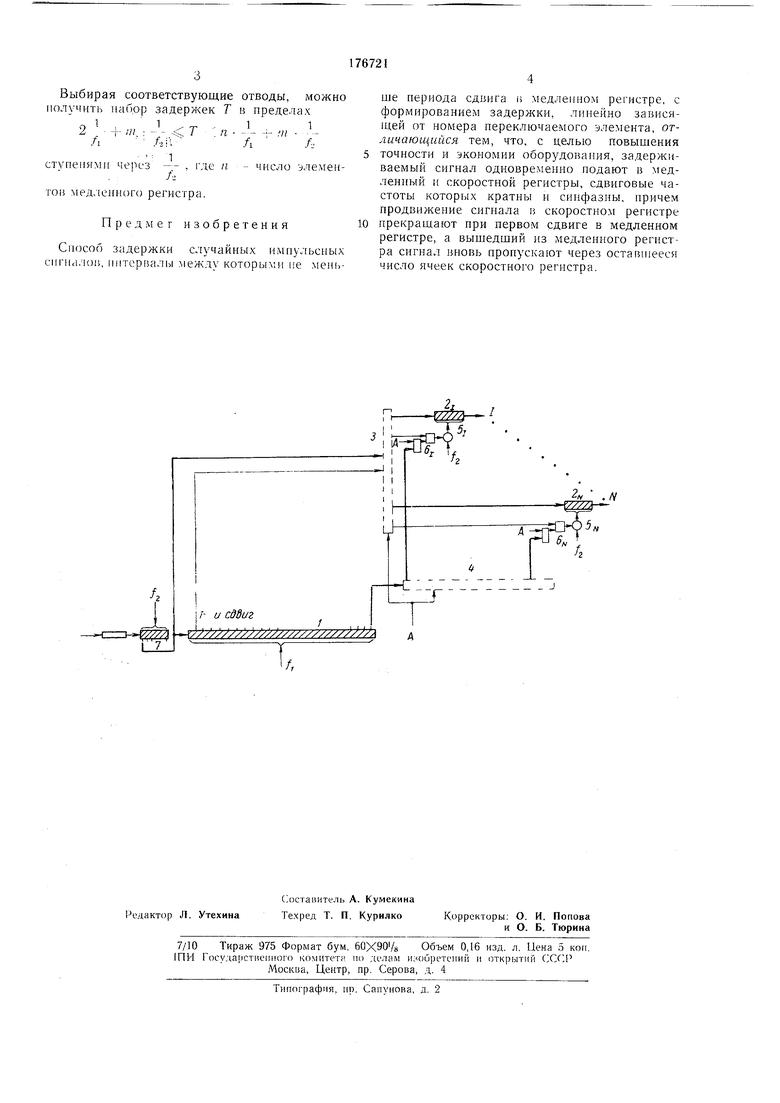

На чертеже приведено устройство, построенное в соответствии с предлагаемым способом.

В медленном регистре / частота продвижения сигналов равна /ц, в быстрых регистрах /, .... 2лг, число которых Л равно числу одновременно задерживаемых сигналов, частота продвижения сигналов равна 1-у. Частоты /ц и /2 синфазны и f- m-f, где т равно числу элементов (триггеров) в каждом быстром регистре.

Вначале сигнал синхронизации ,4 ставит

коммутаторы 3 к 4 в положение / канала, а вентили 5/, ..., 5д, в открытое положение. Первый задерживаемый сигнал подается одновременно в медленный и быстрый регистры. При первом же сдвиге в регистре / триггер

6f устанавливается в положение, при котором закрывается вентиль 5/. Вслед за этим коммутатор 3 ставится Б положение канала //. и процесс повторяется.

Выходящий из регистра / первый задержанный сигнал проходит через коммутатор 4 к триггеру 6i, сбрасывает его, открывая тем самым вентиль 5ц. Этим обеспечивается прохождение сигнала через остав1ииеся ячейки быстрого регистра 2/. Коммутатор 4 первым

сигналом с регистра J ставится li по.аожеиие // канала, и процесс повторяется.

Для получения линейного набора задержек, кратного такту сдвига в быстром регистре, на входе установлен регистр 7, аналогичный реВыбирая соответствующ

получить набор

задержек I , 1

Л Л1 J

ступенями через - , где

Л тов медленного регистра.

Предмет изобретения

Способ задержки случайных импульсных сигн.1/101, интервалы мелчду которыми не меньше нериода сдвига i медленном регистре, с формированием задерл ки, лииейно зависящей от номера переключаемого элемента, отличающийся тем, что, с целью повышения точности и экономии оборудоваиия, задерживаемый сигнал одновременно подают в медленный и скоростной регистры, сдвиговые частоты которых кратны и сиифазпы, причем продвижение сигнала и скоростном регистре прекращаЕот при первом сдвиге в медленном регистре, а вышедший из медленного регистра сигнал вновь пропускают через оставгиееся число ячеек скоростного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА С ПРОГРАММИРУЕМЫМ СОГЛАСОВАННЫМ ФИЛЬТРОМ ДЛЯ ПОИСКА МНОЖЕСТВЕННЫХ ПИЛОТ-СИГНАЛОВ | 2000 |

|

RU2254680C2 |

| ПРОЦЕССОР ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2000 |

|

RU2180969C1 |

| СПОСОБ ПОСТРОЕНИЯ ЦИФРОВЫХ КИХ-ФИЛЬТРОВ СЕТЕВОЙ СТРУКТУРЫ | 2013 |

|

RU2541874C2 |

| ХАОТИЧЕСКИЕ КОДЫ РАСШИРЕНИЯ СПЕКТРА И ИХ СОЗДАНИЕ | 2007 |

|

RU2462819C2 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| Калибратор переменного напряжения | 1983 |

|

SU1115031A1 |

| Устройство интерполяции для отображения графической информации | 1988 |

|

SU1525717A1 |

| СИСТЕМА И СПОСОБ ОПРЕДЕЛЕНИЯ АМПЛИТУДЫ И ФАЗОВОЙ ЗАДЕРЖКИ СИНУСОИДАЛЬНОГО СИГНАЛА | 2017 |

|

RU2729455C2 |

| УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ ДВИЖУЩИХСЯ ЦЕЛЕЙ | 1991 |

|

RU2255354C2 |

| Устройство задержки | 1991 |

|

SU1800601A1 |

-N

Даты

1965-01-01—Публикация