Изобретение относится к области вычислительной техники и может быть использовано в высокопроизводительных системах обработки больших массивов информации, в том числе, и в режиме реального времени.

Известны процессоры матричного типа, объединенные в матрицу процессоров, которая работает под управлением центрального компьютера [1]. Недостатком устройств данного типа является то, что все процессоры выполняют одну и ту же команду, что ведет к снижению быстродействия при обработке массивов данных, по размеру не кратных числу процессоров. Кроме того, при выполнении программ с малым количеством ветвей большинство процессоров простаивает.

Наиболее близкой к описываемому изобретению (прототип) является однородная вычислительная среда с программируемой коммутационно-запоминающей структурой, содержащая матрицу вычислительных ячеек, соединенных двусторонними связями по вертикали и горизонтали, матрицу запоминающих ячеек, соединенных двусторонними связями по вертикали и горизонтали, причем каждая вычислительная ячейка содержит арифметико-логическое устройство (АЛУ), регистр команд и дешифратор кода операций, два элемента задержки, три схемы коммутации входов и четыре схемы коммутации выходов, а каждая запоминающая ячейка содержит управляющий регистр, сдвиговый регистр, четыре входных коммутатора, пять выходных коммутаторов, вентиль, триггер задержки и переключатель, причем каждая запоминающая ячейка соединена двусторонними связями с соответствующей вычислительной ячейкой [2].

Существенным недостатком такого устройства является то, что при работе вычислительных ячеек (процессоров) однородной вычислительной среды соответствующие им запоминающие ячейки зачастую не используются. Кроме того, при перезаписи программы в матрицы вычислительных и запоминающих ячеек работа всех АЛУ останавливается, что снижает производительность.

Объединение схем процессора и запоминающей ячейки, введение блока настройки и обеспечение возможности записывать команду в блок настройки одновременно с работой АЛУ, повышает эффективность использования узлов процессора, позволяет наиболее быстро и эффективно выполнять сложные программы.

Техническим результатом предлагаемого технического решения является повышение производительности работы вычислительной системы.

Такой технический результат достигается тем, что в известное устройство введены второй переключатель, первый и второй блоки задержек, контроллер, блок настройки, который первой и второй управляющими шинами связан с первой и второй группами управляющих входов-выходов арифметико-логического устройства, а третья, пятая и шестая управляющие шины, соответственно, соединяют третью, пятую и шестую группы управляющих входов-выходов блока настройки с группами управляющих входов-выходов сдвигающего регистра, входного и выходного коммутатора, причем четвертая управляющая шина соединяет четвертую группу управляющих входов-выходов блока настройки с группами управляющих входов-выходов первого и второго блоков задержек и элемента задержки, вход которого соединен с выходом второго переключателя, при этом первая и вторая группы входов контроллера являются соответственно программными и управляющими входами процессора, а первая и вторая группы выходов контроллера соединены соответственно с группами программных и управляющих входов блока настройки, программный выход которого является программным выходом процессора, причем управляющий выход контроллера соединен с управляющим входом арифметико-логического устройства, группа информационных выходов которого соединена с группой информационных входов первого блока задержек, группа информационных выходов которого соединена с первой группой информационных входов выходного коммутатора, а группа управляющих выходов арифметико-логического устройства соединена со второй группой управляющих входов сдвигового регистра, управляющий и информационный вход которого соединены, соответственно, с управляющим и информационным выходами первого переключателя, а первая группа управляющих входов соединена с группой управляющих выходов входного коммутатора, управляющий и информационный выходы которого соединены, соответственно, с первым управляющим и первым информационным входами первого переключателя, второй и третий управляющие и второй информационный входы которого, соответственно, соединены со вторым и третьим управляющими и вторым информационным выходами арифметико-логического устройства, а группа информационных входов арифметико-логического устройства соединена с первой группой информационных выходов входного коммутатора, при этом информационный выход сдвигового регистра соединен с информационным входом арифметико-логического устройства и с первым информационным входом второго переключателя, управляющий и второй информационный входы которого соединены с первым управляющим и первым информационным выходами арифметико-логического устройства, причем вторая группа информационных выходов входного коммутатора соединена с группой информационных входов второго блока задержек, группа информационных выходов которого соединена со второй группой информационных входов выходного коммутатора, информационный выход которого соединен с информационным входом входного коммутатора, при этом блок настройки содержит оперативное запоминающее устройство, третий переключатель и регистр настройки, первая, вторая, третья, четвертая, пятая и шестая группы управляющих входов-выходов которого являются, соответственно, первой, второй, третьей, четвертой, пятой и шестой группами управляющих входов-выходов блока настройки, группа программных выходов которого соединена с группой выходов третьего переключателя, группа управляющих входов которого связана с группой управляющих входов блока настройки и группами управляющих входов оперативного запоминающего устройства и регистра настройки, группа программных входов которого соединена с программными входами блока настройки и оперативного запоминающего устройства, группа информационных входов-выходов которого шиной ввода-вывода данных связана с группой информационных входов-выходов регистра настройки, причем оперативное запоминающее устройство и регистр настройки через третий переключатель связаны с программным выходом процессора.

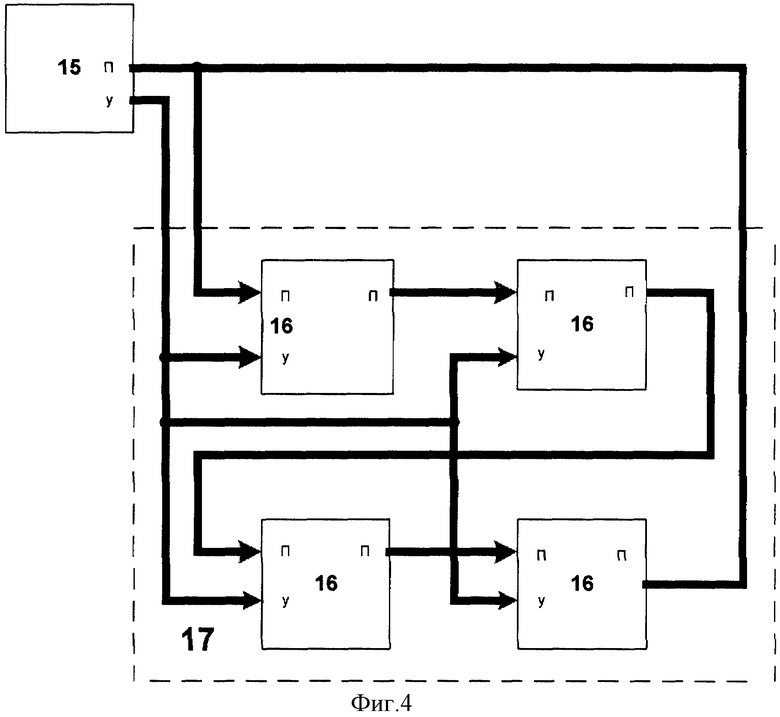

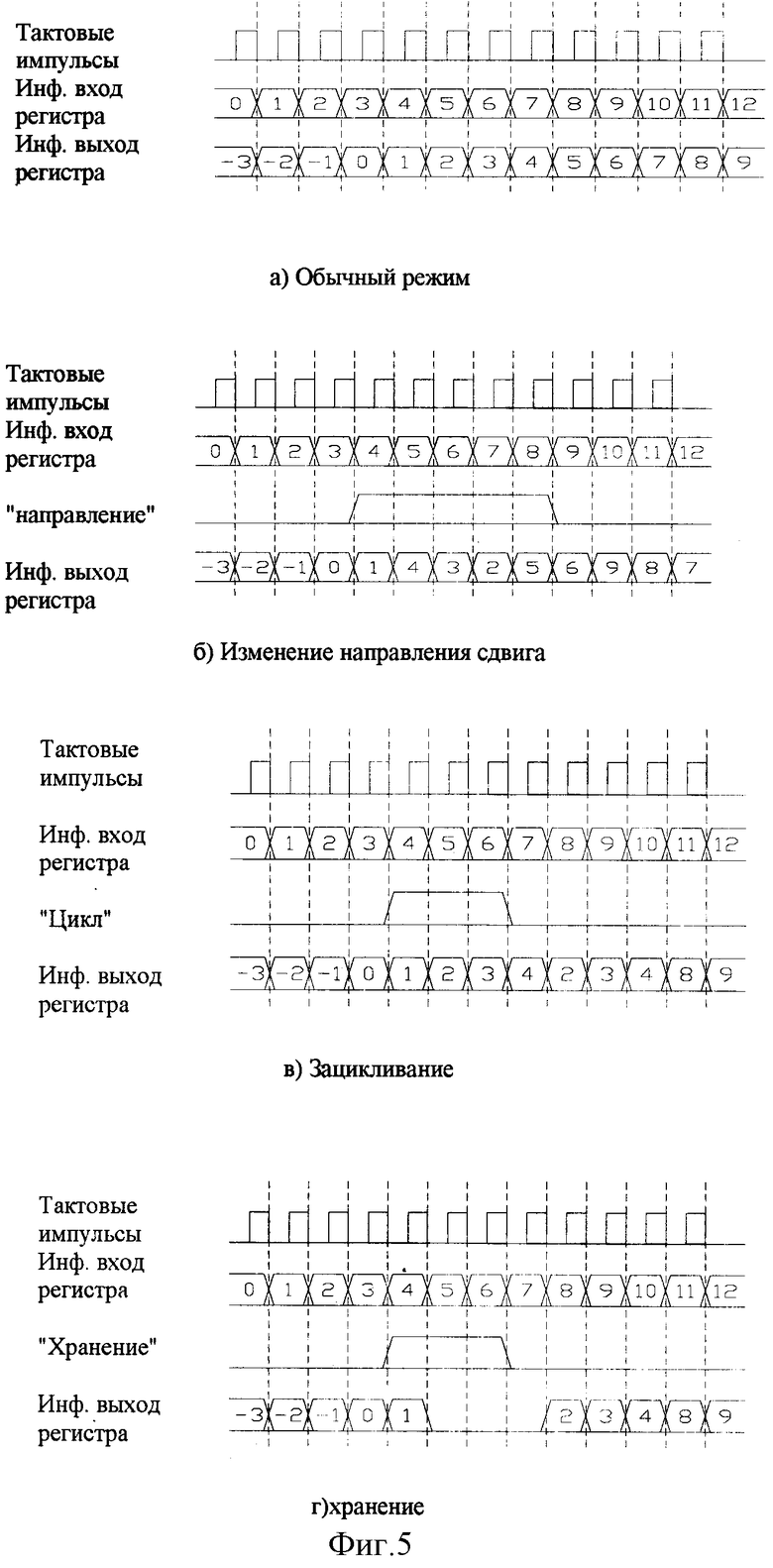

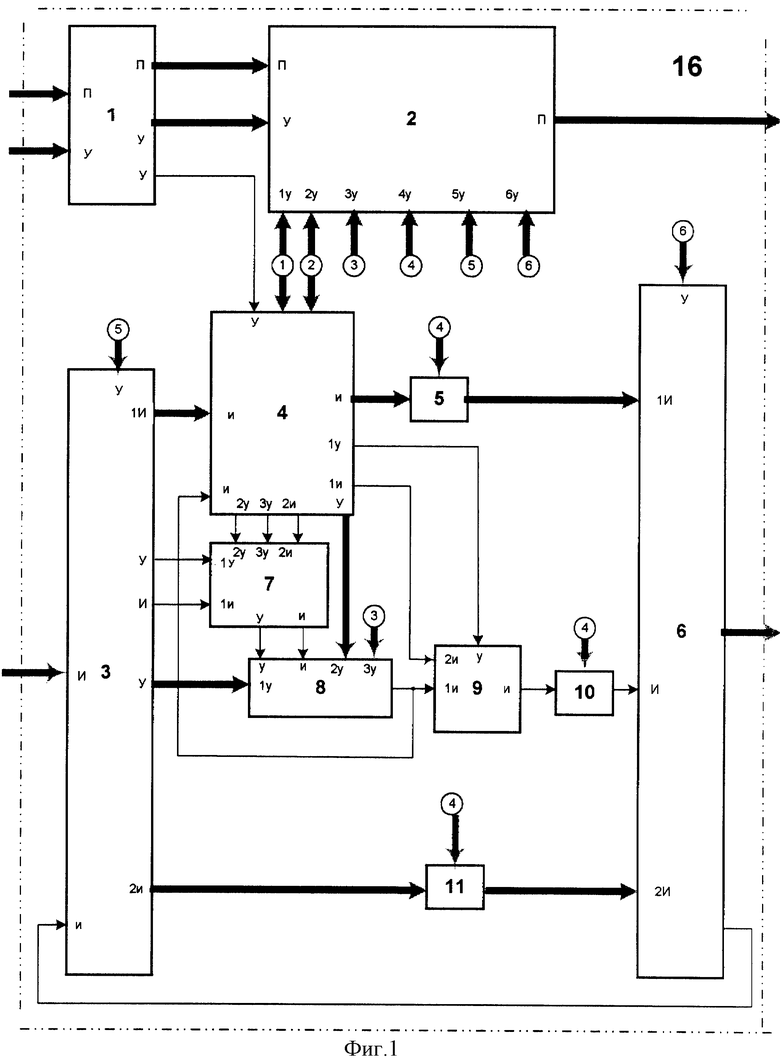

На фиг. 1 приведена структурная схема процессора, на фиг. 2 - структурная схема блока настройки, на фиг. 3 - вариант построения структурной схемы матрицы процессоров с последовательным соединением программных входов, на фиг. 4 - вариант построения структурной схемы матрицы процессоров с параллельным соединением программных входов; на фиг. 5 (а, б, в, г) - временные диаграммы различных режимов работы сдвигового регистра. На фигурах приняты следующие обозначения: 1 - контроллер; 2 - блок настройки; 3 - входной коммутатор; 4 - арифметико-логическое устройство (АЛУ); 5 - первый блок задержек; 6 - выходной коммутатор; 7 - первый переключатель; 8 - сдвиговый регистр; 9 - второй переключатель; 10 - элемент задержки; 11 - второй блок задержек, 12 - оперативное запоминающее устройство (ОЗУ), 13 - регистр настройки, 14 - третий переключатель, 15 - устройство управления матрицей процессоров, 16 - процессор, 17 - матрица процессоров. Шины ввода-вывода пронумерованы цифрами в кружках. Типы и порядковые номера тех входов-выходов, для которых невозможно установить взаимно-однозначное соответствие между текстом и графическим изображением, указаны на фиг. 1-4. Для них приняты следующие сокращения: И - информационный, П - программный, У - управляющий (таким образом, "2у" на фиг. 1 обозначает "второй управляющий").

Контроллер 1 формирует сигналы, управляющие работой процессора 16. Блок 2 настройки предназначен для хранения информации, передаваемой в ходе работы в блок 2 настройки и получаемой из него, а также для настройки отдельных блоков на выполняемую команду. Перед началом выполнения команды регистр 13 настройки содержит информацию о начальной установке всех триггеров процессора, а по окончании программы - информацию о их текущей установке. Входной коммутатор 3 обеспечивает соединение информационных входов процессора с блоками процессора. АЛУ 4 выполняет над входными данными операции, заданные в регистре 13 настройки. Первый 5 и второй 11 блоки задержек предназначены, соответственно, для синхронизации сигналов группы информационных выходов АЛУ 4 и второй группы информационных выходов входного коммутатора 3. Элемент 10 задержки предназначен для синхронизации сигналов, поступающих с информационного выхода второго переключателя 9, с другими выходными сигналами. Выходной коммутатор 6 обеспечивает соединение блоков процессора с информационными выходами процессора 16. Первый переключатель 7 служит для подачи данных и сигнала остановки сдвига в сдвиговый регистр 8, поступающих либо от АЛУ 4, либо от входного коммутатора 3. Сдвиговый регистр 8 в соответствии с содержимым регистра 13 настройки обеспечивает динамическое или статическое хранение входной последовательности данных и выдачу их на второй переключатель 9 и/или в АЛУ 4. Второй переключатель 9 служит для выдачи на выходной коммутатор 6 данных либо с выхода сдвигового регистра 8, либо с первого информационного выхода АЛУ 4, в зависимости от выполняемой команды. ОЗУ настройки 12 в соответствии с управляющими сигналами, поступающими на группу его управляющих входов, запоминает содержимое нескольких команд, которые загружаются по программным входам блока 2 настройки, и передает их в регистр 13 настройки, содержащий информацию о команде, выполняемой АЛУ 4, адреса входов процессора 16 для приема входных данных и адреса выходов процессора для выдачи результатов. Регистр 13 настройки по шинам ввода-вывода данных с первой по шестую настраивает величину задержки для каждого из блоков задержек 5, 11 и элемента задержки 10, устанавливает начальное состояние отдельных триггеров процессора, определяет адреса поступления данных для входного 3 и выходного 6 коммутаторов и рабочую длину сдвигового регистра 8. Третий переключатель 14 в соответствии с управляющими сигналами, поступающими на группу управляющих входов блока 2 настройки, обеспечивает выдачу на программный выход процессора 16 содержимого либо регистра 13 настройки, либо ОЗУ 12. Процессоры 16 объединяются в матрицу 17 и работают под управлением общего устройства управления матрицы процессоров 15.

Устройство работает следующим образом. Все блоки процессора синхронизированы тактовыми импульсами от общего генератора (на фиг. 1-4 не показан). Основные блоки процессора: АЛУ 4, блок 2 настройки, сдвиговый регистр 8. Кроме того, несколько блоков участвуют в передаче данных без обработки от информационных входов процессора к его информационным выходам (через входной коммутатор 3 к выходному коммутатору 6 через блок 11 задержек). Все основные блоки работают независимо друг от друга. То есть процессор может одновременно записывать команды в блок 2 настройки, обрабатывать в АЛУ 4 входные данные и выдавать результат, передавать без обработки данные с нескольких входов процессора на несколько выходов процессора, а также принимать информацию в сдвиговый регистр 8 и выдавать ее из него. Для задания конфигурации процессора используется регистр 13 настройки.

Каждый процессор 16 имеет группы информационных входов и выходов данных, которые могут быть связаны с соседними процессорами 16 или внешними устройствами (см. фиг. 3). Несколько блоков процессора могут использовать одни и те же входные данные. Если к одному из выходов процессора 16 подключены выходы нескольких блоков, то их значения суммируются в "логическое ИЛИ". Кроме возможности получения информации от соседних процессоров существует возможность подключать информационные входы коммутатора к сигналам "константа 0", "константа 1" (при этом на входе постоянно поддерживается соответствующий уровень сигнала) и сигналу "обратная связь". Входы "константа 0" и "константа 1" принадлежат группе информационных входов входного коммутатора 3. Сигнал "обратная связь" является локальным внутри процессора. Он служит для передачи информации от любого из входов выходного коммутатора 6 на информационный вход входного коммутатора 3 без использования других процессоров, что повышает эффективность использования процессора 16.

АЛУ 4 представляет собой вычислительное ядро процессора 16. Оно выполняет поразрядные вычисления над потоками данных. Кроме вычислительных функций АЛУ 4 управляет сдвиговым регистром 8, если он необходим для выполнения операции. АЛУ 4 производит операции над данными, поступающими на группу информационных входов. Результаты через группу информационных выходов постоянно поступают на выходы процессора через первый блок 5 задержек и выходной коммутатор 6, первый информационный выход АЛУ 4 используется только в некоторых операциях, использующих сдвиговый регистр 8. В этом случае переключатель 9 подает на выходной коммутатор 6 через элемент 10 задержки данные с первого информационного выхода АЛУ 4. При этом данные на информационный вход сдвигового регистра 8 через первый переключатель 7 подаются со второго информационного выхода АЛУ 4, которое выполняет операцию, определяемую регистром 13 настройки. Набор операций, выполняемых процессором, по составу аналогичен системе команд RISC-пpoцeccopa [3] и может меняться в зависимости от круга решаемых задач.

Сдвиговый регистр 8 процессора - это регистр программируемой длины, рабочая длина которого определяется блоком 2 настройки. Сдвиговый регистр 8 имеет последовательные информационные вход и выход, а также три управляющих входа, по которым поступают сигналы "хранение", "цикл", "направление", и может работать в трех режимах: "сдвиг" (фиг. 5.а.); "зацикливание" (фиг. 5. в.); "хранение" (фиг. 5.г.).

В режиме "сдвиг" в сдвиговый регистр 8 последовательно вводятся биты, поступающие на его информационный вход и через время, определяемое запрограммированной (рабочей) длиной сдвигового регистра 8, выдаются на его информационный выход. Бит, поступающий на вход сдвигового регистра 8 на n-ном тактовом импульсе, выдается на его выход на n+m-ном такте, где m - рабочая длина сдвигового регистра 8 в битах. При включении режима "зацикливание", по сигналу "цикл" вход сдвигового регистра 8 подключается к его выходу. Таким образом, входная информация игнорируется, а биты информации, находящиеся в сдвиговом регистре 8, появляются на его выходе с периодом m тактов. Данный режим может использоваться для динамического запоминания информации. При включенном режиме "хранение" информация с выхода сдвигового регистра 8 блокируется (приравнивается нулю), а сдвиг информации в сдвиговом регистре 8 не производится. Входная информация игнорируется. Управление режимами осуществляется с помощью сигналов "хранение", "цикл". Существует также возможность изменить направление сдвига с помощью сигнала "направление"(фиг. 5.б. ). При изменении направления сдвига разряд, поступивший последним на вход сдвигового регистра 8, первым появится на его выходе на следующем такте. Сигналы "направление" и "цикл" подаются со входного коммутатора 3 на первую группу управляющих входов сдвигового регистра 8. Сигнал "хранение" подается с управляющего выхода входного коммутатора 3 или с третьего управляющего выхода АЛУ 4 (что зависит от выполняемой операции) соответственно на первый и второй управляющие входы первого переключателя 7, который управляется сигналом, поступающим со второго управляющего выхода АЛУ 4.

Передача данных без обработки (транзит) осуществляется по нескольким линиям, работающим независимо друг от друга - от входного коммутатора 3 к выходному коммутатору 6 через блок 11 задержек. Адреса информационных входов и выходов для каждой из них определяются содержимым регистра 13 настройки. Данные, поступающие на вход линии транзита на n-ном такте, появляются на выходе на n+k-ом такте, где k - величина задержки в тактах и определяется регистром 13 настройки.

Блоки 5, 11 задержек представляют собой наборы сдвиговых регистров переменной разрядности, каждый из которых является элементом 10 задержки. Необходимость подключения дополнительной задержки и ее величина определяется командой, содержащейся в регистре 13 настройки.

Процессор 16 имеет несколько режимов функционирования. Они предназначены для подготовки и выполнения команды. Большинство режимов могут быть совмещены по времени выполнения. Режимы работы процессора задаются словом режима, которое сопровождается сигналом "установка режима" и подается из устройства 15 управления матрицей процессоров через группу управляющих входов процессора на группу управляющих входов контроллера 1, который декодирует внешние управляющие сигналы и формирует сигналы управления блоками процессора в соответствии с таблицей перекодировки, содержимое которой определяется конкретной реализацией интерфейса устройства управления матрицей процессоров 15, и самих процессоров.

Режим "Загрузка/Выгрузка" предназначен для загрузки команд в ОЗУ 12 и выгрузки команд из ОЗУ 12 или регистра 13 настройки блока 2 настройки. Одновременно с загрузкой команды, поступающей на программные входы процессора, команда, которая ранее содержалась в ОЗУ 12 и/или регистре 13 настройки, через переключатель 14 поступает на программный выход процессора. Управляющие входы блоков настройки 2 всех процессоров объединяются общей управляющей шиной. Программные входы и выходы процессоров матрицы 17 могут быть соединены по-разному, но во всех случаях они подключаются к устройству управления матрицей процессоров 15 через шину ввода-вывода программы. На фиг. 3 и фиг. 4 приведены два варианта - с параллельным и последовательным соединением программных входов-выходов.

При последовательном соединении матрица процессоров 17 организована в виде строк. Все процессоры 16 объединяются таким образом, что программный выход первого процессора 16 строки подается на программный вход второго процессора 16 строки. Программный выход последнего процессора 16 первой строки подается на программный вход первого процессора 16 второй строки и так далее, до последнего процессора 16 последней строки. Таким образом организуется как бы единая память с последовательным заполнением. При этом сначала подается команда, записываемая в блок настройки 2 последнего процессора 16 последней строки, которая последовательно проходит через блоки 2 настроек всех процессоров. За ней без задержки сразу же идет команда предпоследнего процессора 16 последней строки и так далее. Когда будет введена команда для первого процессора 16 первой строки, блоки настройки 2 всех процессоров 16 будут содержать предназначавшуюся им команду. При этом команды, которые ранее содержались в процессорах, будут последовательно выданы на программный выход последнего процессора 16 последней строки матрицы 17 процессоров. Так как они содержат информацию о текущем состоянии внутренних триггеров процессора (если выгружались непосредственно из регистров 13 настройки), то эта информация может использоваться при отладке программ.

При параллельном соединении все процессоры 16 объединяются общей программной шиной, по которой подаются адрес процессора 16 и команда для него, на шину же выгружается старая команда. В этом случае возможна выборочная загрузка-выгрузка блоков 2 настройки отдельных процессоров 16. Возможны комбинации двух вышеописанных типов соединения, когда процессоры разбиваются на группы, внутри которых программные входы-выходы соединяются последовательно, а группы соединяются параллельно. Это можно использовать, когда матрица процессоров 17 реализована в виде нескольких интегральных схем (групп). Каждая группа имеет свой адрес, и при записи информации в блоки настройки 2 одной группы адрес не меняется.

В режиме "Активизация команды" процессор 16 производит загрузку команды из ОЗУ 12 в регистр 13 настройки. После этого процессор 16 готов к выполнению команды и автоматически переходит в состояние "Нет операции", в котором он ничего не делает. Если в это время на вход поступает какая-нибудь информация, то она теряется. Адрес ОЗУ 12, по которому содержится команда, поступает на программные входы блока 2 настройки одновременно с тем, как слово режима поступает на управляющие входы процессора.

В режиме "Активизация команды с обменом" процессор 16 производит загрузку новой команды из ОЗУ 12 в регистр 13 настройки аналогично режиму "Активизация команды". Одновременно старая команда из регистра 13 настройки записывается в ОЗУ 12 по тому же адресу, по которому хранилась новая команда. Этот режим используется при прерывании программы, выполняемой матрицей 17 процессоров, и заменой ее другой, которая предварительно была записана во все процессоры матрицы 17.

Основным режимом работы является "Выполнение команды". В этом режиме процессор 16 обрабатывает в АЛУ 4 данные, поступающие на информационные входы процессора, и выдает результаты на его информационные выходы, кроме того, он может одновременно записывать команды в ОЗУ 12, передавать без обработки данные с нескольких входов процессора на несколько выходов процессора, а также принимать информацию в сдвиговый регистр 8 и выдавать ее из него. Пока слово режима не изменяется, процессор обрабатывает поток данных, поступающих на его информационные входы, выполняя над ними одни и те же действия. Типовая последовательность смены режимов выглядит так:

"Загрузка/Выгрузка" - "Активизация команды" - "Выполнение команды"-"Загрузка/Выгрузка"...

Предлагаемое техническое решение позволяет наиболее быстро и эффективно выполнять сложные программы. На его основе могут быть созданы высокопроизводительные вычислительные системы для обработки больших потоков информации.

Источники информации

1. А.И. Водяхо и др. Высокопроизводительные системы обработки данных. М. : Высшая школа, c. 152-163, 1997.

2. RU, патент 2134448 C1, кл. 6 G 06 F 15/16, 7/00, 1999.

3. Корнеев В.В. Современные микропроцессоры. М., Нолидж, 1999.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2001 |

|

RU2202123C2 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| ПАРАЛЛЕЛЬНЫЙ ПРОЦЕССОР С ПЕРЕПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1994 |

|

RU2110088C1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Микропрограммный процессор | 1986 |

|

SU1462339A1 |

| Микропроцессор для вводавывода данных | 1976 |

|

SU618733A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных системах обработки больших массивов информации, в том числе и в режиме реального времени. Техническим результатом является расширение функциональных возможностей. Устройство содержит входной коммутатор, арифметико-логическое устройство, сдвигающий регистр, элемент задержки, первый и второй переключатели, выходной коммутатор, первый и второй блоки задержек, контроллер, блок настройки, управляющие шины. 1 з.п. ф-лы, 5 ил.

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| Процессорный модуль однородной вычислительной структуры | 1985 |

|

SU1345207A1 |

| SU 3559782 A1, 15.12.1987 | |||

| Модуль однородной вычислительной структуры | 1984 |

|

SU1359782A1 |

| US 4562538 A, 31.12.1985. | |||

Авторы

Даты

2002-03-27—Публикация

2000-10-18—Подача