Изобретение относится к радиотехнике и может быть использовано для задержки электрических сигналов в радиотехнических устройствах.

Цель изобретения - повышение точности сохранения амплитуды задерживаемых сигналов за счет уменьшения амплитуды собственных помех и искажений.

Цель достигается тем, что в устройстве задержки, содержащем первый и второй преобразователи уровня, входы которых являются соответственно первым и вторым входами устройства задержки, линию задержки, фильтр нижних частот, генератор тактовых импульсов и блок управления временем задержки, первый и второй входы которого соединены соответственно с вторым выходом генератора тактовых импульсов и выходом второго преобразователя уровня, третий и четвертый входы являются соответственно третьим и четвертым входами устройства задержки, а выход соединен с входом генератора тактовых импульсов, линия задержки состоит из делителя частоты на два, первого коммутатора, первого и

второго аналоговых сдвиговых регистров, первого и второго ключей и сумматора, причем вход делителя частоты на два соединен с вторым выходом генератора тактовых импульсов, а первый и второй выходы соединены соответственно с первым и вторым управляющими входами первого коммутатора, информационный вход которого соединен с выходом первого преобразователя уровня, первый выход первого коммутатора соединен с первым входом первого аналогового сдвигового регистра, а второй выход- с первым входом второгоаналс говогосдвигтж ретстра, выход первого ключа соединен с первым входом сумматора, второй вход которого соединен с выходом второго ключа, а выход сумматора через фильтр нижних частот соединен с выходом устройства задержки, управляющие входы первого ивторого ключей соединены соот- - ветственно с первым и вторым выходами делителя частоты на два, вторые входы первого и второго аналоговых сдвиговых регистров соединены с первым выходом генератора тактовых импульсов, линия задержки выполнена трехканальной, в которую введены второй коммутатор, третий

ел

С

00

о о о о

аналоговый сдвиговый регистр, первый и второй дифференциальные усилители и конденсатор, причем первый вход третьего аналогового сдвигового регистра соединен через конденсатор с шиной нулевого потенциала, второй вход - с первым выходом генератора тактовых импульсов, а выход - с информационным входом второго коммутатора, первый и второй управляющие входы которого соединены соответственно с первым и вторым выходами делителя частоты на два, а первый и второй выходы - с инверсными входами первого и второго дифференциальных усилителей, прямые входы которых соединены соответственно первого и второго аналоговых сдвиговых регистров а выходы - с входами соответственно первого и второго ключей.

Новыми признаками, обладающими существенными отличиями, являются: схема трехканальной линии задержки и новые связи между новыми и известными признаками, т.е. новая схема устройства задержки. Данные признаки обладают существенными отличиями, так как в известных технических решениях не обнаружены.

Введение новых признаков позволяет повысить точность сохранения амплитуды задерживаемых сигналов за счет уменьшения амплитуды собственных помех путем образования трех каналов, объединения попарно первого и третьего каналов, второго и третьего каналов соответственно на первом и втором дифференциальных усилителях с высоким коэффициентом подавления синфазных сигналов. При этом АЧХ линии задержки становится прямоугольной, устраняются искажения четных гармоник, а помехи от импульсов тактового питания подавляются более чем на 40 дБ.

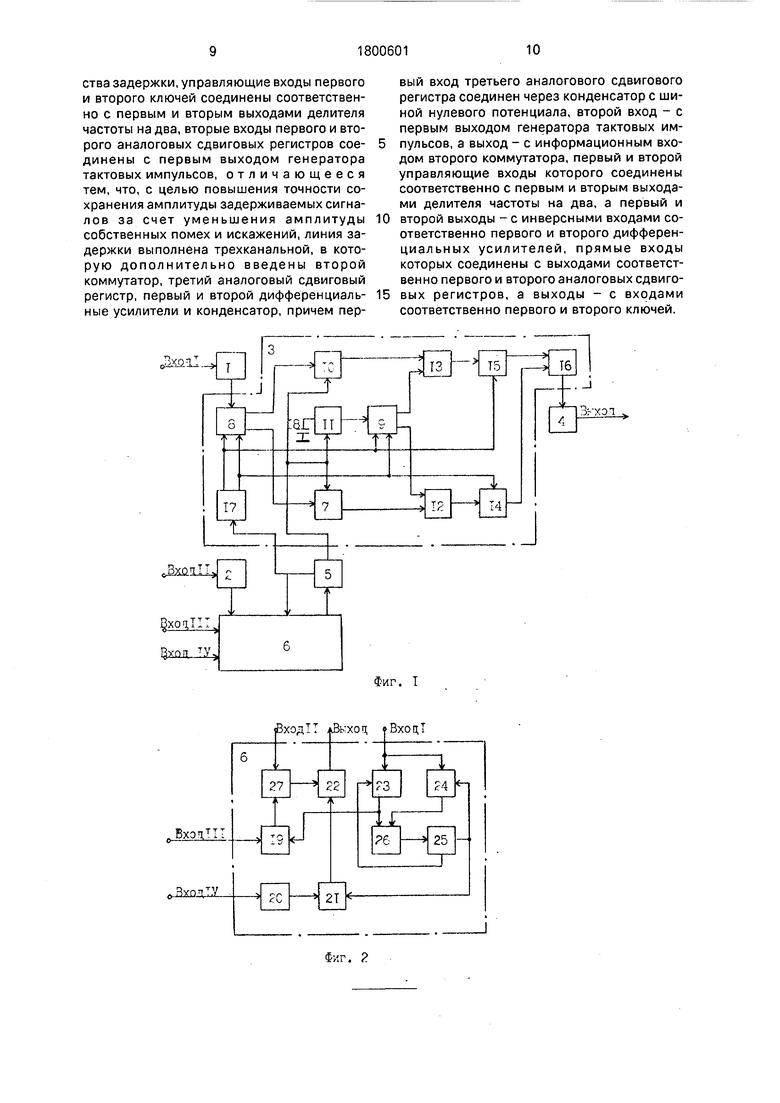

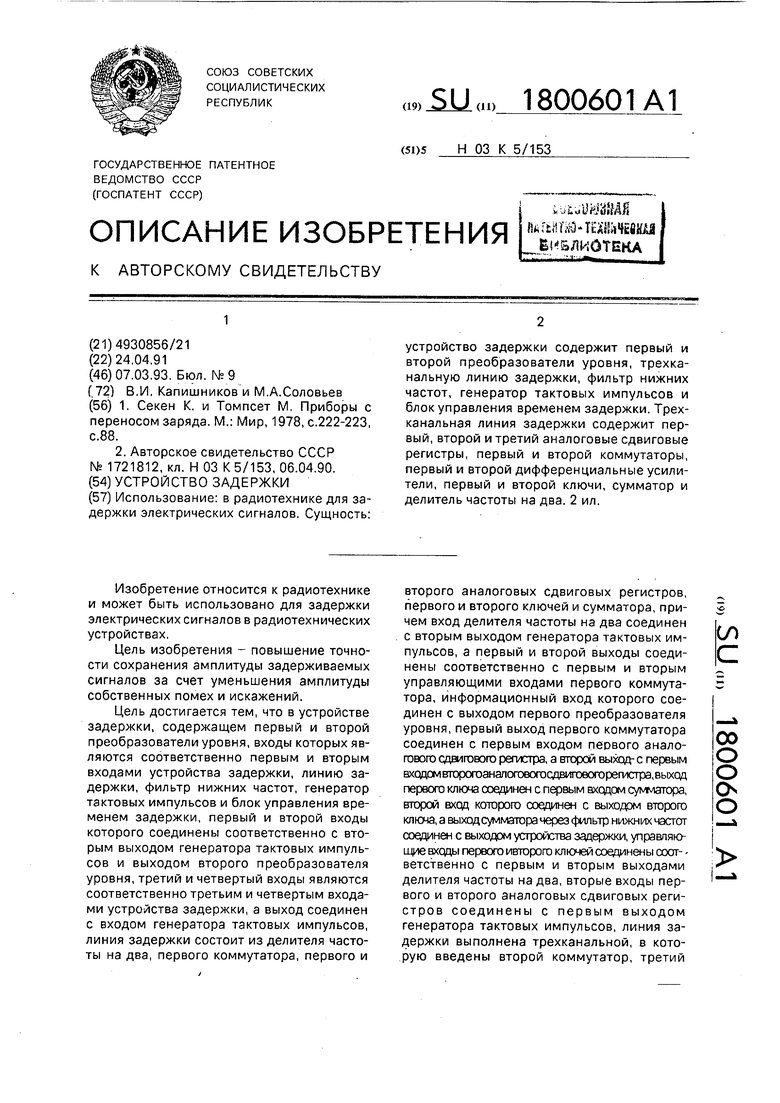

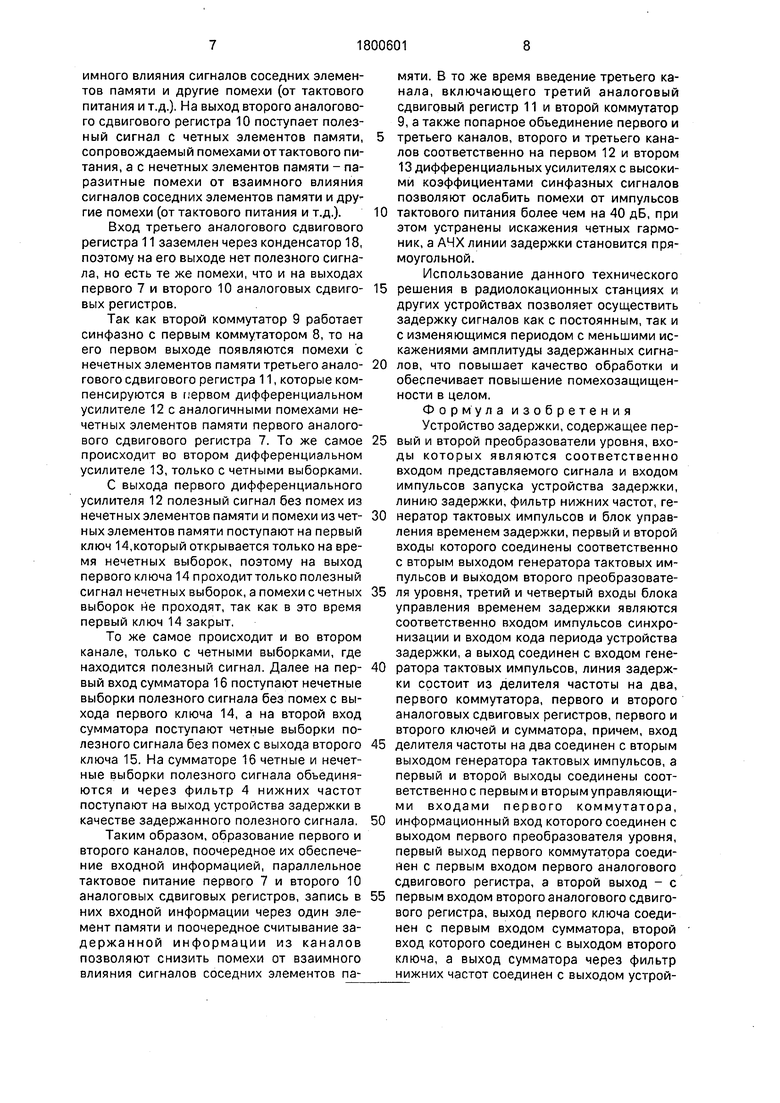

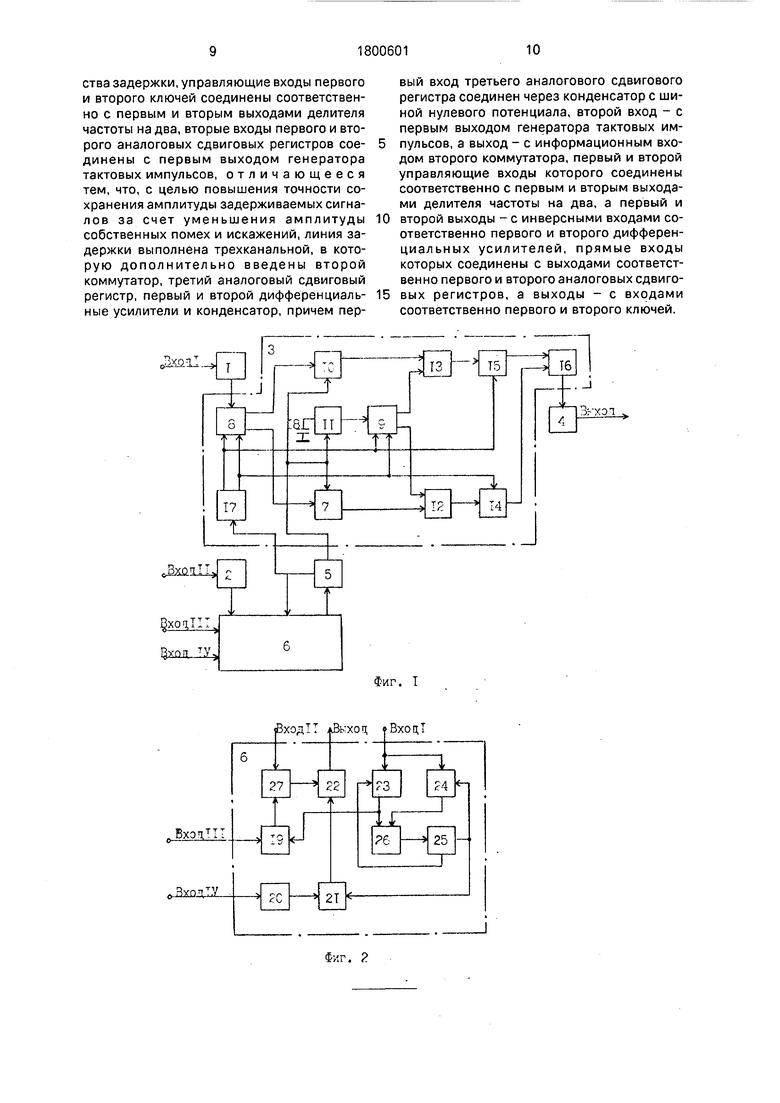

На фиг.1 представлена блок-схема устройства задержки; на фиг.2 - функциональная схема блока управления.

Устройство задержки содержит первый 1 и второй 2 преобразователи уровня, трех- канальнуюлиниюЗ задержки, фильтр4 нижних частот, генератор 5 тактовых импульсов и блок 6 управления временем задержки. Трехканальная линия 3 задержки содержит первый 8 и второй 9 коммутаторы, первый 7, второй 10 и третий 11 аналоговые сдвиговые регистры, первый 12 и второй 13 дифференциальные усилители, первый 14 и второй 15 ключи, сумматор 16, делитель 17 частоты на два и конденсатор 18. Блок 6 управления временем задержки содержит первый триггер 19, дешифратор 20, задающий генератор 21, первый элемент ИЛИ 22, первый 23 и второй 24 счетчики, второй триггер 25, второй элемент ИЛИ 26 и элемент И 27.

Устройство задержки работает следующим образом.

Входной сигнал через первый преобразователь 1 уровня поступает в трехканальную линию 3 задержки, на вторые входы первого 7, второго 10 и третьего 11 аналоговых сдвиговых регистров которой подаются импульсные последовательности с частотой fr от генератора 5 тактовых импульсов, определяющие время задержки входного сигнала в трехканальной линии 3 задержки. Задержанный сигнал с выхода трехканальной линии задержки поступает на вход фильтра 4 нижних частот, с помощью которого подавляются остатки помех от тактового питания, следующих на частотах гт и выше, потому что частота среза фильтра 4 нижних частот выбрана равной fT/2.

Задержанный полезный сигнал с выхода фильтра 4 нижних частот поступает на вход устройства задержки.

Принцип формирования необходимой задержки Т3 в трехканальной линии 3 задержки вытекает из закона изменения периода

входных сигналов.

Для сигналов с постоянным периодом следования Тс время задержки Т3 определяется выражением

30

, (1)

где N - число элементов, в каждом регистре сдвига трехканальной линии 3 задержки; fT - частота следования тактовых импульсов с

генератора 5 тактовых импульсов. На второй вход блока 6 управления временем задержки через второй вход устройства задержки и второй преобразователь 2 уровня подаются импульсы запуска, следующие

с частотой FH 1 /Тс, а на третий вход через третий вход устройства задержки поступают импульсные последовательности с частотой fT, обеспечивающие жесткую синхронизацию через блок 6 управления

временем задержки генератора 5 тактовых импульсов по каждому элементу памяти регистров сдвига.

Для формирования временем задержки Т3| сигналов, следующих с изменяющимся

периодом Т| по закону

Т, Т0 +АТ

(2)

где Т0 - постоянная часть периода Т|, опре- деляемая, например, однозначным определением дальности, и равна То Ni/fT, кроме подачи импульсов запуска и синхронизации на второй и третий входы устройства задержки на его четвертый вход подается код,

соответствующий периоду П. На основании этого кода с помощью блока 6 управления формируется параметр на основании выражения

AT3i N2/fi

(3)

где № N - NI; fj - изменяющаяся частота в соответствии с изменением кода периода.

Таким образом, общее время задержки T3i в трехканальной линии 3 задержки

T3i Ni/fT+N2/fi To + AT Ti. (4)

.Выражение (4) подтверждает возможность межпериодной обработки сигналов с изменяющимся периодом от импульса к импульсу.

Техническая реализация выражения (4) осуществляется с помощью сигналов, подаваемых на второй, третий и четвертый входы устройства задержки и блока 6 управления временем задержки следующим образом.

До поступления вышеуказанных сигналов элементы блока 6 управления временем задержки находятся в исходном состоянии, а именно первый счетчик 23 открыт, второй счетчик 24 закрыт, задающий генератор 21 не работает, элемент И 27 закрыт, поэтому с выхода блока 6 управления временем задержки на вход генератора 5 тактовых импульсов подается нулевой потенциал, и он также не работает.

При поступлении сигналов кода периода, импульсных последовательностей с частотой fT и импульса запуска срабатывает первый триггер 19 и открывает элемент И 27, через который импульсные последовательности с частотой fr и через первый элемент ИЛИ 22 поступают на вход генератора 5 тактовых импульсов, обеспечив жесткую его синхронизацию.

С второго выхода генератора 5 тактовых импульсов начинают поступать импульсы через первый вход блока 6 управления на первые входы первого 23 и второго 24 счетчиков. Первый счетчик 23 открыт и начинает подсчитывать NI импульсов для формирования параметра Т0, С приходом последнего из NI импульсов первый счетчик23 переполняется и с его выхода запирается первый триггер 19, а через второй элемент ИЛИ 26 запускается второй триггер 25, с первого выхода которого подается сигнал обнуления на второй вход первого счетчика 23, а с второго выхода - разрешающий сигнал на вторые входы второго счетчика 24 и задающего генератора 21. При этом на первом входе задающего генератора есть команда

первого периода с дешифратора 20, поэтому задающий генератор 21 начинает работать на частоте fi, импульсные последовательности с которого через первый элемент ИЛИ 22 осуществляют синхронизацию генератора 5 тактовых импульсов на частоте fi. При этом элемент И 26 закрыт с первого триггера 19,

С второго выхода генератора 5 тактовых импульсов импульсные последовательности

поступают на первый 23 и второй 24 счетчики. Так как первый счетчик 23 закрыт, то второй счетчик 24 начинает подсчитывать число N2 импульсов для формирования параметра ДТ-|. При поступлении последнего

из N2 импульсов второй счетчик 24 переполняется и с его выхода запирающий сигнал через второй элемент ИЛИ 26 запирает второй триггер 25, с первого выхода которого подается сигнал разрешения на работу первого счетчика 23, а с второго выхода - сигнал запрета на вторые входы второго счетчика 24 и задающего генератора 21. При этом сформировано два параметра Т0 Ni/fT и ATi N2/fi, а общее время задержки в

трехканальной линии 3

T3i Ni/fi + N2/fi T0 + .

При поступлении второго импульса за- пуска и кода, соответствующего второму периоду Т2, время задержки в трехканальной линии 3 сформировано с помощью блока 6 управления, равное второму периоду

T32 Ni/fT+N2/f2 T0+ AT2 T2, и т.д. Таким образом с помощью блока 6 управления временем задержки обеспечивается получение любой задержки в любой очередности в соответствии с приходящим

кодом периода.

Рассмотрим более подробно процессы подавления помех в устройстве задержки. Для ослабления помех от взаимного влияния сигналов соседних элементов памяти

входная информация в первый и второй каналы записывается поочередно и через один элемент памяти сдвиговых регистров, т.е. в первый аналоговый сдвиговый регистр 7 первого канала записываются нечетные

выборки в нечетные элементы памяти, а во второй аналоговый сдвиговый регистр 10 второго канала записываются четные выборки в четные элементы памяти. На выход первого аналогового сдвигового регистра 7

поступает полезный сигнал с нечетных элементов памяти, который сопровождается помехами от импульсов тактового питания и другими помехами, а с четных элементов памяти - только паразитные помехи от взаимного влияния сигналов соседних элементов памяти и другие помехи (от тактового питания и т.д.). На выход второго аналогового сдвигового регистра 10 поступает полезный сигнал с четных элементов памяти, сопровождаемый помехами оттактового питания, а с нечетных элементов памяти - паразитные помехи от взаимного влияния сигналов соседних элементов памяти и дру гие помехи (от тактового питания и т.д.).

Вход третьего аналогового сдвигового регистра 11 заземлен через конденсатор 18, поэтому на его выходе нет полезного сигнала, но есть те же помехи, что и на выходах первого 7 и второго 10 аналоговых сдвиговых регистров.

Так как второй коммутатор 9 работает синфазно с первым коммутатором 8, то на его первом выходе появляются помехи с нечетных элементов памяти третьего аналогового сдвигового регистра 11, которые компенсируются в первом дифференциальном усилителе 12 с аналогичными помехами нечетных элементов памяти первого аналогового сдвигового регистра 7. То же самое происходит во втором дифференциальном усилителе 13, только с четными выборками.

С выхода первого дифференциального усилителя 12 полезный сигнал без помех из нечетных элементов памяти и помехи из четных элементов памяти поступают на первый ключ 14,который открывается только на время нечетных выборок, поэтому на выход первого ключа 14 проходит только полезный сигнал нечетных выборок, а помехи с четных выборок не проходят, так как в это время первый ключ 14 закрыт.

То же самое происходит и во втором канале, только с четными выборками, где находится полезный сигнал. Далее на первый вход сумматора 16 поступают нечетные выборки полезного сигнала без помех с выхода первого ключа 14, а на второй вход сумматора поступают четные выборки полезного сигнала без помех с выхода второго ключа 15. На сумматоре 16 четные и нечетные выборки полезного сигнала объединяются и через фильтр 4 нижних частот поступают на выход устройства задержки в качестве задержанного полезного сигнала.

Таким образом, образование первого и второго каналов, поочередное их обеспечение входной информацией, параллельное тактовое питание первого 7 и второго 10 аналоговых сдвиговых регистров, запись в них входной информации через один элемент памяти и поочередное считывание за- держанной информации из каналов позволяют снизить помехи от взаимного влияния сигналов соседних элементов памяти. В то же время введение третьего канала, включающего третий аналоговый сдвиговый регистр 11 и второй коммутатор 9, а также попарное объединение первого и

третьего каналов, второго и третьего каналов соответственно на первом 12 и втором 13 дифференциальных усилителях с высокими коэффициентами синфазных сигналов позволяют ослабить помехи от импульсов

0 тактового питания более чем на 40 дБ, при этом устранены искажения четных гармоник, а АЧХ линии задержки становится прямоугольной.

Использование данного технического

5 решения в радиолокационных станциях и других устройствах позволяет осуществить задержку сигналов как с постоянным, так и с изменяющимся периодом с меньшими искажениями амплитуды задержанных сигна0 лов, что повышает качество обработки и обеспечивает повышение помехозащищенности в целом,

Формула изобретения Устройство задержки, содержащее пер5 вый и второй преобразователи уровня, входы которых являются соответственно входом представляемого сигнала и входом импульсов запуска устройства задержки, линию задержки, фильтр нижних частот, ге0 нератор тактовых импульсов и блок управления временем задержки, первый и второй входы которого соединены соответственно с вторым выходом генератора тактовых импульсов и выходом второго преобразовате5 ля уровня, третий и четвертый входы блока управления временем задержки являются соответственно входом импульсов синхронизации и входом кода периода устройства задержки, а выход соединен с входом гене0 ратора тактовых импульсов, линия задержки состоит из делителя частоты на два, первого коммутатора, первого и второго аналоговых сдвиговых регистров, первого и второго ключей и сумматора, причем, вход

5 делителя частоты на два соединен с вторым выходом генератора тактовых импульсов, а первый и второй выходы соединены соответственно с первым и вторым управляющи- ми входами первого коммутатора,

0 информационный вход которого соединен с выходом первого преобразователя уровня, первый выход первого коммутатора соединен с первым входом первого аналогового сдвигового регистра, а второй выход - с

5 первым входом второго аналогового сдвигового регистра, выход первого ключа соединен с первым входом сумматора, второй вход которого соединен с выходом второго ключа, а выход сумматора через фильтр нижних частот соединен с выходом устройства задержки, управляющие входы первого и второго ключей соединены соответственно с первым и вторым выходами делителя частоты на два, вторые входы первого и второго аналоговых сдвиговых регистров соединены с первым выходом генератора тактовых импульсов, отличающееся тем, что, с целью повышения точности сохранения амплитуды задерживаемых сигна- лов за счет уменьшения амплитуды собственных помех и искажений, линия задержки выполнена трехканальной, в которую дополнительно введены второй коммутатор, третий аналоговый сдвиговый регистр, первый и второй дифференциальные усилители и конденсатор, причем пер0

5

вый вход третьего аналогового сдвигового регистра соединен через конденсатор с шиной нулевого потенциала, второй вход - с первым выходом генератора тактовых импульсов, а выход - с информационным входом второго коммутатора, первый и второй управляющие входы которого соединены соответственно с первым и вторым выходами делителя частоты на два, а первый и второй выходы - с инверсными входами соответственно первого и второго дифферен- циальных усилителей, прямые входы которых соединены с выходами соответственно первого и второго аналоговых сдвиговых регистров, а выходы - с входами соответственно первого и второго ключей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1990 |

|

SU1721812A1 |

| Устройство для считывания информации с металлической кодовой пластины | 1985 |

|

SU1278906A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1193655A1 |

| СИСТЕМА ЦИФРОВОГО ЦВЕТНОГО ТЕЛЕВИДЕНИЯ | 1993 |

|

RU2103839C1 |

| Устройство передачи телеметрической и видеоинформации с частотно-временным уплотнением радиоканала и аналого-цифровым методом частотной (фазовой) модуляции несущей частоты | 2017 |

|

RU2641460C1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Цифровой вольтметр | 1981 |

|

SU970675A1 |

| Медианный рекурсивный фильтр | 1988 |

|

SU1654837A1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВИЖУЩИХСЯ ЦЕЛЕЙ | 1981 |

|

SU1841007A1 |

Использование: в радиотехнике для задержки электрических сигналов. Сущность: устройство задержки содержит первый и второй преобразователи уровня, трехка- нальную линию задержки, фильтр нижних частот, генератор тактовых импульсов и блок управления временем задержки. Трех- канальная линия задержки содержит первый, второй и третий аналоговые сдвиговые регистры, первый и второй коммутаторы, первый и второй дифференциальные усилители, первый и второй ключи, сумматор и делитель частоты на два. 2 ил.

Фиг. I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Секен К | |||

| и Томпсет М | |||

| Приборы с переносом заряда | |||

| М.: Мир, 1978, с.222-223, с.88 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство задержки | 1990 |

|

SU1721812A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-03-07—Публикация

1991-04-24—Подача