j

VJ

N СЛ О О

Изобретение относится к вычислительной технике, электросвязи и может использоваться в цифровых системах передачи, хранения и воспроизведения звуковых сигналов.

Целью изобретения является повышение достоверности устройства.

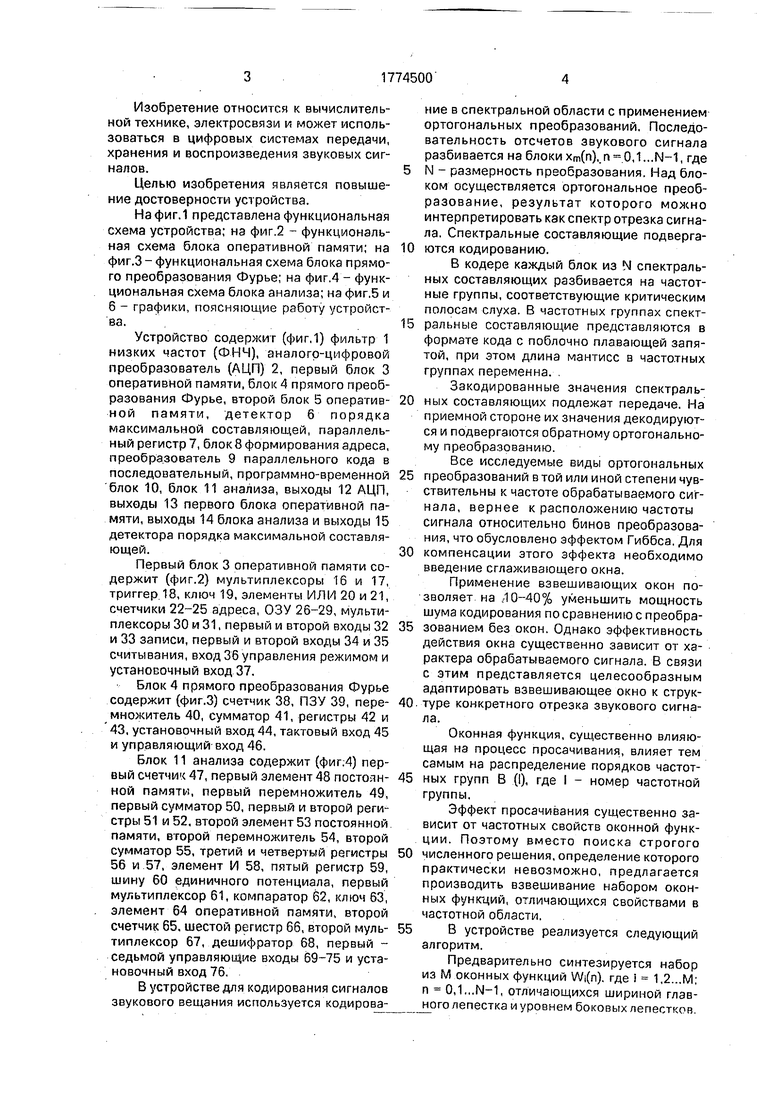

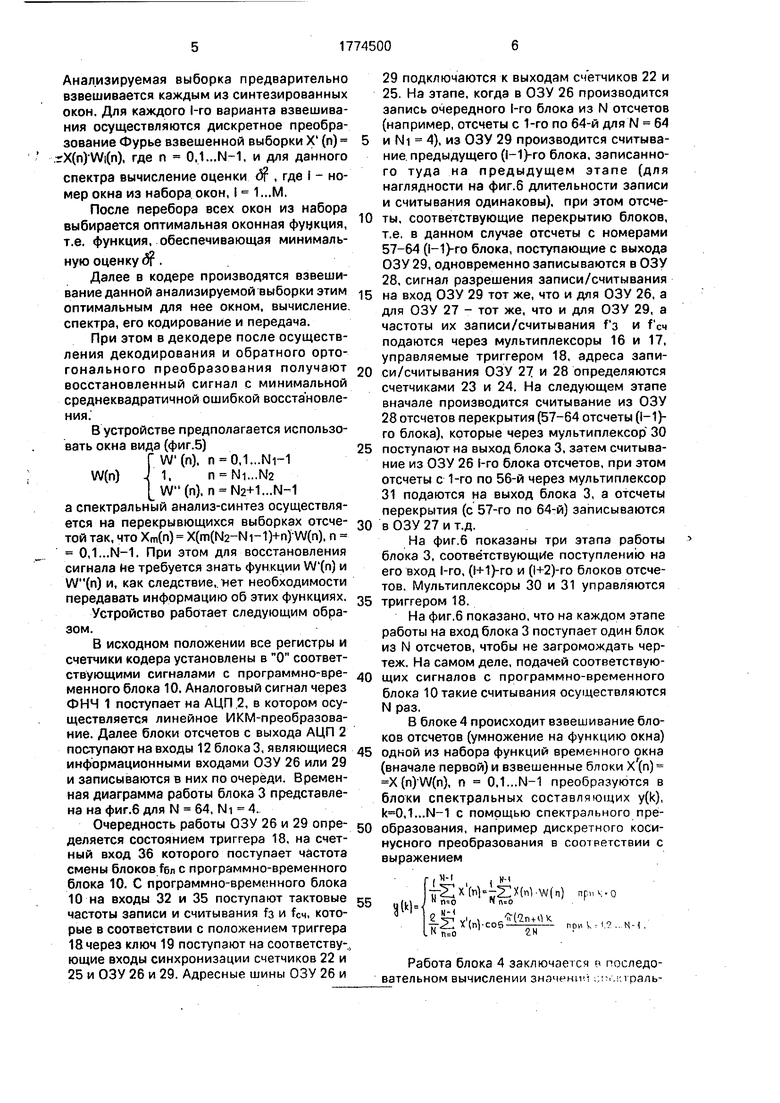

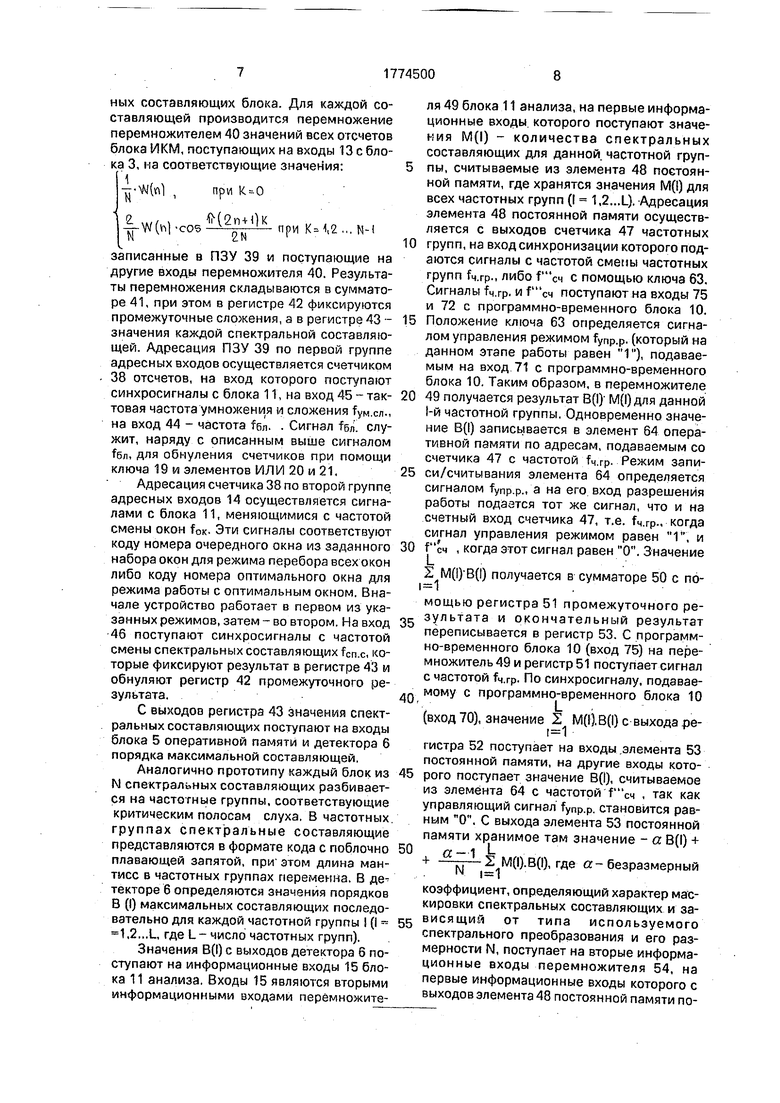

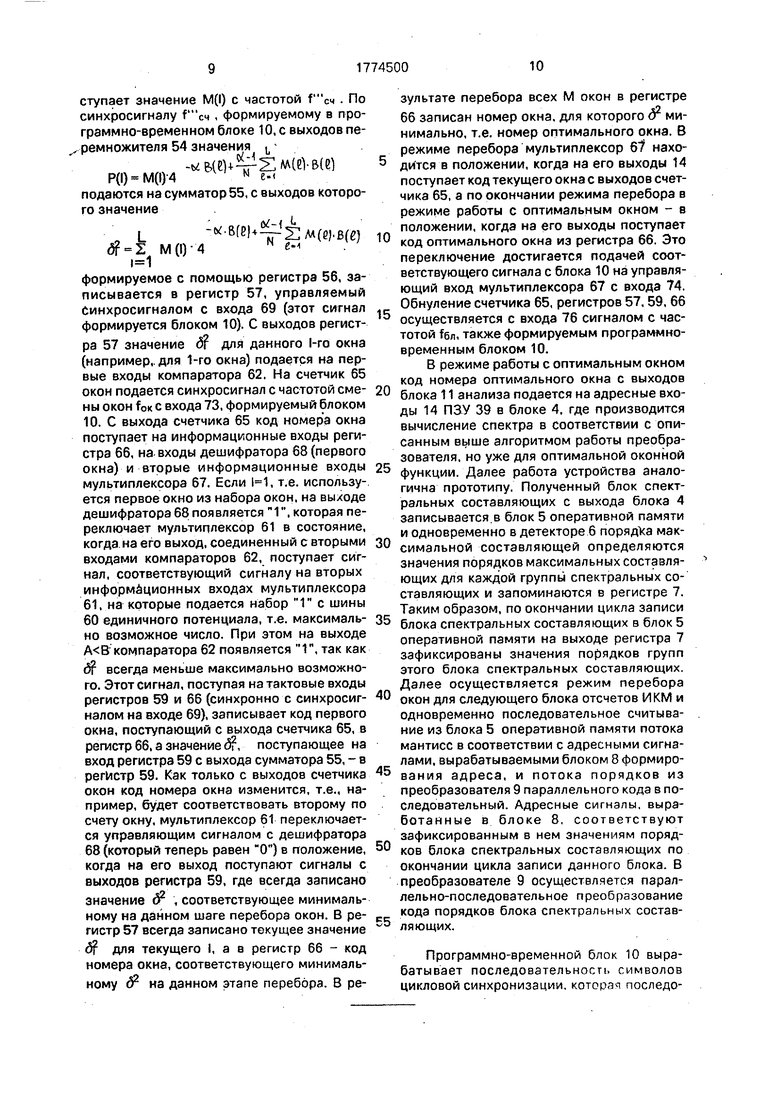

На фиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема блока оперативной памяти; на фиг.З - функциональная схема блока прямого преобразования Фурье; на фиг.4 - функциональная схема блока анализа; на фиг.5 и 6 - графики, поясняющие работу устройства.

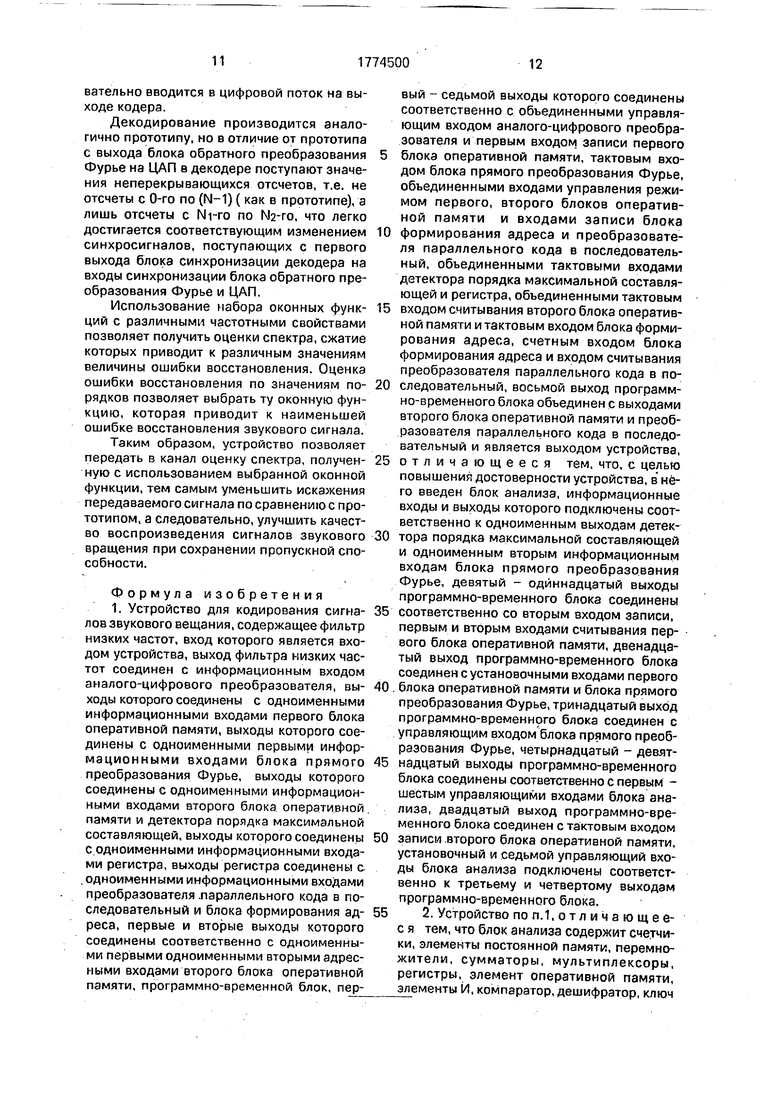

Устройство содержит (фиг.1) фильтр 1 низких частот (ФНЧ), аналого-цифровой преобразователь (АЦП) 2, первый блок 3 оперативной памяти, блок 4 прямого преобразования Фурье, второй блок 5 оперативной памяти, детектор 6 порядка максимальной составляющей, параллельный регистр 7, блок 8 формирования адреса, преобразователь 9 параллельного кода в последовательный, программно-временной блок 10, блок 11 анализа, выходы 12 АЦП, выходы 13 первого блока оперативной памяти, выходы 14 блока анализа и выходы 15 детектора порядка максимальной составляющей.

Первый блок 3 оперативной памяти содержит (фиг.2) мультиплексоры 16 и 17, триггер 18, ключ 19, элементы ИЛИ 20 и 21, счетчики 22-25 адреса, ОЗУ 26-29, мультиплексоры 30 и 31, первый и второй входы 32 и 33 записи, первый и второй входы 34 и 35 считывания, вход 36 управления режимом и установочный вход 37.

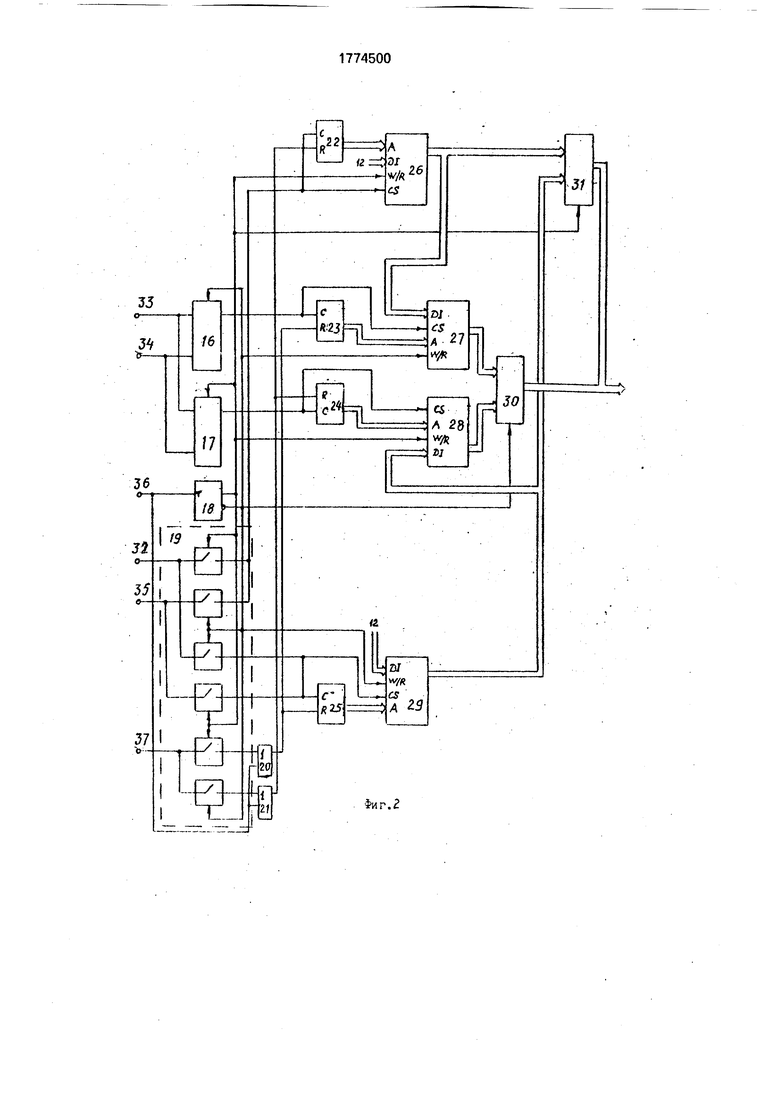

Блок 4 прямого преобразования Фурье содержит (фиг.З) счетчик 38, ПЗУ 39, перемножитель 40, сумматор 41, регистры 42 и 43, установочный вход 44, тактовый вход 45 и управляющий вход 46.

блок 11 анализа содержит (фиг.4) первый счетчик 47, первый элемент 48 постоянной памяти, первый перемножитель 49, первый сумматор 50, первый и второй регистры 51 и 52. второй элемент 53 постоянной памяти, второй перемножитель 54, второй сумматор 55, третий и четвертый регистры 56 и 57, элемент И 58, пятый регистр 59, шину 60 единичного потенциала, первый мультиплексор 61, компаратор 62, ключ 63, элемент 64 оперативной памяти, второй счетчик 65. шестой регистр 66, второй мультиплексор 67, дешифратор 68, первый - седьмой управляющие входы 69-75 и установочный вход 76,

В устройстве для кодирования сигналов звукового вещания используется кодирование в спектральной области с применением ортогональных преобразований. Последовательность отсчетов звукового сигнала разбивается на блокихт(п),.п 0,1...1М-1, где N - размерность преобразования. Над блоком осуществляется ортогональное преобразование, результат которого можно интерпретировать как спектр отрезка сигнала. Спектральные составляющие подверга- 0 ются кодированию.

В кодере каждый блок из N спектральных составляющих разбивается на частотные группы, соответствующие критическим полосам слуха. В частотных группах спект- 5 ральные составляющие представляются в формате кода с поблочно плавающей запятой, при этом длина мантисс в частотных группах переменна.

Закодированные значения спектраль- 0 ных составляющих подлежат передаче. На приемной стороне их значения декодируются и подвергаются обратному ортогональному преобразованию.

Все исследуемые виды ортогональных 5 преобразований в той или иной степени чувствительны к частоте обрабатываемого сигнала, вернее к расположению частоты сигнала относительно бинов преобразования, что обусловлено эффектом Гиббса. Для 0 компенсации этого эффекта необходимо введение сглаживающего окна.

Применение взвешивающих окон позволяет на Л0-40% уменьшить мощность шума кодирования по сравнению с преобра- 5 зованием без окон. Однако эффективность действия окна существенно зависит от характера обрабатываемого сигнала. В связи с этим представляется целесообразным адаптировать взвешивающее окно к струк- 0 туре конкретного отрезка звукового сигнала.

Оконная функция, существенно влияющая на процесс просачивания, влияет тем самым на распределение порядков частот- 5 ных групп В (I), где I - номер частотной группы.

Эффект просачивания существенно зависит от частотных свойств оконной функции. Поэтому вместо поиска строгого 0 численного решения, определение которого практически невозможно, предлагается производить взвешивание набором оконных функций, отличающихся свойствами в частотной области.

5 В устройстве реализуется следующий алгоритм.

Предварительно синтезируется набор из М оконных функций Wi(n). где i 1.2...M; п 0,1...N-1, отличающихся шириной главного лепестка и уровнем боковых лепестков

Анализируемая выборка предварительно взвешивается каждым из синтезированных окон. Для каждого 1-го варианта взвешивания осуществляются дискретное преобразование Фурье взвешенной выборки X (п) rX(n) Wi(n), где n 0.1...N-1, и для данного

спектра вычисление оценки (5 , где f - номер окна из набора окон, I 1...M.

После перебора всех окон из набора выбирается оптимальная оконная функция, т.е. функция, обеспечивающая минимальную оценку б .

Далее в кодере производятся взвешивание данной анализируемой выборки этим оптимальным для нее окном, вычисление, спектра, его кодирование и передача.

При этом в декодере после осуществления декодирования и обратного ортогонального преобразования получают восстановленный сигнал с минимальной среднеквадратичной ошибкой восстановления.

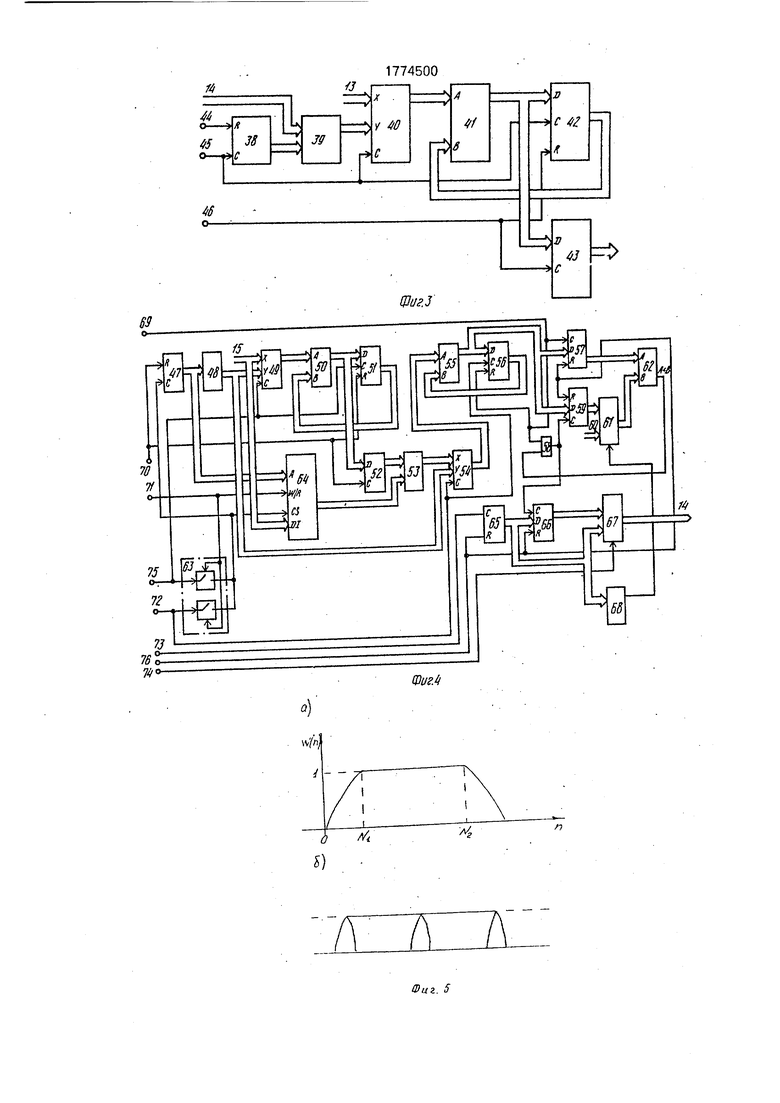

В устройстве предполагается использовать окна вида (фиг.5)

Г W (n}, n 0,1...N1-1

W(n) J 1. n Ni...N2

W(n). n N2+1...N-1 а спектральный анализ-синтез осуществляется на перекрывющихся выборках отсче- той так, что Xm(n) X(m(N2-Ni-1)+n)-W(n). n 0.1...N-1. При этом для восстановления сигнала Не требуется знать функции W (n) и W(n) и, как следствие, нет необходимости передавать информацию об этих функциях.

Устройство работает следующим образом.

В исходном положении все регистры и счетчики кодера установлены в О соответствующими сигналами с программно-временного блока 10. Аналоговый сигнал через ФНЧ 1 поступает на АЦП 2, в котором осуществляется линейное ИКМ-преобразова- ние. Далее блоки отсчетов с выхода АЦП 2 поступают на входы 12 блока 3, являющиеся информационными входами ОЗУ 26 или 29 и записываются в них по очереди. Временная диаграмма работы блока 3 представлена на фиг.б для N 64, NI 4.

Очередность работы ОЗУ 26 и 29 определяется состоянием триггера 18, на счетный вход 36 которого поступает частота смены блоков fбл с программно-временного блока 10. С программно-временного блока 10 на входы 32 и 35 поступают тактовые частоты записи и считывания fa и fC4, которые в соответствии с положением триггера 18 через ключ 19 поступают на соответствую ющие входы синхронизации счетчиков 22 и 25 и ОЗУ 26 и 29. Адресные шины ОЗУ 26 и

29 подключаются к выходам счетчиков 22 и 25. На этапе, когда в ОЗУ 26 производится запись очередного 1-го блока из N отсчетов (например, отсчеты с 1-го по 64-й для N 64 5 и NI 4), из ОЗУ 29 производится считывание предыдущего (i-1)-ro блока, записанного туда на предыдущем этапе (для наглядности на фиг.б длительности записи и считывания одинаковы), при этом отсче0 ты, соответствующие перекрытию блоков, т.е. в данном случае отсчеты с номерами 57-64 (Ы)-го блока, поступающие с выхода ОЗУ 29, одновременно записываются в ОЗУ 28, сигнал разрешения записи/считывания

5 на вход ОЗУ 29 тот же, что и для ОЗУ 26, а для ОЗУ 27 - тот же, что и для ОЗУ 29, а частоты их записи/считывания т з и т сч подаются через мультиплексоры 16 и 17, управляемые триггером 18, адреса запи0 си/считывания ОЗУ 27 и 28 определяются счетчиками 23 и 24. На следующем этапе вначале производится считывание из ОЗУ 28 отсчетов перекрытия (57-64 отсчеты (М)- го блока), которые через мультиплексор 30

5 поступают на выход блока 3, затем считывание из ОЗУ 26 1-го блока отсчетов, при этом отсчеты с 1-го по 56-й через мультиплексор 31 подаются на выход блока 3, а отсчеты перекрытия (с 57-го по 64-й) записываются

0 в ОЗУ 27 и т.д.

На фиг.б показаны три этапа работы блока 3, соответствующие поступлению на его вход 1-го, (i+1)-ro и 0+2)-го блоков отсчетов. Мультиплексоры 30 и 31 управляются

5 триггером 18.

На фиг,6 показано, что на каждом этапе работы на вход блока 3 поступает один блок из N отсчетов, чтобы не загромождать чертеж. На самом деле, подачей соответствую0 щих сигналов с программно-временного блока 10 такие считывания осуществляются N раз.

В блоке 4 происходит взвешивание блоков отсчетов (умножение на функцию окна)

5 одной из набора функций временного окна (вначале первой) и взвешенные блоки Хг(п) Х (n) W(n), n 0.1...N-1 преобразуются в блоки спектральных составляющих y(k), ,1...N-1 с помощью спектрального пре0 образования, например дискретного косинусного преобразования в соответствии с выражением

W I ц , ( нjrS(til--Z XM w(n) np,,v.0

N

i.

пои V. f N-(

Работа блока 4 заключается n последовательном вычислении знэчешп i -тральных составляющих блока. Для каждой составляющей производится перемножение перемножителем 40 значений всех отсчетов блока ИКМ, поступающих на входы 13с блока 3, на соответствующие значения:

при ,2...N-1

записанные в ПЗУ 39 и поступающие на другие входы перемножителя 40. Результаты перемножения складываются в сумматоре 41, при этом в регистре 42 фиксируются промежуточные сложения, а в регистре 43 - значения каждой спектральной составляющей. Адресация ПЗУ 39 по первой группе адресных входов осуществляется счетчиком 38 отсчетов, на вход которого поступают синхросигналы с блока 11, на вход 45 - тактовая частота умножения и сложения fym.cn., на вход 44 - частота fen. . Сигнал 1бл. служит, наряду с описанным выше сигналом fan, для обнуления счетчиков при помощи ключа 19 и элементов ИЛИ 20 и 21,

Адресация счетчика 38 по второй группе адресных входов 14 осуществляется сигналами с блока 11, меняющимися с частотой смены окон foK- Эти сигналы соответствуют коду номера очередного окна из заданного набора окон для режима перебора всех окон либо коду номера оптимального окна для режима работы с оптимальным окном. Вначале устройство работает в первом из указанных режимов, затем - во втором. На вход 46 поступают синхросигналы с частотой смены спектральных составляющих fcn.c, которые фиксируют результат в регистре 43 и обнуляют регистр 42 промежуточного результата.

С выходов регистра 43 значения спектральных составляюи1их поступают на входы блока 5 оперативной памяти и детектора 6 порядка максимальной составляющей.

Аналогично прототипу каждый блок из N спектральных составляющих разбивается на частотные группы, соответствующие критическим полосам слуха. В частотных группах спектральные составляющие представляются в формате кода с поблочно плавающей запятой, при этом длина мантисс в частотных группах переменна. В детекторе 6 определяются значения порядков В (I) максимальных составляющих последовательно для каждой частотной группы I (I - 1,2...L, где L- число частотных групп).

Значения B(l) с выходов детектора 6 поступают на информационные входы 15 блока 11 анализа. Входы 15 являются вторыми информационными входами перемножителя 49 блока 11 анализа, на первые информационные входы которого поступают значения M(l) - количества спектральных составляющих для данной частотной группы, считываемые из элемента 48 постоянной памяти, где хранятся значения M(l) для всех частотных групп (I 1,2..,}. Адресация элемента 48 постоянной памяти осуществляется с выходов счетчика 47 частотных

0 групп, на вход синхронизации которого подаются сигналы с частотой смены частотных групп f4.rp., либо с помощью ключа 63. Сигналы f4,rp. и поступают на входы 75 и 72 с программно-временного блока 10.

5 Положение ключа 63 определяется сигналом управления режимом fynp.p. (который на данном этапе работы равен 1), подаваемым на вход 71 с программно-временного блока 10. Таким образом, в перемножителе

0 49 получается результат B(l) M(l) для данной 1-й частотной группы. Одновременно значение В(1) записывается в элемент 64 оперативной памяти по адресам, подаваемым со счетчика 47 с частотой f4.rp. Режим запи5 си/считывания элемента 64 определяется сигналом fynp.p., а на его вход разрешения работы подазтся тот же сигнал, что и на счетный вход счетчика 47, т.е. тч.гр., когда сигнал управления режимом равен 1, и

0 Г сч , когда этот сигнал равен О. Значение

2 M(I) B(I) получается в сумматоре 50 с по-

мощью регистра 51 промежуточного ре- с зультата и окончательный результат переписывается в регистр 53. С программно-временного блока 10 (вход 75) на перемножитель 49 и регистр 51 поступаетсигнал с частотой f4.rp. По синхросигналу, подавае- Q мому с программно-временного блока 10

(вход 70), значение 2 M(I).B(I) с выхода

гистра 52 поступает на входы элемента 53 постоянной памяти, на другие входы кото5 рого поступает значение B(l), считываемое из элемента 64 с частотой f сч , так как управляющий сигнал fynp.p. становится равным О. С выхода элемента 53 постоянной памяти хранимое там значение - а В(П +

0 L

+ -г:-2 M(I).B(I), где «-безразмерный

Гч { 1

коэффициент, определяющий характер маскировки спектральных составляющих и за- 5 висящий от типа используемого спектрального преобразования и его размерности N, поступает на вторые информационные входы перемножителя 54, на первые информационные входы которого с выходов элемента 48 постоянной памяти поступает значение M(l) с частотой . По инхросигналу , формируемому в программно-временном блоке 10, с выходов пе- ремножителя 54 значения L (EHTrSto(eVe(e)

P(I) M(I)4 V N e- подаются на сумматор 55, с выходов которого значение

L-«№-Ј м(в).в(в)

б 2 М (I) 4N «ч

формируемое с помощью регистра 56, записывается в регистр 57, управляемый Синхросигналом с входа 69 (этот сигнал формируется блоком 10). С выходов регистра 57 значение б для данного 1-го окна (например, для 1-го окна) подается на первые входы компаратора 62. На счетчик 65 окон подается синхросигнал с частотой смены окон Ток с входа 73, формируемый блоком 10. С выхода счетчика 65 код номера окна поступает на информационные входы регистра 66, на входы дешифратора 68 (первого окна) и вторые информационные входы мультиплексора 67. Если , т.е. используется первое окно из набора окон, на выходе ешифратора 68 появляется 1. которая переключает мультиплексор 61 в состояние, когда на его выход, соединенный с вторыми входами компараторов 62, поступает сигнал, соответствующий сигналу на вторых информационных входах мультиплексора 61, на которые подается набор 1 с шины 60 единичного потенциала, т.е. максимально возможное число. При этом на выходе В компаратора 62 появляется 1, так как

всегда меньше максимально возможного. Этот сигнал, поступая на тактовые входы регистров 59 и 66 (синхронно с синхросигналом на входе 69), записывает код первого окна, поступающий с выхода счетчика 65, в регистр 66, а значение (5, поступающее на вход регистра 59 с выхода сумматора 55, - в регистр 59. Как только с выходов счетчика кон код номера окна изменится, т.е., например, будет соответствовать второму по чету окну, мультиплексор 61 переключаетя управляющим сигналом с дешифратора 8 (который теперь равен О) в положение, когда на его выход поступают сигналы с выходов регистра 59, где всегда записано

значение б2 , соответствующее минимальному на данном шаге перебора окон. В регистр 57 всегда записано текущее значение

для текущего 1, а в регистр 66 - код омера окна, соответствующего минимальному б2 на данном этапе перебора. В ре10

5

0

5

0

5

0

5

0

5

зультате перебора всех М окон в регистре

66 записан номер окна, для которого б2 минимально, т.е. номер оптимального окна. В режиме перебора мультиплексор 6t находится в положении, когда на его выходы 14 поступает код текущего окна с выходов счетчика 65, а по окончании режима перебора в режиме работы с оптимальным окном - в положении, когда на его выходы поступает код оптимального окна из регистра 66. Это переключение достигается подачей соответствующего сигнала с блока 10 на управляющий вход мультиплексора 67 с входа 74. Обнуление счетчика 65, регистров 57, 59, 66 осуществляется с входа 76 сигналом с частотой Тбл, также формируемым программно- временным блоком 10.

В режиме работы с оптимальным окном код номера оптимального окна с выходов блока 11 анализа подается на адресные входы 14 ПЗУ 39 в блоке 4, где производится вычисление спектра в соответствии с описанным выше алгоритмом работы преобразователя, но уже для оптимальной оконной функции. Далее работа устройства аналогична прототипу. Полученный блок спектральных составляющих с выхода блока 4 записывается в блок 5 оперативной памяти и одновременно в детекторе 6 порядка максимальной составляющей определяются значения порядков максимальных составляющих для каждой группы спектральных составляющих и запоминаются в регистре 7. Таким образом, по окончании цикла записи блока спектральных составляющих в блок 5 оперативной памяти на выходе регистра 7 зафиксированы значения порядков групп этого блока спектральных составляющих. Далее осуществляется режим перебора окон для следующего блока отсчетов И КМ и одновременно последовательное считывание из блока 5 оперативной памяти потока мантисс в соответствии с адресными сигналами, вырабатываемыми блоком 8 формиро- вания адреса, и потока порядков из преобразователя 9 параллельного кода в последовательный. Адресные сигналы, выработанные в блоке 8, соответствуют зафиксированным в нем значениям порядков блока спектральных составляющих по окончании цикла записи данного блока. В преобразователе 9 осуществляется параллельно-последовательное преобразование кода порядков блока спектральных составляющих.

Программно-временной блок 10 вырабатывает последовательность символов цикловой синхронизации, которая последовательно вводится в цифровой поток на выходе кодера.

Декодирование производится аналогично прототипу, но в отличие от прототипа с выхода блока обратного преобразования Фурье на ЦАП в декодере поступают значения неперекрывающихся отсчетов, т.е. не отсчеты с 0-го по (N-1) ( как в прототипе), а лишь отсчеты с Ni-ro no N2-ro, что легко достигается соответствующим изменением синхросигналов, поступающих с первого выхода блока синхронизации декодера на входы синхронизации блока обратного преобразования Фурье и ЦАП.

Использование набора оконных функций с различными частотными свойствами позволяет получить оценки спектра, сжатие которых приводит к различным значениям величины ошибки восстановления. Оценка ошибки восстановления по значениям порядков позволяет выбрать ту оконную функцию, которая приводит к наименьшей ошибке восстановления звукового сигнала.

Таким образом, устройство позволяет передать в канал оценку спектра, полученную с использованием выбранной оконной функции, тем самым уменьшить искажения передаваемого сигнала по сравнению с прототипом, а следовательно, улучшить качество воспроизведения сигналов звукового вращения при сохранении пропускной способности.

Формула изобретения 1. Устройство для кодирования сигналов звукового вещания, содержащее фильтр низких частот, вход которого является входом устройства, выход фильтра низких частот соединен с информационным входом аналого-цифрового преобразователя, выходы которого соединены с одноименными информационными входами первого блока оперативной памяти, выходы которого соединены с одноименными первыми информационными входами блока прямого преобразования Фурье, выходы которого соединены с одноименными информационными входами второго блока оперативной памяти и детектора порядка максимальной составляющей, выходы которого соединены с одноименными информационными входами регистра, выходы регистра соединены с одноименными информационными входами преобразователя параллельного кода в последовательный и блока формирования адреса, первые и вторые выходы которого соединены соответственно с одноименными первыми одноименными вторыми адресными входами второго блока оперативной памяти, программно-временной блок, первый - седьмой выходы которого соединены соответственно с объединенными управляющим входом аналого-цифрового преобразователя и первым входом записи первого

блока оперативной памяти, тактовым входом блока прямого преобразования Фурье, объединенными входами управления режимом первого, второго блоков оперативной памяти и входами записи блока

0 формирования адреса и преобразователя параллельного кода в последовательный, объединенными тактовыми входами детектора порядка максимальной составляющей и регистра, объединенными тактовым

5 входом считывания второго блока оперативной памяти и тактовым входом блока формирования адреса, счетным входом блока формирования адреса и входом считывания преобразователя параллельного кода в по0 следовательный, восьмой выход программно-временного блока объединен с выходами второго блока оперативной памяти и преобразователя параллельного кода в последовательный и является выходом устройства,

5 отличающееся тем. что, с целью повышения достоверности устройства, в него введен блок анализа, информационные входы и выходы которого подключены соответственно к одноименным выходам детек0 тора порядка максимальной составляющей и одноименным вторым информационным входам блока прямого преобразования Фурье, девятый - одиннадцатый выходы программно-временного блока соединены

5 соответственно со вторым входом записи, первым и вторым входами считывания первого блока оперативной памяти, двенадцатый выход программно-временного блока соединен с установочными входами первого

0 блока оперативной памяти и блока прямого преобразования Фурье, тринадцатый выход программно-временного блока соединен с управляющим входом блока прямого преобразования Фурье, четырнадцатый - девят5 надцатый выходы программно-временного блока соединены соответственно с первым - шестым управляющими входами блока анализа, двадцатый выход программно-временного блока соединен с тактовым входом

0 записи второго блока оперативной памяти, установочный и седьмой управляющий входы блока анализа подключены соответственно к третьему и четвертому выходам программно-временного блока.

5 2. Устройство поп.,отличающее- с я тем, что блок анализа содержит счетчики, элементы постоянной памяти, перемножители, сумматоры, мультиплексоры, регистры, элемент оперативной памяти, элементы И, компаратор, дешифратор, ключ

и шину единичного потенциала, выход ключа соединен с входом разрешения работы элемента оперативной памяти и счетным входом первого счетчика, выходы которого соединены с одноименными адресными 5 входами элемента оперативной памяти и первого элемента постоянной памяти, выходы которого соединены с одноименными первыми информационными входами первого и второго перемножителей, выходы 10 первого перемножителя соединены с одноименными первыми входами первого сумматора, выходы которого соединены с одноименными информационными входами первого и второго регистров, выходы перво- 15 го регистра соединены с одноименными вторыми входами первого сумматора, выходы второго регистра и выходы элемента оперативной памяти соединены соответственно с одноименными первыми входами и одно- 20 именными вторыми входами второго элемента постоянной памяти, выходы которого соединены с одноименными вторыми информационными входами второго перемноителя, выходы которого соединены с 25 одноименными первыми входами второго сумматора, выходы которого соединены с одноименными информационными входами ретьего, четвертого и пятого регистров, выходы которых соединены соответственно с 30 одноименными вторыми входами второго умматора, одноименными первыми входами компаратора и одноименными первыми информационными входами первого мульиплексора, вторые информационные вхо- 35 ы которого подключены к шине единичного потенциала, выходы первого мультиплексора соединены с одноименными вторыми входами компаратора, выход которого соеинен с первым входом элемента И, выход 40 которого соединен с тактовыми входами пяого и шестого регистров, выходы шестого регистра соединены с одноименными первыми информационными входами второго мультиплексора, выходы второго счетчика соединены с одноименными информационными входами шестого регистра, вторыми информационными входами второго мультиплексора и входами дешифратора, выход которого соединен с управляющим входом первого мультиплексора, вторые информационные входы первого перемножителя объединены с одноименными информационными входами элемента оперативной памяти и являются информационными входами блока анализа, входы установки в О второго счетчика, четвертого, пятого и шестого регистров объединены и являются установочным входом блока анализа, вход установлен в О третьего регистра объединен с вторым входом элемента И и тактовым входом четвертого регистра и является первым управляющим входом блока анализа, вход установки в О первого счетчика объединен с входом установки в О первого регистра и тактовым входом второго регистра и является вторым управляющим входом блока анализа, управляющий вход ключа соединен с входом управления режимом элемента оперативной памяти и является третьим управляющим входом блока анализа, первый информационный вход ключа объединен с управляющим входом второго перемножителя и тактовым входом третьего регистра и является четвертым управляющим входом блока анализа, счетный вход второго счетчика и управляющий вход второго мультиплексора являются соответственно пятым и шестым управляющими входами блока анализа, второй информационный вход ключа объединен с управляющим входом первого перемножителя и тактовым входом первого регистра и вляет- ся седьмым управляющим входом блока анализа, выходы второго мультиплексора являются выходами блока анализа.

п

j сх /- и. С. 6 (, |

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| Измеритель частотных характеристик четырехполюсника | 1988 |

|

SU1661679A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Преобразователь кода спектра звукового сигнала | 1990 |

|

SU1800618A1 |

| Способ анализа спектра сигналов и устройство для его осуществления | 1988 |

|

SU1573432A1 |

| Устройство для измерения частотных характеристик четырехполюсника | 1988 |

|

SU1661680A1 |

| ИЗМЕРИТЕЛЬ СПЕКТРАЛЬНЫХ ПАРАМЕТРОВ РАДИОСИГНАЛОВ | 2005 |

|

RU2279098C1 |

| Устройство для временного и спектрального анализа сигналов | 1990 |

|

SU1793445A1 |

| УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОГО ПРИЕМА СИГНАЛОВ РАЗЛИЧНЫХ СИСТЕМ СПУТНИКОВОЙ НАВИГАЦИИ | 2015 |

|

RU2611069C1 |

Изобретение относится к вычислительной технике, электросвязи и может использоваться в цифровых системах передачи, хранения и воспроизведения звуковых сигналов, В устройстве последовательность отсчетов звукового сигнала разбивается на группы, над которыми осуществляется ортогональное преобразование. Результаты ортогонального преобразования можно интерпретировать как спектр отрезка сигнала, при этом кодированию подвергаются спектральные составляющие, что повышает достоверность устройства. Устройство содержит фильтр 1 низких частот, аналого- цифровой преобразователь 2, блоки 3, 5 оперативной памяти, блок 4 прямого преобразования Фурье, детектор 6 порядка максимальной составляющей, регистр 7, блок 8 формирования адреса, Преобразователь 9 параллельного кода в последовательный, программно-временной блок 10 и блок 11 анализа. 1 з.п. ф-лы, 6 ил. (Л С

y

- f U (

лгг

-г

гН/ХЗ

. i-1 V

i-l

i-г I-

| Устройство кодирования и декодирования сигналов звукового вещания | 1985 |

|

SU1624702A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-11-07—Публикация

1990-02-08—Подача