I

Изобретение относится к автоматике и вычислительной технике и может быть использовано, например, для про- Берки работоспособности цифровых линий связи или цифровых.микросхем.

Цель изобретения - расширение функциональных возможностей путем обеспечения возможности работы с сигналами, имеющими произвольную временнзпо расстановку/тактовых и информационных импульсов.

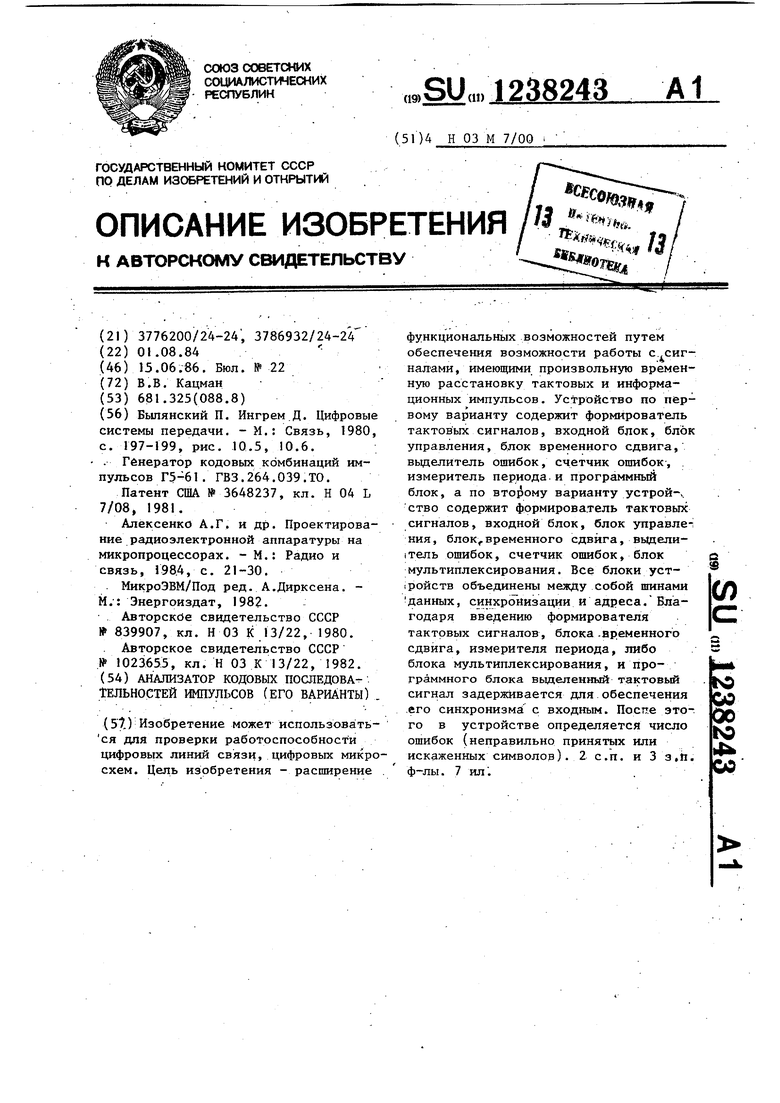

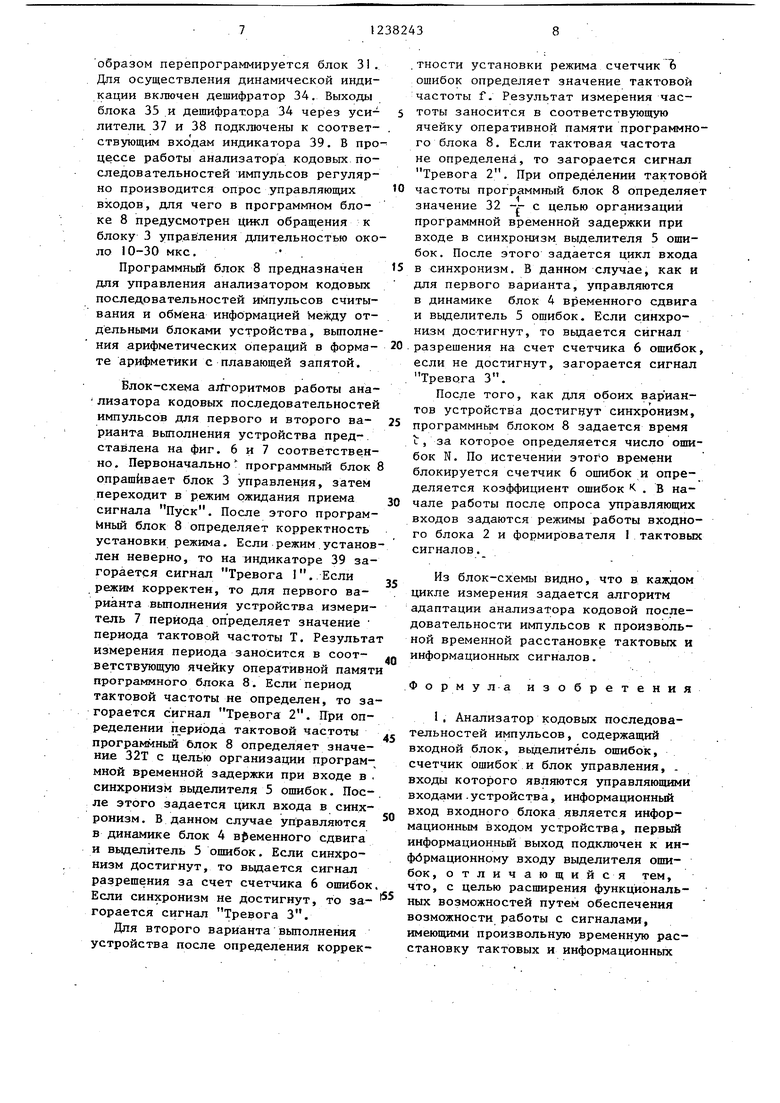

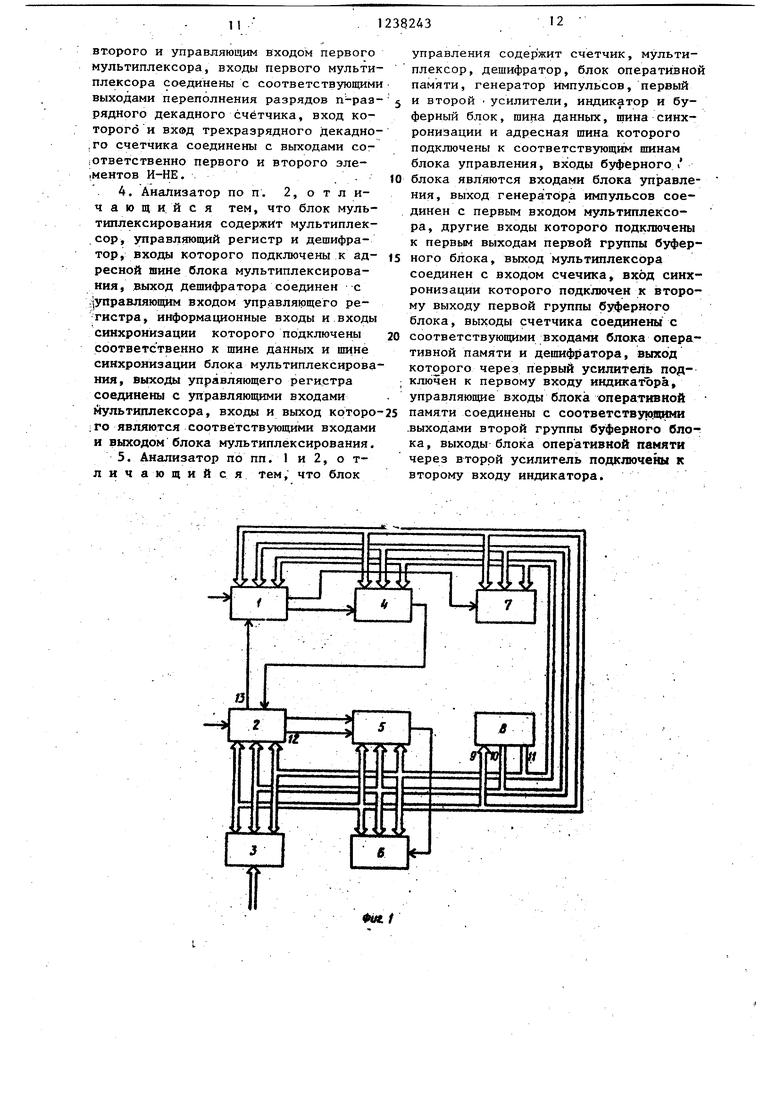

На фиг. и 2 представлены блок- схемы соответствующих вариантов устройства; на фиг. 3 - пример вьтолне- ния измерителя периода; на фиг. 4 - то же, блока мультиплексирования; на фиг. 5 - то же, блока управления; на фиг. 6 и 7 - алгоритмы работы устройства для первого и второго вариантов соответственно.

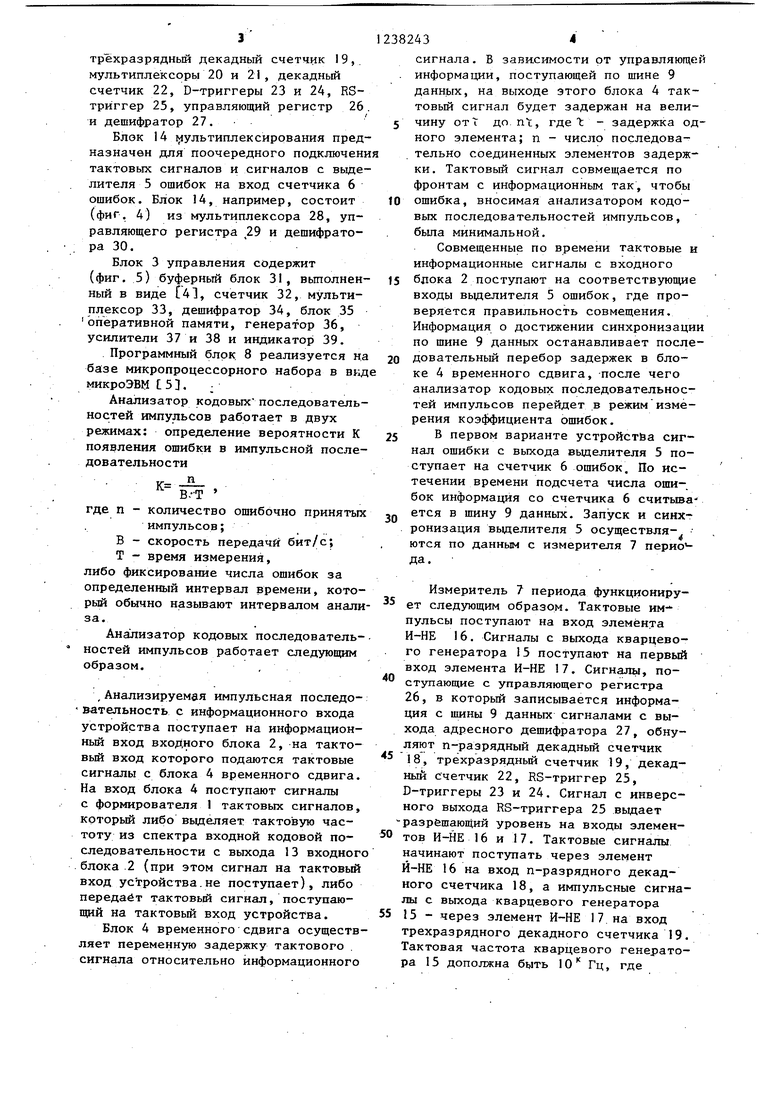

По первому варианту (фиг. 1) ана- пизатор кодовых последовательностей импульсов содержит формирователь |тактовых c Hi HajioB, входной блок 2, блок 3 управления, блок 4 временного сдвига, выделитель 5 ошибок, счетчик 6 ошибок, измеритель 7 периода и программный блок 8, шину 9 данных, шину 10 синхронизации и адресную шину 11. Информационньй вход входного блока 2 являе.тся информационным входом устройства, входы блока 3 управления являются управляющими входами устройства. Первый и второй информационные вьгходы 12 и 13 входного блока 2 соединены соответственно с информационным входом вьщелителя 5 ошибок и первым входом формирователя 1 тактовых, сигналов, второй вход которого является тактовым входом устройства, а первый и второй выходы подключены к входам соответственно измерителя 7. периода и блока 4 временного сдвига, выход которого соединен с так.товым входом входного блока 2, тактовый выход которого подключен к тактовому входу выделителя 5 оши бок, выход которого соединен с входом счетчика 6 ошибок.

По второму варианту (фиг. 2) ана лизатор кодовых последовательностей . импульсов содержит формирователь 1 тактовых сигналов, входной блок 2, блок 3 управления, блок 4 временного сдвига, вьщелитель 5 ошибок, счетчик 6 ошибок, блок 14 мультиплексирования и программный блок 8, шину 9 данных, шииу 10 синхронизации и ад

2382432

ресную шину 11. Информационный вход входного блока 2 является информационным входом устройства, входы блока 3 управления являются управляющими

5 входами устройства. Первый и второй информационные выходы i 2 и 13 входного блока 2 соединены соответственно с информационным входом выделителя 5 ошибок и первым входом формиро 0 вателя 1 тактовых сигналов, второй вход которого является тактовь(М вхо-: дом устройства, а первый и второй выходы подключены соответственно к первому входу блока I4 мультиплекси15 рования .и входу блока 4 временного сдвига, выход которого соединен с тактовым входом входного блока 1, тактовый выход которого подключен к тактовому входу выделителя 5 ошибок,

20 выход которого соединен с вторым входом блока 14 мультиплексирования, выход которого подключен к входу счетчика 6:ошибок, Шина 9 данных является двунаправленной.

25 Формирователь 1 тактовых сигналов может быть выполнен в соответствии с О Он предназначен для того, чтобы преобразовывать выделяемые входным блоком 2 из кодовой последовательнос- .30 ти импульсов, либо поступающие на тактовьй вход устройства .сигналы в сигналы т :товой частоты. Входной . . блок 2 служит для преобразования входных информационных сигналов в

35 стандартные сигналы змиттерно-свя- занной или транзисторно-транзисторной логики (ЭСЛ или ТТЛ) и их декодиро- вания. Блок 4 временного сдвига слу жит для изменения задержки тактового

40 сигнала относительно информационного и может быть выполнен, например, в виде последовательно соединенных элементов одинаковой задержки, выходы котррьгх могут коммутироваться с выхо4J дом блока 2. Выделитель 5 ошибки предназначен дпя определения наличия или отсутствия ошибок в принятом. сигнале, примером его выполнения может служить С33.

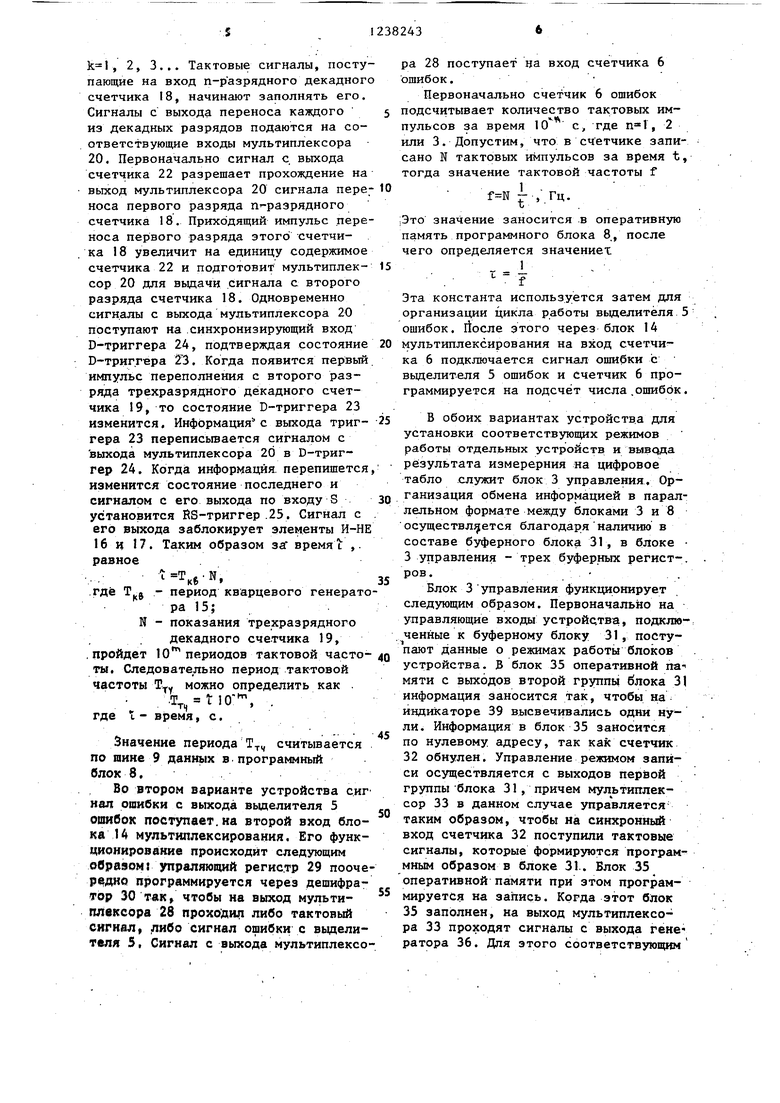

. Измеритель 7 периода предназначен для определения периода тактовой частоты, вьщеленной формирователем 1, на основании данных о котором производится запуск и синхронизация вьще- 55 лителя 5 ошибок. Измеритель 7 перио- да (фиг. З) включает кварцевьй генератор 15, элементы И-НЕ 16, 17,- п-разрядный декадный счетчик 18,

Э

трехразрядный декадный счетник 19,. мультиплексоры 20 и 21, декадный счетчик 22, D-триггеры 23 и 24, RS- триггер 25, управляющий регистр 26 и дешифратор 27.

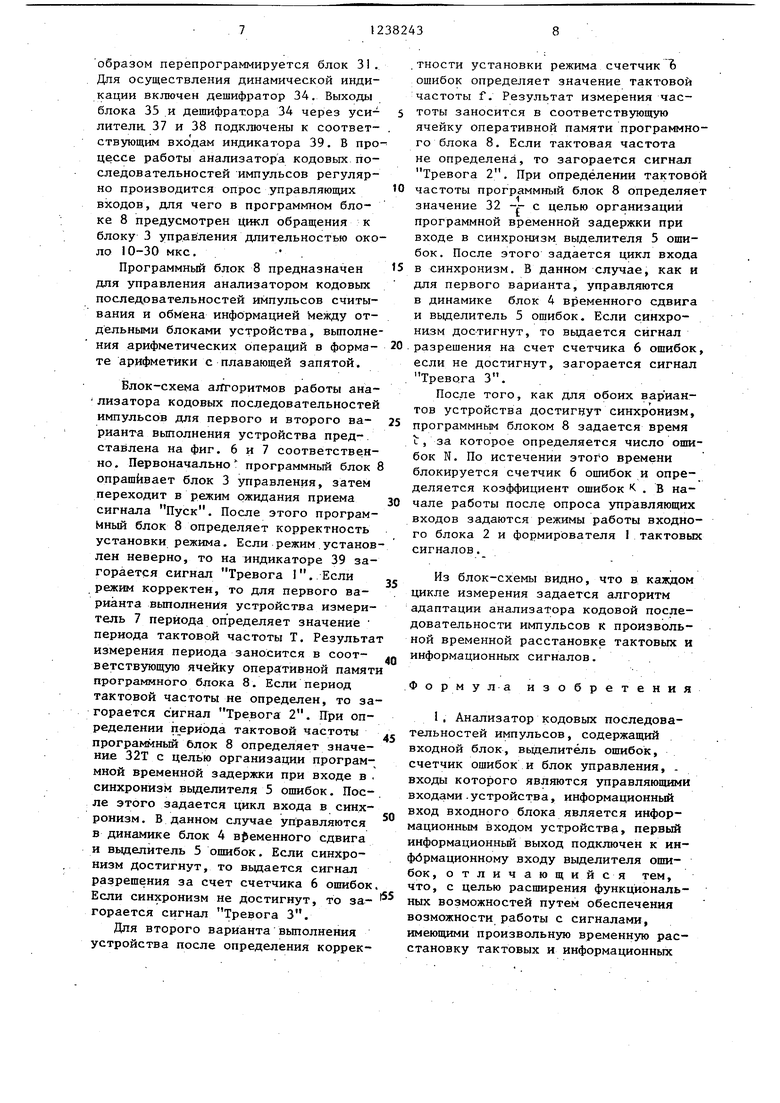

Блок 14 мультиплексирования предназначен для поочередного подключени тактовых сигналов и сигналов с вьще- лителя 5 ошибок на вход счетчика 6 ошибок. Блок 1А, например, состоит (фиг. 4) из мультиплексора 28, управляющего регистра 29 и дешифратора 30.

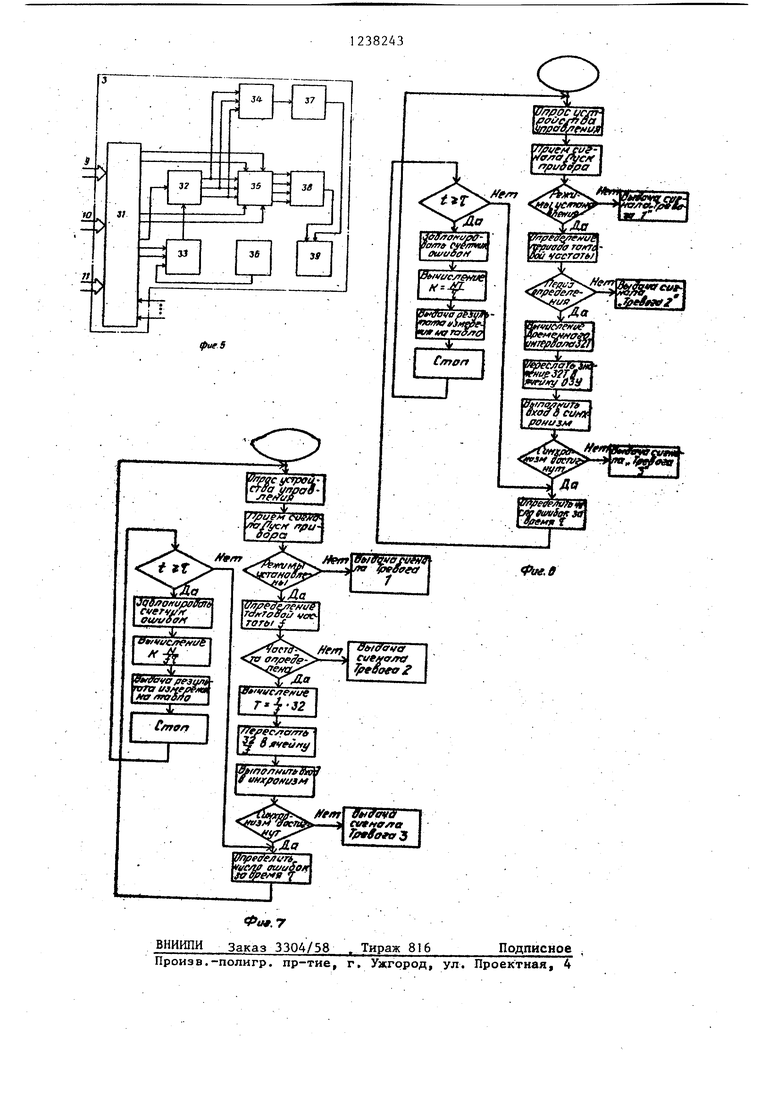

Блок 3 управления содержит (фиг. 5) буферный блок 31, выполненный в виде f4l, счетчик 32, мультиплексор 33, дешифратор 34, блок 35 оперативной памяти, генератор 36, усилители 37 и 38 и индикатор 39.

Программный блок 8 реализуется на базе микропроцессорного набора в вид микроэвм L 5. ;

Анализатор кодовых последовательностей импульсов работает в двух режимах: определение вероятности К появления ошибки в импульсной последовательности п

К

в.-т

где п - количество ошибочно принятых импульсов;

В - скорость передачи бит/с;

Т - время измерения, либо фиксирование числа ошибок за определенный интервал времени, который обычно называют интервалом анализа.

Анализатор кодовых последовательностей импульсов работает следующим образом.,

, Анализируемая импульсная последо- вательность с информационного входа устройства поступает на информационный вход входного блока 2, на тактовый вход которого подаются тактовые сигналы с блока 4 временного сдвига. На вход блока 4 поступают сигналы с формирователя 1 тактовых сигналов, который либо выделяет тактовую частоту из спектра входной кодовой последовательности с выхода 13 входного блока 2 (при этом сигнал на тактовый вход устройства.не поступает), либо передаёт тактовый сигнал, поступающий на тактовый вход устройства.

Блок 4 временного сдвига осуществляет переменную задержку тактового сигнала относительно информационного

382434

сигнала. В зависимости от управляющег . информации, поступающей по шине 9 данных, на выходе этого блока 4 тактовый сигнал будет задержан на вели- 5 чину от Т до nt, гдеt - задержка одного элемента; п - число последовательно соединенных элементов задержки. Тактовый сигнал совмещается по фронтам с информационным так, чтобы

10 ошибка, вносимая анализатором кодовых последовательностей импульсов, была минимальной.

Совмещенные по времени тактовые и информационные сигналы с входного

15 блока 2 поступают на соответствующие входы выделителя 5 ошибок, где проверяется правильность совмещения. Информация о достижении синхронизации по шине 9 данных останавливает после20 довательный перебор задержек в блоке 4 временного сдвига, после чего анализатор кодовых последовательностей импульсов перейдет в режим измерения коэффициента ошибок.

5 В первом варианте устройства сигнал ошибки с выхода вьщелителя 5 поступает на счетчик 6 ошибок. По истечении времени подсчета числа оши-. бок информация со счетчика 6 считыва

,jj ется в шину 9 данных. Запуск и синхронизация выделителя 5 осуществляются по данным с измерителя 7 перио - да.

Измеритель 7 периода функциониру5 ет следующим образом. Тактовые им- пульсы поступают на вход элемента И-НЕ 16. Сигналы с выхода кварцевого генератора 15 поступают на первый вход элемента И-НЕ 17. Сигналы, поступающие с управляющего регистра 26, в который записывается информация с шины 9 данных сигналами с выхода адресного дешифратора 27, обнуляют п-разрядный декадный счетчик

5 18, трехразрядный счетчик 19, декадный с четчик 22, RS-триггер 25, D-триггеры 23 и 24. Сигнал с инверсного выхода RS-триггера 25 выдает -разрешающий уровень на входы элемен0 тов И-НЕ 16 и 17. Тактовые сигналы начинают поступать через элемент И-НЕ 16 на вход п-разрядного декадного счетчика 18, а импульсные сигналы с выхода кварцевого генератора

5 15 - через элемент И-НЕ 17 на вход трехразрядного декадного счетчика 19. Тактовая частота кварцевого генератора 15 дополжна быть IО Гц, где

0

, 2, 3... Тактовые сигналы, поступающие на вход п-р азрядного декадного счетчика 18, начинают заполнять его. Сигналы с выхода переноса каждого из декадных разрядов подаются на соответствующие входы мультиплексора 20. Первоначально сигнал с. выхода счетчика 22 разрешает прохождение на выход fyльтиплeкcopa 20 сигнала пере- носа первого разряда п-разрядного счетчика 18. Приходящий импульс переноса первого разряда этого счетчи- ка 18 увеличит на единицу содержимое счетчика 22 и подготовит мультиплек- сор 20 для выдачи сигнала с второго разряда счетчика 18. Одновременно сигналы с выхода мультиплексора 20 поступают на .синхронизирующий вход D-триггера 24, подтверждая состояние D-триггера 2ГЗ. Когда появится первый импульс переполнения с второго разряда трехразрядного декадного счетчика 19, то состояние D-триггера 23 изменится. Информация с выхода триг- гера 23 переписьшается сигналом с выхода мультиплексора 20 в D-триг- гер 24. Когда информация, перепишется изменится состояние последнего и

сигналом с его выхода по входу S установится RS-триггер .25. Сигнал с

его выхода заблокирует элементы И-НЕ

16 ч 17. Таким образом заг время t ,.

равное

к6

N,

35

где - период кварцевого генератора 15; N - показания трехразрядного

декадного счетчика 19, ройдет 10 периодов тактовой часто- о ты. Следовательно период тактовой частоты TYV можно определить как .

. .T tlO-, . где t- время, с.

Значение периода Т,„ считывается

по шике 9 дани1ых в программный блок 8,

Во втором варианте устройства сиг нал ошибки с вьпсода выделителя 5 ошибок поступает.на второй вход блока 14 мультиплексирования. Его функционирование происходит следующим образомг упраляющий регистр 29 пооче- р(дао программируется через дешифратор 30 так чтобы иа выход мульти- плексора 28 проходил либо тактовый сигнал, .либо сигнал ошибки с выделителя 5, Сигнал с выхода мультиплексо5Ю 15 20 5

0

5

о

5

0

ра 28 поступает на вход счетчика 6 ощибок.

Первоначально счетчик 6 ошибок подсчитывает количество тактовых импульсов за время 10 с, где , 2 или 3. Допустим, что в счетчике записано N тактовых импульсов за время t, тогда значение тактовой частоты f

: ,.гц.

;Это значение заносится в оперативную память программного блока 8, после чего определяется значениет

1

. . t J

Эта константа используется затем для организации цикла работы вьщелителя 5 ошибок. Йосле этого через блок 14 мультиплексирования на вход счетчика 6 подключается сигнал ошибки с вьщелителя 5 ошибок и счетчик 6 программируется на подсчёт числа .ошибок.

В обоих вариантах устройства для установки соответствующих режимов работы отдельных устройств и вывода результата измерерния на цифровое табло .служит блок 3 управления. Организация обмена информацией в параллельном формате между блоками 3 и 8 осуществляется благодаря наличию в составе буферного блока 31, в блоке 3 управления - трех буферных регист-. ров..

Блок 3 управления функционирует следующим образом. Первоначально на управляющие входы устройства, подклю- ченные к буферному блоку 31, поступают данные о режимах работы блоков устройства. В блок 35 оперативной na-i мяти с выходов второй группы блока 31 информация заносится так, чтобы на индикаторе 39 высвечивались одни нули. Информация в блок 35 заносится по нулевому адресу, так как счетчик 32 обнулен. Управление режимом записи осуществляется с выходов первой группы блока 31, причем мультиплексор 33 в данном случае управляется- таким образом, чтобы на синхронный вход счетчика 32 поступили тактовые сигналы, которые формируются програм- MHbW образом в блоке 31. Блок 35 оперативной памяти при этом программируется на запись. Когда этот блок 35 заполнен, на выход мультиплексора 33 проходят сигналы с выхода гене- ратора 36. Для этого соответствующим

образом перепрограммируется блок 31. Для осуществления динамической индикации включен дешифратор 34. Выходы блока 35 и дешифратора 34 через уси- литела 37 и 38 подключены к соответ- . ствующим вхо дам индикатора 39. В про- цессе работы анализатора кодовых последовательностей импульсов регулярно производится опрос управляющих

входов, для чего в программном блоке 8 предусмотрен цикл обращения к блоку 3 управления длительностью около 10-30 МКС. .

Программный блок 8 предназначен для управления анализатором кодовых последовательностей импульсов считывания и обмена информацией между отдельными блоками устройства, вьтолне ния арифметических операций в форма- те арифметики с плавающей запятой.

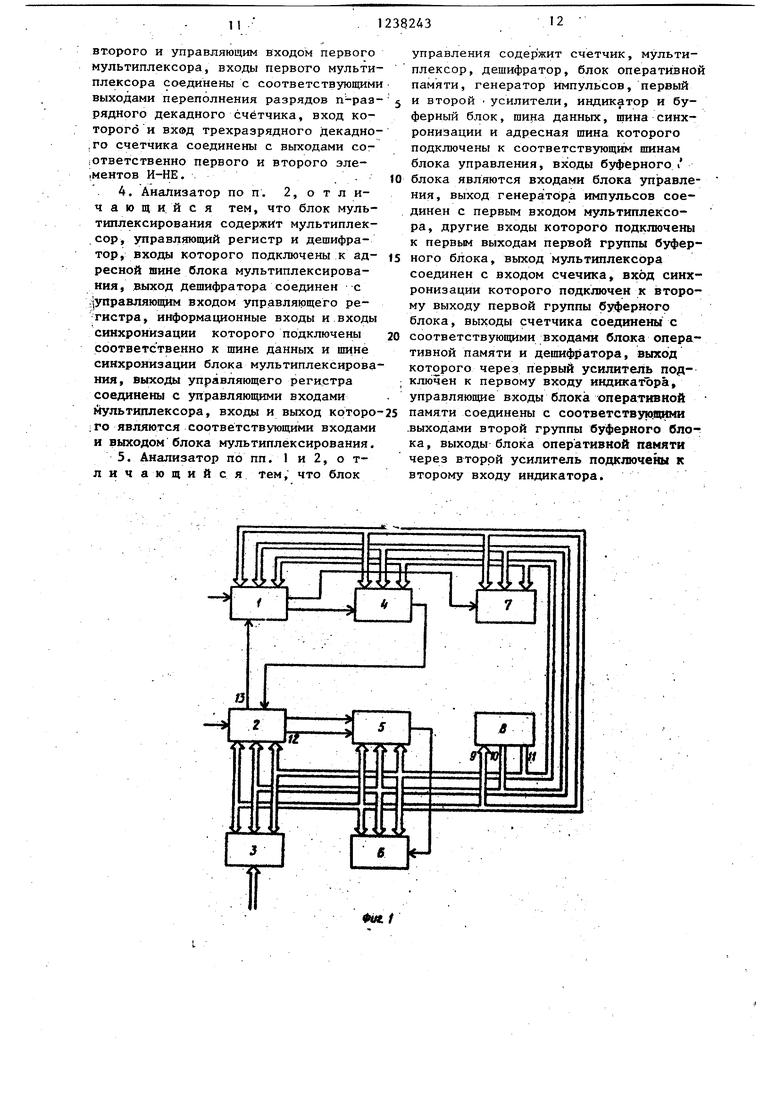

Блок-схема алгоритмов работы ана- лизатора кодовых последовательностей импульсов для первого и второго ва- риаита вьтолнения устройства пред-. ставлена на фиг. 6 и 7 соответственно. Первоначально программный блок опрашивает блок 3 управления, затем переходит в режим ожидания приема сигнала Пуск. После этого программный блок 8 определяет корректность установки режима. Если режим.установлен неверно, то на индикаторе 39 за

горается сигнал Тревога I. Если режим корректен, то для первого варианта вьтолнения устройства измеритель 7 периода определяет значение периода тактовой частоты Т. Результа измерения периода заносится в соответствующую ячейку оперативной памят программного блока 8. Если период тактовой частоты не определен, то загорается сигнал Тревога 2. При определении периода тактовой частоты программный блок 8 определяет значение 32т с целью организации программной временной задержки при входе в синхронизм выделителя 5 ошибок. После этого задается цикл входа в синхронизм . В данном случае управляются в динамике блок 4 временного сдвига и выделитель 5 ошибок. Если синхронизм достигнут, то вьщается сигнал разрешения за счет счетчика 6 ошибок Если синхронизм не достигнут, то за- горается сигнал Тревога 3.

Для второго варианта выполнения устройства после определения коррек

5

10

5 0

5 о

5

0

.тности установки режима счетчик Ъ ошибок определяет значение тактовой частоты f. Результат измерения частоты заносится в соответствующую ячейку оперативной памяти программного блока 8. Если тактовая частота не определена, то загорается сигнал Тревога 2. При определении тактовой частоты программный блок 8 определяет значение 32 -,- с целью организации программной временной задержки при входе в синхронизм выделителя 5 ошибок. После этого задается цикл входа в синхронизм. В данном случае, как и для первого варианта, управляются в динамике блок 4 временного сдвига и выделитель 5 ошибок. Если синхронизм достигнут, то вьщается сигнал разрешения на счет счетчика 6 ошибок, если не достигнут, загорается сигнал Тревога 3.

После того, как для обоих вариантов устройства достигнут синхронизм, программнь1м блоком 8 задается время t, за которое определяется число ошибок N. По истечении этого времени блокируется счетчик 6 ошибок и определяется коэффициент ошибок . В начале работы после опроса управляющих входов задаются режимы работы входного блока 2 и формирователя 1 тактовых сигналов.

Из блок-схемы видно, что в каждом цикле измерения задается алгоритм адаптации анализатора кодовой последовательности импульсов к произвольной временной расстановке тактовых и информационных сигналов. .

Формула изобретения

1, Анализатор кодовых последовательностей импульсов, содержащий входной блок, вьщелитёль ошибок, счетчик ошибок и блок управления, . входы которого являются управляющими входами-устройства, информационный вход входного блока является информационным входом устройства, первый информационньй выход подключен к ин- фбрмационному входу выделителя ошибок , отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения возможности работы с сигналами, имеющими произвольную временную расстановку тактовых и информационных

импульсов, в него введены формирователь тактовых сигналов, блок временного сдвига, измеритель периода и программный блок, шина данных, шина синхронизации и адресная шина которого подключены -к соответствующим шинам входного блока, выделителя ошибок, счетчика ошибок, блока управления, формирователя тактовых сигналов, блока временного сдвига и измерителя периода, второй информационный выход входного -блока ,соединен с первым входом формирователя тактовых сигналов, второй вход кото- рого является тактовым входом устрой ства, а первый и второй выходы подключены к входам соответственно измерителя периода и блока временного сдвига, выход которого соединен с тактовым входом входного блока, тактовый выход которого подключен к тактовому входу выделителя ошибок, выход которого соединен с входом счетчика ошибок.

2.. Анализатор кодовых последова- тельнбстей импульсов, содержащий входной блок, выделитель ошибок, счетчик ошибок и блок управления, входы которого являются управляющими входами устройства, информационный вход входного блока является информационным входом устройства, первый информационньй выход подключен к информационному входу вьщелителя ошибок, отличающийся тем, что, с целью расширения функциональ- ных возможностей путем обеспечения возможности работы с сигналами, имеющими произвольную временную расста-; новку тактовых и информационных импульсов, в него введены формирователь тактовых сигналов, блок временного сдвига, блок мультиплексировани и программный блок, шина данных, синхронизации и адресная шина которого подключены к соответствующим шина входного блока, выделителя ошибок, счетчика ошибок, блока управления, формирователя тактовых сигналов, блока временного сдвига и блока мультиплексирования, второй информационный выход входного блока соединен с первым входом формирователя тактовых сигналов, второй вход которого явля- ется тактовым входом устройства, а первый и второй выходы подключены со ответетвенно к первому входу блока

0 5 0 5

о

5

0

мультиплексирования и входу блока временного сдвига, выход которого соединен с тактовым входом входного блока, тактовьй выход которого подключен к тактовому входу выделителя ошибок, выход которого соединен с вторым входом блока мультиплексирования, выход которого подключен к входу счетчика ошибок..

3. Анализатор по п. -1 , о т л и- чающийся тем, что измеритель периода содержит кварцевый,генератор, п-разрядный декадный счетчик, трех- . разрядный декадный счетчик, первый и второй мультиплексоры, декадный счетчик, RS-триггер, первый и второй Б-триггеры, управляющий регистр, дешифратор, первый и второй элементы И-НЕ, первые входы которых соединены соответ ственно с входом измерителя периода и с выходом кварцевого генератора, вторые входы объединены и подключены к выходу RS-триггера, вход установки в ноль которого объединен с входами установки в ноль D-тригге- ров декадного счетчика, п-разрядного декадного счетчика и трехразрядного декадного счетчика и подключен к выходу управляющего регистра, выходы разрядов трехразрядного декадного счетчика соединены с соответствующими входами второго мультиплексора, выходы которого объединены с соответствующими информационными входами уп-- равлякэщего регистра и подключены к , шине данных измерителя периода, входы синхронизации управлякмцего регистра соединены с шиной синхронизации измерителя периода, управляющий вход уп- райляющего регистра подключен к первому выходу дешифратора. Входы которого соединены с адресной шиной измерителя периода, второй выход дешифратора соединен с первым управляк - щим входом второго мультиплексора, второй управляющий вход которого объединен с входом установки в единицу RS-триггера и подключен к выходу второго D-триггера, вход которого соединен с выходом первого D-триггера, вход которого подключен к выходу переполнения второго разряда трехразрядного декадного счетчика, синхронизирующий вход второго D-триггера объединен с входом декадного счетчика и подключен к выходу первого мультиплексора, выход декадного счетчика соедин ен с третьим управляющим входом

второго и управляющим входом первого мультиплексора, входы первого мультиплексора соединены с соответствующими выходами переполнения разрядов рядного декадного счётчика, вход которого и вх®д трехразрядного декадно- ,го счетчика соединены с выходами со- ответственно первого и второго эле- (Ментов И-НЕ.. -

4.Анализатор по п. 2, о т л и- чающийся тем, что блок мультиплексирования содержит мультиплексор, управляющий регистр и дешифратор, входы которого подключены к ад- ресной шине блока мультиплексирования, выход дешифратора соединен с

.управляющим входом управляющего регистра, информационные входы и входы синхронизации которого подключены соответственно к шине данных и шине синхронизации блока мультиплексирования, выходы управляющего регистра соединены с управляющими входами мультиплексора, входы и выход которо :го являются соответствующими входами и выходом блока мультиплексирования.

5.Анализатор по пп. 1 и 2, о т- личающийся тем, что блок

управления содержит счетчик, мультиплексор, дешифратор, блок оперативной памяти, генератор Импульсов, первый и второй усилители, индикатор и буферный блок, шина данньпс, щина синхронизации и адресная шина которого подключены к соответствующш шинам блока управления, входы буферного i блока являются входами блока управления, выход генератора импульсов соединен с первым входом мультиплексора, другие входы которого подключены к первым выходам первой группы буферного блока, выход мультиплексора соединен с входом счечика, вход синхронизации которого подключен к второму выходу первой группы бзгферного блока, выходы счетчика соединены с соответствующими входами блока оперативной памяти и дешифратора, выход которого через первый усилитель подключен к первому входу индикат ора, управляющие входы блока оперативной памяти соединены с соответствуккщими .выходами второй группы буферного блока, выходы блока оперативной памяти через второй усилитель подключены к второму входу индикатора.

Фia.f

ut г

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1985 |

|

SU1339894A1 |

| Декодирующее устройство | 1987 |

|

SU1497745A1 |

| Анализатор кодовых последовательностей импульсов | 1985 |

|

SU1305868A2 |

| Анализатор кодовых последовательностей импульсов | 1984 |

|

SU1208609A2 |

| Генератор кодовых последовательностей импульсов | 1987 |

|

SU1531080A1 |

| Анализатор кодовых последовательностей импульсов | 1982 |

|

SU1099387A2 |

| Устройство телеконтроля регенераторов цифровой системы передачи | 1985 |

|

SU1261125A1 |

| Устройство для обнаружения неисправного регенератора | 1988 |

|

SU1561207A1 |

| Кодирующее устройство | 1988 |

|

SU1587638A1 |

| УСТРОЙСТВО ПРИЕМА ИНФОРМАЦИИ ИЗ КАНАЛА | 1998 |

|

RU2137320C1 |

) Изобретение может использова ть- ся для проверки работоспособности цифровых линий связи, цифровых микросхем. Цель изобретения - расширение функциональных возможностей путем обеспечения возможности работы с сигналами , имеющими произвольную временную расстановку тактовых и информационных импульсов. Устройство по первому варианту содержит формирователь так то в ых сигналов, входной блок, блок управления, блок временного сдвига, вьщелитель ошибок, счетчик ошибок, измеритель периода.и программный блок, а по второму варианту устрой-., ство содержит формирователь тактовых сигналов, входной блок, блок управле-- НИН, блок временного сдвига, выдели- |Тель ошибок, счетчик ошибок, блок мультиплексирования. Все блоки уст- Фойств объединены между собой шинами данных, синхронизации и адреса. Благодаря введению формирователя тактовых сигналов, блока .временного сдвига, измерителя периода, либо блока мультиплексирования, и программного блока вьщеленный тактовый сигнал задерживается для обеспечения его синхронизма с входным. Поспе это-: го в устройстве определяется число ошибок (неправильно принятых или искаженных символов). 2 с.п. и 3 з.й, ф-лы. 7 ил . О ф (Л

29

10

30

JJ

фиг Л

№ ffcycipffu CTffa иарао- effuf

ycipoti- rn

f/flt/ef cuffffif

off/fycff паиoopa

Mrm

J fS/fOffuaffffcfft

CWfVf/ff

owt/o rf

o fvc/rf/ tfe

fftfffffva реза/ч vravMfjpfiM far moMo

Стоп

g effMi, V4fM/r me/u&OH f 7

f,e

Тираж 816

Подписное

г. Ужгород, ул. Проектная, 4

Тираж 816

Подписное

Ужгород, ул. Проектная, 4

| Былянский П | |||

| Ингрем Д | |||

| Цифровые системы передачи | |||

| - М.: Связь, 1980, с | |||

| Способ утилизации отработанного щелока из бучильных котлов отбельных фабрик | 1923 |

|

SU197A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3648237, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Алексенко А.Г | |||

| и др | |||

| Проектирование радиоэлектронной аппаратуры на микропроцессорах | |||

| - М.: Радио и связь, 198.4, с | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Микроэвм/Под ред | |||

| А.Дирксена | |||

| - М.: Энергоиздат, 1982 | |||

| Вибрационный конвейер | 1979 |

|

SU839907A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Анализатор кодовых последовательностей импульсов | 1982 |

|

SU1023655A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-06-15—Публикация

1984-08-01—Подача