VI

4;ib

4

Изобретение относится к импульсной технике и может быть использовано как с составе универсальных выс:о- копроизводительных систем технической диагностики, автоматическсн о управления и контроля, так и автономно, в качестве таймера для вычислительных устройств, работающих в реальном масштабе времени, блока задания и измерения временных интервалов, устройства синхронизации и т.д.

Цель изобретения - расширение функциональных возможностей многоканального программируемого генератора импульсов за счет обеспечения взаимно независимого формирования периода импульсов в каждом канале и изменения значений периода, длительности и задержки формируемых в каждом канале импульсов без прерывания их генерирования, а также расширение динамического диапазона значений периода импульсных последовательностей при со- рранении разрядности управляющего слова.

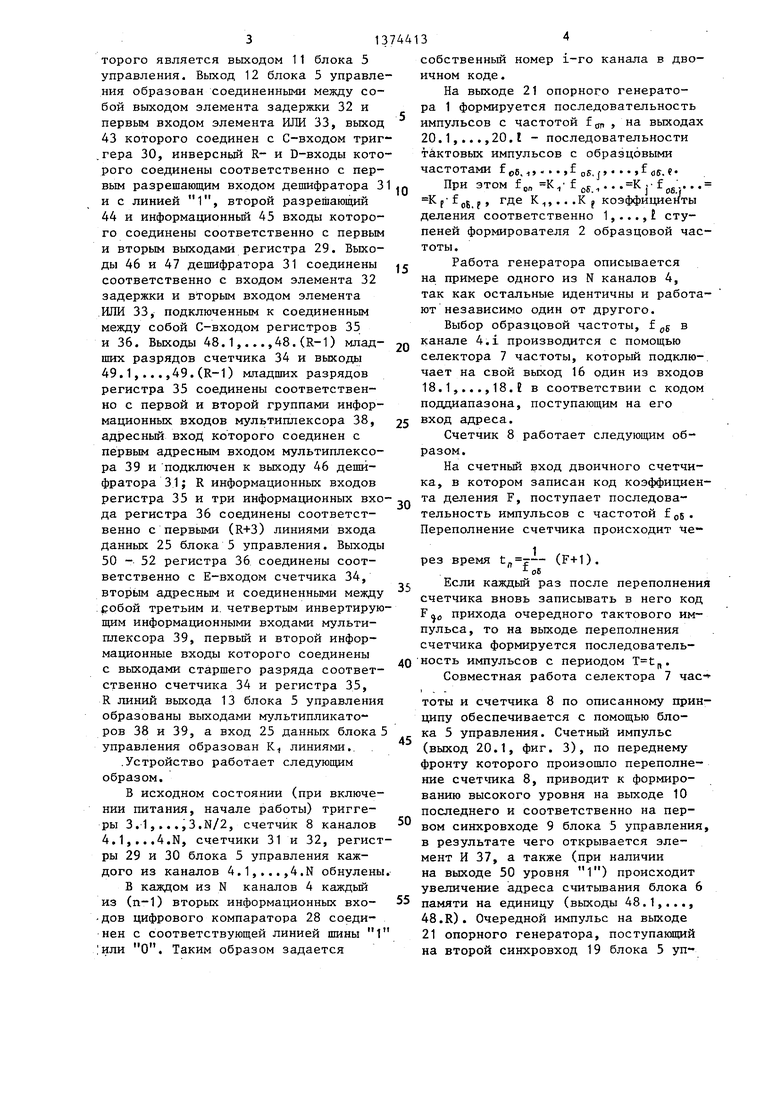

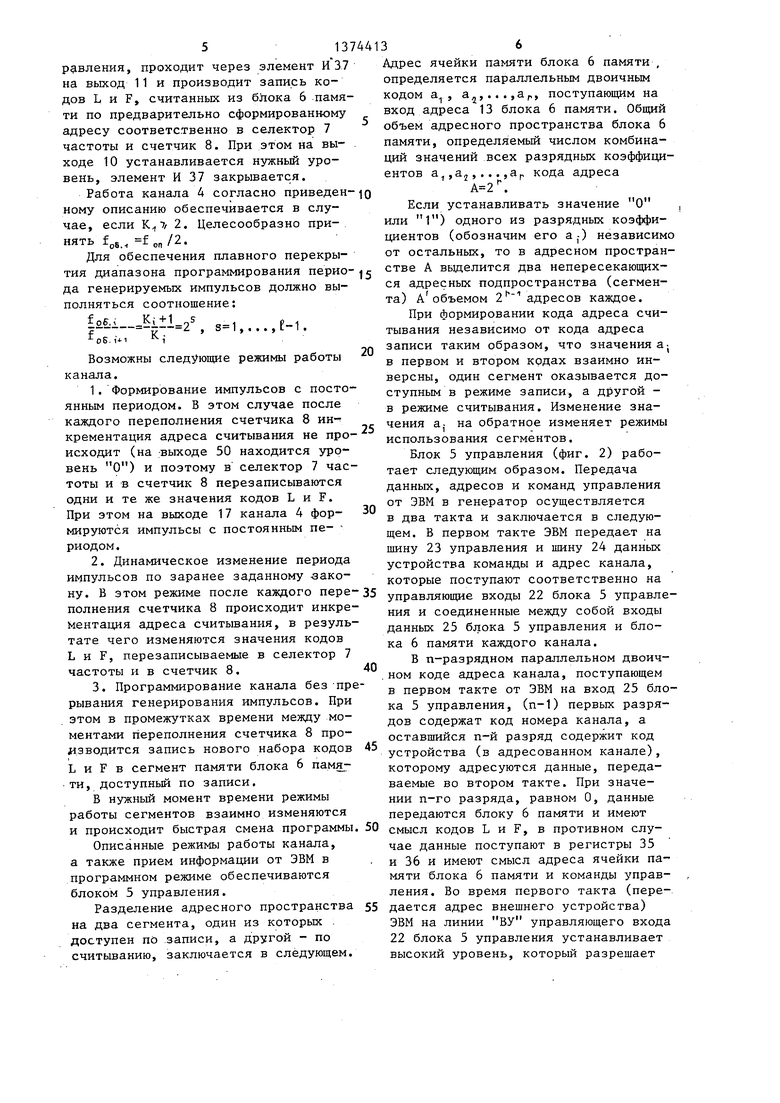

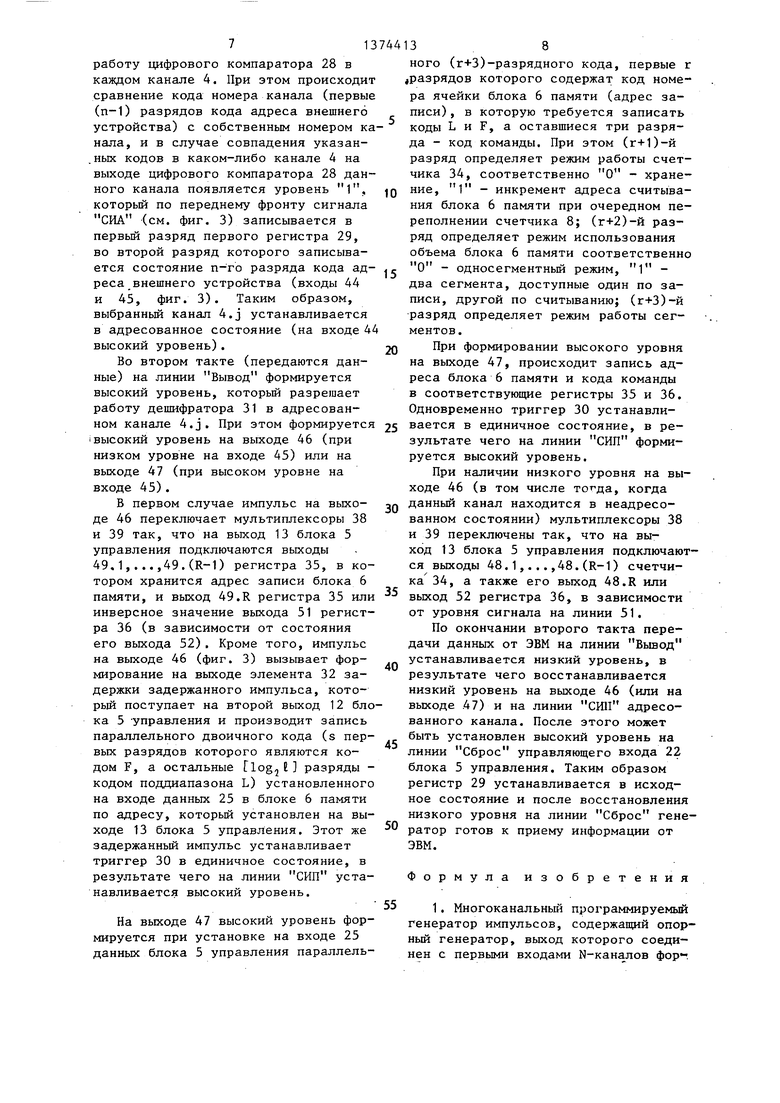

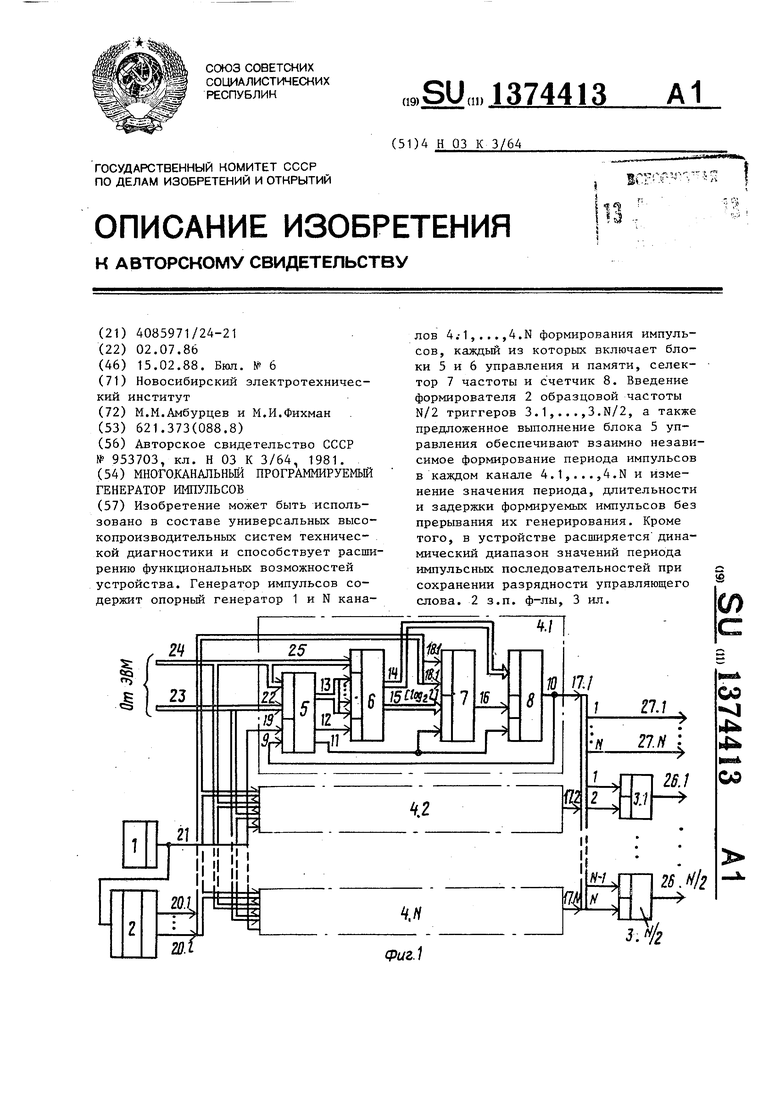

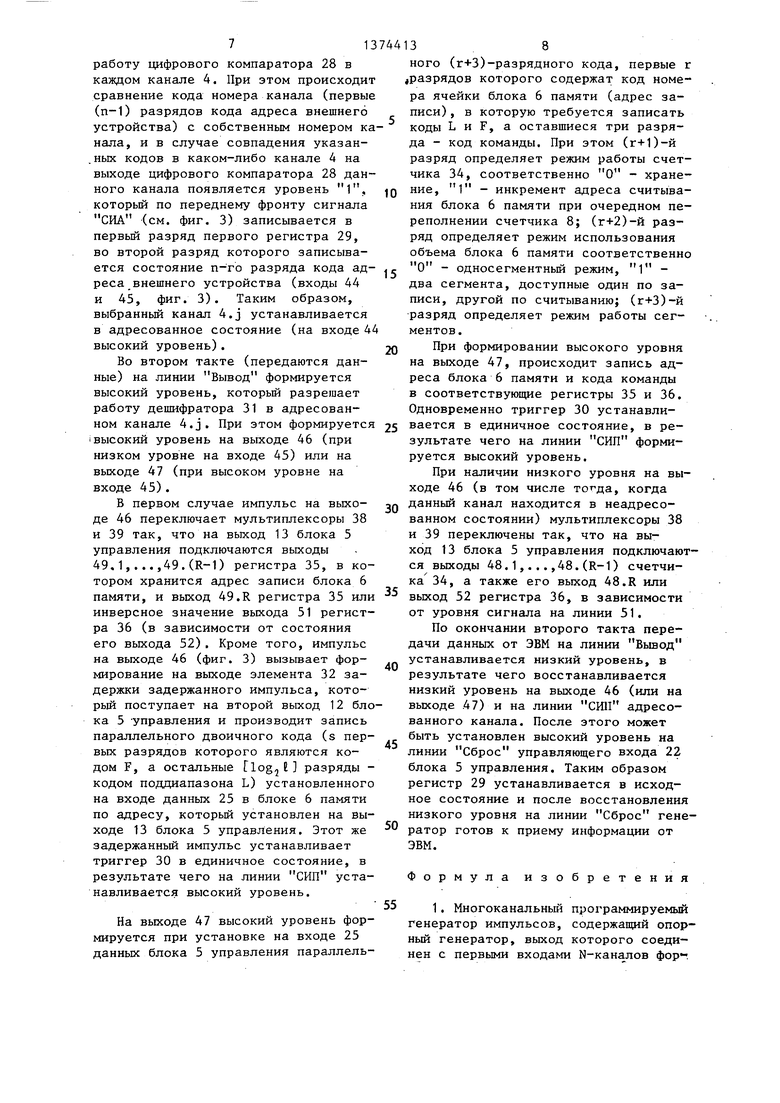

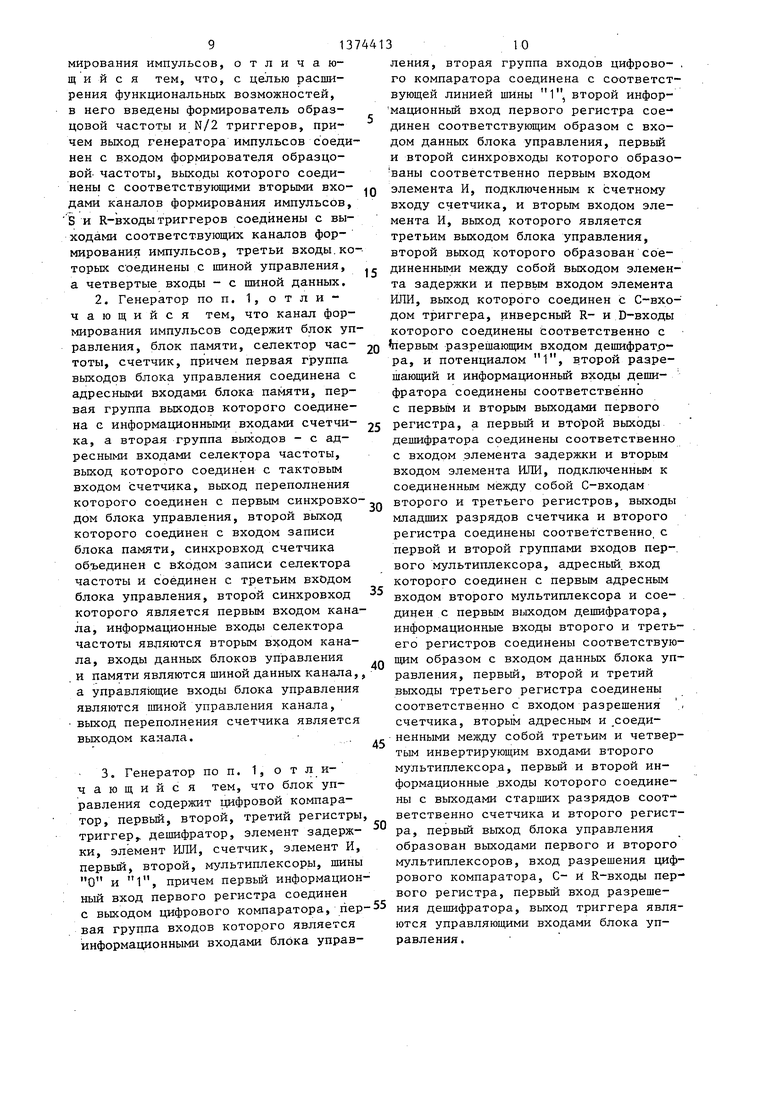

На фиг. 1 представлена функциональная схема многоканального программируемого генератора импульсов; на фиг. 2 - функциональная схема бло ка управления; на фиг. 3 - временные диаграммы, поясняющие работу блока управления;

Многоканальньй программируемьгй генератор импульсов содержит опорный генератор 1, выход которого подключен к входу формирователя 2 образцовой частоты N/2 триггеров 3.1,.,., 3.N/2 и N каналов 4.1,...,4,N формирования импульсов, каждый из которых содержит блок 5 управления, блок 6 памяти,селектор 7 частоты и счетчик 8 В каждом из N каналов 4.1,.,.,4.N синхровход 9 блока 5 управления соединен с выходом 10 переполнения счетчика 8, С-вход которого соединен с входом записи адреса селектора 7 частоты и подключен к выходу 11 блока 5 управления, выходы 12 и 13 которого соединены соответственно с входами записи и адреса блока 6 памяти. Группы выходов 14 и 15 блока 6 памяти соединены соответственно с информационными входами счетчика 8 и с соответствующими адресными входами селектора 7 частоты, подключенного выходом 16 к счетному входу счетчика В, выход переполнения 10 которого является выходом 17 канала 4. Инфор10

15

20

25

13744132

мационные входы 18.1,...,18.Р селектора частоты 7 и синхровход 19 блока 5 управления каждого канала 4 соединены соответственно с выходами 20.1,...,20.Р формирователя 2 образцовых частот и выходом 21 опорного генератора 1. Управляющий вход 22 блока 5 управления соединен с соответствующими входами остальных каналов 4 и образует шину 23 управления генератора, шина 24 данных которого образована К линиями, из которых в каждом канале первые К линий соединены с входами 25 данных блока 5 управления, а Kj линий - с соответствующим входом данньк блока 6 памяти. Выходы триггеров 3 . 1, .. .,3.N/2 образуют группу выходов 26.1,...,26.N/2 генератора, дополнительная группа выходов 27.1,...,27.N которого образована выходами 17.1,...,17.N каналов 4.1,...,4.N причем выходы 17.(21-1) и 17.(21) подключены соответственно к S- и R-входам триггера 3.1, где 1 - от 1 до N/2. Цепи установки устройства в исходное состояние не показаны.

Блок 5 управления (фиг.2) содержит цифровой компаратор 28, регистр 29, триггер 30, дешифратор 31, элемент 32 задержки, элемент ИЛИ 33, двоичньш R-разрядный счетчик 34, R-разрядный регистр 35 и регистр 36, элемент И 37, мультиплексоры 38 и 39 и шину О 40. При этом линии ВУ, СИП, Вывод, СИЛ и Сброс управляющего входа 22 блока 5 управления образованы соответственно разрешающим входом цифрового компаратора 28, выходом триггера 30, первым разрешающим входом дешифратора 31, С- и R-входами регистра 29, информационный вход 41 которого соединен с выходом цифрового компаратора 28. Первые (п-1) линии входа данных 25 блока 5 управления соединены соответственно с первыми (п-1) информационными входами 42 .1,.. . ,42.(п-1) цифрового компаратора 28, каждый из (п-1) вторых информационных входов которого соединен с соответствующей линией шины 1. Второй информационньй вход регистра 29 соединен с п-й линией входа данных 25 блока 5 управления. Син- хровходы 9 и 19 блока 5 управления образованы соответственно первым входом элемента И 37, подключенным к счетному входу счетчика 34, и. вторым входом элемента И 37, выход ко-30

35

40

45

50

55

-30

3137441

торого является выходом 11 блока 5 управления. Выход 12 блока 5 управления образован соединенными между собой выходом элемента задержки 32 и первым входом элемента ИЛИ 33, выход 43 которого соединен с С-входом триг- ,гера 30, инверсный R- и D-входы которого соединены соответственно с первым разрешающим входом дешифратора 31

и с линией 1, второй разрешающий 44 и информационный 45 входы которого соединены соответственно с первым и вторым выходами регистра 29. Выходы 46 и 47 дешифратора 31 соединены соответственно с входом элемента 32 задержки и вторым входом элемента ИЛИ 33, подключенным к соединенным между собой С-входом регистров 35 и 36. Выходы 48.1,...,48.(R-1) млад- ших разрядов счетчика 34 и выходы 49.1,...,49.(R-1) младших разрядов регистра 35 соединены соответственно с первой и второй группами информационных входов мультиплексора 38, адресный вход которого соединен с первым адресным входом мультиплексора 39 и подключен к выходу 46 дешифратора 31; R информационных входов регистра 35 и три информационных вхо да регистра 36 соединены соответственно с первыми (R+3) линиями входа данных 25 блока 5 управления. Выходы 50 - 52 регистра 36 соединены соответственно с Е-входом счетчика 34, вторым адресным и соединенными между собой третьим и. четвертым инвертирующим информационными входами мультиплексора 39, первый и второй информационные входы которого соединены с выходами старшего разряда соответственно счетчика 34 и регистра 35, R линий выхода 13 блока 5 управления образованы выходами мультипликаторов 38 и 39, а вход 25 данных блока 5 управления образован К линиями,. .Устройство работает следующим образом.

В исходном состоянии (при включении питания, начале работы) триггеры 3.1,...,3.N/2, счетчик 8 каналов 4,1,...4.N, счетчики 31 и 32, регистры 29 и 30 блока 5 управления каждого из каналов 4,1,...,4.N обнулены

В каждом из N каналов 4 каждый из (п-1) вторых информационных вхо-

дов цифрового компаратора 28 соединен с соответствующей линией шины 1

;или О. Таким образом задается

0 5 ,.

0

5

5

0

5

собственный номер i-ro канала в двоичном коде.

На выходе 21 опорного генератора 1 формируется последовательность импульсов с частотой f ;,„ , на выходах 20.1,...,20.I - последовательности тактовых импульсов с образцовыми

частотами f pg. и ,f os.j Д of.

При этом „„ К, f jf , ...K.,. .. Kp-fpjj, где К ,.. .К j коэффициенты деления соответственно 1,..., ступеней формирователя 2 образцовой частоты.

Работа генератора описывается на. примере одного из N каналов 4, так как остальные идентичны и работают независимо один от другого.

Выбор образцовой частоты, f g в канале 4.1 производится с помощью селектора 7 частоты, который подключает на свой выход 16 один из входов 18.1,...,18. в соответствии с кодом поддиапазона, поступающим на его вход адреса.

Счетчик 8 работает следующим образом.

На счетный вход двоичного счетчика, в котором записан код коэффициента деления F, поступает последовательность импульсов с частотой foS Переполнение счетчика происходит че

рез время (F+1).

- о5

Если каждьш раз после переполнения счетчика вновь записывать в него код F д прихода очередного тактового импульса, то на выходе переполнения счетчика формируется последовательность импульсов с периодом .

Совместная работа селектора 7 час-

тоты и счетчика 8 по описанному принципу обеспечивается с помощью блока 5 управления. Счетный импульс (выход 20.1, фиг. 3), по переднему фронту которого произошло переполнение счетчика 8, приводит к формированию высокого уровня на выходе 10 последнего и соответственно на первом синхровходе 9 блока 5 управления, в результате чего открывается элемент И 37, а также (при наличии на выходе 50 уровня 1) происходит увеличение адреса считьшания блока 6 памяти на единицу (выходы 48.1,..., 48.R). Очередной импульс на выходе 21 опорного генератора, поступающий на второй синхровход 19 блока 5 уп513744

р вления, проходит через элемент И 37 на выход 11 и производит запись кодов L и F, считанных из блока 6 памяти по предварительно сформированному адресу соответственно в селектор 7 частоты и счетчик 8. При этом на выходе 10 устанавливается нужный уровень, элемент И 37 закрьшается.

Работа канала 4 согласно приведен-ю ному описанию обеспечивается в случае, если К 7, 2. Целесообразно принять „5., f оп/2.

Для обеспечения плавного перекрытия диапазона программирования перио- да генерируемых импульсов должно выполняться соотношение:

foe,, Ki+1.

-оБ. 1-1-1

К,2 , s- 1, , L-1,

.Возможны следующие режимы работы канала,

1.Формирование импульсов с постоянным периодом. В этом случае после каждого переполнения счетчика 8 ин- крементация адреса считывания не происходит (на выходе 50 находится уровень О) и поэтому в селектор 7 частоты и в счетчик 8 перезаписываются одни и те же значения кодов L и F.

При этом на выходе 17 канала 4 фор- мируются импульсы с постоянным пе- риодом.

2.Динамическое изменение периода импульсов по заранее заданному -закону. В этом режиме после каждого переполнения счетчика 8 происходит инкре- Ментация адреса считывания, в результате чего изменяются значения кодов

L и F, перезаписываемые в селектор 7 частоты и в счетчик 8.

3.Программирование канала без пре рыва1шя генерирования импульсов. При этом в промежутках времени между моментами переполнения счетчика 8 производится запись нового набора кодов L и F в сегмент памяти блока 6 памя;- ти, доступньш по записи,

В нужный момент времени режимы работы сегментов взаимно изменяются и происходит быстрая смена программы

Описанные режимы работы канала, а также прием информации от ЭВМ в программном режиме обеспечиваются блоком 5 управления,

Разделение адресного пространства на два сегмента, один из которых доступен по записи, а другой - по считыванию, заключается в следующем.

7441

ю

25

30

35 40

- 45

. 50

55

36

Адрес ячейки памяти блока 6 памяти , определяется параллельным двоичным кодом а , а,...,ар, поступающим на вход адреса 13 блока 6 памяти. Общий объем адресного пространства блока 6 памяти, определяемый числом комбинаций значений всех разрядных коэффициентов а,,а2,.,.,а кода адреса

Если устанавливать значение О или 1) одного из разрядных коэффициентов (обозначим его а,-) независимо от остальных, то в адресном пространстве А выделится два непересекающихся адресных подпространства (сегмента) А объемом адресов каждое.

При формировании кода адреса считывания независимо от кода адреса записи таким образом, что значения а; в первом и втором кодах взаимно инверсны, один сегмент оказывается доступным в режиме записи, а другой - в режиме считывания. Изменение значения aj на обратное изменяет режимы использования сегментов.

Блок 5 управления (фиг, 2) работает следующим образом. Передача данных, адресов и команд управления от ЭВМ в генератор осуществляется в два такта и заключается в следующем, В первом такте ЭВМ передает на щину 23 управления и шину 24 данных устройства команды и адрес канала, которые поступают соответственно на управляющие входы 22 блока 5 управления и соединенные между собой входы данных 25 блока 5 управления и блока 6 памяти каждого канала,

В п-разрядном параллельном двоичном коде адреса канала, поступающем в первом такте от ЭВМ на вход 25 блока 5 управления, (п-1) первых разрядов содержат код номера канала, а оставшийся п-й разряд содержит код устройства (в адресованном канале), которому адресуются данные, передаваемые во втором такте. При значении п-го разряда, равном О, данные передаются блоку 6 памяти и имеют смысл кодов L и F, в противном случае данные поступают в регистры 35 и 36 и имеют смысл адреса ячейки памяти блока 6 памяти и команды управления. Во время первого такта (передается адрес внешнего устройства) ЭВМ на линии ВУ управляющего входа 22 блока 5 управления устанавливает высокий уровень, который разрешает

713

работу цифрового компаратора 28 в каждом канале 4. При этом происходит сравнение кода номера канала (первые (п-1) разрядов кода адреса внешнего устройства) с собственным номером канала, и в случае совпадения указанных кодов в каком-либо канале 4 на выходе цифрового компаратора 28 данного канала появляется уровень 1, который по переднему фронту сигнала СИА (см. фиг. 3) записывается в первый разряд первого регистра 29, во второй разряд которого записывается состояние п-го разряда кода ад- реса внешнего устройства (входы 44 и 45, фиг. 3). Таким образом, выбранный канал 4.j устанавливается в адресованное состояние (на входе 4 высокий уровень).

Во втором такте (передаются данные) на линии Вывод формируется высокий уровень, который разрешает работу дешифратора 31 в адресованном канале 4.J. При этом формируется iвысокий уровень на выходе 46 (при низком уровне на входе 45) или на выходе 47 (при высоком уровне на входе 45).

В первом случае импульс на выхо- де 46 переключает мультиплексоры 38 и 39 так, что на вькод 13 блока 5 управления подключаются выходы 49.1,...,49.(R-1) регистра 35, в котором хранится адрес записи блока 6 памяти, и выход 49.R регистра 35 или инверсное значение выхода 51 регистра 36 (в зависимости от состояния его выхода 52). Кроме того, импульс на выходе 46 (фиг. 3) вызывает формирование на выходе элемента 32 задержки задержанного импульса, который поступает на второй выход 12 блока 5 -управления и производит запись параллельного двоичного кода (s первых разрядов которого являются кодом F, а остальные log Е разряды - кодом поддиапазона L) установленного на входе данньпс 25 в блоке 6 памяти по адресу, который установлен на выходе 13 блока 5 управления. Этот же задержанный импульс устанавливает триггер 30 в единичное состояние, в результате чего на линии СИП устанавливается высокий уровень.

На выходе 47 высокий уровень формируется при установке на входе 25 данных блока 5 управления параллель

0

5

о

5

0

138

ного (г+3)-разрядного кода, первые г разрядов которого содержат код номера ячейки блока 6 памяти (адрес записи) , в которую требуется записать коды L и F, а оставшиеся три разряда - код команды. При этом (г+1)-й разряд определяет режим работы счетчика 34, соответственно О - хранение, 1 - инкремент адреса считывания блока 6 памяти при очередном переполнении счетчика 8; (г+2)-й разряд определяет режим использования объема блока 6 памяти соответственно О - односегментньш режим, 1 - два сегмента, доступные один по записи, другой по считыванию; (г+3)-и разряд определяет режим работы сегментов.

При формировании высокого уровня на выходе 47, происходит запись адреса блока 6 памяти и кода команды в соответствующие регистры 35 и 36. Одновременно триггер 30 устанавливается в единичное состояние, в результате чего на линии СИП формируется высокий уровень.

При наличии низкого уровня на выходе 46 (в том числе тот да, когда данный канал находится в неадресованном состоянии) мультиплексоры 38 и 39 переключены так, что на выход 13 блока 5 управления подключаются выходы 48.1,...,48.(R-1) счетчика 34, а также его выход 48.R или выход 52 регистра 36, в зависимости от уровня сигнала на линии 51.

По окончании второго такта передачи данных от ЭВМ на линии Вьшод устанавливается низкий уровень, в результате чего восстанавливается низкий уровень на выходе 46 (или на выходе 47) и на линии СИП адресованного канала. После этого может быть установлен высокий уровень на линии Сброс управляющего входа 22 блока 5 управления. Таким образом регистр 29 устанавливается в исходное состояние и после восстановления низкого уровня на линии Сброс генератор готов к приему информации от ЭВМ.

Формула изобретения

1. Многоканальный программируемый генератор импульсов, содержащий опорный генератор, выход которого соединен с первыми входами N-каналов фор-.

9137441

мирования импульсов, отличаюийся тем, что, с целью расширения функциональных возможностей, в него введены формирователь образцовой частоты и N/2 триггеров, при- чем выход генератора импульсов соединен с входом формирователя образцовой- частоты, выходы которого соединены с соответствующими вторыми вхо- п ами каналов формирования импульсов, и R-входытриггеров соединены с выходами соответствующих каналов формирования импульсов, третьи входы, ко-- торых соединены с шиной управления, , а четвертые входы - с шиной данных. 2. Генератор по п.1,отличающийся тем, что канал формирования импульсов содержит блок управления, блок памяти, селектор час- 2Q тоты, счетчик, причем первая группа выходов блока управления соединена с адресными входами блока памяти, первая группа выходов которого соединена с информационными входами счетчи- 25 ка, а вторая группа выходов - с адресными входами селектора частоты, выход которого соединен с тактовым входом счетчика, выход переполнения

которого соединен с первым синхровхо30

ом блока управления, второй выход которого соединен с входом записи блока памяти, синхровход счетчика объединен с входом записи селектора частоты и соединен с третьим входом блока управления, второй синхровход 35 которого является первым входом канаа, информационные входы селектора частоты являются вторым входом канала, входы данных блоков управления и памяти являются шиной данных канала,, а управляющие входы блока управления являются шиной управления канала, выход переполнения счетчика является

выходом канала.

45

3, Генератор по п. 1, о т л и- чающийся тем, что блок управления содержит цифровой компаратор, первый, второй, третий регистры, триггер,, дешифратор, элемент задержки, элемент ИЛИ, счетчик, элемент И, первьш, второй, мультиплексоры, шины О и 1, причем первый информационный вход первого регистра соединен с выходом цифрового компаратора, пер-55 вая группа входов которого является информационными входами блока управ

Q 5

0

5

5

5

310

ления, вторая группа входов цифрово- , го компаратора соединена с соответствующей линией шины 1, второй инфор- мационньш вход первого регистра соединен соответствующим образом с входом данных блока управления, первьй и второй синхровходы которого образо- ваны соответственно первым входом элемента И, подключенным к счетному входу счетчика, и вторым входом элемента И, выход которого является третьим выходом блока управления, второй выход которого образован соединенными между собой выходом элемента задержки и первьт входом элемента ИЛИ, выход которого соединен с С-вхо- дом триггера, инверсный R- и D-входы которого соединены соответственно с первым разрешающим входом дешифратора, и потенциалом 1, второй разрешающий и информационный входы дешифратора соединены соответственно с первьм и вторым выходами первого регистра, а первый и второй выходы дешифратора соединены соответственно с входом элемента задержки и вторым входом элемента ИЛИ, подключенным к соединенным между собой С-входам второго и третьего регистров, выходы младших разрядов счетчика и второго регистра соединены соответственно с первой и второй группами входов пер-, вого мультиплексора, адресньй вход которого соединен с первым адресным входом второго мультиплексора и соединен с первым выходом дешифратора, информационные входы второго и третьего регистров соединены соответствующим образом с входом данных блока управления, первый, в-торой и третий выходы третьего регистра соединены соответственно с входом разрешения . счетчика, вторым адресным и соеди- ненными между собой третьим и четвертым инвертирующим входами второго мультиплексора, первый и второй информационные .входы которого соединены с выходами старших разрядов соот- ветственно счетчика и второго регистра, первьш выход блока управления образован выходами первого и второго мультиплексоров, вход разрешения цифрового компаратора. С- и R-входы первого регистра, первый вход разрешения дешифратора, выход триггера являются управляющими входами блока управления.

(ры

Многаканольный apoifai tjfyfiinu te/f/xt/xcf uitnf/jrtcof

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1987 |

|

SU1453397A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

Изобретение может быть использовано в составе универсальных высокопроизводительных систем технической диагностики и способствует расширению функциональных возможностей устройства. Генератор импульсов содержит опорный генератор 1 и N каналов 4.-1,...,4.N формирования импульсов, каждый из которых включает блоки 5 и 6 управления и памяти, селектор 7 частоты и с четчик 8. Введение формирователя 2 образцовой частоты N/2 триггеров 3.1,...,3.N/2, а также предложенное выполнение блока 5 управления обеспечивают взаимно независимое формирование периода импульсов в каждом канале 4.1,...,4.N и изменение значения периода, длительности и задержки формируемых импульсов без прерывания их генерирования. Кроме того, в устройстве расширяется динамический диапазон значений периода импульсных последовательностей при сохранении разрядности управляющего слова. 2 з.п. ф-лы, 3 ил. о О)

| Многоканальный программируемый генератор импульсов | 1981 |

|

SU953703A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-15—Публикация

1986-07-02—Подача