00 о: 65 со а

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Преобразователь активной мощности в цифровой код | 1987 |

|

SU1451615A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Цифровой вольтметр среднеквадратического значения переменного напряжения | 1988 |

|

SU1652933A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1647893A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Преобразователь активной мощности в цифровой код | 1987 |

|

SU1471143A2 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

Изобретение относится к цифровой электроизмерительной технике и служит для повышения точности преобразования. Устройство содержит калиб- рованньм резистор 1, фиксатор 2 уровня, аналоговый коммутатор 4, преобразователь 5 напряжения в цифровой код, регистр 6, сумматор 12, формирователь 16 импульсов, генератор 17 опорной частоты, счетчик 18 и элемент 20 задержки. В преобразователь введены источник 3 опорного напряжения, регистры 7-11, умножитель 13, блоки 14 и 15 памяти, счетчик 19, элемент И 21 и формирователь 22 управляющих сигналов и образованы новые функциональные связи. 2 ил. S (Л

Cpue.i

Изобретение относится к цифровой электроизмерительной технике и предназначено для преобразования активной мощности (энергии) в цифровой код.

Цель изобретения - повьшение точности преобразования.

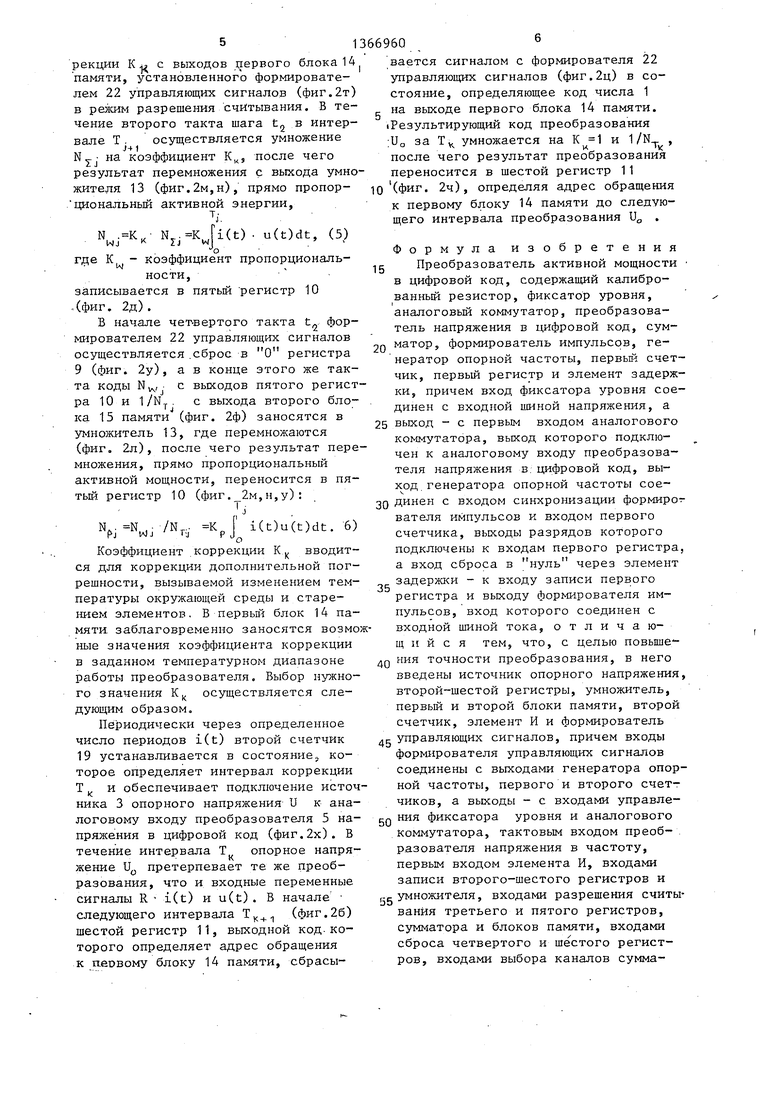

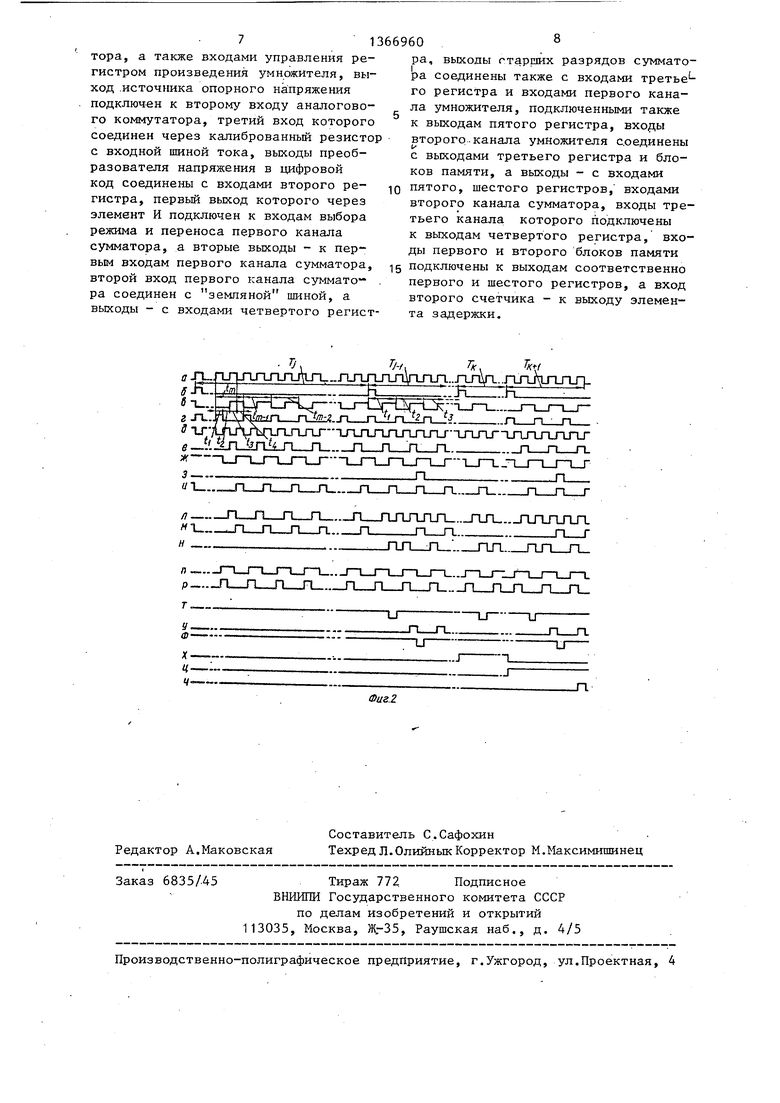

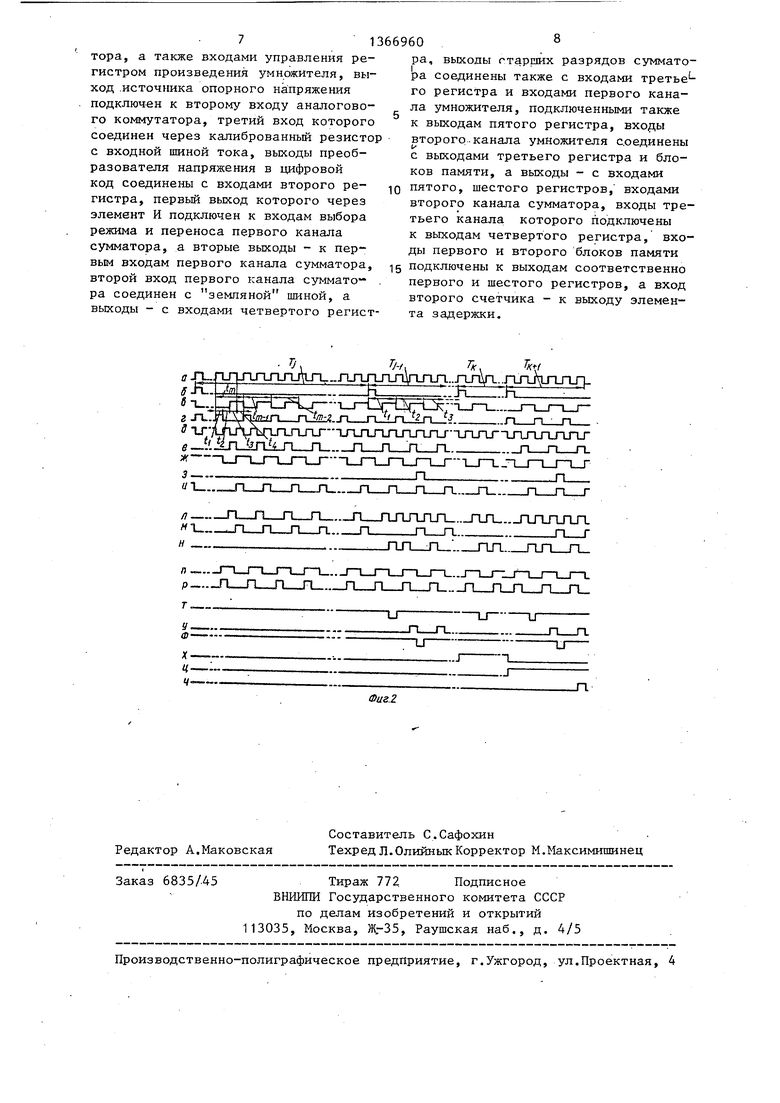

На фиг. 1 представлена схема преобразователя активной мощности в цифровой код; на фиг. 2 - временные диаграммы, поясняющие его работу.

Преобразователь активной мощности в цифровой код содержит калиброванный резистор 1, фиксатор 2 уровня, источник 3 опорного напряжения, аналоговый коммутатор 4, преобразователь 5 напряжения в цифровой код, первый - шестой регистры 6 -11, сумматор 12, умножитель 13, первый 14 и второй 15 блоки памяти, фop цipo- ватель 16 импульсов, генератор 17 опорной частоты, первьй 18 и второй 19 счетчики, элемент 20 задержки, элемент И.21 и формирователь 22 управляющих сигналов, причем первьй вход фиксатора 2 уровня соединен с входной ишной напряжения, а выход- с первым входом аналогового коммутатора 4, второй вход которого подключен через калиброванный резистор 1 к входной шине тока и входу формирователя 15 импульсов, третий вход - к выходу источника 3 опорного напряжения,, а выход - к аналоговому входу 35 цифровой код работает следующим преобразователя 5 напряжения в цифро- образом.

вой код; выход генератора 17 опорной Формирователь 16 импульсов выде- .частоты соединен с входом синхрони- ляет периоды Tj колебаний входного зации формирователя 16 импульсов и с входом первого счетчика 18, выходы разрядов которого подключен к входам первого регистра 6, вход сброса - к входу второго счетчика 19 и через

тока i(t), определяющие интервалы (0 преобразования, и в начале каждого текущего периода (фиг.26) формирует

элемент 20 задержки - к выходу запи-

импульс, синхронизированный с импуль- сом опорной последовательности с выхода генератора 17 опорной частоты си первого регистра 6 и выходу форми- 45 ( 2а), производящий по своему рователя 16 импульсов. Входы форми- . переднему фронту перенос кода из пер- рователя 22 управляющих сигналов соединены с выходами генератора 17 опорной частоты и первого 18 и второго

50

вого счетчика 18 в первьй регистр 6, а через время, определяемое элемен-- том 20 задержки, сброс первого счет19 счетчиков, а выходы - с входами управления фиксатора 2 уровня и аналогового коммутатора 4, тактовым входом преобразователя 5 напряжения в цифровой код, первым входом первого элемента И 21, входами записи второго- шестого регистров 7-11 и умножителя 13, входами разрешения считывания третьего 8 и пятого 10 регистров, сумматора 12 и первого 14,

чика 18 в нуль. В течение очередного периода Т: счетчик 18 произво дит подсчет числа импульсов опорной частоты следования „ с выхода генератора 17 опорной частоты: S5 NT. f Т ,

Ij о J

(1)

код которого в начале следующего периода T,j; переносится в первьй регистр 6. Выходной код первого регистра 6

второго 15 блоков памяти, входами сброса регистров 9,11, входами выбора каналов сумматора 12, а также входами управления регистром произведения умножителя 13. Выходы преобразователя 5 напряжения в цифровой код соединены с входами второго регистра 7, первый выход которого через

элемент И 21 подключен к входам выбора режима и переноса первого канала сумматора 12, а вторые входы - к первым входам первого канала сумматора 12, второй вход первого канала

сумматора 12 соединен с земпяной шиной, а выходы с входами четвертого регистра 9. Выходы старших разрядов сумматора 12 соединены также с входами третьего регистра 8 и входами первого канала умножителя 13, подключенными также к выходам пятого регистра .10, входы второго накала умножителя 13 соединены с выходами третьего регистра 8, первого 14 и

второго 15 блоков памяти, а выходы - с входами пятого 10, шестого 11 регистров и входами второго ка нала сумматора 12, входы третьего канала которого подключены к выходам

четвертого регистра 9, входы блоков 14 и 15 памяти подключены к выходам соответственно первого 6 и шестого 11 .регистров.

Преобразователь активной мощности

Формирователь 16 импульсов выде- ляет периоды Tj колебаний входного

тока i(t), определяющие интервалы преобразования, и в начале каждого текущего периода (фиг.26) формирует

импульс, синхронизированный с импуль- сом опорной последовательности с выхода генератора 17 опорной частоты ( 2а), производящий по своему переднему фронту перенос кода из пер-

вого счетчика 18 в первьй регистр 6, а через время, определяемое элемен-- том 20 задержки, сброс первого счетчика 18 в нуль. В течение очередного периода Т: счетчик 18 произво дит подсчет числа импульсов опорной частоты следования „ с выхода генератора 17 опорной частоты: S5 NT. f Т ,

Ij о J

(1)

код которого в начале следующего периода T,j; переносится в первьй регистр 6. Выходной код первого регистра 6

является адресным для второго блока 15 памяти, где по адресу N. записан код числа N-j-. .

Период t работы младшего разряда первого счетчика 18 (фиг. 2в) определяет шаг дискретизации входных сигналов и разделен на четыре такта

-Ъ -i первом такте1 очередного шага дискретизации t (фиг.2в) значение падения напряжения R « i. на калиброванном резисторе 1, прямо пропорциональное значению 1, входного тока в текущей точке m периода Tj, и значение входного напряжения и ,в этой же точке поступают через аналоговый коммутатор 4- соответственно на вход преобразователя 5 напряжения в цифровой код и на вход фиксатора 2 уровня, устанавливаемьпс формирователем 22 управляющих сигналов в режим выборки сигнала (фиг.2г, д), где фиксируются. Во втором такте Vj шага t преобразователь 5 напряжения в цифровой код устанавливается формирователем 22 управляющих сигналов в режим хранения (фиг.2д) и преобразует напряжение R цифровой прямой код переносимый по окончании Т,2 передним фронтом сигнала с выхода генератора 17 опорной частоты (фиг.2а) во второй регистр 7.

N.

К.

(2)

im Ti где - коэффициент пропорциональности.

В третьем такте t, шага 1|(фиг.2в аналоговый коммутатор 4, управляемый формирователем 22 управляющих сигналов (фиг. 2е) , подключает к входу преобразователя 5 напряжения в цифровой код напряжение U с выхода фиксатора 2 уровня, а сумматор 12 производит преобразование прямого кода N в дополнительньй. При этом сумматор 12 установлен в состояние выборки первого канала и разрешения считывания (фиг. 2ж,з), а на входы выбора режима и переноса этого канала при инверсном значении N поступает 1 знака этого числа, определяющая инвертирование кода сумматора и прибавление к результату инвертирования единицы. В конце результат преобразования (фиг.2и) переносится в третий регистр 8. При положитель- .ном значении N его код остается без изменения, так как прямой и

дополнительный коды положительного числа совпадают.

В четвертом такте t шага t преобразователь 5 напряжения в цифровой код преобразует напряжение цифровой прямой код числа N (фиг.2д):

К

U

Ц

ni

(3)

0

5

0

5

0

где KI - коэффициент пропорциональности,

который по окончании преобразования переносится во второй регистр 7 (фиг.2а), а во втором такте сле- g дующего шага дискретизации t, преобразуется сумматором 12 в дополнительньй код (фиг. 2в,ж,з). В концеTg

коды чисел N.

и N,:соответственно

с выходов сумматора 12 и третьего

р регистра 8, находящихся в состоянии разрешения считывания (фиг. 2з,ж), записываются сигналом с выхода формирователя 22 управляющих сигналов (фиг. 2л) в умножитель 13, где в те5 чение следующего такта с (фиг. 2в) перемножаются, после чего результат перемножения (фиг. 2м,н) заносится в регистр произведения. В первом такте шага дискретизации t,,JKOД произведения N N,, с выхода умноI ГТЧ о Ьгл

жителя 13 подается на входы третьего канала сумматора 12, установленного в состояние выборки второго и третьего каналов (фиг.2п), где прибавляется к сумме результатов перемножения значений входных сигналов за (т-1) предшествующие точки дискретизации в текущем интервале преобра-Зования Т; с выходов четвертого регистра 9, после чего результат суммирования (фиг. 2р) заносится в четвертый регистр 9. Такой обработке подвергаются значения входных сигналов-всех точек дискретизации за интервал Т

J за исключением того, что результат

перемножения кодов входных сигналов для последней точки дискретизации за Т- не записывается в регистр Произведения умножителя 13, а непосредственно в четвертом такте шага дискретизации t., интервала преобразования Т ;, , складывается сумматоJ -т- Т

ром 12 с выходным кодом четвертого регистра 9 (фиг.2б,в,н,м,п), после

чего результирующий код 1L J

1и

: f

N;

N,

(4)

..,,

переносится в умножитель 13(фиг.2з,л)

одновременно с кодом коэффициента коррекции К с выходов цервого блока 14 памяти, установленного формирователем 22 управляющих сигналов (фиг.2т) в режим разрешения считывания. В течение второго такта шага t в интер- (Результирующий код преобразова ния

:Uo за TV умножается на К 1 и 1/N

вале Т , осуществляется умножение NJ-J на коэффициент К, после чего результат перемножения с выхода умножителя 13 (фиг.2м,н), прямо пропор- циональный активной энергии.

после чего результат преобразовани переносится в шестой регистр 11 10 (фиг. 2ч), определяя адрес обращен к первому блоку 14 памяти до следу щего интервала преобразования и

N

IJ

J .

(t) . u(t)dt, (5;

ь гл

где К - Коэффициент пропорциональности,

записывается в пятьй регистр 10 .(фиг. 2д).

В начале чет-вертсзго такта t. формирователем 22 управляющих сигналов осуществляется .сброс в О регистра 9 (фиг. 2у), а в конце этого же такта коды N , с выходов пятого регистра 10 и 1/N. с выхода второго блока 15 памяти (фиг. 2ф) заносятся в умножитель 13, где перемножаются (фиг. 2л), после чего результат перемножения, прямо пропорциональный активной мощности, переносится в пятый регистр 10 (фиг.2м,н,у):

I

NN N.

T-J

/NT-,. к„ i(t)u(t)dt. 6)

Коэффициент коррекции К вводится для коррекции дополнительной погрешности, вызываемой изменением температуры окружающей среды и старением элементов. В первьм блок 14 памяти, заблаговременно заносятся возмоные значения коэффициента коррекции в заданном температурном диапазоне работы преобразователя. Выбор нужного значения К, осуществляется следующим образом.

Периодически через определенное число периодов i(t) второй счетчик 19 устанавливается в состояние,, которое определяет интервал коррекции и обеспечивает подключение источ3 опорного напряжения U к аналоговому входу преобразователя 5 напряжения в цифровой код (фиг.2х). В течение интервала Т опорное напряжение Uy претерпевает те же преобразования, что и входные переменные сигналы R i(t) и u(t). В начале следующего интервала Т (фиг.26) шестой регистр 11, выходной код.которого определяет адрес обращения к пеовому блоку 14 памяти, сбрасыTKника

вается сигналом с формирователя 22 управляющих сигналов (фиг.2ц) в состояние, определяющее код числа 1 на выходе первого блока 14 памяти.

:Uo за TV умножается на К 1 и 1/N

после чего результат преобразования переносится в шестой регистр 11 10 (фиг. 2ч), определяя адрес обращения к первому блоку 14 памяти до следующего интервала преобразования и .

15

20

Формула изобретения

Преобразователь активной мощности Б цифровой код, содержащий калиброванный резистор, фиксатор уровня, аналоговый коммутатор, преобразователь напряжения в цифровой код, сумматор, формирователь импульсов, генератор опорной частоты, первьй счетчик, первый регистр и элемент задержки, причем вход фиксатора уровня соединен с входной шиной напряжения, а

25 выход - с первым входом аналогового коммутатора, выход которого подключен к аналоговому входу преобразователя напряжения в:цифровой код, выход генератора опорной частоты сое30 динен с входом синхронизации формирог вателя импульсов к входом первого счетчика, выходы разрядов которого подключены к входам первого регистра, а вход сброса в нуль через элемент задержки - к входу записи первого регистра и выходу формирователя импульсов, вход которого соединен с входной шиной Тока, о т л и ч а ю35

40

имя точности преобразования, в него введены источник опорного напряжения второй-шестой регистры, умножитель, первый и второй блоки памяти, второй счетчик, элемент И и формирователь g управляющих сигналов, причем входы формирователя управляющих сигналов соединены с выходами генератора опорной частоты, первого и второго счетчиков, а выходы - с входами управле50

ния фиксатора уровня и аналогового

Коммутатора, тактовым входом преобразователя напряжения в частоту, первым входом элемента И, входами записи второго-шестого регистров и ,-g умножителя, входами разрешения считвания третьего и пятого регистров, сумматора и блоков памяти, входами сброса четвертого и шестого регистров, входами выбора каналов сумма7

тора, а также входами управления регистром произведения умножителя, выход .источника опорного напряжения подключен к второму входу аналогового коммутатора, третий вход которог соединен через калиброванньш резист с входной шиной тока, выходы преобразователя напряжения в цифровой код соединены с входами второго регистра, первый выход которого через элемент И подключен к входам выбора режима и переноса первого канала сумматора, а вторые выходы - к первым входам первого канала сумматора второй вход первого канала суммато - ра соединен с земляной шиной, а выходы - с входами четвертого регис

Jn-rlJyгпJ JTJ ln „ЛJ JpглV

-п-пллллги1..п гитпл.

т.

tf

ф-::.

у

«««.«

8

ра, выходы гтариих разрядов сумматоI ;

ра соединены также с входами третье - го регистра и входами первого канала умножителя, подключенными также к выходам пятого регистра, входы второго.канала умножителя соединены с выходами третьего регистра и блоков памяти, а выходы - с входами пятого, шестого регистров, входами второго канала сумматора, входы третьего канала которого подключены к выходам четвертого регистра, входы первого и второго блоков памяти 15 подключены к выходам соответственно первого и шестого регистров, а вход второго счетчика - к выходу элемента задержки.

| ПРЕОБРАЗОВАТЕЛЬ АКТИВНОЙ МОЩНОСТИ В ЦИФРОВОЙ КОД | 1967 |

|

SU223459A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-01-15—Публикация

1986-04-03—Подача