VI с о

...k

00

о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1982 |

|

SU1184105A1 |

| Формирователь линейно изменяющегося напряжения | 1986 |

|

SU1387180A1 |

| Устройство для измерения внутреннего угла синхронной машины | 1984 |

|

SU1226331A1 |

| Устройство для разгона и торможения двигателя исполнительного механизма | 1986 |

|

SU1361507A1 |

| Генератор синусоидального сигнала | 1986 |

|

SU1410065A1 |

| Программно-управляемый модуль | 1986 |

|

SU1327060A1 |

| Управляемый умножитель частоты следования импульсов | 1982 |

|

SU1034145A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Устройство для интегрирования частотно-импульсных сигналов | 1984 |

|

SU1160444A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU525235A1 |

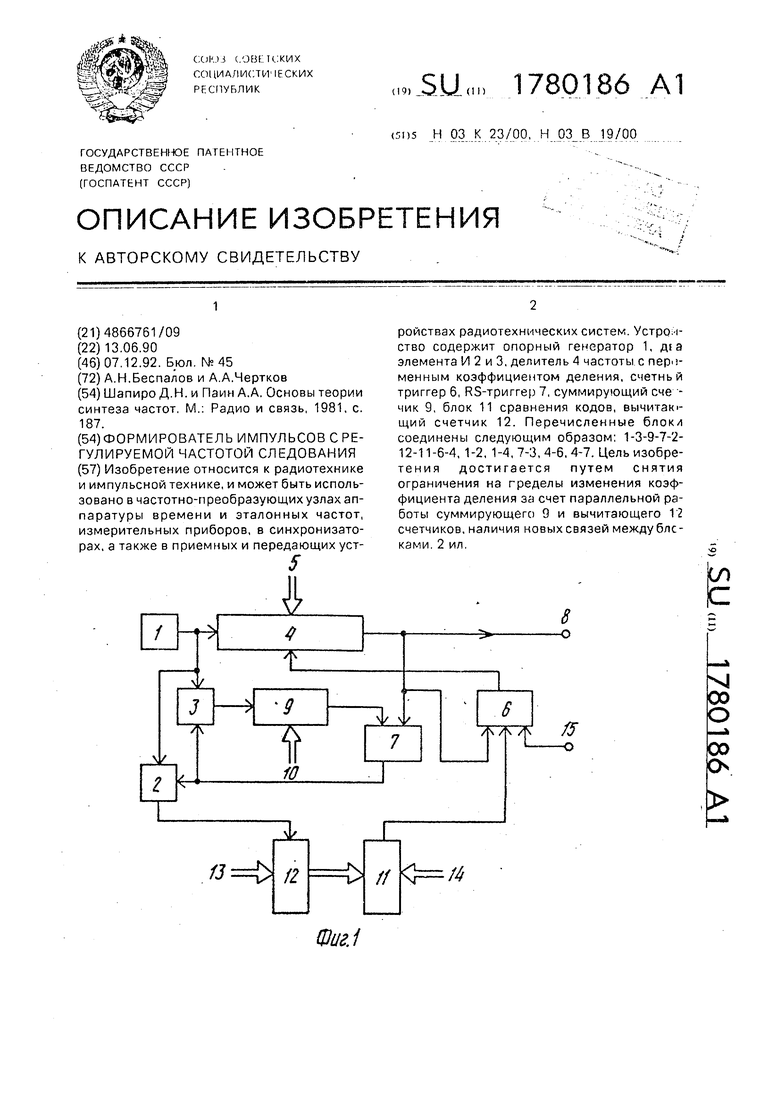

Изобретение относится к радиотехнике и импульсной технике, и может быть использовано в частотно-преобразующих узлах аппаратуры времени и эталонных частот, измерительных приборов, в синхронизаторах, а также в приемных и передающих устройствах радиотехнических систем. Устройство содержит опорный генератор 1, Д(а элемента И 2 и 3, делитель 4 частоты с nep'S- менным коэффициентом деления, счетньй триггер 6, RS-триггер 7. суммирующий сче '- чик 9, блок 11 сравнения кодов, вычитак'- щий счетчик 12. Перечисленные блоки соединены следующим образом; 1-3-9-7-2- 12-11-6-4, 1-2, 1-4, 7-3, 4-6,4-7. Цель изобретения достигается путем снятия ограничения на пределы изменения коэффициента деления за счет параллельной работы суммирующего 9 и вычитающего ^2 счетчиков, наличия новых связей между блоками. 2 ил.V1слс

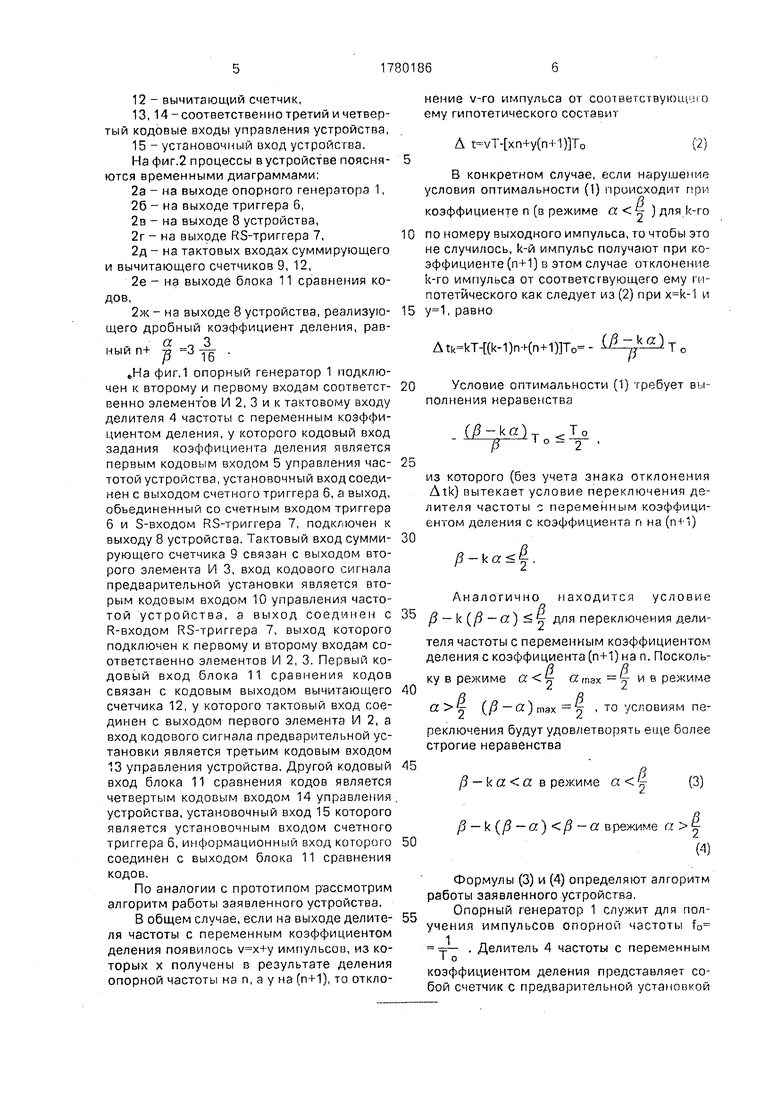

i/e.f Предлагаемое изобретение относится к импульсной технике и может быть использовано в частотно-преобразующих узлах аппаратуры времени и эталонных частот, измерительных приборов, в синхронизаторах, а также в приемных и передающих устройствах радиотехнических систем. Известно устройство, которое содержит делитель частоты с переменным коэффициентом деления, генератор случайных чисел, блок сравнения кодов, триггер, два элемента И и делитель частоты. Недостатком устройства является низкая фазовая стабильность выходных импульсов, обусловленная неоптимальным алгоритмом дробного преобразования опорной частоты, который приводит к формированию выходной импульсной последовательностисмаксимальнойнеравномерностью. Наиболее близким по технической сущности является устройство, которое состоит из опорного генератора, делителя частоты с переменным коэффициентом деления, трех счетчиков (сложения, вычитания и реверсивного), семи элементов И, двух триггеров, двух элементов ИЛИ и одного инвентора. Сущность заключается в минимизации неравномерности выходной импульсной последовательности путем такого чередования интервалов деления опорной частоты напили(п+1), при котором выполняется условие оптимальности; отклонение А t выходного импульса, от соответствующего ему гипотетического (с периодом Т(п+ -73 ),То где То - период опорной частоты, п, сг , /3соответственно целая часть, числитель и знаменатель дробного коэффициента деления. Недостатком прототип.а является наличие ограничения п(/ -а ) на пределы изменения целой, части дробного коэффициента деления, что сужает диапазон изменения частоты следования импульсов и уменьшает быстродействие устройства. Целью изобретения является расширение диапазона изменения частоты следования импульсов и повышение быстродействия устройства. Предлагается формирователь импульсов с регулируемой частотой следоЕ ания, содержащий последовательно соединенные опорный генератор, делитель частоты с переменным коэффициентом деления и триггер, последовательно соединенные RSтриггер, первый элемент И и вычитающий счетчик, суммируюа ий счетчик, тактовый вход которого подключен к выходу второго элемента И, при этом выход опорного генератора соединен с другим входом первого элемента И и первым входом второго элемента И, а кодовый вход задания коэффмциента деления делителя частоты с переменным коэффициентом деления является первым кодовым входом управления частотой формирователя импульсов с регулируемой частотой следования, вторым кодовым входом управления частотой которого является вход кодового сигнала предварительной установки суммирующего счетчика. Указанная цель достигается тем. что в устройство введен блок сравнения кодов, первый кодовый вход которого соединен с кодовым выходом вычитающего счетчика, при этом выход суммирующего счетчика соединен с R-входом RS-триггера, выход которого соединен с другим входом второго элемента И, а выход счетного триггера соединен с установочным входом делителя честоты с переменным коэффициентом деления, выход которого соединен с S-вхсдом RS-триггера, выход блока сравнения кс дов соединен с информационным входом триггера, установочный вход которого является установочным входом формирователя последовательности импульсов с регулируемой частотой следования, выходом которого является выход делителя частоты с переменным коэффициентом деления, при этом вход кодового сигнала предварительной установки вычитающего счетчика и другой кодовый вход блока сравнения кодом являются соответственно третьим и четвертым кодовыми входами управления формирователя последовательности импульсов с регулируемой частотой следования, Реализация устройства поясняется на фиг.1, где I- опорный генератор, 2,3- соответственно первый и второй элементы И, 4 - делитель частоты с переменным коэффициентом деления, 5- первый кодовый вход управления частотой устройства, 6- счетный триггер, 7 - RS-триггер, 8- выход устройства, 9- суммирующий счетчик, 10- второй кодовый вход управления частотой устройства, I1- блок сравнения кодов.

кода коэффициента деления. При низком и высоком потенциалах на его установочном входе он срабатывает с коэффициентом пересчета соответственно п и (п+1). Счетный триггер 6 реализуется на основе тактируемого JK- или D-триггеров, в которых информационнымвходбмявляетсясоответственно J- или D-входы, Использование в нем третьего входа (начальной установки) позволяет установить требуемый

режим работы устройства ( или

а ) в зависимости от его исходного

состояния. В первом случае он устанавливается в единичное состояние, во втором случае - в нулевое состояние. Триггер 7 представляет собой обычный асинхронный RS-триггер, Суммирующий счетчик 9 также является счетчиком с предварительной установкой кода коэффициента деления. Он служит для подсчета а или(у9-а) импульсов входной частоты в режимах соответственно с или (2 . Если

счетчикЭ имеет емкость /3 , то коэффициент пересчета, равный а , реализуется путем подачи на его вход кодового сигнала предварительной установки дополнительного кода (инвентированный + дв.ед. в младшем разряде) числителя дробной части коэффициента деления. Коэффициент пересчета (/9- а) реализуется при подаче на его вход кодового сигнала предварительной установки прямого кода числителя дробной части коэффициента деления, так как его емкость в этом случае станет равной ()8 - а) . Указанные режимы работы счетчика 9 являются известными и подробных .пояснений не требуют. Вычитающий счетчик 12 служит для формирования разности (3) или (4). Он представляет собой реверсивный счетчик с предварительной установкой кода знаменателя , работающий в режиме вычитания содержимого на единицу по приходу опорного импульса. Запись числа в счетчик 12 производится по сигналу обнуления, поступающему с выхода обратный перенос (вывод 13 микросхемы 155ИЕ6) на его вход разрешения записи (вывод 11 микросхемы 155ИЕ6). Эта связь является внутренней, поэтому на фиг;1 она не показана.

Блок 11 сравнения кодов служит для проверки условий (3) или (4). Согласно этим условиям, на его второй кодовый вход подается код а или (/3-а) в режимах соота . При

ветственно cf или выполнении условий (3) или (4) на его выходе

появляется высокий потенциал, в противном случае - низкий потенциал.

Поясним работу устройства в режиме

а с исходного состояния, в котором:

в управляемый делитель 4 частоты, счетчики 9 и 12 и блок 11 сравнения кодов занесены коды установки соответственно с входов 5, 10, 13 и 14 управления устройства;

триггеры 6 и 7 находятся соответственно в единичном и нулевом состояниях.

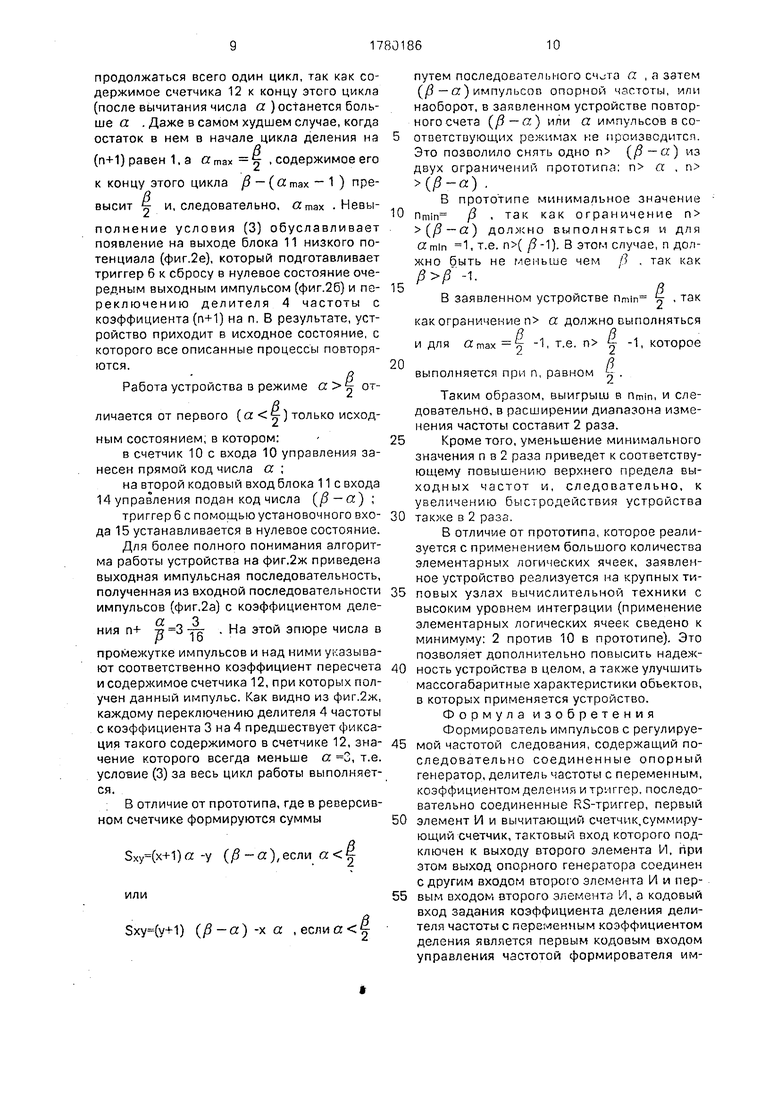

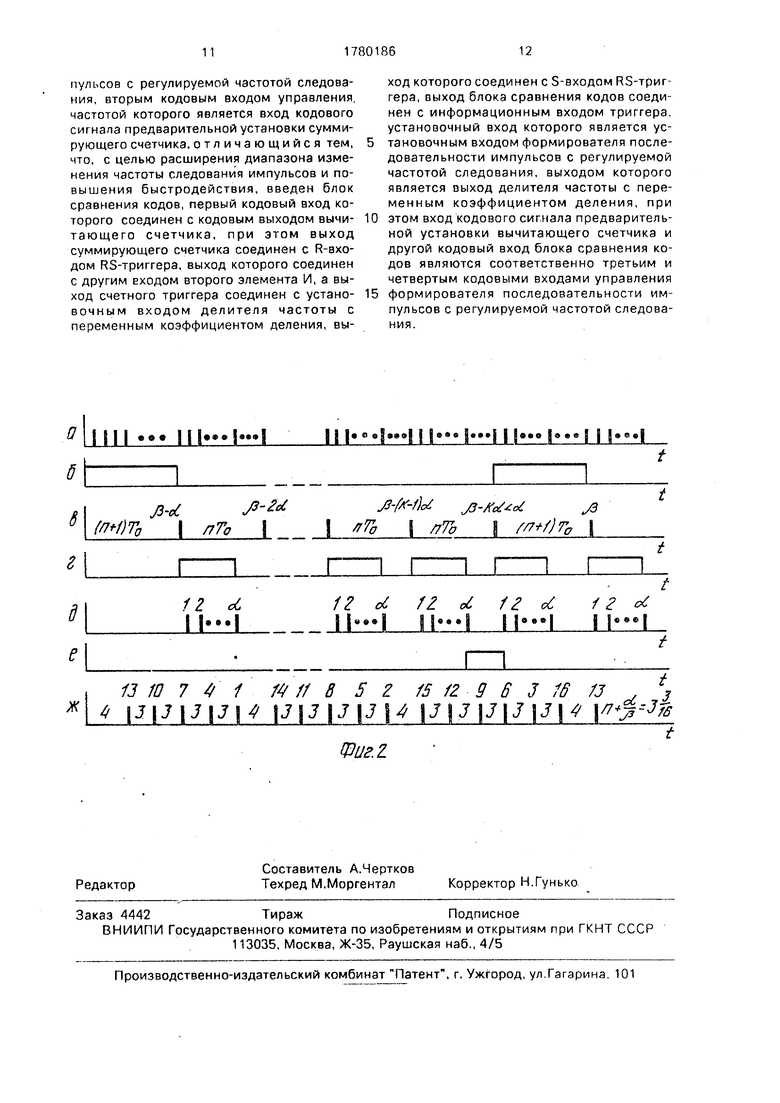

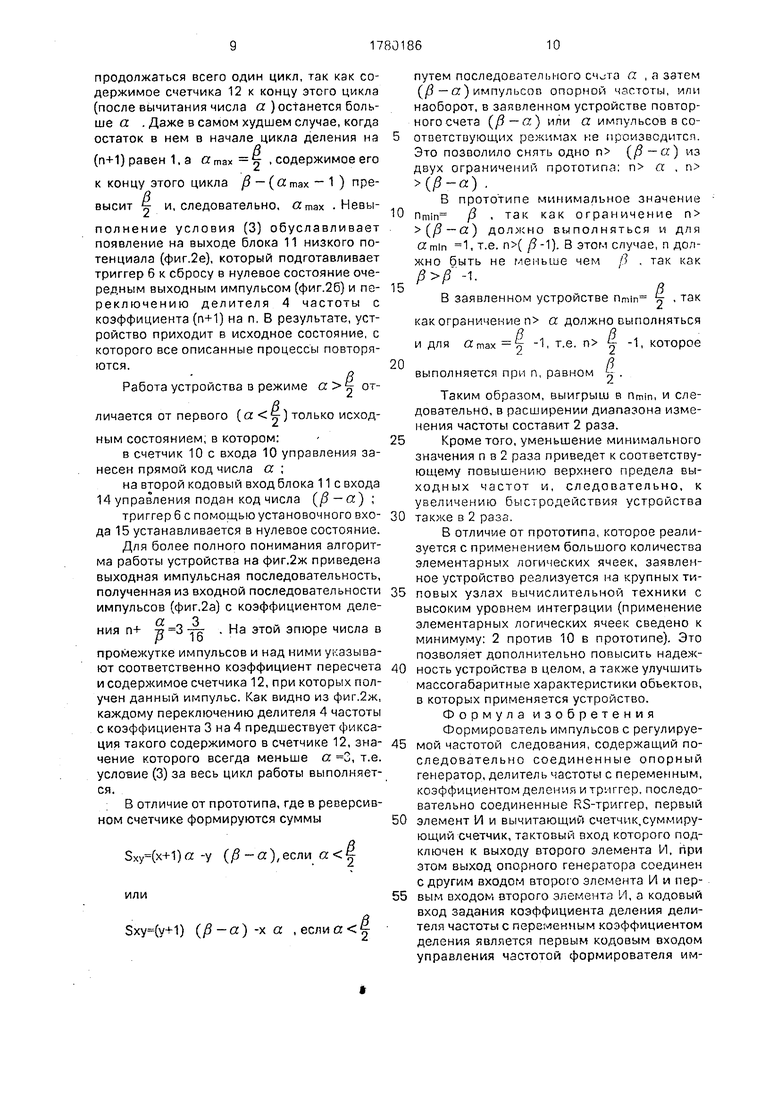

После запуска устройства на тактовый вход управляемого делителя 4 частоты поступают входные импульсы (фиг.2а) отопорного генератора 1. Высокий потенциал на установочном входе делителя 4 частоты (фиг.2б) вынуждает его срабатывать с коэффициентом (п+1) (фиг.2в). Первым выходным импульсом устройства триггер 6 сбрасывается, а триггер 7 устанавливается в единичное состояние (фиг.26, г) и разрешает прохождение опорных импульсов на входы счетчиков 9 и 12 (фиг.2д). При этом содержимое счетчика 12 с каждым входным импульсом уменьшается на единицу. После поступления на счетчик 9 а импульсов он переполняется и своим выходным импульсом сбрасывает триггер 7 в нулевое состояние (фиг.2г, д), запрещая прохождение

импульсов на входы счетчиков 9 и 12. В счетчике 12 фиксируется содержимое, равное (/3 - а ) которое сравнивается в блоке 11с а . Если (/3-a)ci; ,то при поступлении на выход устройства очередного импульса коэффициент пересчета делителя 4 частоты не изменится и процессы в устройстве повторяются. Повторение циклов формирования выходных импульсов с интервалом пТо (фиг.2в) будет происходить

до тех пор, пока содержимое счетчика 12 не станет меньше а . В этом случае появление высокого потенциала на выходе блока 11 (фиг.2е) подготавливает триггер 6 к установке в единичное состояние очередным

выходным импульсом устройства (фиг.2в, б). С поступлением очередного импульса на выход устройства в делителях 4 частоты устанавливается коэффициент деления (п+1) и тактовые импульсы,, поступающие на счетчик 12, считывают остаток в нем до полного его обнуления. Тогда сигналом обнуления счетчика 12, поступающего с выхода обратный перенос на его вход разрешения записи, в него заносится код числа j3 .

Оставшимися из о: в пачке тактовыми импульсами производится вновь считывание содержимого счетчика 12. но теперь со значения /3 . Работа делителя 4 частоты с коэффициентом пересчета (п+1) будет

12 - вычитающий счетчик,

13,14-соответственно третий и четвертый кодовые входы управления устройства,

15 - установочный оход устройства.

На фиг.2 процессы в устройстве поясняются временными диаграммами;

2а - на выходе опорного генератора 1,

26 - на выходе триггера 6,

2а - на выходе 8 устройства,

2г - на выходе RS-триггера 7,

2д - на тактовых входах суммирующего и вычитающего счетчиков 9, 12,

2е - на выходе блока 11 сравнения кодов,

2ж - на выходе 8 устройства, реализующего дробный коэффициент деления, равный п+ -о 3 -х-р .

На фиг.1 опорный генератор 1 подключен к второму и первому входам соответственно элементов И 2, 3 и к тактовому входу делителя 4 частоты с переменным коэффициентом деления, у которого кодовый вход задания коэффициента деления является первым кодовым входом 5 управления частотой устройства, установочный вход соединен с выходом счетного триггера 6, а выход, объединенный со счетным входом триггера 6 и S-входом RS-триггера 7, подключен к выходу 8 устройства. Тактовый вход суммирующего счетчика 9 связан с выходом второго элемента И 3, вход кодового сигнала предварительной установки является вторым кодовым входом 10 управления частотой устройства, а выход соединен с R-входом RS-триггера 7, выход которого подключен к первому и второму входам соответственно элементов И 2, 3. Первый кодовый вход блока 11 сравнения кодов связан с кодовым выходом вычитающего счетчика 12, у которого тактовый вход соединен с выходом первого элемента И 2, а вход кодового сигнала предварительной установки является третьим кодовым входом 13 управления устройства. Другой кодовый вход блока 11 сравнения кодов является четвертым кодовым входом 14 управления . устройства, установочный вход 15 которого является установочным входом счетного триггера б, информационный вход которого соединен с выходом блока 11 сравнения кодов.

По аналогии с прототипом рассмотрим алгоритм работы заявленного устройства.

В общем случае, если на выходе делителя частоты с переменным коэффициентом деления появилось импульсов, из которых X получены в результате деления опорной частоты на п, а у на (п+1), то отклонение v-ro импульса от соответствующло ему гипотетического составит

Л (n+1)To

(2)

В конкретном случае, если нарушение условия оптимальности (1) происходит при

коэффициенте п (в режиме а ) для k-го

по номеру выходного импульса, то чтобы это не случилось, k-й импульс получают при коэффициенте (п+1) в этом случае отклонение k-го импульса от соответствующего ему гипотетического как следует из (2) при и

, равно

(k-1)n-Kn+1)

Условие оптимальности (1) требует выполнения неравенства

(/g-ka) То

i ,

из которого (без учета знака отклонения Atk) вытекает условие переключения делителя частоты с переменным коэффициентом деления с коэффициента п на (n-t-l)

/3-ka |.

Аналогично находится условие /5 - k (/5 - а) 4- для переключения делителя частоты с переменным коэффициентом деления с коэффициента (п+1) на п. Поскольку в режиме «max n и в режиме

иfi

(/5 - ct) max - о- . ТО условиям переключения будут удовлетворять еще более строгие неравенства

45

/3 - k а а в режиме а t(3)

/3-k(-a)y5-a врежиме а

50

(

Формулы (3) и (4) определяют алгоритм работы заявленного устройства. Опорный генератор 1 служит для получения импульсов опорной частоты fo

т;- . Делитель 4 частоты с переменным

I о

коэффициентом деления представляет собой счетчик с предварительной установкой

продолжаться всего один цикл, так как содержимое счетчика 12 к концу этого цикла (после вычитания числа а. ) octaнeтcя больше а . Даже в самом худшем случае, когда остаток в нем в начале цикла деления на

(п+1) равен 1, а а max 2 . содержимое его к концу этого цикла /5 - ( а max - 1 ) превысит t и, следовательно, ctmax .Невыполнение условия (3) обуславливает появление на выходе блока 11 низкого потенциала (фиг.2е), который подготавливает триггер 6 к сбросу в нулевое состояние очередным выходным импульсом (фиг.2б) и переключению делителя 4 частоты с коэффициента (п+1) на п, В результате, устройство приходит в исходное состояние, с которого все описанные процессы повторяются.

Работа устройства в режиме от ё

личается от первого (

только исходным состоянием; в котором:

в счетчик 10 с входа 10 управления занесен прямой код числа а ;

на второй кодовый вход блока 11 с входа 14 управления подан код числа (/3-а);

триггер 6 с помощью установочного входа 15 устанавливается в нулевое состояние.

Для более полного понимания алгоритма работы устройства на фиг.2ж приведена выходная импульсная последовательность, полученная из входной последовательности импульсов (фиг.2а) с коэффициентом деле« о 3

На этой эпюре числа в

ния п+

промежутке импульсов и над ними указывают соответственно коэффициент пересчета и содержимое счетчика 12, при которых получен данный импульс. Как видно из фиг.2ж, каждому переключению делителя 4 частоты с коэффициента 3 на 4 предшествует фиксация такого содержимого в счетчике 12, значение которого всегда меньше о. 3, т.е. условие (3) за весь цикл работы выполняется.

В отличие от прототипа,где в реверсивном счетчике формируются суммы

Sxy(x+)« -у (JS-G:),ecли «

или

Sxy(y+1) (/3-а)-X а ,еслиа §

путем последовательного а , а затем (у8 - с;) импульсов опорной частоты, или наоборот, в заявленном устройстве повторного счета (/З - а ) или а импульсов в соответстоующих режимах не производитсл. Это позволило снять одно п (S-а) из двух ограничений прототипа: п а , п (-а).

В прототипе минимальное значение Пт1п /3 , так как ограничение п (/3-а) должно выполняться и для 1, т.е. п( /9-1). В этом случае, п должно б.ыть не Mei-ibLue чем в , так как -1.

В

В заявленном устройстве Пт1п %- , так

как ограничение п а должно выполняться и для «max -1, Т.е. п -1, которое

/

выполняется при п, равном .

Таким образом, выигрыш в Птт, и следовательно, в расширении диапазона изменения частоты составит 2 раза.

Кроме того, уменьшение минимального

значения п в 2 раза приведет к соответствующему повышению верхнего предела выходных частот и, следовательно, к увеличению быстродействия устройства

также в 2 раза.

В отличие от прототипа, которое реализуется с применением большого количества элементарных логических ячеек, заявленное устройство реализуется на крупных типовых узлах вычислительной техники с высоким уровнем интеграции (применение элементарных логических ячеек сведено к минимуму: 2 против 10 в прототипе). Это позволяет дополнительно повысить надежность устройства в целом, а также улучшить массогабаритные характеристики объектов, в которых применяется устройство. Формула изобретения Формирователь импульсов с регулируемой частотой следования, содержащий последовательно соединенные опорный генератор, делитель частоты с переменным, коэффициентом делеиия и триггер, последовательно соединенные RS-триггер, первый

элемент И и вычитающий счетчик.суммирующий счетчик, тактовый вход которого подключен к выходу второго элемента И, Г1ри этом выход опорного генератора соединен с другим входом второго элемента И и первым входом второго элемента И, а кодовый вход заданий коэффициента деления делителя частоты с переменным коэффициентом деления является первым кодовым входом управления частотой формирователя импульсов с регулируемой частотой следования, вторым кодовым входом управления, частотой которого является вход кодового сигнала предварительной установки суммирующего счетчика, отличающийся тем, что, с целью расширения диапазона изменения частоты следования импульсов и повышения быстродействия, введен блок сравнения кодов, первый кодовый вход которого соединен с кодовым выходом вычитающего счетчика, при этом выход суммирующего счетчика соединен с R-BXOдом RS-триггера, выход которого соединен с другим входом второго элемента И, а выход счетного триггера соединен с установочным входом делителя частоты с переменным коэффициентом деления, вы ||| « J3-cC - « )Го i лГо 13 10 7 i r ff 8 52 UlJiJUH UUIJfJH

Фиг.г

ход которого соединен с S-входом RS-триггера, выход блока сравнения кодов соединен с информационным входом триггера, установочный вход которого является установочным входом формирователя последовательности импульсов с регулируемой частотой следования, выходом которого является выход делителя частоты с переменным коэффициентом деления, при этом вход кодового сигнала предварительной установки вычитающего счетчика и другой кодовый вход блока сравнения кодов являются соответственно третьим и четвертым кодовыми входами управления формирователя последовательности импульсов с регулируемой частотой следования. 1 f i °i J3-/fc oC Го fjTo )ra f5 f2 9 8 J fff /J -;.т4 |J|JiJ|JiJi

Авторы

Даты

1992-12-07—Публикация

1990-06-13—Подача