код, а выход элемента И и разрядные выходы счетчика импульсов являются

кодовыми выходами преобразователя фаза - код.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1352645A1 |

| Устройство для приема частотно-манипулированных сигналов | 1978 |

|

SU768000A1 |

| Цифровой демодулятор сигналов | 1989 |

|

SU1589420A1 |

| Устройство для измерения преобладаний двоичных сигналов | 1985 |

|

SU1246396A1 |

| Устройство тактовой синхронизации | 1983 |

|

SU1234983A1 |

| Анализатор кодовых последовательностей импульсов (его варианты) | 1984 |

|

SU1238243A1 |

| Видеорегенератор для систем связи с импульсно-кодовой модуляцией | 1977 |

|

SU792603A1 |

| Регенератор двоичных сигналов | 1984 |

|

SU1185630A1 |

| Устройство для передачи и приема дискретной информации | 1987 |

|

SU1443178A1 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1529459A1 |

1. УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ, содержащее последовательно соединенные вьщелитель границ посылок, преобразователь фаза - код, анализатор сигнала и делитель частоты, а также блок опорных частот, выход которого подсоединен к тактовому входу преобразователя фаза код, причем вход вьщелителя границ посылок является входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения синхронизации в щироком диапазоне тактовых частот входного сигнала, введены блок управления, управляемый генератор и буферный регистр, при этом выход выделителя границ посылок подсоединен к объединенным информационным входам анализатора сигнала и блока управления, тактовый вход которого подключен к выходу блока опорных частот, выходы Разрешение записи, Сброс, Установка О блока управления подсоединены соответственно к входу Разрешение записи анализатора сигнала и входам Сброс и Установка О преобразователя фаза - код, а коррекционный выход блока управления подсоединен к объединенным коррекционным входам преобразователя фаза код и анализатора сигнала, тактовый вход которого подключен к тактовому выходу преобразователя фаза код, запускающий вход и тактовый вход управляемого генератора подключены соответственно к запускающему выходу анализатора сигнала и дополнительному выходу блока опорных часS тот, разрядные входы и разрядные выходы буферного регистра подключены соответственно к кодовым выходам преобразователя фаза - код и кодовым входам управляемого генератора, выход которого подсоединен к тактовому входу делителя частоты, а установочный выход анализатора сигнала подсоединен к входу Разрешение записи буферного регистра, причем 00 4 вход делителя частоты является выходом устройства. 2. Устройство по п.1, отлисл чающееся тем, что преобразователь фаза - код вьтолнен в виде последовательно соединенных RS-триггера, элемента И и счетчика импуль сов, причем S-вход и R-вход RS-триггера являются соответственно информационным входом и входом Установка О преобразователя фаза - код, второй вход элемента И, вход Сброс и установочный вход счетчика импульсов являются соответственно тактовым входом, входом Сброс и коррек

Изобретение относится к электросвязи и может быть использовано в системах передачи дискретной информации для обеспечения тактовой ,синхронизации.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения синкронизации в широком диапазоне тактовых частот входного сигнала.

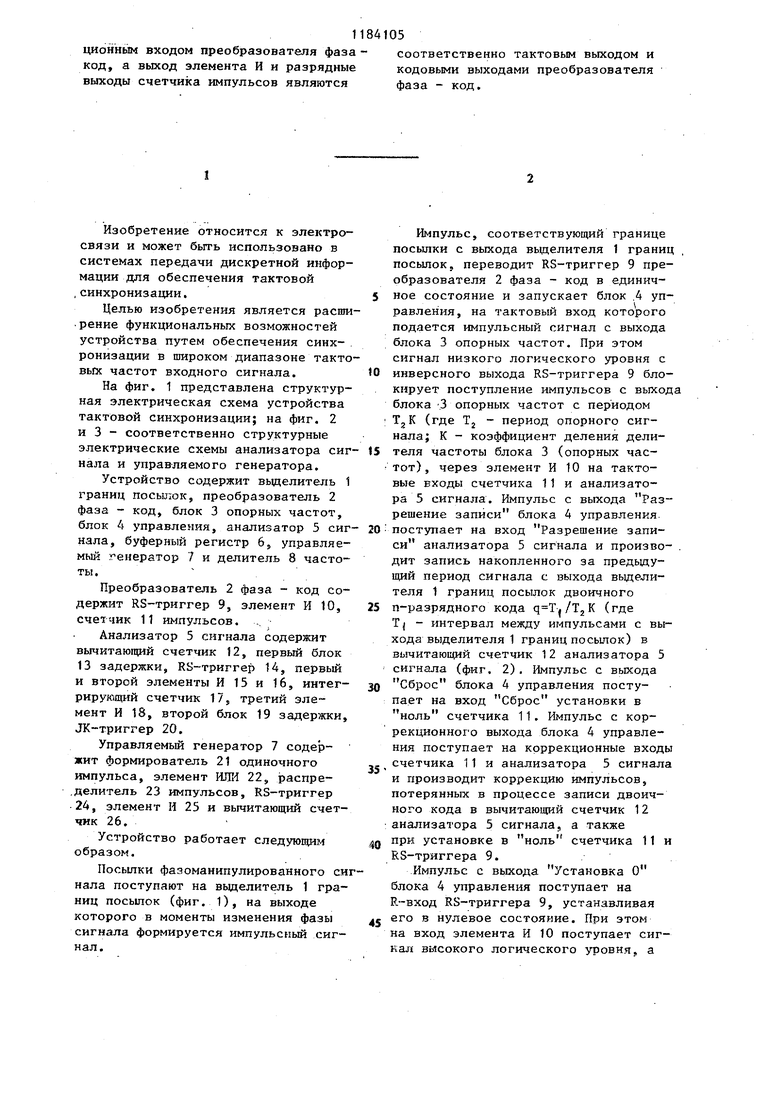

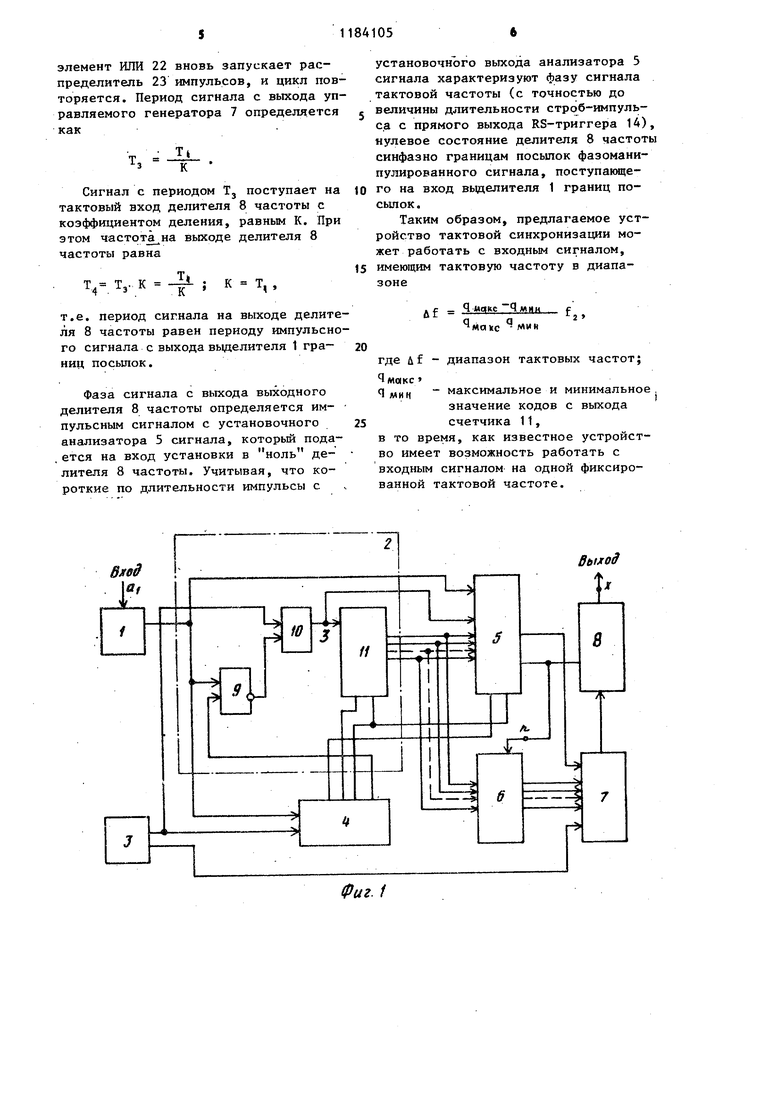

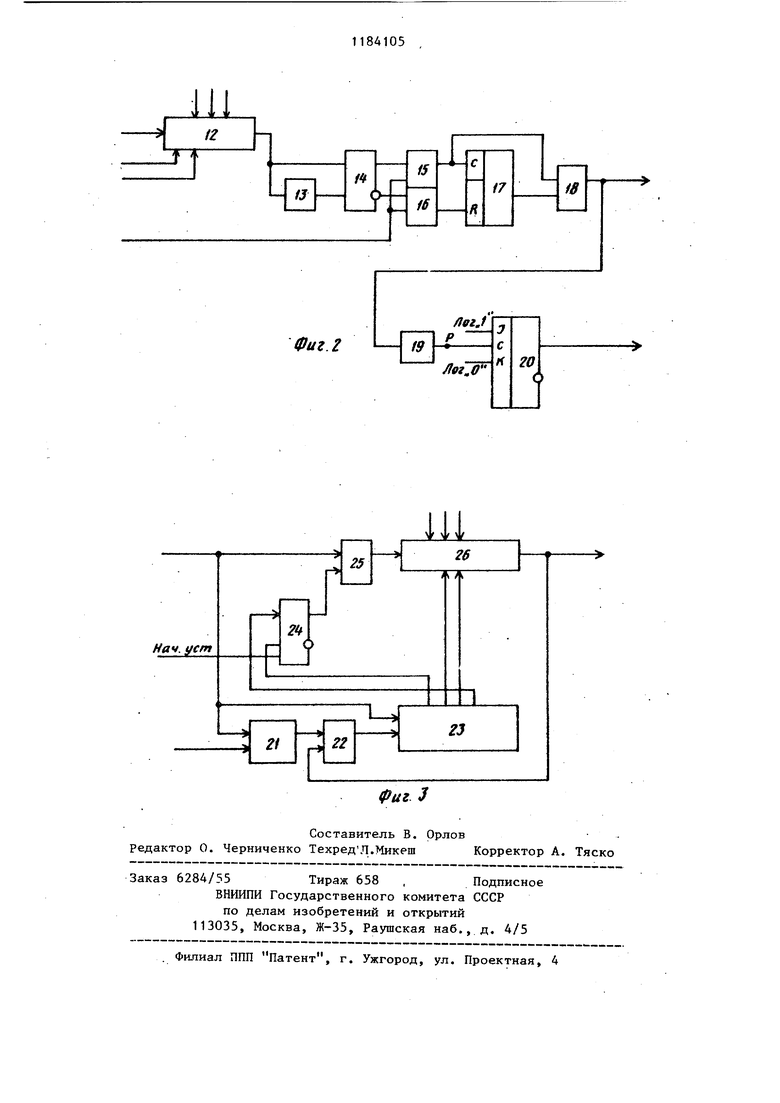

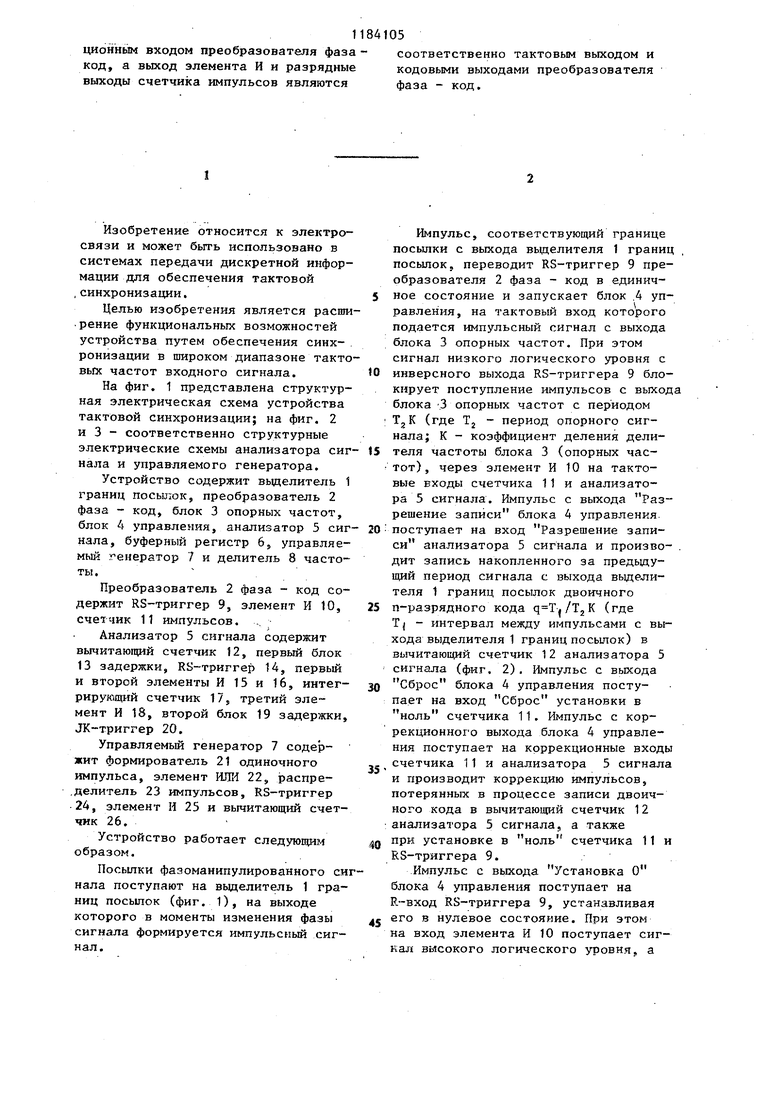

На фиг, 1 представлена структурная электрическая схема устройства тактовой синхронизации; на фиг, 2 и 3 - соответственно структурные электрические схемы анализатора сигнала и управляемого генератора.

Устройство содержит вьщелитель 1 границ посылок, преобразователь 2 фаза - код, блок 3 опорных частот, блок 4 управления, анализатор 5 сигнала, буферный регистр 6, управляемый генератор 7 и делитель 8 частоты, .

Преобразователь 2 фаза - код содержит RS-триггер 9, элемент И 10, счетчик 11 импульсов, ..

Анализатор 5 сигнала содержит вычитающий счетчик 12, первый блок 13 задержки, RS-триггер 14, первый и второй элементы И 15 и 16, интегрирующий счетчик 17, третий элемент И 18, второй блок 19 задержки, JK-триггер 20,

Управляемый генератор 7 содержит формирователь 21 одиночного импульса, элемент РШИ 22, распре,делитель 23 импульсов, RS-триггер 24, элемент И 25 и вычитающий счетчик 26,

Устройство работает следующим образом.

Посылки фазоманипулированного синала поступают на вьщелитель 1 границ посылок (фиг, 1), на выходе которого в моменты изменения фазы сигнала формируется импульсный сигнал.

Импульс, соответствующий границе посыпки с выхода вьщелителя 1 границ , посылок, переводит RS-триггер 9 преобразователя 2 фаза - код в единичное состояние и запускает блок .4 управления, на тактовый вход которого подается импульсный сигнал с выхода блока 3 опорных частот. При этом сигнал низкого логического уровня с

инверсного выхода RS-триггера 9 блокирует поступление импульсов с выхода блока -3 опорных частот с периодом Tjк (где Tj - период опорного сигнала; К - коэффициент деления делителя частоты блока 3 (опорных частот), через элемент И 10 на тактовые входы счетчика 11 и анализатора 5 сигнала. Импульс с выхода Разрешение записи блока 4 управления.

поступает на вход Разрешение записи анализатора 5 сигнала и произво- . дит запись накопленного за предыдущий период сигнала с выхода выделителя 1 границ посылок двоичного

п-раэрядного кода ./TjK (где

Tj - интервал между импульсами с выхода выделителя 1 границ посылок) в вычитающий счетчик 12 анализатора 5 сигнала (фиг, 2). Импульс с выхода

Сброс блока 4 управления поступает на вход Сброс установки в ноль счетчика 11, Импульс с коррекционного выхода блока 4 управления поступает на крррекционные входы

счетчика 11 и анализатора 5 сигнала и производит коррекцию импульсов, потерянных в процессе записи двоичного кода в вычитающий счетчик 12 : анализатора 5 сигнала, а также

при установке в ноль счетчика 11 и RS-триггера 9,

Импульс с вькода Установка О блока 4 управления поступает на R-вход RS-триггера 9, устанавливая

его в нулевое состояние. При этом на вход элемента И 10 поступает сигнал высокого логического уровня, а импульсы с выхода блока 3 опорных частот с периодом Tj К вновь поступают на тактовый вход счетчика 11 и тактовый вход вычитающего счетчика 12 анализатора 5 сигнала. В этом случае происходит очередное накопление кода q, соответствующего теку щему периоду тактовой частоты с помощью счетчика 11, и считывание двоичного кода , соответствующего предыдущему периоду тактовой частоты с разрядов вычитающего счетчика 12 анализатора 5 сигнала. При достижении вычитающим счетчиком 12 определенного состояния на его выходе появляется короткий по длительности импульс который по тупает непосредственно и через первый блок 13 задержки на Зи R-входы RS-триггера 14, формируется стробимпульс, длительность которого равна времени задержки первого блока 13 задержки. На информационный вход анализатора сигнала 5 (объединенные входы первого и второго элементов И 15 и 16) поступают импульсы с выхода выделителя 1 границ посьшок. В случае совпадения длительности (1-1)-й посыпки входного сигнала с длительностью i-й посьшки происходит совпадение импульса с выхода выдели теля 1 границ посылок строб-импульса, снимаемого с прямого выхода RS-триггера 14. Это совпадение фиксируется с помощью .первого элемента И 15. Несовпадение строб-импульса и импульса с выхода выделителя 1 границ посылок фиксируется с помощью второго элемента И 16. С выхода первого элемента И 15 импульсный си нал поступает на тактовый вход интегрирующего счетчика 17, Импульс с выхода второго элемента И 16 поступает на вход установки в ноль (R-вход) интегрирующего счетчика 17, При следовании одинаковых по длительности смежных периодов импульсного сигнала с выхода вьщелителя 1 границ посыпок происходит заполнение интегрирующего сче чика 17 и на его выходе появляется сигнал высокого логического уровня, разрешающий импульсу, соответствующему концу т+1 и началу iiH-2 периодов тактовой частоты, с выхода пер- вого элемента И 15 пройти на выход третьего элемента И 18. Импульс с выхода третьего элемента И 18 посту 1 пает на вход Разрешение буферного регистра 6 (фиг. 1), переписыTJвая при зтом двоичный код q из счетчика 11 в буферный регистр 6. Импульс, появившийся на выходе третьего элемента И 18, поступает также через второй блок 19 задержки на С-вход JK-триггера 20, переводя его в единичное положение. Сигнал с выхода JK-триггера 20 анализатора 5 сигнала поступает на вход Запуск управляемого генератора 7, RS-триггер 24 управляемого генератора 7 (фиг. 3) установлен с помощью сигнала начальной установки в нулевое положение (по R-входу), При этом сигнал с прямого выхода RS-триггера 24 блокирует поступление импульсов с дополнительного выхода блока 3 опорных частот 3 через элемент И 25. При поступлении на вход Запуск управляемого генератора 7 сигнала высокого логического уровня срабатывает формирователь 21 одиночного импульса и через элемент ИЛИ 22 запускается распределитель 23импульсов. Импульс с первого выхода распределителя 23 импульсов поступает на R-вход RS-триггера 24. Импульс с второго выхода распределителя 23 импульса записьшает в вычитающий счетчик 26 двоичный код q, поступающий на кодовые входы управляемого генератора 7, Импульс с третьего выхода распределителя 23 импульсов производит поправку кода q, что необходимо для учета операций установления RS-триг- , гера 24 в нулевое положение, записи кода q в вычитающий счетчик 26, самой поправки и установления RS-триггера , 24в единичное положение. с четвертого выхода распределителя 23 импульсов поступает на вход RS-триггера 24, При этом сигнал с периодом TJ поступает на второй вход управляемого генератора 7 и через элемент И 25 поступает на тактовый вход вычитающего счетчика 26 и производит считывание кода с учетом указанной поправки с разрядов вычитающего счетчика 26, При достижении вычитающим счетчиком 26 нулевого состояния на выходе вычитающего счетчика 26, являкмцимся одновременно и выходом управляемого генератора 7, появляется импульс, который через

элемент ИЛИ 22 вновь запускает распределитель 23 импульсов, и цикл повторяется. Период сигнала с выхода управляемого генератора 7 определяется как

Тэ

Сигнал с периодом Tj поступает на тактовый вход делителя 8 частоты с коэффициентом деления, равным К. При этом частота на выходе делителя 8 частоты равна

К --II .

Т .

к 3. К

М

т.е. период сигнала на выходе делителя 8 частоты равен периоду импульсного сигнала с выхода выделителя 1 границ посылок.

Фаза сигнала с выхода выходного делителя 8 частоты определяется импульсным сигналом с установочного анализатора 5 сигнала, которьй подается на вход установки в ноль делителя 8 частоты. Учитывая, что короткие по длительности импульсы с

Фиг. 1

установочного выхода анализатора 5 сигнала характеризуют фазу сигнала тактовой частоты (с точностью до величины длительности строб-импульса с прямого выхода RS-триггера 14), нулевое состояние делителя 8 частоты синфазно границам посылок фазоманипулированного сигнала, поступающего на вход вьщелителя 1 границ посылок ,

Таким образом, предлагаемое устройство тактовой синхронизации может работать с входным сигналом,

имеющим тактовую частоту в диапазоне

д Ч мдкс Чмяц

-2

манс мин

диапазон тактовых частот;

максимальное и минимальное,

значение кодов с выхода

счетчика 11,

в то время, как известное устройство имеет возможность работать с входным сигналом на одной фиксированной тактовой частоте.

ш

ш

Авторы

Даты

1985-10-07—Публикация

1982-12-07—Подача