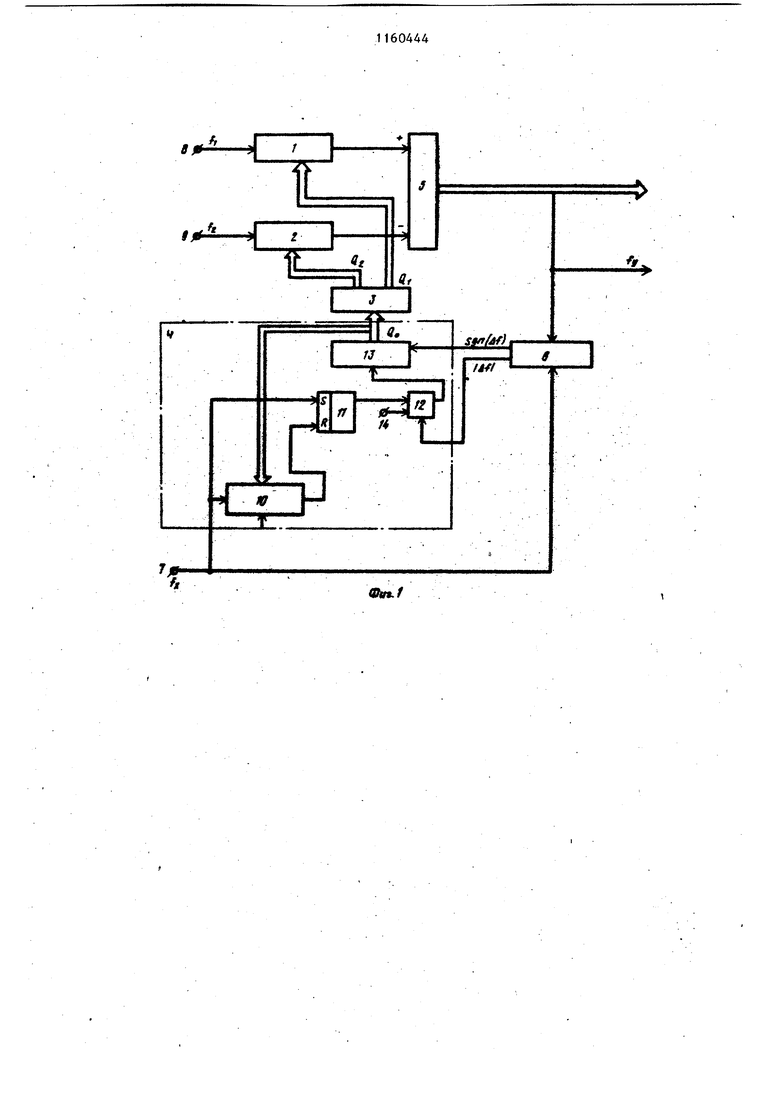

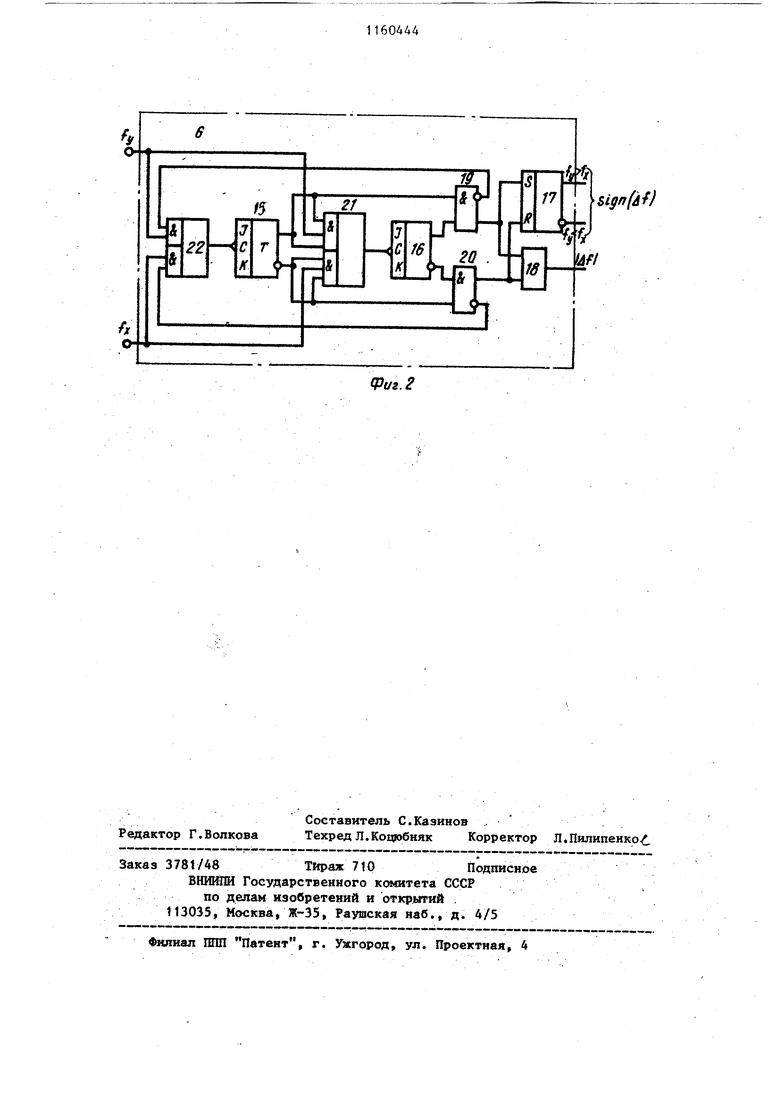

Изобретение относится к автоматике и вьиислительной технике и может быть использовано в импульсных систе мах для преобразования частотно-импульсной формы представления информации. Известен интегратор частотно-импульсных сигналов, содержащий генератор импульсов, управляемый делитель частоты, компенсатор фазовой ошибки, счетчик, измеритель рассогласования и блок управления (11. Недостатками данного устройства являются ограниченный частотный диа,пазон входных сигналов и неравномерность следования импульсов на счетном входе счетчика, обусловленная работой схемы фазовой коррекцир-. Наиболее близким к изобретению является устройство для интегрирования частотно-импульсных сигналов содержащее выходной счетчик, измеритель рассогласования, подключенный первым входом к информационному входу устройства, первый управляемый делитель частоты, соединенный счетным входом с шиной ввода первой опорной частоты, и блок комбинированного управления, содержащий триггер, элемент И и счетчик, подключенный входом управления установкой кода к входу устройства и к первому установочному входу триггера блока комбинированного управления, соединенного вторым установочным входом с выходом счетчика блока комбинированного управления, а выходом с первым элемента И блока ком бинированного управления, подключенного вторым входом к шине ввода тактовой частоты, а выходом - к счетному входу счетчика блока комбинированного управления и первому входу узла управления блока комбинированного управления, соединенного вторым входом с выходом измерения рассогласования, а выходом - с установочным входом счетчика блока крмби нированного управления и управляющим входом управляемого делителя частоты подключенного выходом к второму входу измерителя рассогласования и первому входу компенсатора фазовой ошибки, соединенного вторым и третьи входами с вмной ввода опорной частот и выходом измерителя рассогласования а выходом - с входом выходного счетчика СОИзвестное устройство осуществляет умножение входной частоты импульсов и вычисляет ее интегральное значение на заданном интервале времени. Сигнал рассогласования формируется путем подсчета импульсов умноженной частоты (с выхода управляемого делителя частоты) в интервале входных импульсов. Сигнал рассогласования определяет компенсирующее воздействие по фазе, а с учетом входной частоты - и компенсирующее воздействие по частоте. Схема компенсатора фазовой ошибки может осуществлять сброс ошибки добавлением или вычитанием из входной последовательности импульсов повышенной частоты требуемого коли- честна (как правило, не более трех). Однако такой способ коррекции приводит к неравномерности следования импульсов на импульсном входе реверсивного счетчика (соответственно к скачкам.и сбоям реверсивного счетчика). Кроме того, при фазовой коррекции не учитывается частота входных импульсов (вносится дополнительная динамическая ошибка). Поэтому известное устройство обладает невысокой точностью умножения и интегрирования частоты импульсов. Цель изобретения - повьппение точности умножения интегрирования частоты импульсов и упрощение устройства за счет исключения компенсатора фазовой опшбки. Поставленная цель достигается тем, что в устройство для интегрирования частотно-импульсных сигналов, содержащее выходной счетчик, измеритель рассогласования, подключенный первым входом к информационному входу устройства, первый управляемый делитель частоты, соединенньй счетньм входом с шиной ввода первой опорной частоты, и блок комбинированного управления, содержащий триггер, злемент И и счетчик, подключенный входом управления установкой кода к входу устройства и к первому установочному- входу триггера.блока комбинированного управления, соединенного вторым установочным входом с выходом счетчика блока комбинированного управления, а выходом - с первым входом элемента И блока комбинированного управления, подключенного вторым входом к шине ввода тактовой частоты, введены второй управляемый делитель частоты и дешифратор, а блок комбинированного управления содержит реверсивный счетчик, соединеиньй выходами разрядов с входами деши4ч атора и установочными входами счетчика блока комбинированного управления, входом управления реверсом - со знаковьв выходом измерителя рассогласования,а счетным входом - с выходом элемента И блока комбинированного управления, подключенного третьим входом к выходу модуля рассогласования измерителя рассогласования, соединенного вторьм входом с выходом выходного ,счетчика, подключенного суммирующим И вычитаюпр«м входами к выходи первого и второго управляемых делителе частоты соответственно, управлякицие входы которых соединены с первой и второй группами выходов дешифратора, причем второй управляемый делитель частоты Подключен счетным вход к шине ввода второй опорной частоты а счетный вход счетчика блока комбинированного управления соединен с шиной ввода тактовой частоты. На фиг.1 дана блок-схема предлагаемого устройства для интегрирования Цастртно-импульсньк сигналов) на фиг.2 - схема возмол1:ного варианта реализации измерителя рассогласо вания. Устройство для интегрирования частотно-импульсных сигналов , (фиг.1) содержит первый и второй управляемые делители 1 и 2 частоты дешифратор 3, блок 4 комбинированно го управления, выходной счетчик 5 (реверсивного типа), измеритель 6 рассогласования, вход 7 устройства и шины 8 и 9 ввода первой и второй опорных частот. Блок 4 комбинирован ного управления .содержит счетчик 10, триггер И, элемент И 12, ревер сивный счетчик 13 и ншну 14 ввода тактовой частоты. Измеритель 6 рассогласования (фиг.2) содержит Ктриггеры 15 и 16, Р5-триггер 17 и элементы ИЛИ 18, И 19 и 20 и И-ШШ 21 и 22. Управляемые делители 1 и 2 часто ты предназначены для формирования импульсов повьшенных частот (по отношению к входной частоте) в соответствии с вьфажениями г {-1 , . fj --IT 444 где f , первая и вторая некратные друг другу опорные частоты; ®,02 - коэффициенты деления, формируемые на вьпсодах дешифратора 3. Дешифратор 3 используется по прямому назначению. Он как бы расщепляет сигнал (кой 9р ) с выхода блока 4 комбинированного управления на два 0 и Q в соответствии с требуемым коэффициентом умножения частоты. Блок 4 комбинированного управления предназначен для формирования кода Q зависимости от сигнала рассогласования df и входной чаетоты импульсов ( . Могут быть реализованы различные законы управления (пропорционально-интегральный. пропорционально-интегрально-дифференциальный и т.д.) в зависимости от выбора принципиальной схемы. Так, может быть использована принципиальная схема (фиг.1) с использованием реверсивного счетчика 13, счетчика 10, триггера 11 и элемента И 12. Для расширения частотного диапазона блок 4 комбинированного управления должен вьздерживать соотношение: д «const (где 4(1 -приращение кода), что достигается корректирующим контуром в его составе (счетчик 10, триггер 11 и злемент И 12). Для вычисления интервалов может быть использована тактовая частота ,, или же использована одна из опорных частот. Выходной счетчик 5 предназначен для формирования цифрового и импульсного выходных сигналов устройства путем алгебраического суммирования импульсов разных частот, поступающих на его суммирующий и вычитающий входы (динамически изменяемых в зависимости от состояния входного процесса) Измеритель 6 рассогласования предназначен для измерения рассогласования по величине и знаку между входной f и выходной ,, частотами. Измерение может осуществляться на скользящем временном интервале. Для реализации измерителя рассогласования может быть использован ревер:ивный счетчик, подсчитьгеающий имтульсы - l,j в интервале импульсов ., дешифратор, определяюпщй модуль знак 9gn { рассогласования. $ измеритель 6 рассогласования может быть также реализован, с использованием JK-триггеров (фиг.2), элемент И, ИЛИ, НЕ и RS -триггера. Изменение знака входного процесса (направления изменения) может осу ществляться переключением входов опорных .частот (не показано), кроме того, установочные входы выходного счетчика 5 можно подключить к шине корректирующего кода для юстировки. Устройство работает следующим образом. При передаче плавно изменяющего-ся процесса (например, угла вращения инерционного объекта) методом равных приращений по каналу связи передается последовательность импульсов частоты fy (следующих через равные угловые интервалы) и юст ровочные импульсы (определяющие зна чения корректирующих кодов), устанавливающие счетчик 5 в требуемое состояние. В интервалах между юстир вочными импульсами устройство осуществляет экстраполяцию состояния процесса, используя его инерционные свойства. Направление изменения про цесса оценивается предварительно и определяется для интегратора соотношением опорных частот. Замкнутый контур, содержаш 1й блок 4 ком|бинированного управления, депшфрато 3, управляемые делители 1 и 2 частоты, счетчик 5 и измеритель 6 рас,согласования осуществляет слежение за частотой входных импульсов и ее кратное умножение. Изменение частот импульсов повьш1енных частот-f и достигается изменением коэффициенто деления управляемых делителей 1 и 2 частоты, причем каждому значению ко с выхода блока 4 комбинированного управления соответствует на выходах 44 дешифратора 3 определенная пара управляющих сигналов. Блок 4 комбинированного управления изменяет приращение && пропорционально 0, чем и достигается слежение за часГотой входных импульсов в широком диапазоне частот с сохранением точности воспроизведения инерционного процесса. Так, при низкой частоте входных импульсов, управляющее воздействие изменяется на большую величину, позволяющую эффективно .компенсировать ошибку по частоте, чем при высокой частоте (достигается малая динамическая ошибка в широком диапазоне частот). Компенсация фазовой ошибки осуществляется разнесением частот {, и 2 по величине, чем и достигается эффект фазовой коррекции. Код состояния инерционного процесса форьшруется на выходе счетчика 5 путем алгебраического суммирования импульсов, поступающшс на его суммируюоосй и вычитающий входы относительно установленного значения. По сравнению с известньм предлагаемое устройство обладает большей точностью (ориентировочно на 2030%). В известном устройстве используется неравнс(ерная фазовая коррекция (добавление или вычитание импульсов), осуществляемая после частотной коррекции. Аппаратурная реализация предлагаемого устройства значительно проще, так как функцюо фазовой коррекции выпсшняют управляемые делители частоты (достигается совмещение фазорой и частотной коррекций). .Уменьоекие аппаратурных затрат ориентировочно на 25 % достигается за счет использования двух некратных onopHfsiK частот.

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий умножитель частоты | 1979 |

|

SU832556A1 |

| Интегратор импульсов | 1978 |

|

SU750508A1 |

| Интегратор азимутных импульсов | 1977 |

|

SU691877A2 |

| Интегратор азимутных импульсов | 1975 |

|

SU572795A1 |

| Интегратор азимутных импульсов | 1977 |

|

SU732907A1 |

| Устройство для управления многоканальным электроприводом тренажера | 1984 |

|

SU1180846A1 |

| Интегратор азимутных импульсов | 1976 |

|

SU646348A2 |

| Цифровой умножитель частоты | 1977 |

|

SU691853A1 |

| Преобразователь частоты в код | 1978 |

|

SU744974A1 |

| Устройство фазирования бинарного сигнала | 1981 |

|

SU1075431A1 |

УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ, содержащее выходной счетчик, измеритель рассогласования, подключенный первьм входом к информационному входу устройства, первый управляе 4ЪЙ делитель частоты, соединенный счетным входом с шиной ввода первой опорной частоты, и блок комбинированного управления, содержащий триг гер, элемент И и счетчик, подключенный входом управления установкой кода к входу устройства и к первому установочному входу триггера блока комбинированного управления, соединенного BTOpt установочным входом с выходом счетчика блока комбинированного управления, а выходом - с первым входом элемента И блока комбинированного управления, подключеняого втор входом к Евине ввода тактовой частоты, о т л и чающее ся тем, что, с целью повьшения точности, в него введены второй управляемый делитель частоты и дешифратор, а блок комбинированного управления содержит реверсивный счетчик, соединенный выходами разрядов с входами дешифратора и установочными входами счетчика блока комбинированного управления, входом управления реверсом - соэнаковым выходом измерителя рассогласования, а счетньм входом - с выходом элемента И блока комбинированного управления, подключенного третьим входом к выходу модуля рассогласования измерителя рассогла(Л сования, соединенного вторым входом с выходом выходного сметчика, подключенного суммирующим и вычитающим входами к выходам первого и второго управляемых делителей частотысоответственно, управляющие входы которых соединены с первой и второй группами выходов дешифратора, приО5 чем второй управляемьй делитель часо тоты подключен счетным входом к ши4 4 4 не ввода второй опорной частоты, а i счетный вход счетчика блока ком:бинированного управления соединен с шиной ввода тактовой частоты.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ИНТЕГРАТОР АЗИМУТНЫХ И/\\ПУЛЬСОВ | 1972 |

|

SU424164A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Интегратор азимутных импульсов | 1975 |

|

SU572795A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-07—Публикация

1984-01-04—Подача