Изобретение относится к электрическим измерениям и может быть использова- но при построении высокоточных измерительных приборов,

Известно устройство для измерения среднеквадратического значения сигнала. Оно состоит из управляющего устройства, электронного ключа, генератора импульсов, источника компенсирующего напряжения, счетчика импульсов, дешифратора, регистрирующего устройства, нуль-органа, управляемого делителя и программирующего блока. В данном устройстве переменное входное напряжение предварительно преобразовывается в постоянное, а затем производится его измерение. Для преобразования переменного напряжения в постоянное применен преобразователь средних значений.

Постоянное напряжение измеряется следующим образом, При поступлении пускового импульса от управляющего устройства открывается электронный ключ и к источнику компенсирующего напряжения поступают сигналы генератора импульсов, которые одновременно фиксируются счет- чиком импульсов. Источник компенсирующего напряжения вырабатывает компенсирующее напряжение Ux, изменяющееся на Дихс приходом каждого импульса от генератора импульсов, Процесс измерения сводится к подсчету числа импульсов счетчиком, прошедших через электронный ключ за определенное время. При срабатывании нуль-органа, когда преобразованное в постоянное переменное входное напряжение их, поступающее на нуль-орган через управляемый делитель, станет равным компенсирующему напряжению Ux, ключ закроется, генерирование AUx и счет импульсов прекратится, показания счетчика импульсов после дешифрации передаются на регистрирующее устройство.

Недостатком данного устройства измерения среднеквадратического значения сигнала является низкая точность измерения. Это обусловлено гем, что применяемый в устройстве преобразователь переменного напряжения в постоянное не предназначен для преобразования сигналов произвольной формы.

Из известных устройств измерения среднеквадратическйх значений сигнала наиболее близким п о технической сущности явлйеТся устройство для измерения среднеквадратического значения сигнала. Оно состоит из формирователя измеряемого сигнала, формирователя импульсов перехода через ноль, генератора импульсов, делителя частоты, счетчика, регистров, формирователя интервала записи, триггеров, счётчика адреса, аналого-цифрового и цифрогналогового преобразователей, групп элементов И, элементов И, групп элементов И-ИЛИ, блоков памяти, формирователя среднеквадратическйх значений, формирователя сигналов считывания, блока регистрации и формирователя управляющих сигналов.

Измерение среднеквадратического значения сигнала происходит следующим образом. Переменный сигнал Уусформиро- зателя измеряемого сигнала поступает на формирователь импульсов перехода через ноль и аналого-цифровой преобразователь. По сигнапам формирователя импульсов перехода через ноль формирователь управляющих сигналов вырабатывает сигналы, синхронизирующие работу всего устройства.

С помощью генератора импульсов, делителя частоты, счетчика, дешифратора, регистра и формирователя интервалов записи вырабатываются сигналы запуска аналого- цифрового преобразователя. Частота запуска последнего определяет число выборок мгновенных значений входного сигнала за интервал наблюдения. Максимальное число выборок зависит в заданном интервале наблюдения от заданной точности измерения.

Информация, преобразованная аналого-цифровым преобразователем, поступает поочередно на два блока памяти через группы элементов И-ИЛИ по адресам, формиру1 емым счетчиком адреса. В эго же время с блоков памяти считывается информация, поступившая в них в предыдущем такте. Считываемая информация поступает и регистр. Дискретная информация, хранащая- ся о регистре, преобразуется цифроаиалоговым преобразователем в переменный сигнал. Этот сигнал после преобразователя среднеквадратическйх значений и усилителя поступает на блок регистрации.

Недостатком данного устройства для измерения среднеквадратического значения сигнала является низкая точность измерения (1-2)% в широком частотном диапазоне. Это обусловлено тем, что при работе в области высоких частот уровень входного сигнала изменяется за время измерения больше допустимого значения. Поэтому и разрядный аналого-цифровой преобразователь не успевает закодировать текущее значение выборки разрядным кодом, т.е. обеспечить заданную точность измерения.

Целью изобретения является повышение точности измерения среднеквадратического значения сигнала.

Поставленная цель достигается тем, что

в устройство для измерения среднеквадратического значения сигнала; содержащее формирователь измеряемого сигнала, подсоединенный входом к входной шкале, формирователь среднеквадратического

значения, выход которого соединен через усилитель с входом блока регистрации, первый регистр и дешифратор, подсоединенные входами соответственно к первому и второму выходам формирователя управляющих сигналов, счетчик, соединенный нулевым входом и входом разрешения соответственно с третьим и четвертым выходами формирователя управляющих сигналов, второй регистр, подсоединенный

управляющим входом к пя тому выходу формирователя управляющих сигналов, первый и второй элементы И, соединенные первыми входами с шестым выходом формирователяуправляющихсигналов,

аналого-цифровой преобразователь, подсоединенный запускающим входом к седьмому выходу формирователя управляющих сигналов, счетчик адреса, соединенный нулевым ВХОДОМ С ВОСЬМЫМ ВЫХОДОМ фОрМИрО;

вателл управляющих сигналов, триггер , подсоединенный счетным входом к девятому выходу формирователя управляющих сигналов, формирователь интервала записи, соединенный входом и выходом соответственно с десятым выходом и первым входом формирователя управляющих сигналов, формирователь импульсов перехода через ноль, включенный между выходом формирователя измеряемого сигнала и вторым входом формирователя управляющих сигналов, цифроаналоговый преобразователь, подключенный выходом к входу формирователя среднеквадратического значения, формирователь сигналов считыоания, третий регистр, третий и четвертый

элементы И, первая, вторая, третья, четвертая и пятая группы элементов И-ИЛИ, первая и вторая группы элементов И, первый и второй блоки памяти, делитель частоты, генератор импульсов и элемент ИЛИ, причем формирователь управляющих сигналов подключен седьмым выходом к счетному входу счетчика адреса, соединенного выходами с первыми группами входов первой и второй групп элементов И-ИЛИ, выход делителя частоты соединен с первым входом формирователя сигналов считывания, который подключен первым, вторым и третьим выходами к входу третьего регистра и к входам считывания первого и второго блоков памяти, соединен четвертым и пятым выходами с первым и вторым входами первой группы элементов И-ИЛИ, подключен шестым и седьмым выходами к первому и второму входам второй группы элементов И-ИЛИ, соединен восьмым и девятым выходами с первым и вторым входами третьей группы элементов И-ИЛИ и подсоединен вторым входом к первому выходу триггера, соединенному с выходом первой группы элементов И и с вторым входом первого элемента И, подключенного выходом к входу записи первого блока памяти, который подсоединен адресными входами к выходам первой группы элементов И-ИЛИ и соединен информационными входами с выходами первой группы элементов И, выходы второй группы элементов И соединены с информационными входами второго блока памяти, который соединен адресными входами с выходами второй группы элементов И-ИЛИ и подсоединен входом записи к выходу второго элемента И, соединенного вторым входом с вторым выходом триггера, подключенным к входу второй группы элементов И, вход цифроаналогового преобразователя подсоединен к выходу третьего регистра, соединенного информационными входами с выходами третьей группы элементов И-ИЛИ, подсоединенной первой и второй группами входов к выходам соответственно первого и второго блоков памяти, а выход формирователя измеряемого сигнала соединен с измерительным входом аналого- цифрового преобразователя, подсоединенного тактовым входом к второму выходу делителя частоты, который соединен входом с выходом генератора импульсов, подключен третьим выходом к счетному входу счетчика и соединен группой выходов с первой группой входов формирователя интервала записи, подсоединенного второй группой входов к выходам первого регистра, соединенного группой входов с выходами дешифратора, группа входов которого

подсоединена к выходам счетчика, дополни тельно введены третий блок памяти, пода единенный адресными входами к выходам первой группы элементов И-ИЛИ и соединен входом считывания с выходом элемента ИЛИ, подсоединенного первым входом к десятому выходу формирователя сигналов считывания и соединенного вторым входом с выходом третьего элемента И, первый

0 вход которого подсоединен к одиннадцатому выходу формирователя управляющих сигналов, подключенному к первому входу четвертого элемента И, соединенного вторым входом с первым выходом триггера,

5 подключенным к первому входу четвертой группы элементов И-ИЛИ, соединенного выходами с информационными входами второго регистра и подсоединенного вторым входом к второму выходу триггера, со0 единенному с вторым входом третьего элемента И, четвертый блок памяти, подключенный выходами к входам четвертой группы элементов И-ИЛИ и к входам пятой группы элементов И-ИЛИ, соединенной вы5 ходами с другой группой входов третьего регистра и подсоединенной первым и вторым входами к одиннадцатому и двенадцатому выходам формирователя сигналов считывания, пятый и шестой элементы И,

0 соединенные первыми входами с двенадцатым выходом формирователя управляющих сигналов, третья и четвертая группы элементов И, подсоединенные группами входов к выходам аналого-цифрового

5 преобразователя, дополнительный аналого- цифровой преобразователь, подсоединенный тактовым входом к второму выходу делителя частоты, соединенный запускающим входом с седьмым выходом формиро0 вателя управляющих сигналов и подключенный выходами к группам входов первой и второй групп элементов И.допол- нительный элемент ИЛИ, подсоединенный первым и вторым входами к выходу четвер5 того элемента И и к тринадцатому выходу формирователя сигналов считывания, дополнительный цифроаналоговый преобразователь, соединенный входами с выходами второго регистра, блок вычитания, подсое0 диненный первым входом к выходу форми- рователя измеряемого сигнала. формирователь адреса счмтывания,подсое- диненный первым и вторым входами к первому выходу делителя частоты и к

5 тринадцатому выходу формирователя -управляющих сигналов, соединенный группой входов с выходами счетчика адреса и подсоединенный выходами к другим группам входов первой и второй групп элементов И-ИЛИ, причем первый выход триггера подключей к входу третьей группы элементов И и к второму входу пятого элемента И, соединенного выходом с входом записи третьего блока памяти, подсоединенного информационными входами к выходам третьей труп- пы элементов И, второй выход триггера подключен к входу четвертей группы элементов И и к второму входу шестого элемента И, соединенного выходом с входом записи четвертого блока памяти, который подсоединен информационными входами к выходам четвертой группы элементов И, выход дополнительного цифроаналогового преобразователя подключен к второму входу блока вычитания, соединенного выходом с сигнальным входом дополнительного аналого-цифрового преобразователя, выходы третьего блока памяти подключены к другим группам входов четвертой и пятой групп элементов И-ИЛИ, а выход дополнительно- го элемента ИЛИ соединен с входом считывания четвертого блока памяти.

Повышение точности измерения сред- неквадратических значений переменных сигналов на порядок по сравнению с прото- типом обусловлено поэтапным кодированием входного сигнала. В i период входного сигнала кодируются старшие разряды, а в 0+1) период - младшие разряды входного сигнала. В (1+1) период кодируется разност- ный сигнал, полученный путем вычитания из входного сигнала преобразованного сигнала после цифроаналогового преобразования кода старших разрядов i периода.

Для кодирования младших разрядов в (i+1) периоде входного сигнала вводятся два блока памяти, две группы элементов И- ИЛ И, две группы элементов И, цифроанало- говый, аналого-цифровой преобразователи, регистр и блок вычитания.

Управляющие сигналы, необходимые для кодирования младших разрядов вырабатываются формирователем управляющих сигналов, формирователем сигналов считывания, элементами И и элементами ИЛИ,

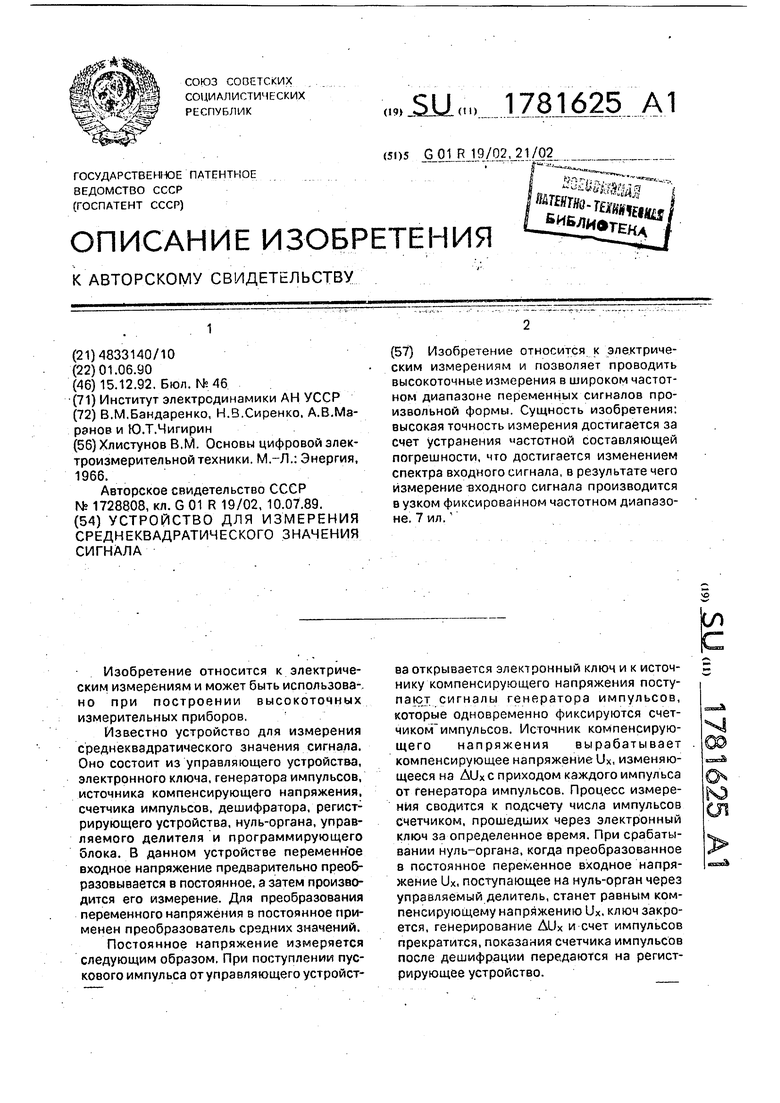

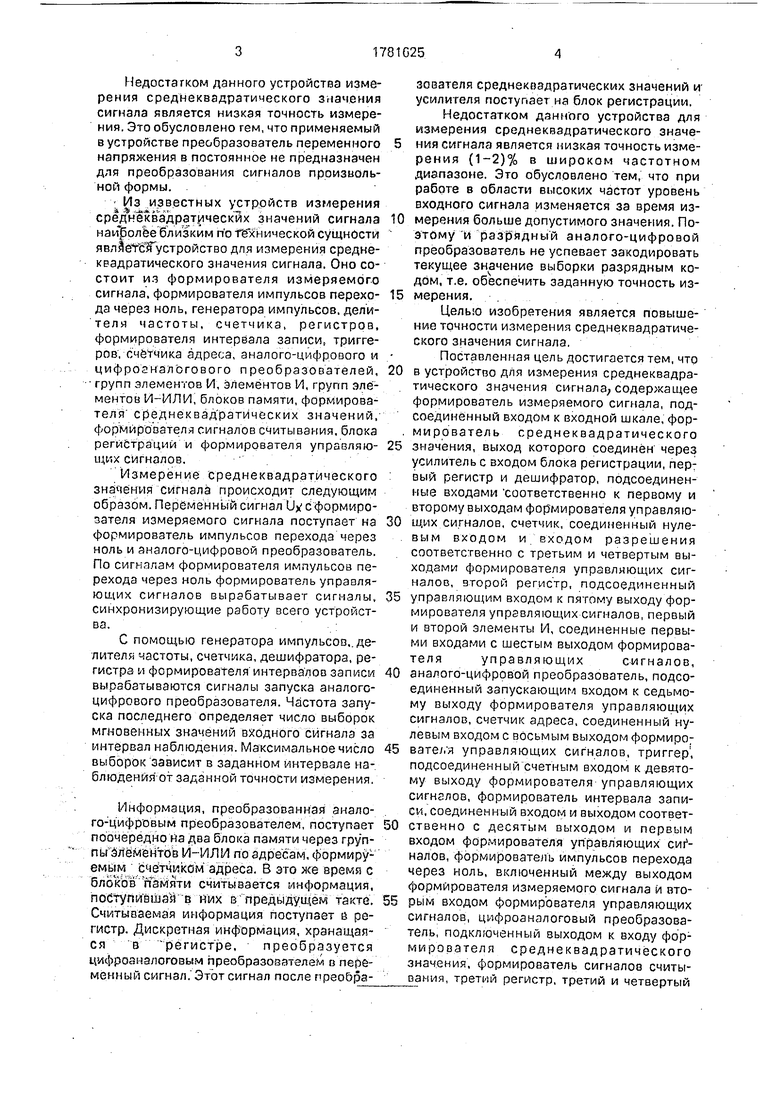

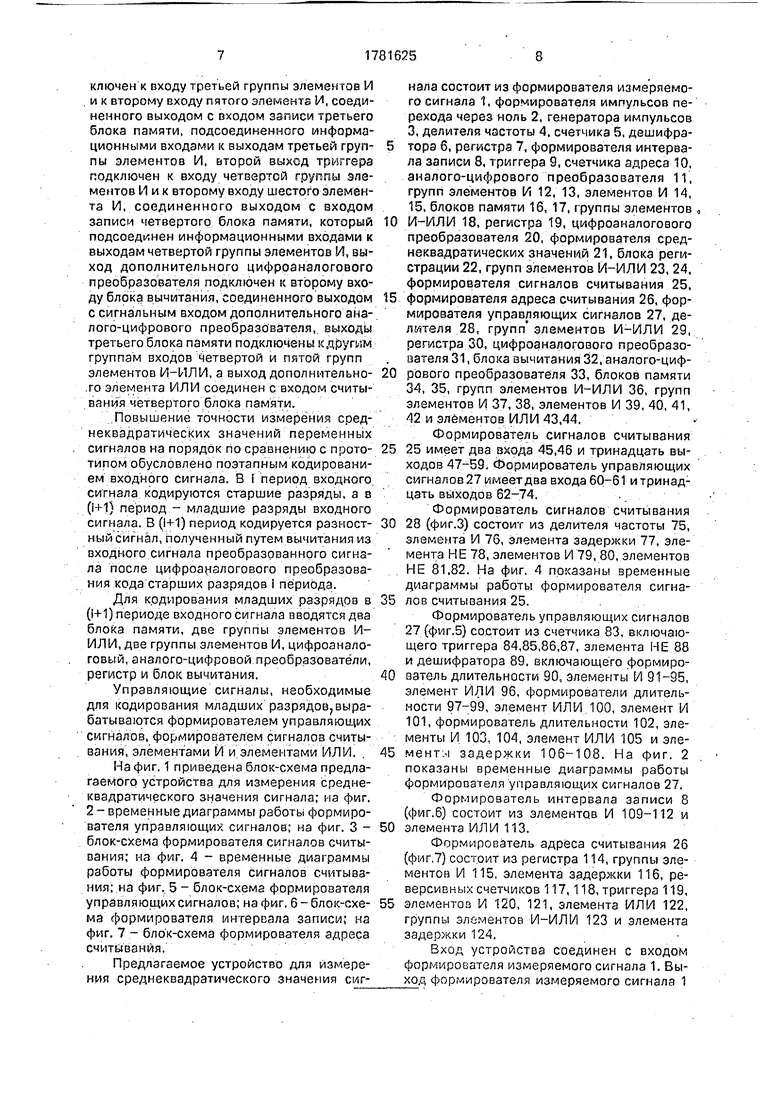

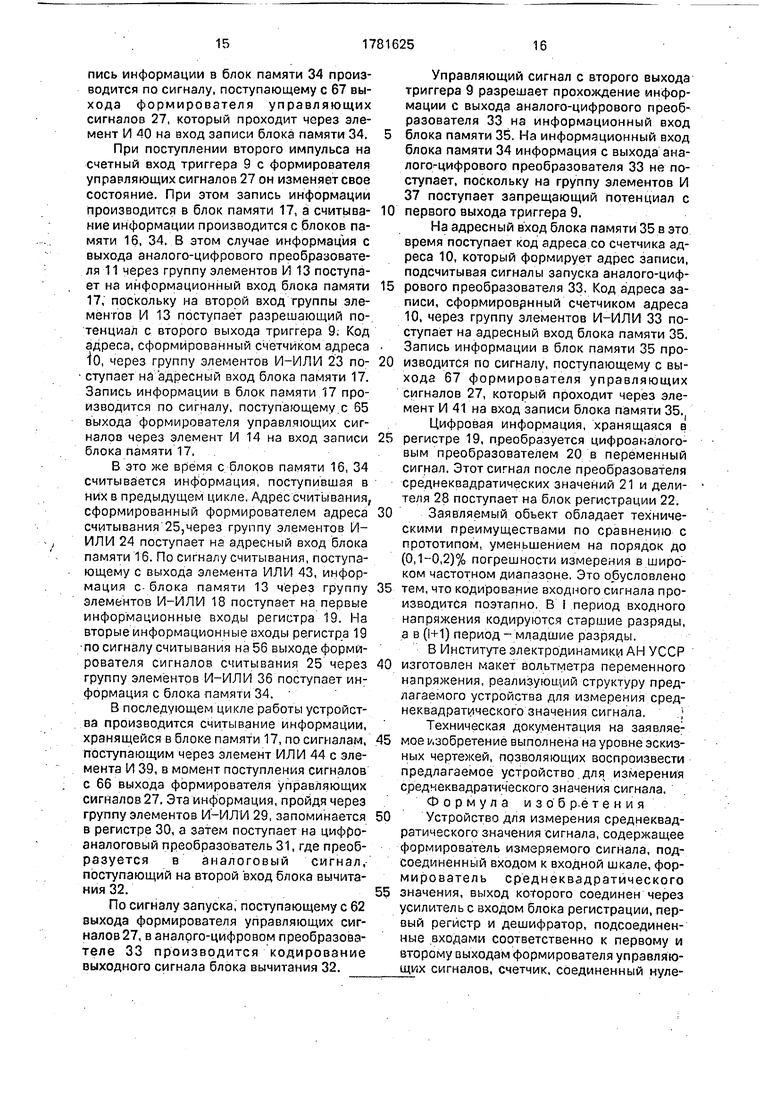

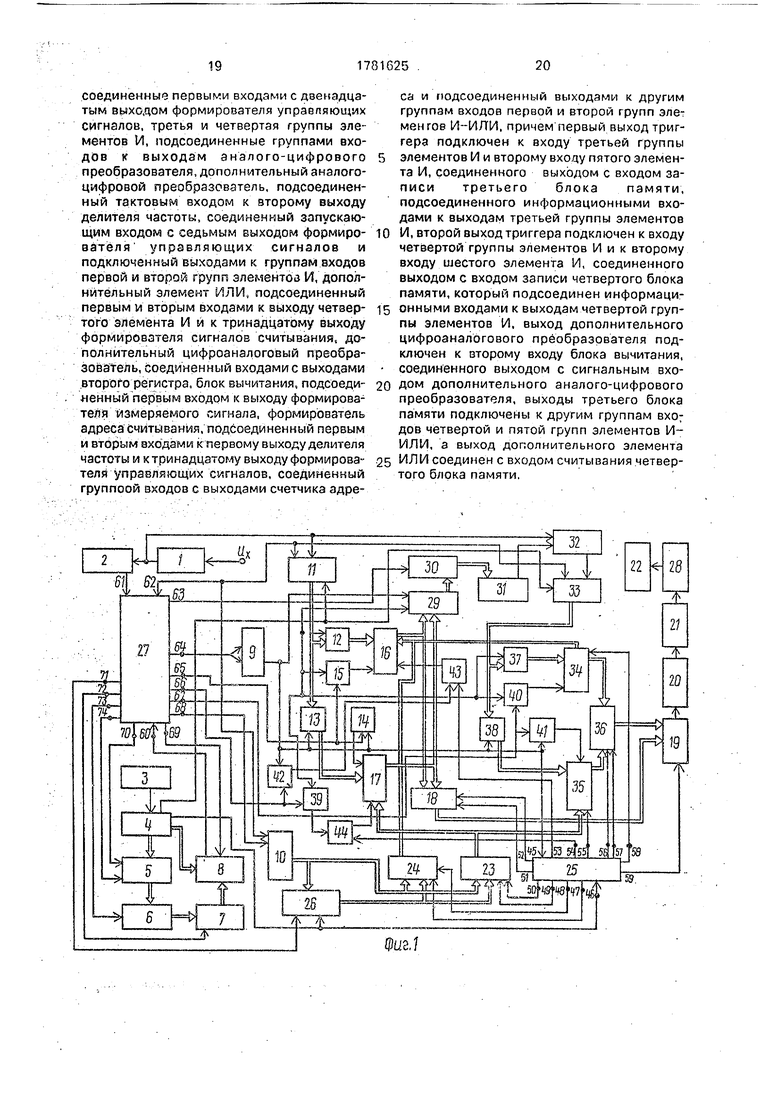

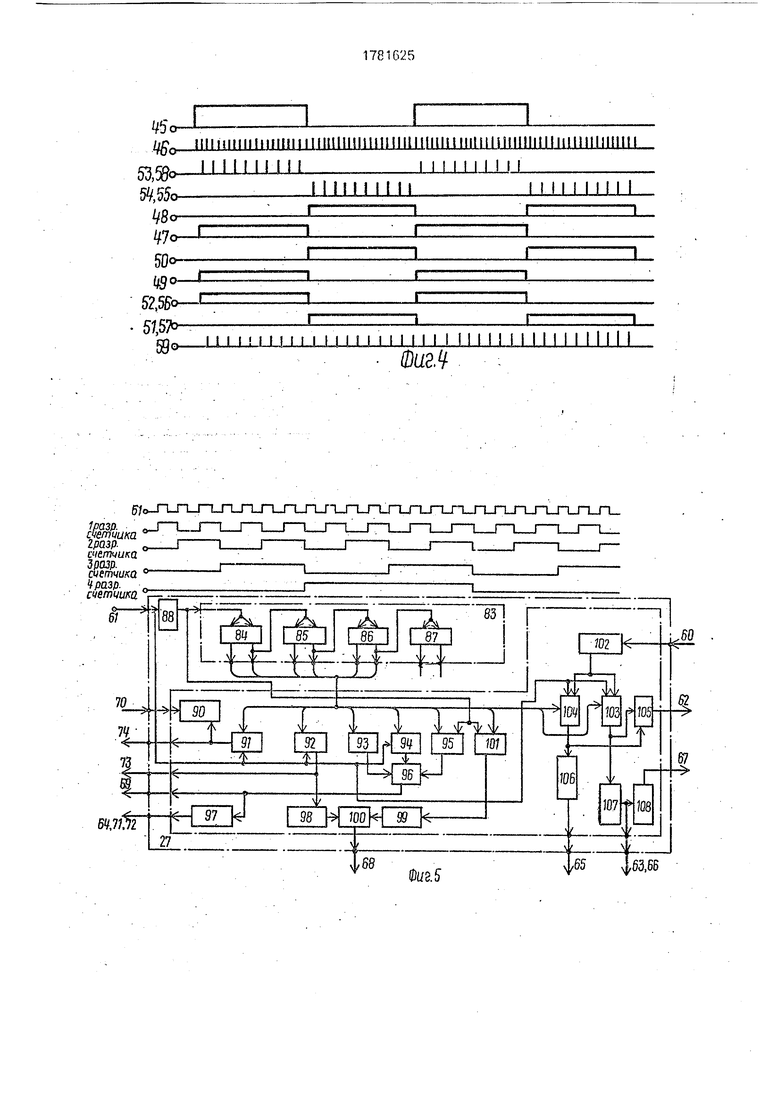

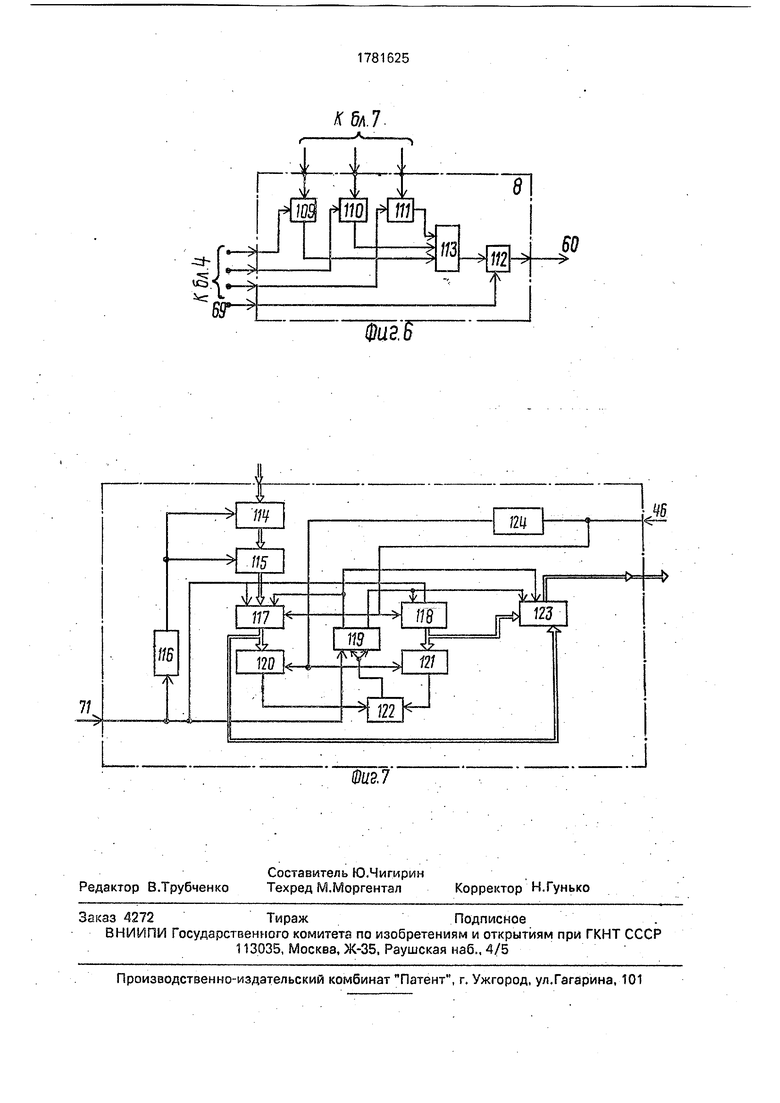

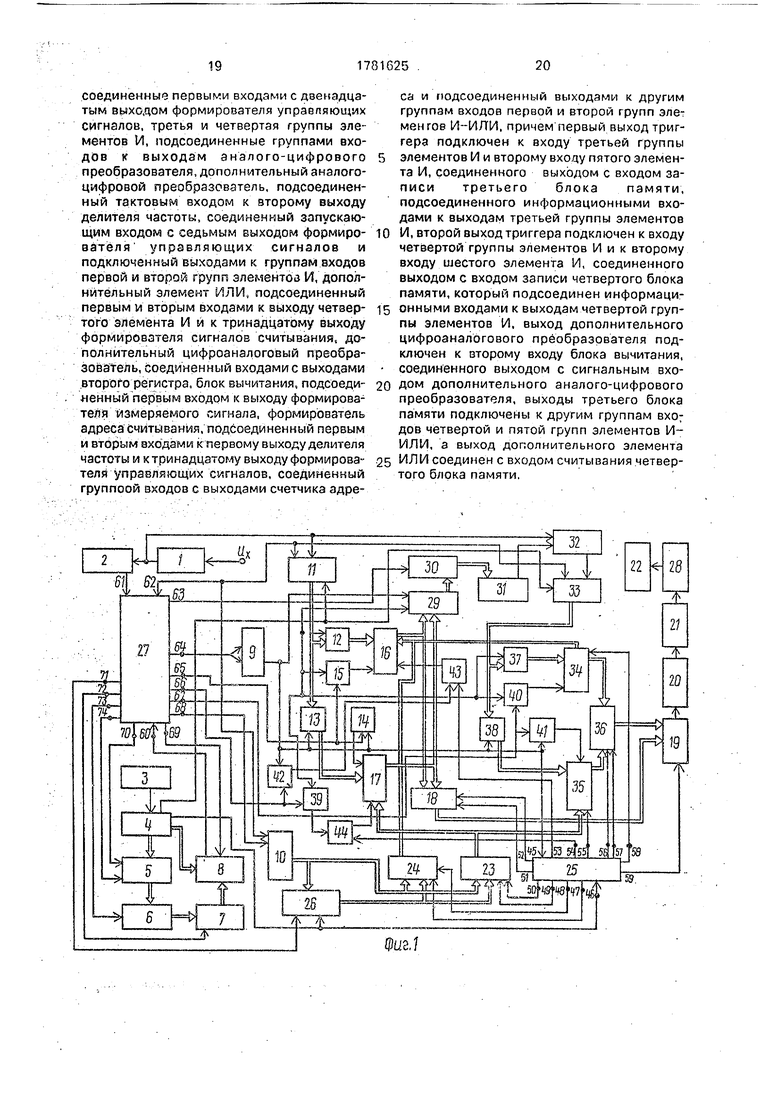

Иа фиг. 1 приведена блок-схема предлагаемого устройства для измерения средне- квздратического значения сигнала; на фиг. 2 - временные диаграммы работы формирователя управляющих сигналов; на фиг. 3блок-схема формирователя сигналов считывания; на фиг. 4 - временные диаграммы работы формирователя сигналов считывания; на фиг. 5 - блок-схема формирователя управляющих сигналов; на фиг. 6 - блок-схе- ма формирователя интерсала записи; на фиг. 7 - блок-схема формирователя адреса считывания.

Предлагаемое устройство для измерения среднеквадратического значения сигнала состоит из формирователя измеряемого сигнала 1, формирователя импульсов перехода через ноль 2, генератора импульсов 3, делителя частоты 4, счетчика 5, дешифратора 6, регистра 7, формирователя интервала записи 8, триггера 9, счетчика адреса 10, аналого-цифрового преобразователя 11, групп элементов И 12, 13, элементов И 14, 15, блоков памяти 16, 17, группы элементов И-ИЛИ 18, регистра 19, цифроаналогового преобразователя 20, формирователя сред- неквадратических значений 21, блока регистрации 22, групп элементов И-ИЛИ 23, 24, формирователя сигналов считывания 25, формирователя адреса считывания 26, формирователя управляющих сигналов 27, делителя 28, групп элементов И-ИЛИ 29, регистра 30, цифроаналогового преобразователя 31, блока вычитания 32, аналого-цифрового преобразователя 33, блоков памяти 34, 35, групп элементов И-ИЛИ 36, групп элементов И 37, 38, элементов И 39, 40, 41, 42 и элементов ИЛИ 43,44.

Формирователь сигналов считывания 25 имеет два входа 45,46 и тринадцать выходов 47-59, Формирователь управляющих сигналов 27 имеет два входа 60-61 и тринадцать выходов 62-74,

Формирователь сигналов считывания 28 (фиг.З) состоит из делителя частоты 75, элемента И 76, элемента задержки 77, элемента НЕ 78, элементов И 79, 80, элементов НЕ 81,82. На фиг. 4 показаны временные диаграммы работы формирователя сигналов считывания 25.

Формирователь управляющих сигналов 27 (фиг.5) состоит из счетчика 83, включающего триггера 84,85,86,87, элемента НЕ 88 и дешифратора 89, включающего формирователь длительности 90, элементы И 91-95, элемент ИЛИ 96, формирователи длительности 97-99, элемент ИЛИ 100, элемент И 101, формирователь длительности 102, элементы И 103, 104, элемент ИЛИ 105 и эле- мент.-i задержки 106-108. На фиг. 2 показаны временные диаграммы работы формирователя управляющих сигналов 27.

Формирователь интервала записи 8 (фиг.6) состоит из элементов И 109-112 и элемента ИЛИ 113,

Формирователь адреса считывания 26 (фиг,7) состоит из регистра 114, группы элементов И 115, элемента задержки 116, реверсивных счетчиков 117,118, триггера 119, элементов И 120, 121, элемента ИЛИ 122, группы элементов И-ИЛИ 123 и элемента задержки 124.

Вход устройства соединен с входом формирователя измеряемого сигнала 1. Выход формирователя измеряемого сигнала 1

соединен с входом формирователя импульсов перехода через ноль 2, измерительным входом аналого-цифрового преобразователя 11 и первым входом блока вычитания 32. Выход формирователя импульсов перехода через ноль 2 соединен с первым входом 61 формирователя управляющих сигналов 27. Выход генератора импульсов 3 соединен с входом делителя частоты 4. Первый выход делителя частоты 4 соединен со счетным входом счетчика 5. Второй выход делителя частоты 4 соединен с первым 46 входом формирователя сигналов считывания 25 и первым входом формирователя адреса считывания 26. Третий выход делителя частоты 4 соединен с тактовым входом аналого-цифрового преобразователя 11 и тактовым входом аналого-цифрового преобразователя 33. Четвертые выходы делителя частоты 4 соединены с первыми входами формирователя интервала записи 8. Нулевой вход счетчика 5 соединен с первым выходом формирователя управляющих сигналов 27, второй 74 выход которого соединен с входом разрешения счетчика 5. Выходы счетчика 5 соединены с первыми входами дешифратора 6, второй вход которого соединен с третьим 73 выходом формирователя управляющих сигналов 27. Выходы дешифратора 6 соединены с входами регистра 7, выходы которого соединены со вторыми входами формирователя интервала записи 8, второй вход которого соединен с четвертым 69 выходом формирователя управляющих сигналов 27. Выход формирователя интервала записи 8 соединены с вторым 60 входом формирователя управляющих сигналов 27. Второй вход регистра 7 соединен с пятым 72 выходом формирователя управляющих сигналов 27.

Счетный вход триггера 9 соединен с шестым 64 выходом формирователя управляющих сигналов 27. Первый выход триггера 9 соединен с первым входом группы элементов И-ИЛ1Л 29, с первыми входами групп элементов И 12, 37 и первыми входами элементов И 15, 39, 40. Второй выход триггера 9 соединен с вторым входом группы элементов И-ИЛИ 29, с первыми входами групп элементов И 13, 38, первыми входами элементов И 14, 41, 42 и вторым 45 входом формирователя сигналов считывания 25.

Нулевой вход счетчика адреса 10 соединен с седьмым 68 выходом формирователя управляющих сигналов 27. Счетный вход счетчика адреса 10 соединен с восьмым 62 выходом формирователя управляющих сигналов 27, запускающим входом аналого- цифрового преобразователя 11 и запускающим входом аналого-цифрового

преобразователя 33. Выходы аналого-цифрового преобразователя 11 соединены со вторыми входами групп элементов И 12, 13. Выходы групп элементов И 12 соединены с

информационными входами блока плмяти 16. Выходы групп элементов И 13 соединены с информационными входами блока памяти 17. Вторые входы элементов И 14, 15 соединены с девятым 65 выходом формиро0 вателя управляющих сигналов 27. Выход элемента И 14 соединен с входом записи блока памяти 17. Выход элемента И 15 соединен с входом записи блока памяти 16. Адресные входы блока памяти 16 соеди5 нены с выходами группы элементов И-ИЛИ 24 и адресными входами блока памяти 34. Адресные входы блока памяти 17 соединены с выходами группы элементов И-ИЛИ 23 и адресными входами блока памяти 35. Вход х

0 считывания блока памяти 16 соединен с выходом элемента ИЛИ 43. Вход считывания блока памяти 17 соединен с выходом элемента ИЛИ 44. Выходы блока памяти 16 соединены с первыми входами групп эле5 ментов И-ИЛИ 18 и третьими входами группы элементов И-ИЛИ 29, четвертые входы которой соединены с выходами блока памяти 17 и вторыми входами групп элементов И-ИЛИ 18.

0 Третий вход групп элементов И-ИЛИ 18 соединен с первым 51 выходом формирователя сигналов считывания 25, второй 52 вход которого соединен с четвертым входом группы элементов И-ИЛИ 18. Выходы груп5 пы элементов И-ИЛИ 18 соединены с первыми информационными входами регистра 19, управляющий вход которого соединен с третьим 59 выходом формирователя сигна- .- лов считывания 25.

0 Выходы регистра 19 соединены с информационными входами цифроаналогово- го преобразователя 20, выход которого через формирователь среднеквадратиче- ских значений 21 и усилитель 28 соединен с

5 блоком регистрации 22.

Первый вход группы элементов И-ИЛИ 23 соединен с четвертым 49 выходом формирователя сигналов считывания 25, пятый 50 выход которого соединен с вторым вхо0 дом группы элементов И-ИЛИ 23.Третьи ( / входы группы элементов И-ИЛИ 23 соединены с третьими входами группы элементов / И-ИЛИ 24, адресными входами формирова- теля адреса считывания 26 и выходами счет5 чика адреса 10. Четвертые входы группы элементов И-УЛИ 23 соединены с четвертыми входами группы элементов И-ИЛИ 24 и выходами формирователя адреса считывания 26. Первый вход группы элементов И- ИЛИ 24 соединен с шестым 47 выходом

iJ OpMUfiOfVHRJiH СИГН.ЬМЯ) С, СЧЫПЛМ I 25,

сядьмоп 4В выход нотрого г. вторым влодс м группы j/icMfUiTon И- ИЛИ 24.

Восьмой 54 выход Формирователя сигналов считывания 25 соединен с первым входом элемента ИЛИ 44. Девятый 55 выход формирователя сигналов считывания 25 соединен с входом считывания блока памяти 35. Десятый 56 выход формирователя сигналов считывания 25 соединен с первым входом группы элементов И-ИЛИ 35, второй вход которой соединен с одиннадцатым 57 выходом формирователя сигналов считывания 25. Двенадцатый 58 выход формирователя сигналов считывания 25 соединен с входом считывания блока памяти 34. Тринадцатый 53 выход формирователя сигналов считывания 25 соединен с первым входом схемы ИЛИ 43.

Десятый 71 выход формирователя управляющих сигналов 27 соединен с входом записи формирователя адреса считывания 26. Одиннадцатый 66 выход формирователя управляющих сигналов 27 соединен с первыми входами элементов И 39. 42. Двенадцатый 67 выход формирователя управляющих сигналов 27 соединен с первыми входами элементов И 40, 41. Тринадцатый 63 выход формирователя управляющих сигналов 27 соединен с управляющим входом регистра 30.

Выходы групп элементов И-ИЛИ 29 соединены с информационными входами регистра 30. Информационные выходы регистра 30 соединены с. входами цифроа- налогового преобразователя 31. Выход цифроаналогового преобразователя 31 соединен с вторым входом блока вычитания 32, выход которого соединен с измерительным входом аналого-цифрового преобразователя 33.

Выходы аналого-цифрового преобразователя 33 соединены с вторыми входами групп элементов И 37, 38.

Информационные входы блока памяти

34соединены с выходами группы схем И 37. Вход записи блока памяти 34 соединен с выходом элемента И 40. Выходы блока памяти 34 соединены с третьими входами группы элементов И-ИЛИ 36, четвертые входы которой соединены с выходами блока памяти 35. Информационные входы блока памяти 35 соединены с выходами группы элементов И 38. Вход записи блока памяти

35соединен с выходом элемента И 41.

Выход элемента И 39 соединен с вторым входом элемента ИЛИ 44. Выход элемента И 42 соединен со вторым nxorn-f элемента ИЛИ 43. Выходы IPV

тов И-ИЛИ 36 соединены с вторыми информационными входами регистра 19.

Работа устройства дня измерения сред- неквадратического значения сигнала происходит следующим образом.

Переменный сигнал Ux с формирователя измеряемого сигнала 1 поступает на формирователь импульсов перехода через ноль 2 и измерительный вход аналого-цифрового

0 преобразователя 11. По входным сигналам формирователя импульсов перехода через ноль 2, поступающим на 61 вход, формирователь управляющих сигналов 27 вырабатывает сигналы, синхронизирующие работу

5 всего устройства. Временные положения сигналов формирователя управляющих сигналов 27 показаны на фиг. 2.

С помощью генератора импульсов 3, делителя частоты 4, счетчика 5, дешифратора

0 6, регистра 7 и формирователя интервала записи 8 вырабатываются сигналы запуска аналого-цифрового преобразователя 11.

Счетчик 5 подсчитывает число импульсов, которые вырабатываются генератором

5 импульсов 3 и делителем частоты 4 за один период входного сигнала. Для этого счетчик 5 устанавливается в нулевое состояние сигналом, поступающим с выхода 70 формирователя управляющих сигналов и

0 подсчитывает импульсы, поступающие на него за един период входного напряжения. Разрешение на прохождение импульсов на счетчик 5 поступает с выхода 74 формирователя управляющих сигналов 27. Показания

5 счетчика 5 анализируются дешифратором 6 и при наличии управляющего сигнала на выходе 73 формирователя управляющего сигнала 27 дешифратор 6 выдает сигнал на регистр 7, который в нем запоминается.

0 Формирователь интервала записи 8 по состоянию регистра 7 и соответствующим этим состояниям сигналам делителя частоты 4 формирует сигналы определенной частоты, которые поступают на вход 60

5 формирователя управляющих сигналов 27. По этим сигналам формирователь управляющих сигналов 27 вырабатывает сигналы запуска аналого-цифрового преобразователя 11 и аналого-цифрового преобразоателя

0 33, которые с выхода 62 формирователя управляющих сигналов 27 поступают на запуск аналого-цифровых преобразователей 11, 33.

Информация, преобразованная анало5 го-цифровым преобразователем 11 (старшие разряды кода) в i период входного сигнала, поочередно поступает на блоки памяти 16, 17. Разделение этой информации г.г,о/.; д /тся триггером 9, управление

: f. с- .„ ч

щим на его счетный вход с выхода 64 формирователя управляющих сигналов 27.

Управляющий сигнал с первого выхода триггера 9 разрешает прохождение информации с выхода аналого-цифрового преобразователя 11 через группу элементов И 12 на информационный вход блока памяти 16. На информационный вход блока памяти 17 информация с выхода аналого-цифрового преобразователя 11 не поступает, поскольку на группу элементов И 13 поступает запрещающий потенциал с второго выхода триггера 9.

На адресный вход блока памяти 1 б в это время поступает код счетчика адреса 10, который формирует адрес записи, подсчитывая сигналы запуска аналого-цифрового преобразователя 11. Код адреса записи, сформированный счетчиком адреса 10, через группу элементов И-ИЛИ 24 поступает на адресный вход блока памяти 16. Запись информации в блок памяти 16 производится по сигналу, поступающему с 65 выхода формирователя управляющих сигналов 27. который проходит через элемент И 15 на вход записи блока памяти 16.

В это время с блоков памяти 17, 35 считывается информация (коды старших и младших разрядов), поступающая с них в предыдущем такте. Формирователь адреса считывания 26 из адреса записи, сформированного счетчиком адреса 10, вырабатывает адрес для непрерывного считывания информации (старших и младших разрядов) с блоков памяти 17, 35, необходимой для восстановления переменного входного сигнала. Адрес считывания, сформированный формирователем адреса считывания 26, через группу элементов И-ИЛИ 23 поступает на адресные входы блоков памяти 17,35. По сигналу считывания, поступающему с выхода элемента ИЛИ 44, на который поступает управляющий сигнал с 54 выхода формирователя сигналов считывания 25, с блока па- мяти 17 через группу элементов И-ИЛИ 18 поступает информация на первые входы регистра 19. В это время управление прохождением сигналов через группы элементов И-ИЛИ 18, 23 осуществляется сигналами с 50, 51 выходов формирователя сигналов считывания 25. На вторые информационные входы регистра 19 по сигналу на 59 выходе формирователя сигналов считывания 25 через группу элементов И-ИЛИ 36 поступает информация с блока памяти 35, разрешающий сигнал на прохождение информации через группу элементов И-ИЛИ 36 поступает с выхода 57 формирователя сигналов считывания 25. Запись информации в регистр 19 производится управляющим сигналом,

поступающим с 59 выхода формирователя сигналов считывания 25. После восстановления переменного входного сигнала цифро-аналоговым преобразователем 20

производится преобразование этого сигнала преобразователем среднеквадратиче- ских значений 21 и индикация результатов измерения блоком регистрации 22.

В последующий (1+1) период входного

0 напряжения производится кодирование сигнала, сформированного блоком вычитания 32 и цифро-аналоговым преобразователем 31. На один вход блока вычитания 32 поступает входной сигнал Ux после форми5 рователя измеряемого сигнала 1. На второй вход блока вычитания 32 поступает восстановленный аналоговый сигнал, закодированный аналого-цифровым преобразователем 11 в I период входного сигнала.

0 В (i+1) период входного сигнала производится считывание информации, хранящейся Б блоке памяти 16 по сигналам, поступающим через элемент ИЛИ 43 с элемента И 42 в момент поступления сигналов

5 с 66 выхода формирователя управляющих сигналов 27.

Эта информация, пройдя через группу элементов И-ИЛИ 29, запоминается в регистре 30, а затем поступает на цифро-анало0 говый преобразователь 31, где преобразуется в аналоговый сигнал, поступающий на второй вход блока вычитания 32. Разностный сигнал Ди Uex-ицдп (где UBX - входной сигнал, УЦАП восстановлен5 ный входной сигнал) поступает на аналого- цифровой преобразователь 33.

По сигналу запуска, поступающему с 62 выхода формирователя управляющих сигналов 27, в аналого-цифровом преобразовате:

0 леЗЗ производится кодирование выходного сигнала блока вычитания 32.

Управляющий сигнал с первого выхода триггера 9 разрешает прохождение кодовой информации с выхода аналого-цифрового

5 преобразователя 33 через группу элементов И 37 на информационный вход блока памяти 34. На информационный вход блока памяти 35 кодовая информация с выхода аналого- цифрового преобразователя 33 не поступа0 ет, поскольку на группу элементов И 38 поступает запрещающий потенциал с второго выхода триггера 9.

На адресный вход блока памяти 34 в это время поступает код адреса со счетчика ад5 реса 10, который формирует адрес записи, подсчитывая сигналы запуска аналого-цифрового преобразователя 33. Код адреса записи, сформированный счетчиком адреса, через группу элементов И-ИЛИ 24 поступает на адресный вход блока памяти 34. Запись информации в блок памяти 34 производится по сигналу, поступающему с 67 выхода формирователя управляющих сигналов 27, который проходит через элемент И 40 на вход записи блока памяти 34.

При поступлении второго импульса на счетный вход триггера 9 с формирователя управляющих сигналов 27 он изменяет свое состояние. При этом запись информации производится в блок памяти 17, а считыаа- ние информации производится с блоков памяти 16, 34. В этом случае информация с выхода аналого-цифрового преобразователя 11 через группу элементов И 13 поступает на информационный вход блока памяти 17, поскольку на второй вход группы элементов И 13 поступает разрешающий потенциал с второго выхода триггера 9. Код адреса, сформированный счетчиком адреса io, через группу элементов И-ИЛИ 23 по- ступает ни адресный вход блока памяти 17. Запись информации в блок памяти 17 производится по сигналу, поступающему с 65 выхода формирователя управляющих сигналов через элемент И 14 на вход записи блока памяти 17,

В это же время с блоков памяти 16, 34 считывается информация, поступившая в них в предыдущем цикле. Адрес считывания, сформированный формирователем адреса считывания 25,через группу элементов И- ИЛИ 24 поступает на адресный вход блока памяти 16. По сигналу считывания, поступающему с выхода элемента ИЛИ 43, информация с-блока памяти 13 через группу элементов И-ИЛИ 18 поступает на первые информационные входы регистра 19. На вторые информационные входы регистра 19 по сигналу считывания на 56 выходе формирователя сигналов считывания 25 через группу элементов И-ИЛИ 36 поступает информация с блока памяти 34.

В последующем цикле работы устройства производится считывание информации, хранящейся в блоке памяти 17, по сигналам, поступающим через элемент ИЛИ 44 с элемента И 39, в момент поступления сигналов с 66 выхода формирователя управляющих сигналов 27. Эта информация, пройдя через группу элементов И-ИЛИ 29, запоминается в регистре 30, а затем поступает на цифро- аналоговый преобразователь 31, где преобразуется в аналоговый сигнал, поступающий на второй вход блока вычитания 32.

По сигналу запуска, поступающему с 62 выхода формирователя управляющих сиг- налов27, в аналого-цифровом преобразователе 33 производится кодирование выходного сигнала блока вычитания 32.

Управляющий сигнал с второго выхода триггера 9 разрешает прохождение информации с выхода аналого-цифрового преобразователя 33 на информационный вход блока памяти 35. На информационный вход блока памяти 34 информация с выхода аналого-цифрового преобразователя 33 не поступает, поскольку на группу элементов И 37 поступает запрещающий потенциал с первого выхода триггера 9.

На адресный вход блока памяти 35 в это время поступает код адреса со счетчика адреса 10, который формирует адрес записи, подсчитывая сигналы запуска аналого-цифрового преобразователя 33, Код адреса записи, сформированный счетчиком адреса 10, через группу элементов И-ИЛИ 33 поступает на адресный вход блока памяти 35. Запись информации в блок памяти 35 производится по сигналу, поступающему с выхода 67 формирователя управляющих сигналов 27, который проходит через элемент И 41 на вход записи блока памяти 35

Цифровая информация, хранящаяся в регистре 19, преобразуется цифроакалого- вым преобразователем 20 в переменный сигнал. Этот сигнал после преобразователя среднеквадратических значений 21 и делителя 28 поступает на блок регистрации 22.

Заявляемый объект обладает техническими преимуществами по сравнению с прототипом, уменьшением на порядок до (0,1-0,2)% погрешности измерения в широком частотном диапазоне. Это обусловлено тем, что кодирование входного сигнала производится поэтапно. В i период входного напряжения кодируются старшие разряды, а в (1+1) период - младшие разряды.

В Институте электродинамики АН УССР изготовлен макет вольтметра переменного напряжения, реализующий структуру предлагаемого устройства для измерения сред- неквадратического значения сигнала. ;

Техническая документация на заявляемое i/.зобретение выполнена на уровне эскизных чертежей, позволяющих воспроизвести предлагаемое устройство дляч измерения средчеквадратич еского значения сигнала.

Формула изобр.етения

Устройство для измерения среднеквад- ратического значения сигнала, содержащее формирователь измеряемого сигнала, подсоединенный входом к входной шкале, формирователь среднеквадратического значения, выход которого соединен через усилитель с входом блока регистрации, первый регистр и дешифратор, подсоединенные входами соответственно к первому и второму выходам формирователя управляющих сигналов, счетчик, соединенный нулеBUM входом и входом разрешения соответственно с третьим и четвертым выходами формирователя управляющих сигналов, второй регистр, подсоединенный управляющим входом к пятому выходу формирователя управляющих сигналов, первый и второй элементы И, соединенные первыми входами с шестым выходом формирователя управляющих сигналов, аналого-цифровой преобразователь, подсоединенный запускающим входом к седьмому выходу формирователя управляющих сигналов, счетчик адреса, соединенный нулевым входом с восьмым выходом формирователя управляющих сигналов, триггер, подсоеДийейный счетным входом к девятому выходу формирователя управляющих сигналов, формирователь интервала записи, соединенный входом и выходом соответственно с десятым выходов и первым входом формирователя управляющих сигналов, формирователь импульсов перехода через ноль, включенный между выходом формирователя измеряемого сигнала и вторым входом формирователя управляющих сигналов, цифроаналоговый преобразователь, подключенный выходом к входу формирователя среднеквадратиче- ского значения, формирователь сигналов считывания, третий регистр, третий и четвертый элементы И, первая, вторая, третья, четвертая и пятая группы элементов И- ИЛИ, первая и вторая группы элементов И, первый и второй блоки памяти, делитель частоты, генератор импульсов и элемент ИЛИ, причем формирователь управляющих сигналов подключен седьмым выходом к счетному входу счетчика адреса, соединенного выходами с первыми группами входов первой и второй групп элементов И-ИЛИ, выход делителя частоты соединен с первым входом формироватепя сигналов считывания, который подключен первым, вторым и третьим выходами к входу третьего регистра и к входам счи гывания первого и второго блоков памяти, соединен четвертым и пятым выходами с первым и вторым входами первой группы элементов И-ИЛИ, подключен шестым и седьмым выходами к первому и второму входам второй элементов И- ИЛИ, соединен восьмым и девятым выходами с первым и вторым входами третьей группы э И-ИЛИ и подсоединен вторым вход. 1 к первому выходу триггера, соединному с выходом первой группы элементов И и с вторым входом первого элемента И, подключенного выходом к входу записи первого блока памяти, который подсоединен адресными входами к выходам |Ц,эиой группы элементов И-ИЛИ и соеди- . ч ормационными входами с выходами

первой группы элементов И, выходы второй группы элементов И соединены с информационными входами второго блока памяти, который соединен адресными входами с выходами второй группы элементов И-ИЛИ и подсоединен входом записи к выходу второго элемента И, соединенного вторым входом с вторым выходом триггера, подключенным к входу второй группы эле0 ментов И, вход цифроаналогового преобразователя подсоединен к выходу третьего регистра, соединенного информационными входами с выходами третьей группы эле- менто й И-ИЛИ, подсоединенной первой и

5 второй группами входов к, выходам соответственно первого и второго блоков памяти, а выход формирователя измеряемого сигнала соединен с измерительным входом аналого- цифрового преобразователя, подсоединен0 ного тактовым входом к второму выходу делителя частоты, который соединен входом с выходом генератора импульсов, подключен третьем выходом к счетному входу счетчика и соединен группой выходов с пер5 вой группой входов формирователя интервала записи, подсоединенного второй группой входов к выходам первого регистра, соединенного группой входов с выходами дешифратора, группа входов которого

0 подсоединена к выходам счетчика, отличающееся тем, что, с целью повышения точности измерения, дополнительно введены третий блок памяти, подсоединенный адресными входами к выходам первой группы

5 элементов И-ИЛИ и соединен входом считывания с выходом элемента ИЛИ, подсоединенного первым входом к десятому выходу формирователя сигналов считывания и соединенного вторым входом с выхо0 дом третьего элемента И, первый вход которого подсоединен к одиннадцатому выходу формирователя управляющих сигналов, подключенному к перво му входу четвертого элемента И, соединенного вто5 рым входом с первым выходом триггера, подключенным к первому входу четвертой группы элементов И-ИЛИ. соединенного выходами с информационными входами второго регистра и подсоединенного вто0 рым входом к второму выходу триггера, соединенному с вторым входом третьего элемента И, четвертый блок памяти, подключенный выходами к входам четвертой группы элементов И-ИЛИ и к входам пятой

5 группы элементов И-ИЛИ, соединенной-вы- ходами с другой группой входов третьего регистра и подсоединенной первым и вторым входами к одиннадцатому и двенадцатому выходам формирователя сигналов считывания, пятый и шестой элементы И,

соединенные первыми входами с двенадцатым выходом формирователя управляющих сигналов, третья и четвертая группы элементов И, подсоединенные группами входов к выходам аналого-цифрового преобразователя, дополнительный аналого- цифровой преобразователь, подсоединенный тактовым входом к второму выходу делителя частоту, соединенный запускающим входом с седьмым выходом формирователя управляющих сигналов и подключенный выходами к группам входов первой и второй групп элементов И, дополнительный элемент 1/1Л1Л, подсоединенный первым и вторым входами к выходу четвертого элемента И и к тринадцатому выходу формирователя сигналов считывания, дополнительный цифроаналоговый преобразователь, соединенный входами с выходами второго регистра, блок вычитания, подсоединенный первым входом к выходу формирователя измеряемого сигнала, формирователь адреса считывания, подсоединенный первым и вторым входами к первому выходу делителя частоты и х тринадцатому выходу формирователя управляющих сигналов, соединенный группоой входов с выходами счетчика адреса и подсоединенный выходами к другим группам входов первой и второй групп элементов И--ИЯИ. причем первый выход триггера подключен к входу третьей группы

элементов И и второму входу пятого элемента И, соединенного выходом с входом записи третьего блока памяти, подсоединенного информационными входами к выходам третьей группы элементов

И, второй выход триггера подключен к входу четвертой группы элементов И и к второму входу шестого элемента И, соединенного выходом с входом записи четвертого блока памяти, который подсоединен информационными входами к выходам четвертой группы элементов И, выход дополнительного цифроаналогового преобразователя подключен к второму входу блока вычитания, соединенного выходом с сигнальным входом дополнительного аналого-цифрового преобразователя, выходы третьего блока памяти подключены к другим группам вхо: дов четвертой и пятой групп элементов И- ИЛИ, а выход дополнительного элемента

ИЛИ соединен с входом считывания четвертого блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1986 |

|

SU1327174A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1990 |

|

SU1771533A3 |

| Устройство для многоканальной записи аналоговых процессов | 1985 |

|

SU1304070A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1561075A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Измерительный прибор | 1989 |

|

SU1661653A1 |

Изобретение относится к электрическим измерениям и позволяет проводить высокоточные измерения в широком частотном диапазоне переменных сигналов произвольной формы. Сущность изобретения: высокая точность измерения достигается за счет устранения частотной составляющей погрешности, что достигается изменением спектра входного сигнала, в результате чего измерение входного сигнала производится в узком фиксированном частотном диапазоне. 7 ил.

Фиг,/

4R

NЈ

55$5Ч

(Шг.3

5 2Л(Ц

il m .;........... ,«:

| | 1 | I I I I I I I 1 I I 1 IMill ГТТТТГПТТГП-°№

°№

ГПГП I I I I IГТПТПТП

|11111 111111тттттттгтштптгтштгтпттшт1Ш°

-°5/7

дам

тпншзм tJevdt,

0 ОУЛЛШЗ/р t/OTf

0 плшэ/ з dfvdl

аупли/эл7 asvai

°№

SMISil

Кбл7

Фагь

48

Физ.7

| Хлистунов В.М | |||

| Основы цифровой электроизмерительной техники | |||

| М.-Л.: Энергия, 1966 | |||

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-12-15—Публикация

1990-06-01—Подача