Х| 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1675935A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1993 |

|

RU2069018C1 |

| Устройство для отображения информации на газоразрядной индикаторной панели переменного тока | 1989 |

|

SU1793458A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для обработки информации | 1981 |

|

SU993262A1 |

| Устройство для отображения информации на матричном индикаторе | 1989 |

|

SU1783573A1 |

| Устройство для отображения информации | 1987 |

|

SU1424052A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1992 |

|

RU2042216C1 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

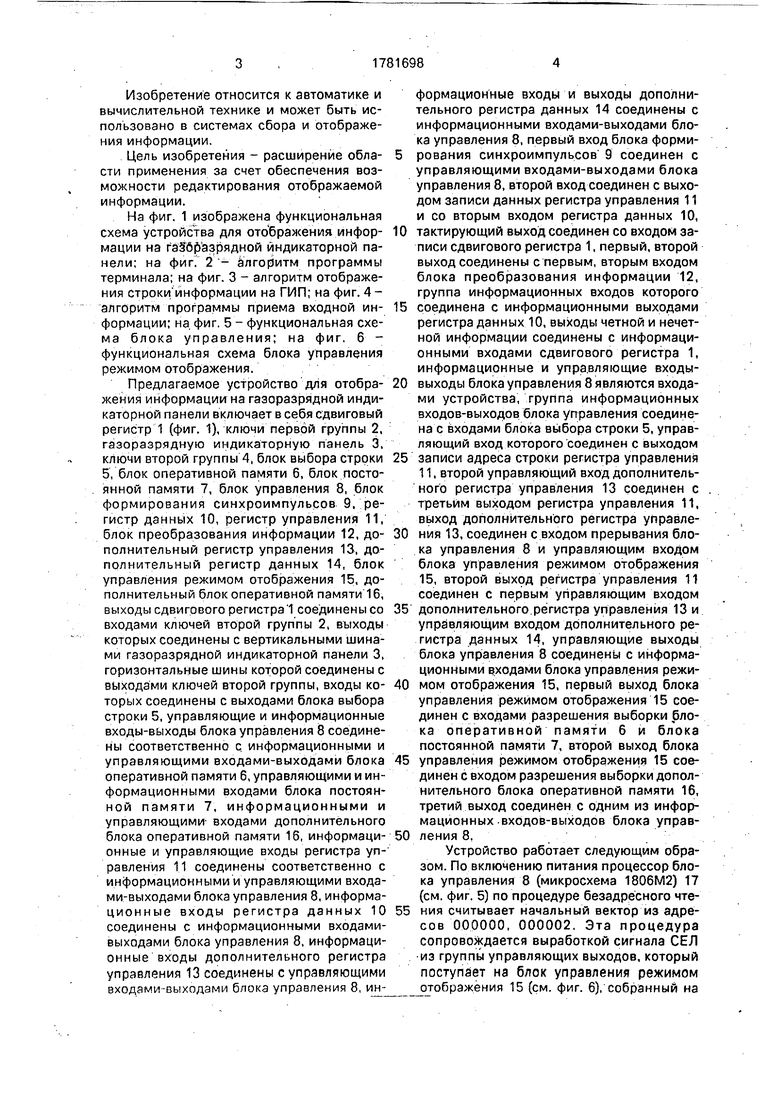

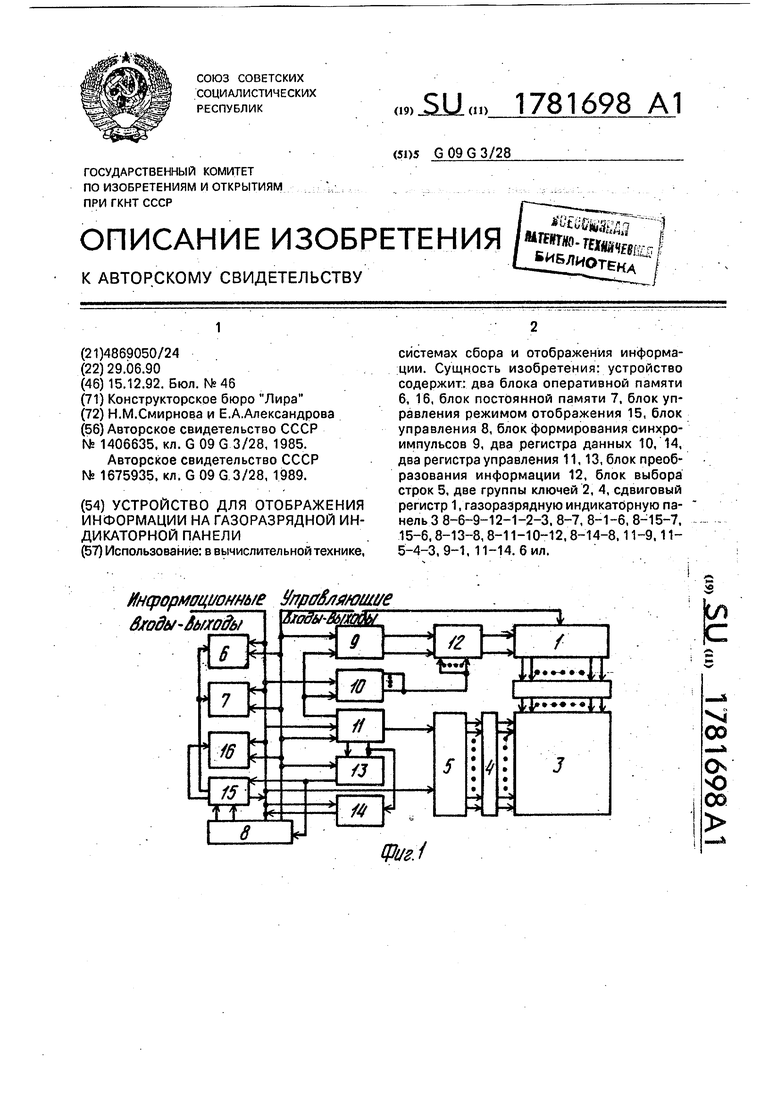

Использование: в вычислительной технике, системах сбора и отображения информации. Сущность изобретения: устройство содержит: два блока оперативной памяти 6, 16, блок постоянной памяти 7, блок управления режимом отображения 15, блок управления 8, блок формирования синхроимпульсов 9, два регистра данных 10, 14, два регистра управления 11,13, блок преобразования информации 12, блок выбора строк 5, две группы ключей 2, 4, сдвиговый регистр 1, газоразрядную индикаторную панель 3 8-6-9-12-1-2-3, 8-7, 8-1-6, 8-15-7, 15-6,8-13-8, 8-11-10-12,8-14-8,11-9.11- 5-4-3,9-1, 11-14. бил.

®№.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах сбора и отображения информации.

Цель изобретения - расширение области применения за счет обеспечения возможности редактирования отображаемой информации.

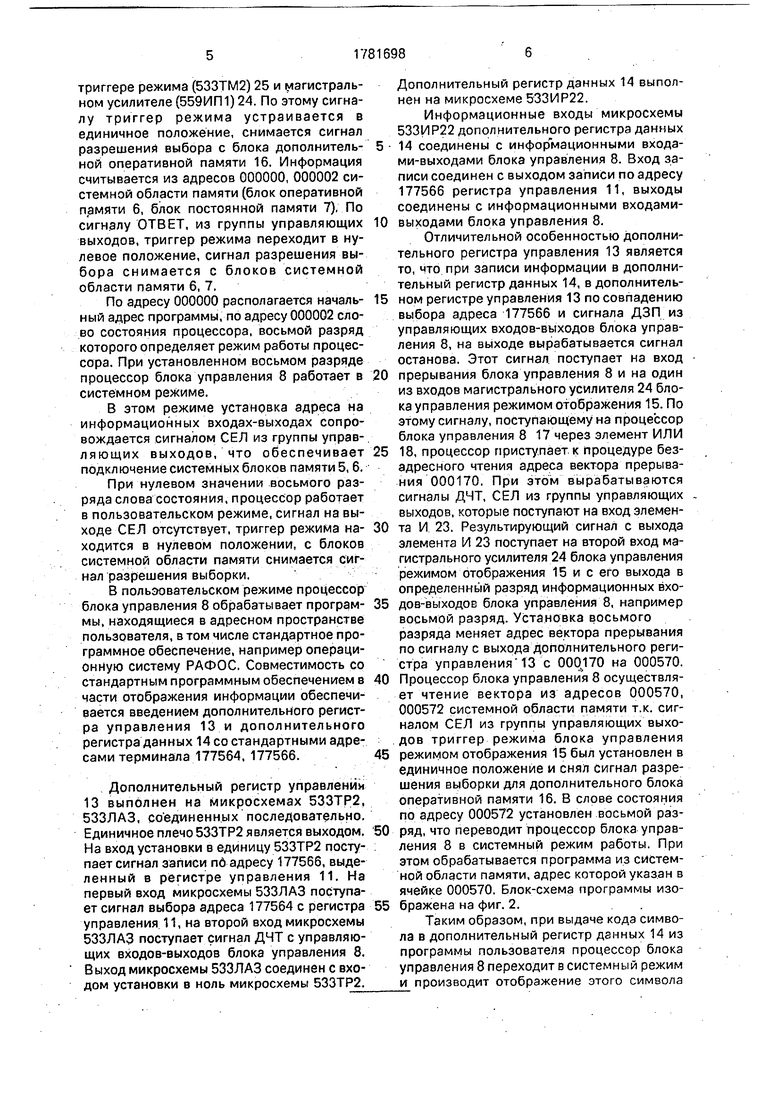

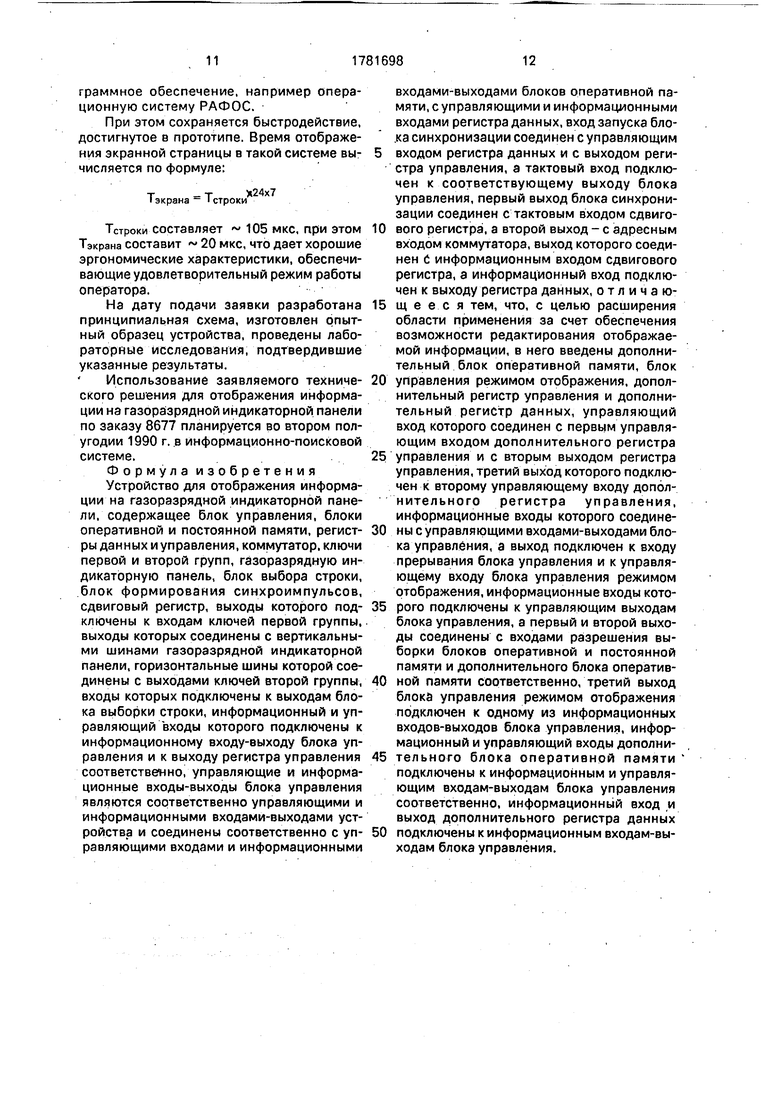

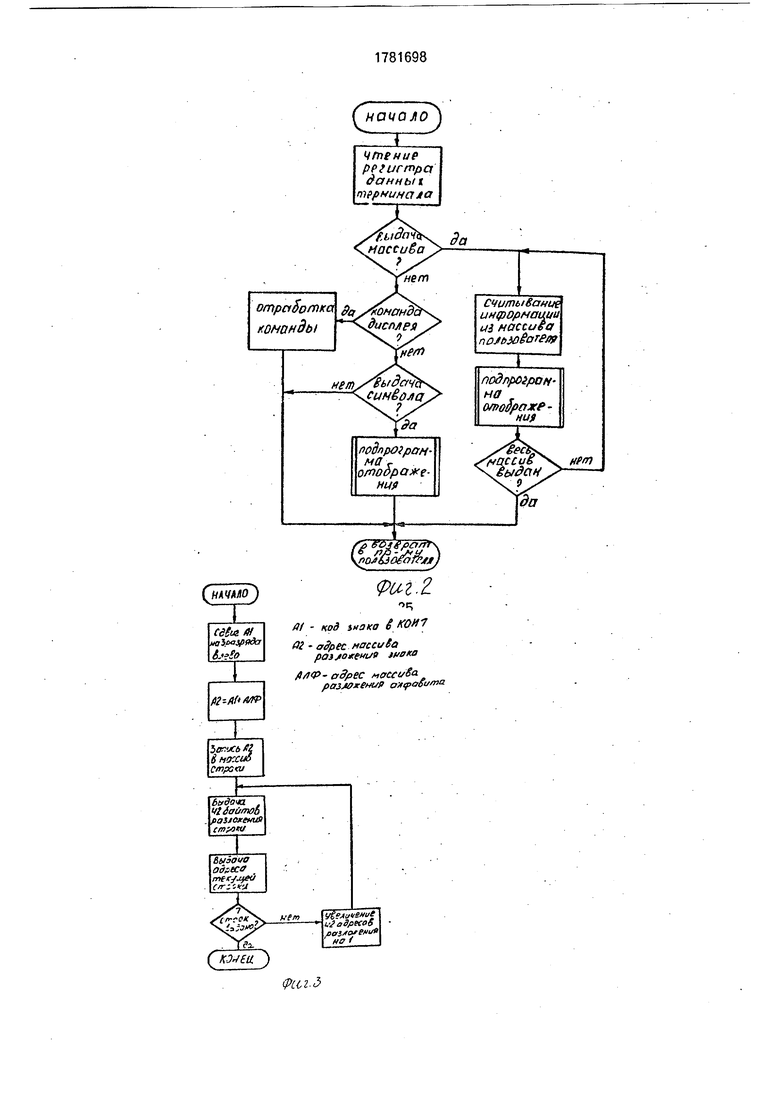

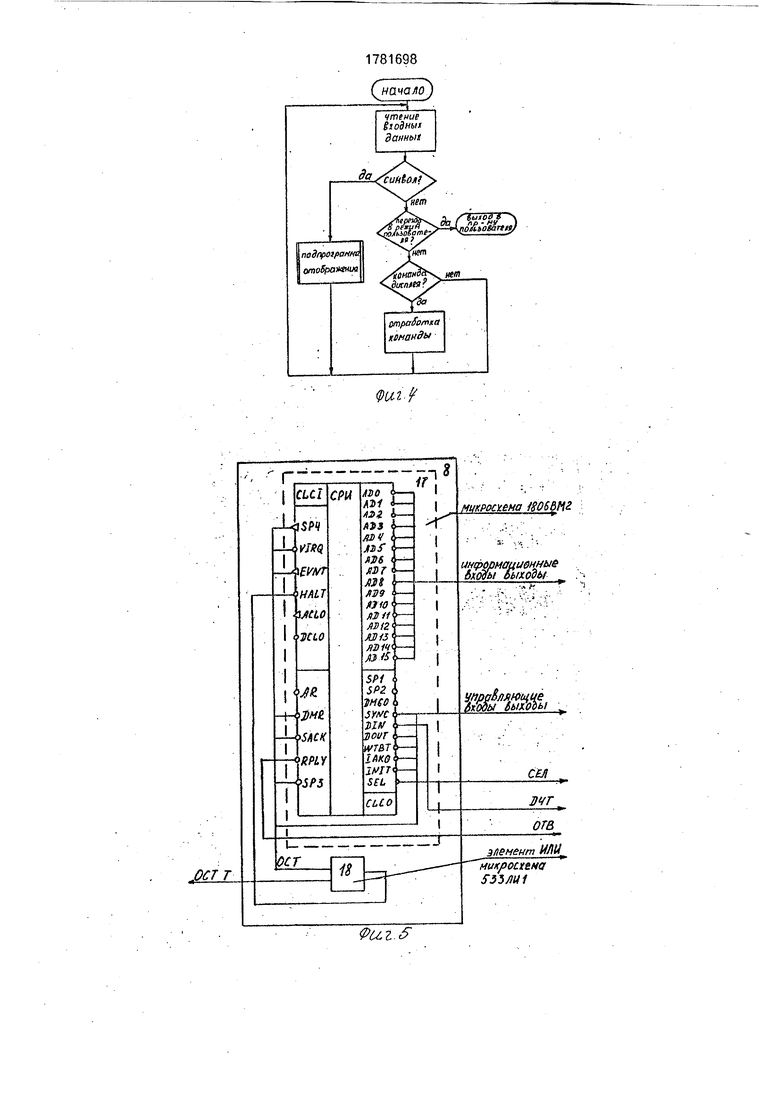

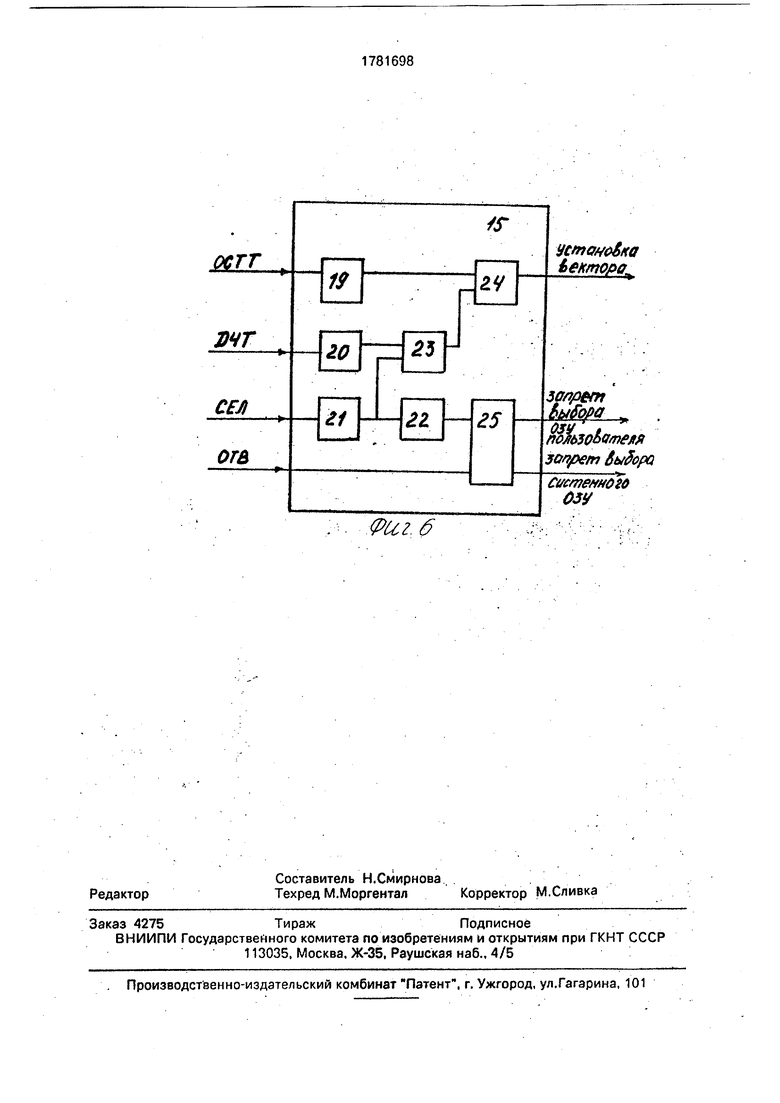

На фиг. 1 изображена функциональная схема устройства для отображения информации на гэ§бразрядной индикаторной панели; на фиг. 2 - алгоритм программы терминала; на фиг. 3 - алгоритм отображения строки информации на ГИП; на фиг. 4 - алгоритм программы приема входной информации; на фиг. 5 - функциональная схема блока управления; на фиг. 6 - функциональная схема блока управления режимом отображения.

Предлагаемое устройство для отображения информации на газоразрядной индикаторной панели включает в себя сдвиговый регистр 1 (фиг. 1), ключи первой группы 2, газоразрядную индикаторную панель 3, ключи второй группы 4, блок выбора строки 5, блок оперативной памяти 6, блок постоянной памяти 7, блок управления 8, блок формирования синхроимпульсов 9, регистр данных 10, регистр управления 11, блок преобразования информации 12, дополнительный регистр управления 13, дополнительный регистр данных 14, блок управления режимом отображения 15, дополнительный блок оперативной памяти 16, выходы сдвигового регистра 1 соединены со входами ключей второй группы 2, выходы которых соединены с вертикальными шинами газоразрядной индикаторной панели 3, горизонтальные шины которой соединены с выходами ключей второй группы, входы которых соединены с выходами блока выбора строки 5, управляющие и информационные входы-выходы блока управления 8 соединены соответственно с информационными и управляющими входами-выходами блока оперативной памяти 6, управляющими и информационными входами блока постоянной памяти 7, информационными и управляющими входами дополнительного блока оперативной памяти 16, информационные и управляющие входы регистра управления 11 соединены соответственно с информационными и управляющими входами-выходами блока управления 8, информа- ционные входы регистра данных 10 соединены с информационными входами- выходами блока управления 8, информационные входы дополнительного регистра управления 13 соединены с управляющими входами-выходами блока управления 8, информационные входы и выходы дополнительного регистра данных 14 соединены с информационными входами-выходами блока управления 8, первый вход блока формирования синхроимпульсов 9 соединен с управляющими входами-выходами блока управления 8, второй вход соединен с выходом записи данных регистра управления 11 и со вторым входом регистра данных 10,

0 тактирующий выход соединен со входом записи сдвигового регистра 1, первый, второй выход соединены с первым, вторым входом блока преобразования информации 12, группа информационных входов которого

5 соединена с информационными выходами регистра данных 10, выходы четной и нечетной информации соединены с информационными входами сдвигового регистра 1, информационные и управляющие входы0 выходы блока управления 8 являются входами устройства, группа информационных входов-выходов блока управления соединена с входами блока выбора строки 5, управляющий вход которого соединен с выходом

5 записи адреса строки регистра управления 11, второй управляющий вход дополнительного регистра управления 13 соединен с третьим выходом регистра управления 11, выход дополнительного регистра управле0 ния 13, соединен с входом прерывания блока управления 8 и управляющим входом блока управления режимом отображения 15, второй выход регистра управления 11 соединен с первым управляющим входом

5 дополнительного регистра управления 13 и управляющим входом дополнительного регистра данных 14, управляющие выходы блока управления 8 соединены с информационными входами блока управления режи0 мом отображения 15, первый выход блока управления режимом отображения 15 соединен с входами разрешения выборки блока оперативной памяти 6 и блока постоянной памяти 7, второй выход блока

5 управления режимом отображения 15 соединен с входом разрешения выборки дополнительного блока оперативной памяти 16, третий выход соединен с одним из информационных входов-выходов блока управ0 ления 8.

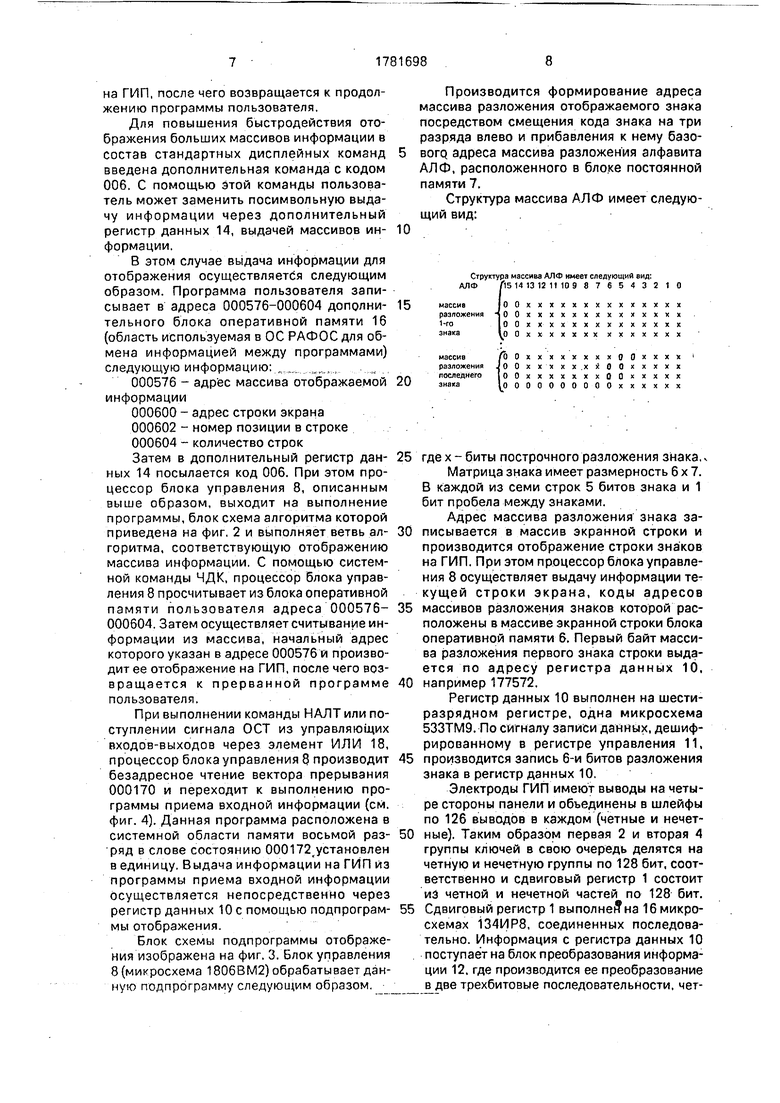

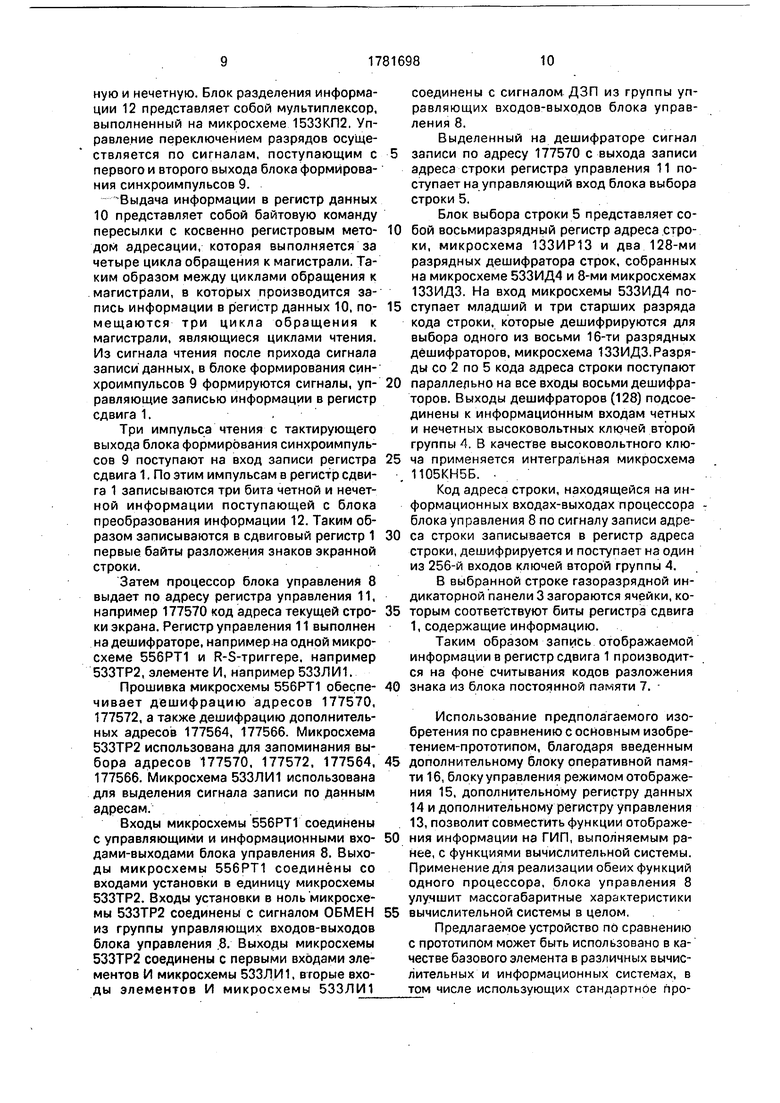

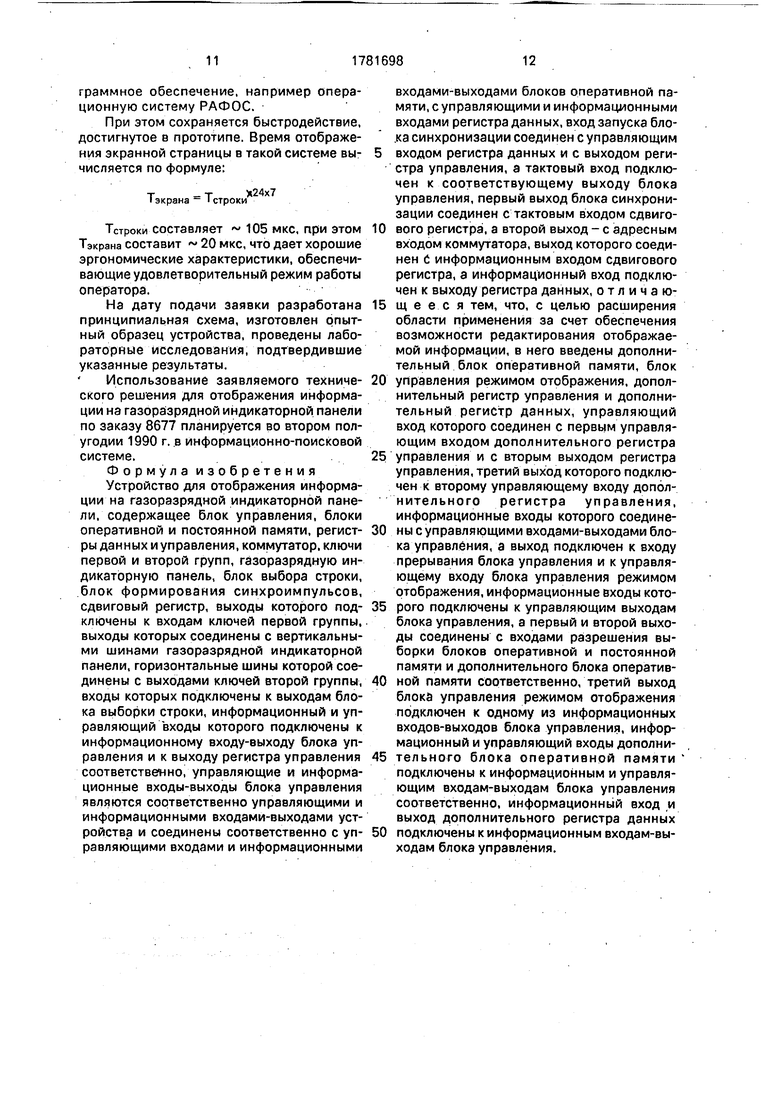

Устройство работает следующим образом. По включению питания процессор блока управления 8 (микросхема 1806М2) 17 (см. фиг. 5) по процедуре безадресного чте5 ния считывает начальный вектор из адресов 000000, 000002, Эта процедура сопровождается выработкой сигнала СЕЛ из группы управляющих выходов, который поступает на блок управления режимом отображения 15 (см. фиг. 6), собранный на

триггере режима (533ТМ2) 25 и магистраль- ном усилителе (559ИП1) 24. По этому сигналу триггер режима устраивается в единичное положение, снимается сигнал разрешения выбора с блока дополнитель- ной оперативной памяти 16, Информация считывается из адресов 000000, 000002 системной области памяти (блок оперативной памяти 6, блок постоянной памяти 7), По сигналу ОТВЕТ, из группы управляющих выходов, триггер режима переходит в нулевое положение, сигнал разрешения выбора снимается с блоков системной области памяти 6, 7.

По адресу 000000 располагается началь- ный адрес программы, по адресу 000002 слово состояния процессора, восьмой разряд которого определяет режим работы процессора. При установленном восьмом разряде процессор блока управления 8 работает в системном режиме.

В этом режиме установка адреса на информационных входах-выходах сопровождается сигналом СЕЛ из группы управляющих выходов, что обеспечивает подключение системных блоков памяти 5,6.

При нулевом значении восьмого разряда слова состояния, процессор работает в пользовательском режиме, сигнал на выходе СЕЛ отсутствует, триггер режима на- ходится в нулевом положении, с блоков системной области памяти снимается сигнал разрешения выборки.

В пользовательском режиме процессор блока управления 8 обрабатывает програм- мы, находящиеся в адресном пространстве пользователя, в том числе стандартное программное обеспечение, например операционную систему РАФОС. Совместимость со стандартным программным обеспечением в части отображения информации обеспечивается введением дополнительного регистра управления 13 и дополнительного регистра данных 14 со стандартными адресами терминала 177564, 177566.

Дополнительный регистр управлении 13 выполнен на микросхемах 533ТР2, 533ЛАЗ, соединенных последовательно. Единичное плечо 533ТР2 является выходом. На вход установки в единицу 533ТР2 поступает сигнал записи по адресу 177566, выделенный в регистре управления 11. На первый вход микросхемы 533ЛАЗ поступает сигнал выбора адреса 177564 с регистра управления 11, на второй вход микросхемы 533ЛАЗ поступает сигнал ДЧТ с управляющих входов-выходов блока управления 8. Выход микросхемы 533ЛАЗ соединен с входом установки в ноль микросхемы 533ТР2.

Дополнительный регистр данных 14 выполнен на микросхеме 533ИР22.

Информационные входы микросхемы 533ИР22 дополнительного регистра данных 14 соединены с информационными входами-выходами блока управления 8. Вход записи соединен с выходом записи по адресу 177566 регистра управления 11, выходы соединены с информационными входами- выходами блока управления 8.

Отличительной особенностью дополнительного регистра управления 13 является то, что при записи информации в дополнительный регистр данных 14, в дополнительном регистре управления 13 по совпадению выбора адреса 177566 и сигнала ДЗП из управляющих входов-выходов блока управления 8, на выходе вырабатывается сигнал останова. Этот сигнал поступает на вход прерывания блока управления 8 и на один из входов магистрального усилителя 24 блока управления режимом отображения 15. По этому сигналу, поступающему на процессор блока управления 8 17 через элемент ИЛИ 18, процессор приступает к процедуре безадресного чтения адреса вектора прерывания 000170. При этом вырабатываются сигналы ДЧТ, СЕЛ из группы управляющих выходов, которые поступают на вход элемента И 23. Результирующий сигнал с выхода элемента И 23 поступает на второй вход магистрального усилителя 24 блока управления режимом отображения 15 и с его выхода в определенный разряд информационных входов-выходов блока управления 8, например восьмой разряд. Установка восьмого разряда меняет адрес вектора прерывания по сигналу с выхода дополнительного регистра управления 13 с 000170 на 000570. Процессор блока управления 8 осуществляет чтение вектора из адресов 000570, 000572 системной области памяти т.к. сигналом СЕЛ из группы управляющих выходов триггер режима блока управления режимом отображения 15 был установлен в единичное положение и снял сигнал разрешения выборки для дополнительного блока оперативной памяти 16. В слове состояния по адресу 000572 установлен восьмой разряд, что переводит процессор блока управления 8 в системный режим работы, При этом обрабатывается программа из системной области памяти, адрес которой указан в ячейке 000570. Блок-схема программы изображена на фиг. 2.

Таким образом, при выдаче кода символа в дополнительный регистр данных 14 из программы пользователя процессор блока управления 8 переходит в системный режим и производит отображение этого символа

на ГИП, после чего возвращается к продолжению программы пользователя.

Для повышения быстродействия отображения больших массивов информации в состав стандартных дисплейных команд введена дополнительная команда с кодом 006. С помощью этой команды пользователь может заменить посимвольную выдачу информации через дополнительный регистр данных 14, выдачей массивов информации.

В этом случае выдача информации для отображения осуществляется следующим образом. Программа пользователя записывает в адреса 000576-000604 дополнительного блока оперативной памяти 16 (область используемая в ОС РАФОС для обмена информацией между программами) следующую информацию:

000576 - адрес массива отображаемой информации

000600 - адрес строки экрана

000602 - номер позиции в строке

000604 - количество строк

Затем в дополнительный регистр данных 14 посылается код 006. При этом процессор блока управления 8, описанным выше образом, выходит на выполнение программы, блок схема алгоритма которой приведена на фиг, 2 и выполняет ветвь алгоритма, соответствующую отображению массива информации. С помощью системной команды ЧДК, процессор блока управления 8 просчитывает из блока оперативной памяти пользователя адреса 000576- 000604. Затем осуществляет считывание информации из массива, начальный адрес которого указан в адресе 000576 и производит ее отображение на ГИП, после чего воз- вращается к прерванной программе пользователя.

При выполнении команды НАЛТ или поступлении сигнала ОСТ из управляющих входов-выходов через элемент ИЛИ 18, процессор блока управления 8 производит безадресное чтение вектора прерывания 000170 и переходит к выполнению программы приема входной информации (см. фиг. 4). Данная программа расположена в системной области памяти восьмой разряд в слове состоянию 000172густановлен в единицу. Выдача информации на ГИП из программы приема входной информации осуществляется непосредственно через регистр данных 10 с помощью подпрограммы отображения.

Блок схемы подпрограммы отображения изображена на фиг. 3. Блок управления 8 (микросхема 1806ВМ2) обрабатывает данную подпрограмму следующим образом.

Производится формирование адреса массива разложения отображаемого знака посредством смещения кода знака на три разряда влево и прибавления к нему базовогр адреса массива разложения алфавита АЛФ, расположенного в блоке постоянной памяти 7.

Структура массива АЛФ имеет следующий вид:

Структура массива АЛФ имеет следующий вид: АЛФ )31211109 8 7 6 5 4 3 2 1 О

массив разложения 1-го знака

ООххххххххххх ООххххххххххх ООххххххххххх ООххххххх хххх

массиви)0хххххххх00ххх

разложенияJOOxxxxxxxOOxxxx

последнегоJOOxxxxxxxOOxxxx

знакаloOOOOOOOOOxxxxx

где х - биты построчного разложения знака, ., Матрица знака имеет размерность 6x7. В каждой из семи строк 5 битов знака и 1 бит пробела между знаками.

Адрес массива разложения знака записывается в массив экранной строки и производится отображение строки знаков на ГИП, При этом процессор блока управления 8 осуществляет выдачу информации текущей строки экрана, коды адресов

массивов разложения знаков которой расположены в массиве экранной строки блока оперативной памяти 6. Первый байт массива разложения первого знака строки выдается по адресу регистра данных 10,

например 177572,

Регистр данных 10 выполнен на шестиразрядном регистре, одна микросхема 533ТМ9. По сигналу записи данных, дешифрированному в регистре управления 11,

производится запись 6-и битов разложения знака в регистр данных 10.

Электроды ГИП имеют выводы на четыре стороны панели и объединены в шлейфы по 126 выводов в каждом (четные и нечетные). Таким образом первая 2 и вторая 4 группы ключей в свою очередь делятся на четную и нечетную группы по 128 бит, соответственно и сдвиговый регистр 1 состоит из четной и нечетной частей по 128 бит.

Сдвиговый регистр 1 выполнен на 16 микросхемах 134ИР8, соединенных последовательно. Информация с регистра данных 10 поступает на блок преобразования информации 12, где производится ее преобразование в две трехбитовые последовательности, четную и нечетную. Блок разделения информации 12 представляет собой мультиплексор, выполненный на микросхеме 1533КП2. Управление переключением разрядов осуществляется по сигналам, поступающим с первого и второго выхода блока формирования синхроимпульсов 9.

Выдача информации в регистр данных 10 представляет собой байтовую команду пересылки с косвенно регистровым методом адресации, которая выполняется за четыре цикла обращения к магистрали. Таким образом между циклами обращения к магистрали, в которых производится запись информации в регистр данных 10, помещаются три цикла обращения к магистрали, являющиеся циклами чтения. Из сигнала чтения после прихода сигнала записи данных, в блоке формирования синхроимпульсов 9 формируются сигналы, управляющие записью информации в регистр сдвига 1.

Три импульса чтения с тактирующего выхода блока формирования синхроимпульсов 9 поступают на вход записи регистра сдвига 1. По этим импульсам в регистр сдвига 1 записываются три бита четной и нечетной информации поступающей с блока преобразования информации 12. Таким образом записываются в сдвиговый регистр 1 первые байты разложения знаков экранной строки.

Затем процессор блока управления 8 выдает по адресу регистра управления 11, например 177570 код адреса текущей строки экрана. Регистр управления 11 выполнен на дешифраторе, например на одной микросхеме 556РТ1 и R-S-триггере. например 533ТР2, элементе И, например 533ЛИ1.

Прошивка микросхемы 556РТ1 обеспечивает дешифрацию адресов 177570, 177572, а также дешифрацию дополнительных адресов 177564, 177566. Микросхема 533ТР2 использована для запоминания выбора адресов 177570, 177572, 177564, 177566. Микросхема 533ЛИ1 использована для выделения сигнала записи по данным адресам.

Входы микросхемы 556РТ1 соединены с управляющими и информационными входами-выходами блока управления 8. Выходы микросхемы 556РТ1 соединены со входами установки в единицу микросхемы 533ТР2. Входы установки в ноль микросхемы 533ТР2 соединены с сигналом ОБМЕН из группы управляющих входов-выходов блока управления 8. Выходы микросхемы 533ТР2 соединены с первыми входами элементов И микросхемы 533ЛИ1, вторые входы элементов И микросхемы 533ЛИ1

соединены с сигналом ДЗП из группы управляющих входов-выходов блока управления 8.

Выделенный на дешифраторе сигнал 5 записи по адресу 177570 с выхода записи адреса строки регистра управления 11 поступает на управляющий вход блока выбора строки 5.

Блок выбора строки 5 представляет со0 бой восьмиразрядный регистр адреса строки, микросхема 133ИР13 и два 128-ми разрядных дешифратора строк, собранных на микросхеме 533ИД4 и 8-ми микросхемах 133ИДЗ. На вход микросхемы 533ИД4 по5 ступает младший и три старших разряда кода строки, которые дешифрируются для выбора одного из восьми 16-ти разрядных дешифраторов, микросхема 133ИДЗ,Разряды со 2 по 5 кода адреса строки поступают

0 параллельно на все входы восьми дешифраторов. Выходы дешифраторов (128) подсоединены к информационным входам четных и нечетных высоковольтных ключей второй группы 4. В качестве высоковольтного клю5 ча применяется интегральная микросхема . 1105КН5Б.

Код адреса строки, находящейся на информационных входах-выходах процессора блока управления 8 по сигналу записи адре0 са строки записывается в регистр адреса строки, дешифрируется и поступает на один из 256-й входов ключей второй группы 4.

В выбранной строке газоразрядной индикаторной панели 3 загораются ячейки, ко5 торым соответствуют биты регистра сдвига 1, содержащие информацию.

Таким образом запись отображаемой информации в регистр сдвига 1 производится на фоне считывания кодов разложения

0 знака из блока постоянной памяти 7.

Использование предполагаемого изобретения по сравнению с основным изобретением-прототипом, благодаря введенным

5 дополнительному блоку оперативной памяти 16, блоку управления режимом отображения 15, дополнительному регистру данных 14 и дополнительному регистру управления 13, позволит совместить функции отображе0 ния информации на ГИП, выполняемым ранее, с функциями вычислительной системы. Применение для реализации обеих функций одного процессора, блока управления 8 улучшит массогабаритные характеристики

5 вычислительной системы в целом,

Предлагаемое устройство по сравнению с прототипом может быть использовано в качестве базового элемента в различных вычислительных и информационных системах, в том числе использующих стандартное программное обеспечение, например операционную систему РАФОС.

При этом сохраняется быстродействие, достигнутое в прототипе. Время отображения экранной страницы в такой системе вычисляется по формуле:

Тэкрана строки

Тстроки составляет 105 мкс, при этом Тэкрана составит 20 мкс, что дает хорошие эргономические характеристики, обеспечивающие удовлетворительный режим работы оператора.

На дату подачи заявки разработана принципиальная схема, изготовлен опытный образец устройства, проведены лабораторные исследования, подтвердившие указанные результаты.

Использование заявляемого технического решения для отображения информации на газоразрядной индикаторной панели по заказу 8677 планируется во втором полугодии 1990 г. в информационно-поисковой системе.

Формула изобретения

Устройство для отображения информации на газоразрядной индикаторной панели, содержащее блок управления, блоки оперативной и постоянной памяти, регистры данных и управления, коммутатор, ключи первой и второй групп, газоразрядную индикаторную панель, блок выбора строки, блок формирования синхроимпульсов, сдвиговый регистр, выходы которого подключены к входам ключей первой группы, выходы которых соединены с вертикальными шинами газоразрядной индикаторной панели, горизонтальные шины которой соединены с выходами ключей второй группы, входы которых подключены к выходам блока выборки строки, информационный и управляющий входы которого подключены к информационному входу-выходу блока управления и к выходу регистра управления соответственно, управляющие и информационные входы-выходы блока управления являются соответственно управляющими и информационными входами-выходами устройства и соединены соответственно с управляющими входами и информационными

входами-выходами блоков оперативной памяти, с управляющими и информационными входами регистра данных, вход запуска блока синхронизации соединен с управляющим

входом регистра данных и с выходом регистра управления, а тактовый вход подключен к соответствующему выходу блока управления, первый выход блока синхронизации соединен с тактовым входом сдвигового регистра, а второй выход - с адресным входом коммутатора, выход которого соединен и информационным входом сдвигового регистра, а информационный вход подключен к выходу регистра данных, отличающ е е с я тем, что, с целью расширения области применения за счет обеспечения возможности редактирования отображаемой информации, в него введены дополнительный блок оперативной памяти, блок

управления режимом отображения, дополнительный регистр управления и дополнительный регистр данных, управляющий вход которого соединен с первым управляющим входом дополнительного регистра

управления и с вторым выходом регистра управления, третий выход которого подключен к второму управляющему входу дополнительного регистра управления, информационные входы которого соединены с управляющими входами-выходами блока управления, а выход подключен к входу прерывания блока управления и к управляющему входу блока управления режимом отображения, информационные входы которого подключены к управляющим выходам блока управления, а первый и второй выходы соединены с входами разрешения выборки блоков оперативной и постоянной памяти и дополнительного блока оперативной памяти соответственно, третий выход блока управления режимом отображения подключен к одному из информационных входов-выходов блока управления, информационный и управляющий входы дополнительного блока оперативной памяти подключены к информационным и управляющим входам-выходам блока управления соответственно, информационный вход и выход дополнительного регистра данных

подключены к информационным входам-выходам блока управления.

Фкг2.

°ц

at - код ьнако ё КОИ7

(К-адрес масса Sa роиюхеш

АЛФ- адрес MffCCt/Sa

o tpoSunja

{КЭг/еи. )

Фи Р

микросхема 1WRW.

Фиг Ј

остт

19

зчг

10

СЕЛ

ч-

11

ОГВ

М

yc/rtavojxff iexmopa

25

г5

заяр&п wfoPQ

пошо&ателя зофе/п быйора

Системного ОМ

Риг. б

| Устройство для отображения информации на газоразрядной индикаторной панели | 1985 |

|

SU1406635A1 |

| кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1675935A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1992-12-15—Публикация

1990-06-29—Подача