(54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления обменом | 1977 |

|

SU771655A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

| Многоканальное буферное запоминающее устройство | 1985 |

|

SU1280453A1 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Устройство для выборки команд | 1978 |

|

SU726533A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

Изобретение относится к вычиспитепь ной технике и может быть использовано в системах обработки информационных массивов переменного формата данных. Известны устройства для обработки информации, работающие с коротким машинным словом (8,12 иди 16 разрядов) Для адресации ячеек оперативной памяти в таких устройствах используются внут- римашинные nporpaMNJHO доступные регистры 1 . Все эти устройства ведут обработку данных только в формате полного слова. Наиболее близким по техническойсущности к предлагаемому является устройство для обработки инфор дации, содержащее оперативную память, Коммутатор, . сумматор-сдвигатепь, выходные элеме ты И и регистровую памятьj включающую восем.ь регистров общего назначения. Номер одного из восьми регистров определя ется тремя битами, указанными в команд ном слове. Кроме того, еще три бита команды 5гказывают один из восьми способов адресации, которые используются при ({армировании исполнительных адр©;сов операндов. Указанное устройство оперирует со словами (16 1 зрядов) и байтами (8 разрядов). Признак формата дачных (слово или байт) указывается в стар-шем разряде командного слова 21. Использование данного устройства для обработки операндов с длиной меньще восьми разрядов становится малоэффективным. В частности, при обработка маосиБОв цифровой информации (длина операв« да - четыре разряда) или битовых массивов такое устройство будет работать с меньшей производительностью при больших затратах оперативной памяти. Это связано с тем, что для реалвзашки в устройстве функций обработки цифровых и битовых массивов с помощью имеющегося набора команд необходимо напнсанве специальных программ, занимающих много места в оперативной памяти. Многежрат.

ное выполкешю этих программ значительно снижает производительность устройства.

Цель изобретения увеличетше проиаводитепьиости при обработке полей данных переменного формата.

Поставленная цетгь достигается тем, что в устройство для обработки информа- шт. содержащее блок оперативной памяти блок элементов И, коммутатор, сумматор и блок регистровой памяти, причем алросный вход и информационный выход блока оператир ой памяти подключены соответственно X адресному входу и информационному выходу устройства, выход блока элементов И соединен с выходом данных результата устройства, первый вход коммутатора подключен к выходу блснса регистровой памяти, а выход коммутатор® соединен с входом сумматора, выход результата которого подключен к входам блока элементов И и блока регистровой памяти, введены блок считывания данных ..переменного формата, блок записи данных переменного формата, регистр сдвига и дополнительный блок регистровой памяти, вход которого соединен с выходом результата сумматора, а выход - с первым входом коммутатора, вход регистра сдвига подключен к выходу переноса сумматора, а выход - к первым управляющим входам блоков считывания и записи данных переменного формата, вторые управляющие входы и информационные входы которых соединены соответственно с выходом

результата сумматора и входом данных переменного формата устройства, выходы блоков считывания и записи данных переменного формата подключены соответственно к второму входу коммутатора и информациоиному входу блока оперативной памяти..

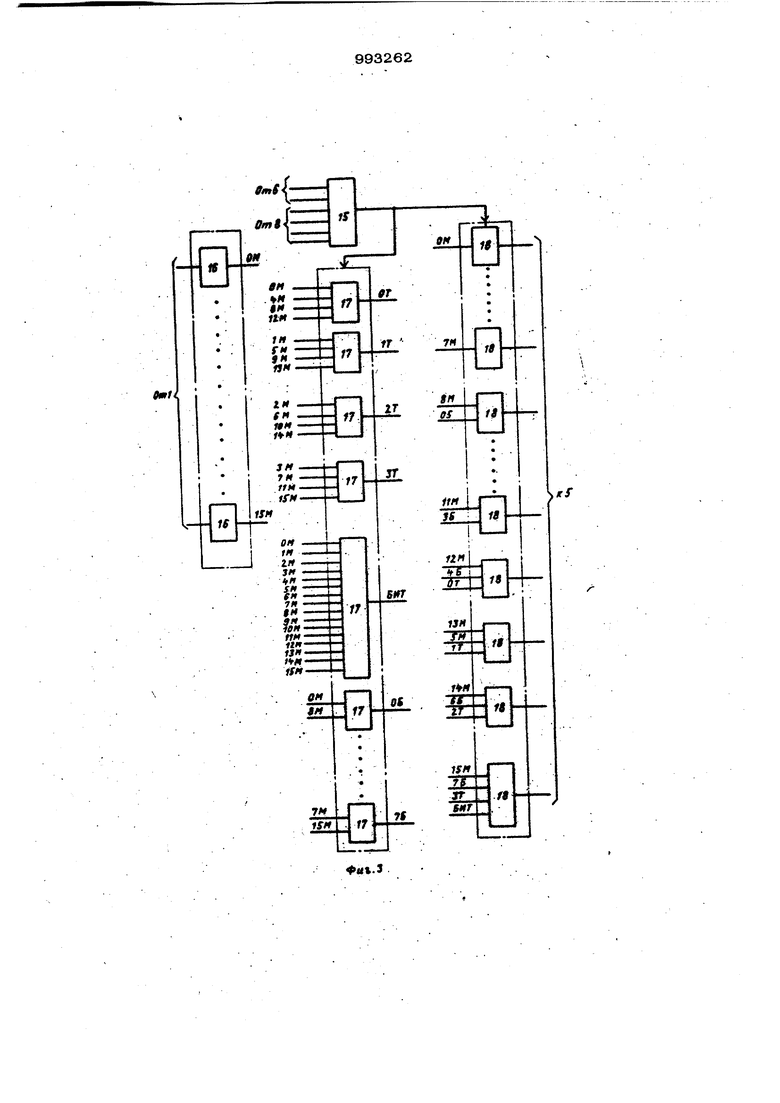

При этом блок считывания данных переменного формата содержит дешифратор, группу элементов НЕ и две группы элементов ИЛИ, причем входы элементов НЕ группы соединены с информационным входом, блока, а первые и вторые входы де- щифратора подключены к первому и второму управляющим входам блока, управляющие входы элементов ИЛИ первой и второй групп соединены соответственно с первым и вторым выходами дещифратора, входы элементов ИЛИ первой группы подключены к соответствующим выходам элементов НЕ 1 руппы, а их выходы соединейы с соответствующими входами элементов ИЛИ второй группы, выходы которых подключены к выходу блока.

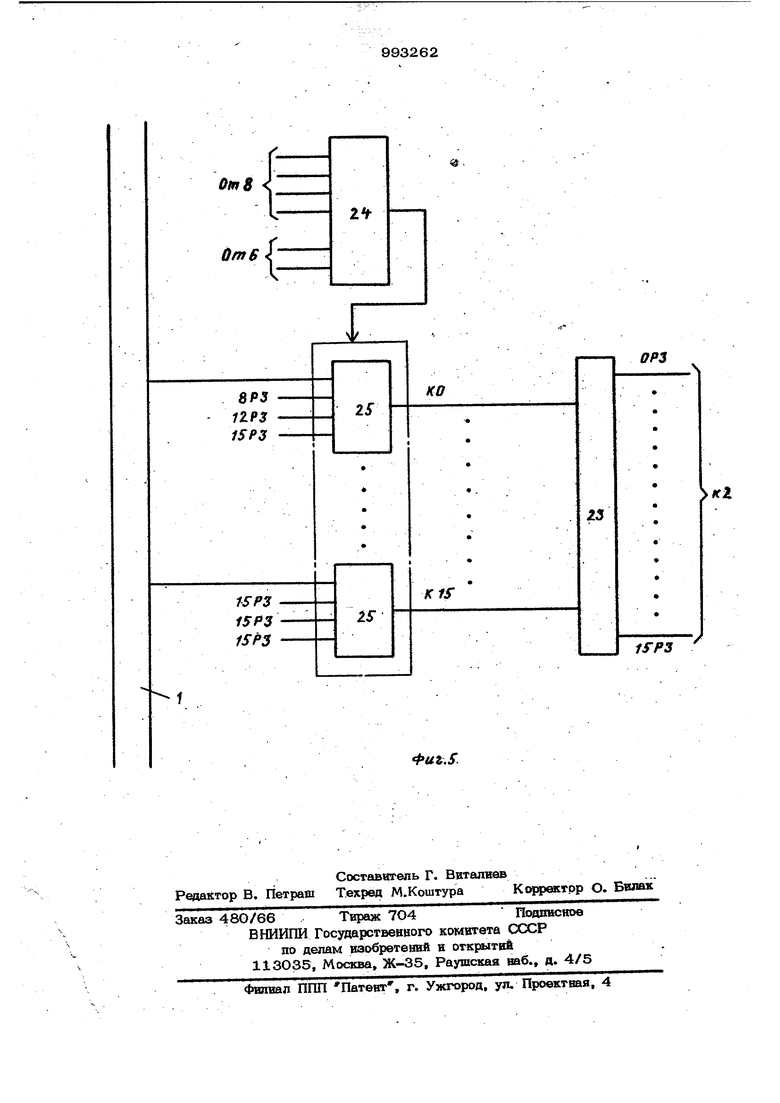

Кроме того, блок записи данных переменного формата содержит дешифратор, группу элементов ИЛИ и регистр записи числа, входы которого соединены с выходами соответствующих элементов ИЛИ группы, а выходы подключены к выходу блока, первые и вторые входы дешифратора соединены с первым и вторым управляющими входами блока, а выход дешиф{}атора подключен к управляющим входам эл ентов ИЛИ группы, входы которых соединены с информационным входом блока.

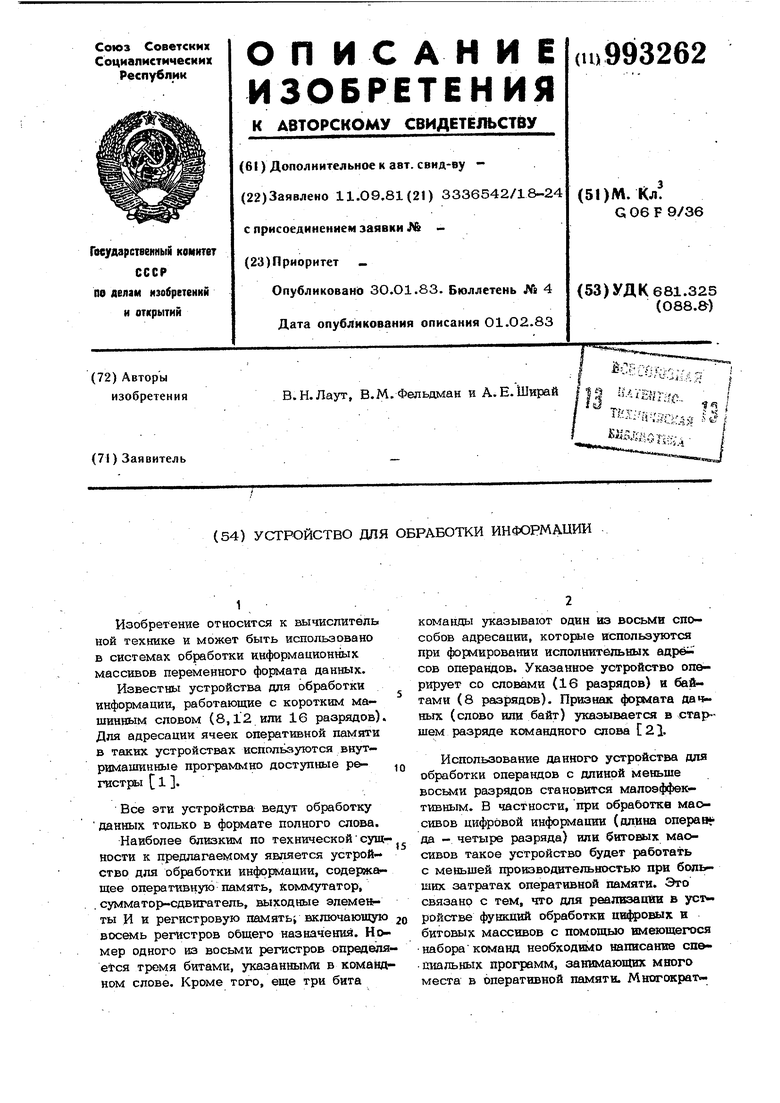

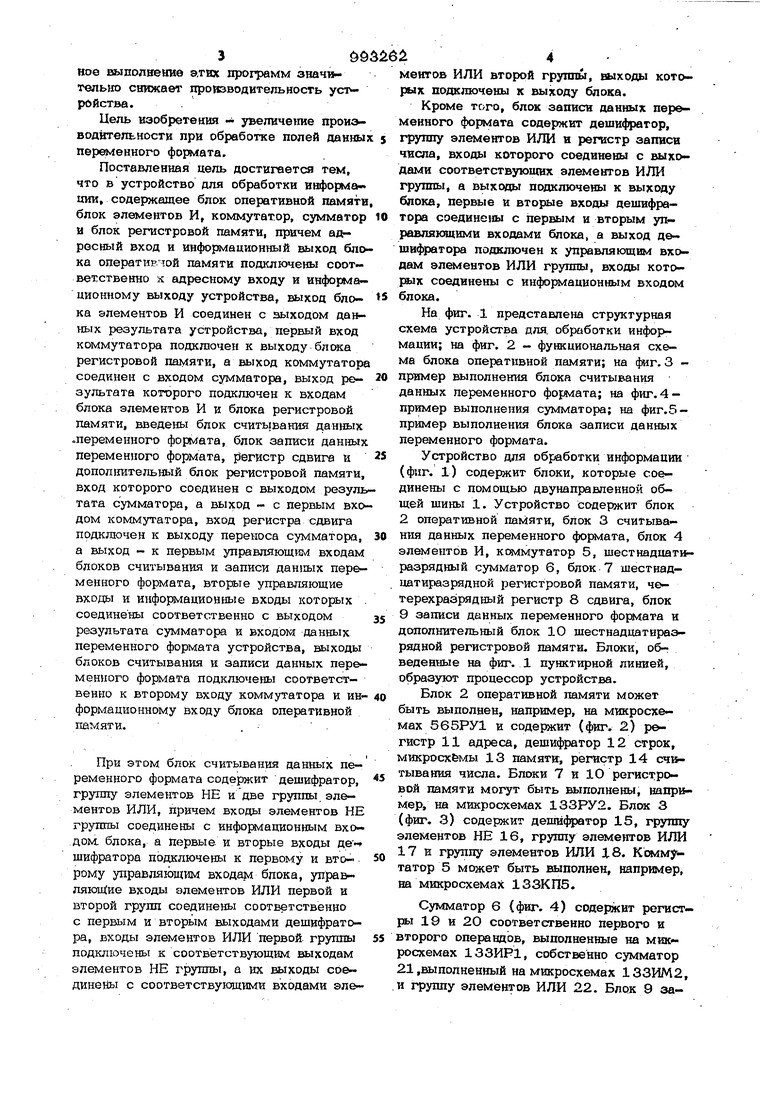

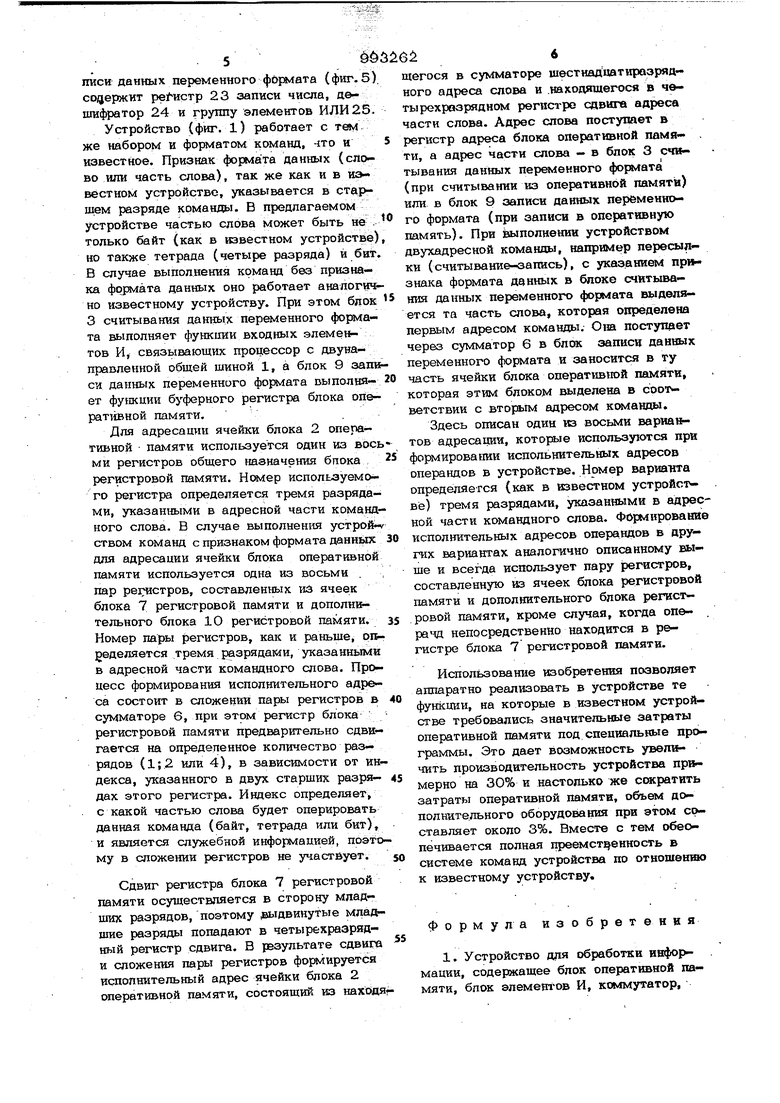

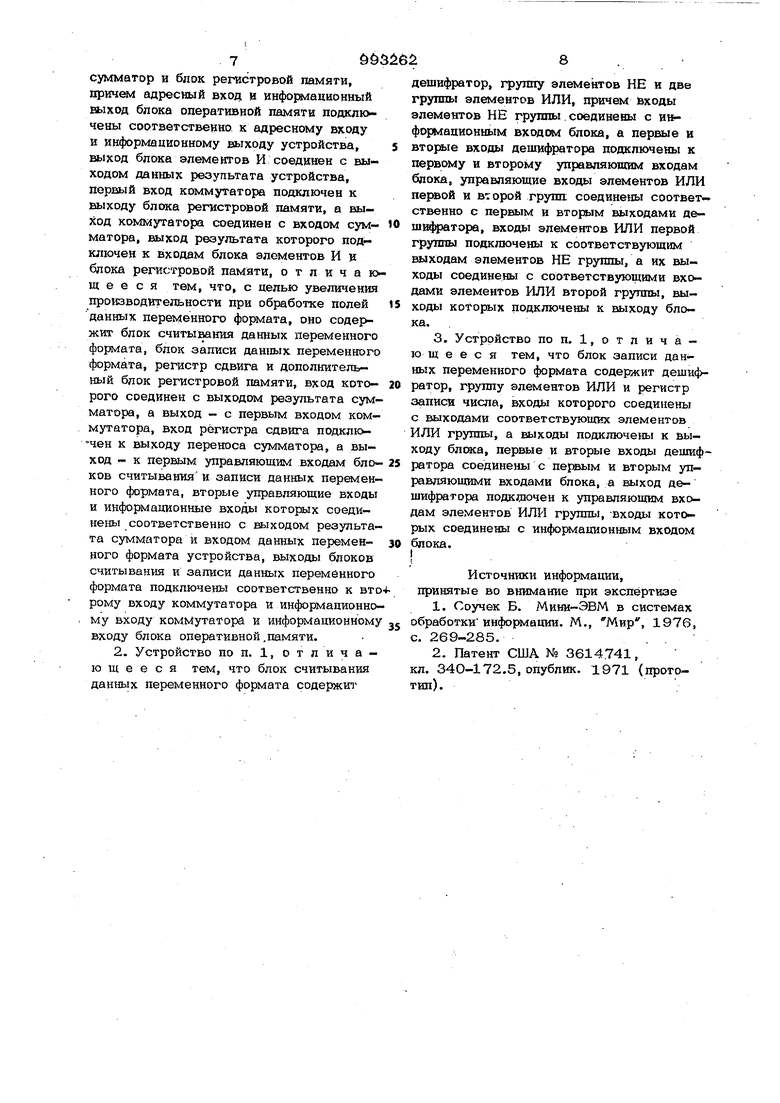

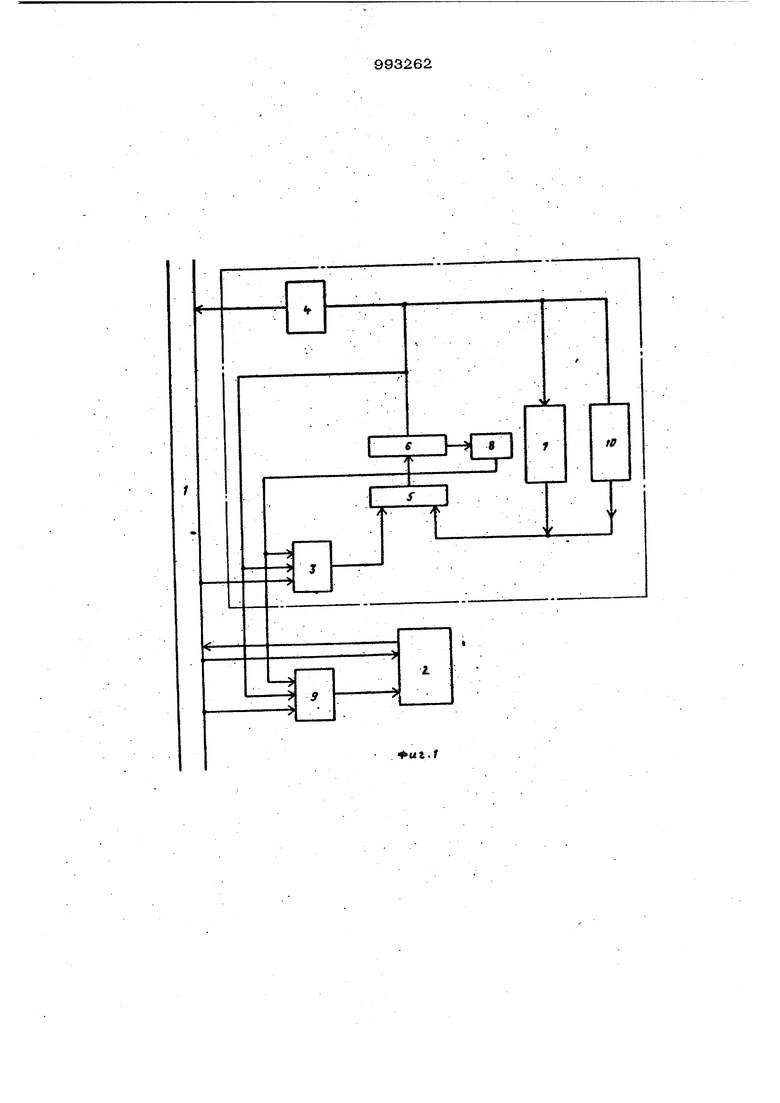

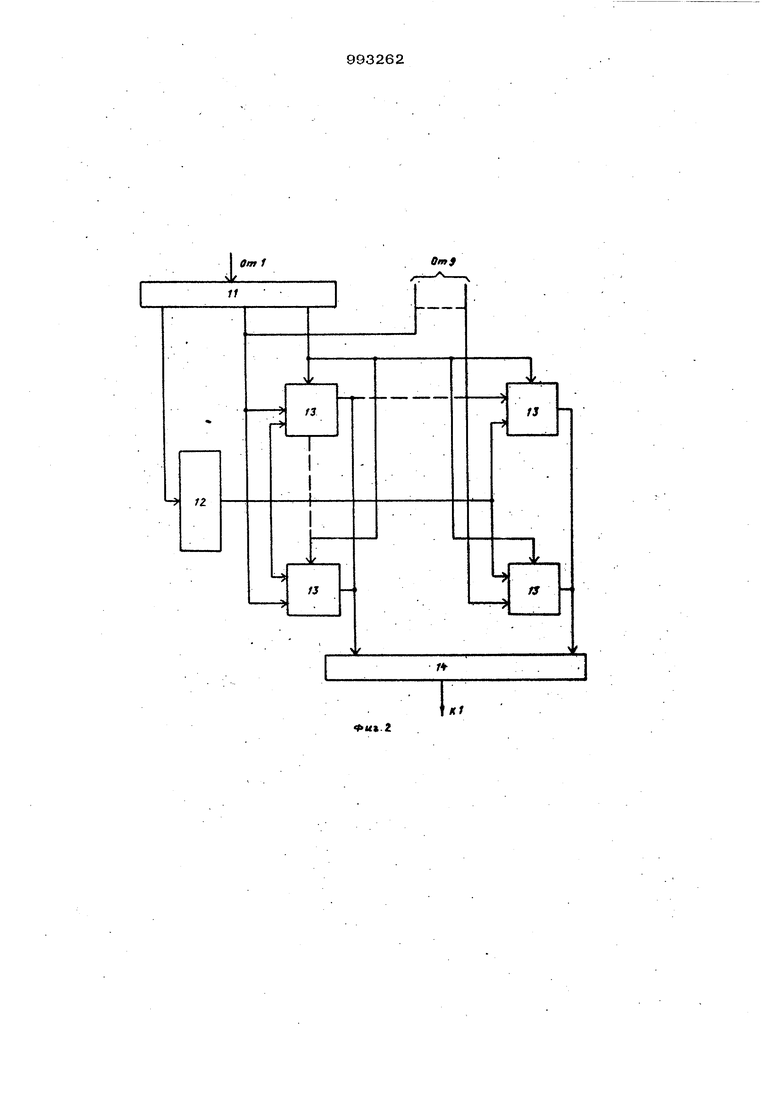

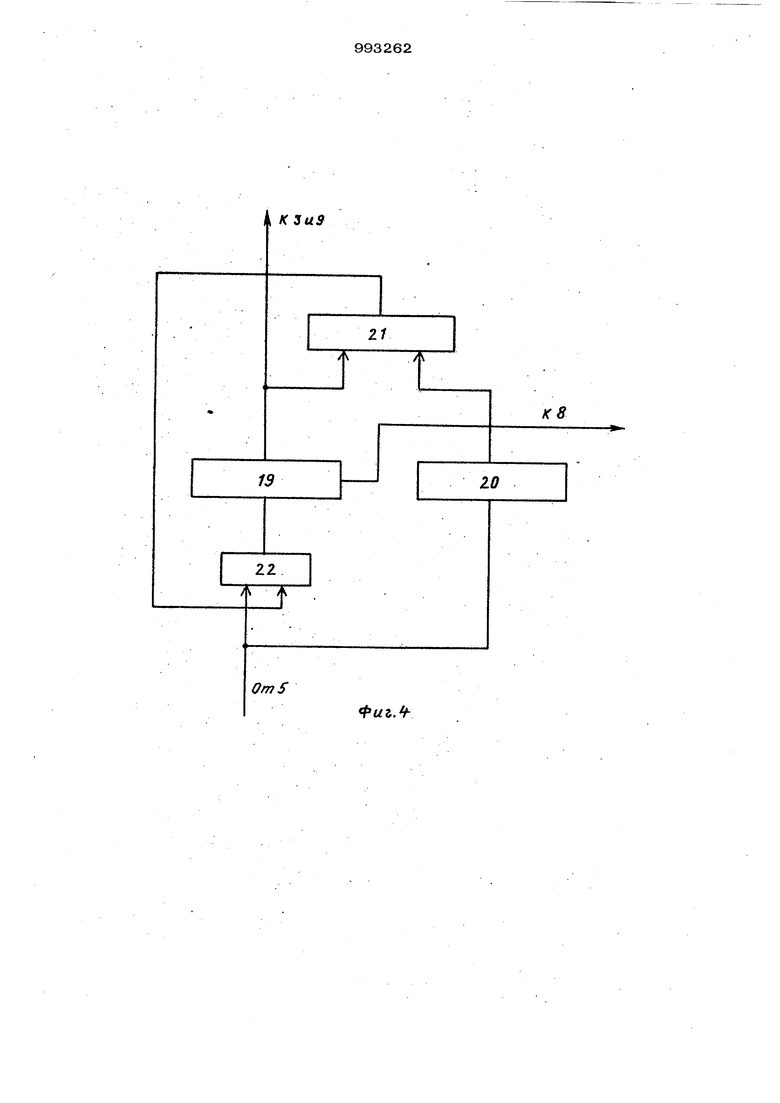

На фиг. 1 представлена структурная схема устройства для. обработки информации; на фиг. 2 - функциональная схема блока оперативной памяти; на фиг. 3 пример выполнения блока считывания данных переменного фогмата; на фиг. 4пример выполнения сумматора; на фиг.5пример выполнения блока записи данных переменного формата.

Устройство для обработки информации (фиг. 1) содержит блоки, которые соединены с помощью двунаправленной общей шины 1. Устройство содержит блок 2 оперативной памяти, бЛок 3 считывания данных переменного формата, блок 4 элементов И, ки«(мутатор 5, шестнадцатиразрядный сумматор 6, блок 7 шестнадцатиразрядной регистровой памяти, четерехразрядный регистр 8 сдвига, блок 9 записи данных переменного и дополнительный блок 10 шестнадцатиразрядной регистровой памяти. Блоки, обведенные на фиг. 1 пунктирной линией, образуют процессор устройства.

Блок 2 оперативной памяти может быть выполнен, например, на микросхемах 565РУ1 и содержит (фиг. 2) регистр 11 адреса, дешифратор 12 строк, микросхемы 13 памяти, регистр 14 считывания числа. Блоки 7 и 10 регистровой памяти могут быть выполнены, например, на микросхемах 133РУ2. Блок 3 (фиг. 3) содержит дешифратор 15, групп элементов НЕ 16, группу элементов ИЛИ 17 и группу элементов ИЛИ Д. 8. Коммутатор 5 может быть выполнен, например, на микросхемах 133КП5.

Сумматор 6 (фиг. 4) содержит регистры 19 и 2О соответственно первого и второго операндов, выполненные на микросхемах 133ИР1, собственно сумматор 21 .выполненный на микросхемах 133ИМ2 и группу элем евтов ИЛИ 22. Блок 9 записи данных переменного формата (фиг. 5) содержит регистр 23 записи числа, д&шифратор 24 и группу элементов ИЛИ 25.

Устройство (фиг. 1) работает с т& же набором и форматом команд, -ITO и 5 известное. Признак формата данных (слово или часть слова), так же как и в иэ- вестном устройстве, указывается в старшем разряде команды. В предлагаемом устройстве частью слова может быть нё только байт (как в известном устройстве), но также тетрада (четыре разряда) и бит, В случае выполнения команд без признака формата данных оно работает аналогично известному устройству При этом блок 3 считывания данных переменного формата выполняет функции входных, элементов И, связывающих процессор с двунаправленной общей шиной 1, а блок 9 записи данных переменного формата выполни- 20 ет функции буферного регистра блока one- ратшной памяти.

Для адресации ячейки блока 2 оперативной памяти используется один из восьми регистров общего назначения бпока 25 регистровой памяти. Номер используемого регистра определяется тремя разрядами, указантшми в адресной части командного слова. В случае выполнения устрой-v ством команд с признаком формата данных 30 для адресации ячейки блока оперативной памяти используется одна из восьми пар рез истров, составленных из ячеек блока 7 регистровой памяти и дополн тельного блока 1О регистровой памяти. 35 Номер пары регистров, как и раньше, определяется тремя разрядами, указанными в адресной части командного слова. Процесс формирования исполнительного адреса состоит в сложении пары регистров в 40 сумматоре 6, при этом регистр блока регистровой памяти предварительно сдвигается на определенное количество разрядов (1;.2 или 4), в зависимости от индекса, указанного в двух старших разря- 45 дах этого регистра. Индекс определяет, с какой частью слова будет оперировать данная команда (байт, тетрада или бит), и является служебной информацией, поэтому в сложении регистров не участвует. 50

Сдвиг регистра блока 7 регистровой памяти осуществляется в сторону младших разрядов, поэтому гдвинутые разряды попадают в четырехразрядный регистр сдвига. В результате сдвига и сложения пары регистров формируется исполнительный адрес ячейки блока 2 (шеративной памяти, состоящий из нах:с дящегося в сумматоре шестнадцапфазряцного адреса слова и .находящегося в четырехразрядном регис1-ре сдвига адреса части слова. Адрес слова поступает в регистр адреса блока оперативной памя TVI, а адрес части слова - в блок 3 считывания данных переменного формата (при считывании из оперативной памяти) или в блок 9 записи данных переменного формата (при записи в оперативную память). При выполнении устройством двухадресной команды, например пересылки (считывание-запись), с указанием пр знака формата денных в блоке сяитыва- ния данных переменного формата выдел - ется та часть слова, которая определена первым адресом команды. Она поступает через сумматор 6 в блок записи данных переменного формата и заносится в ту часть ячейки блока оперативтгой памяти, которая этим блоком выделена в соот ветствии с вторьш адресом команды.

Здесь описан один из aocuviH вариа тов адресация, которые используются при формирова{гаи испольнительных адресов операндов в устройстве. Номер варианта определяется (как в известном устройстве) тремя разрядами, указанными в адресной части командного слова. Формировани исполнительных адресов операндов в других вариантах аналогично описанному выше и всегда использует пару регистров, составленную из ячеек блока регистровой памяти и дополнительного блока регистровой памяти, крюме случая, когда onepaад непосредственно находится в регистре блока 7 регистровой памяти.

Использование изобретения позволяет апларатно реализовать в устройстве те фун1сш1И, на которые в известном устройстве требовались значительные затраты оперативной памяти под специальные npt граммы. Это дает возможность увеличить производительность устройства примерно на 30% и настолько же сократить затраты оперативной памяти, объем дополнительного оборудования при этом составляет около 3%. Вместе с тем обеспечивается полная преемственность в системе команд устройства по отношеншо к известному устройству.

формула изобретеиия

to

Фиг.1

От 1

От)

emS

emt

Оя1

7М

fZM

19

/It

fl

-Л

sUn

I К 3u9

/Vл

19

ZO

иг.ЧOmS

Omf

8P3 1iP3 15P3

1SP3 15 РЗ 1SP3

КО

К If

IfPS

Фиг.5.

Авторы

Даты

1983-01-30—Публикация

1981-09-11—Подача