Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления с повышенными требованиями к надежности.

Целью изобретения является повышение надежности и расширение функциональных возможностей путем обеспечения работоспособности при большом разбросе величины нагрузки и обнаружения вида неисправностей.

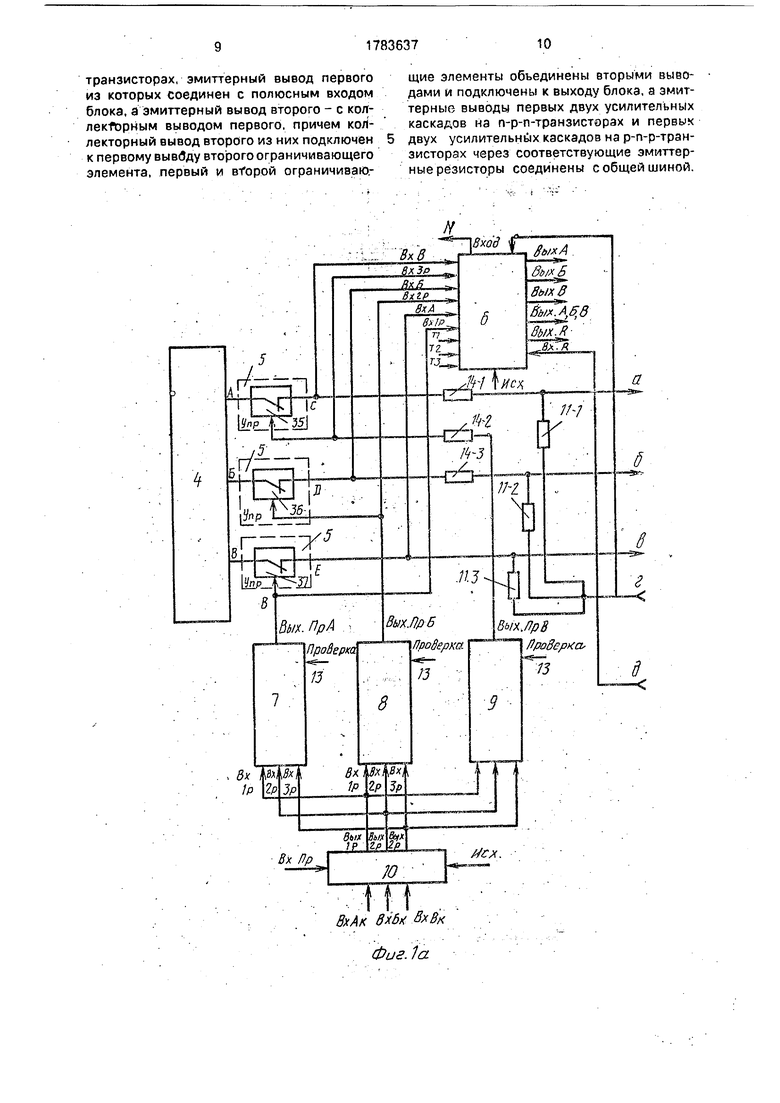

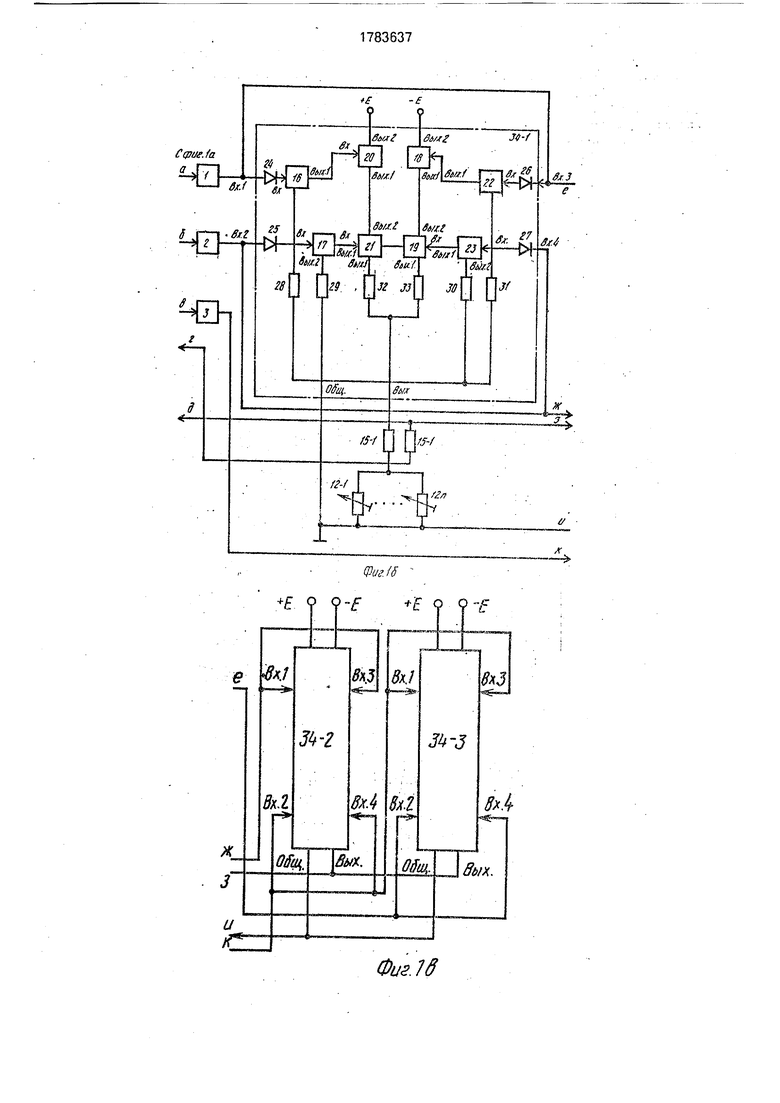

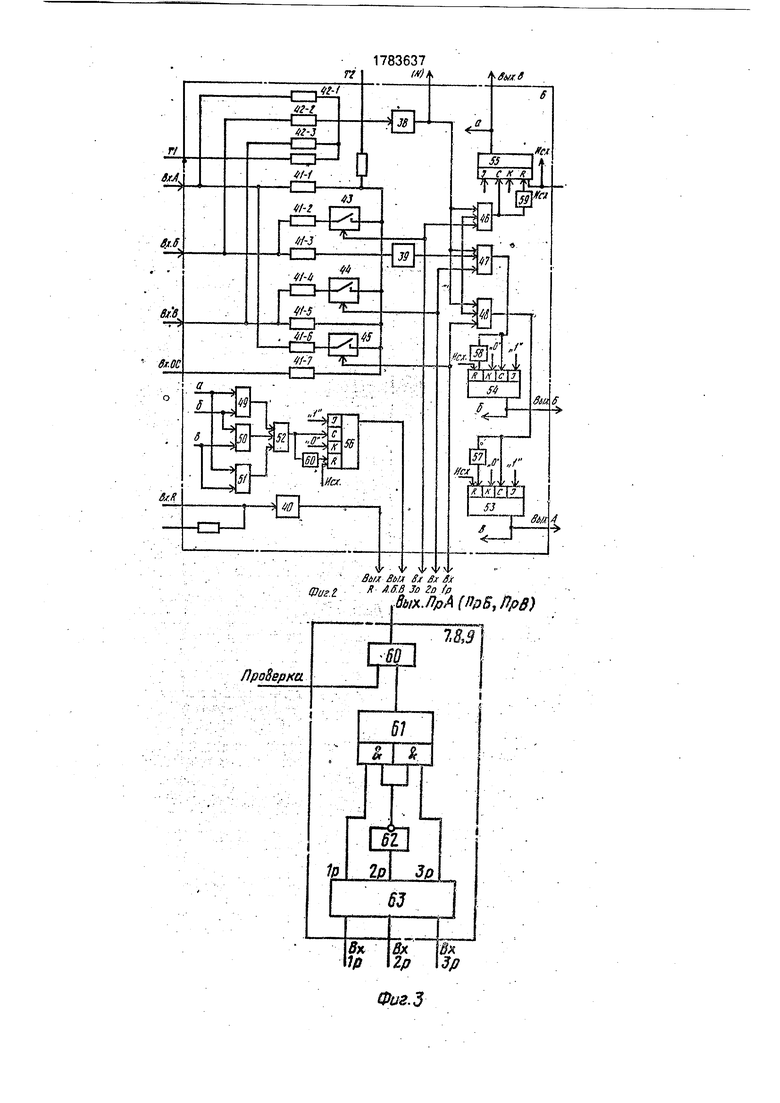

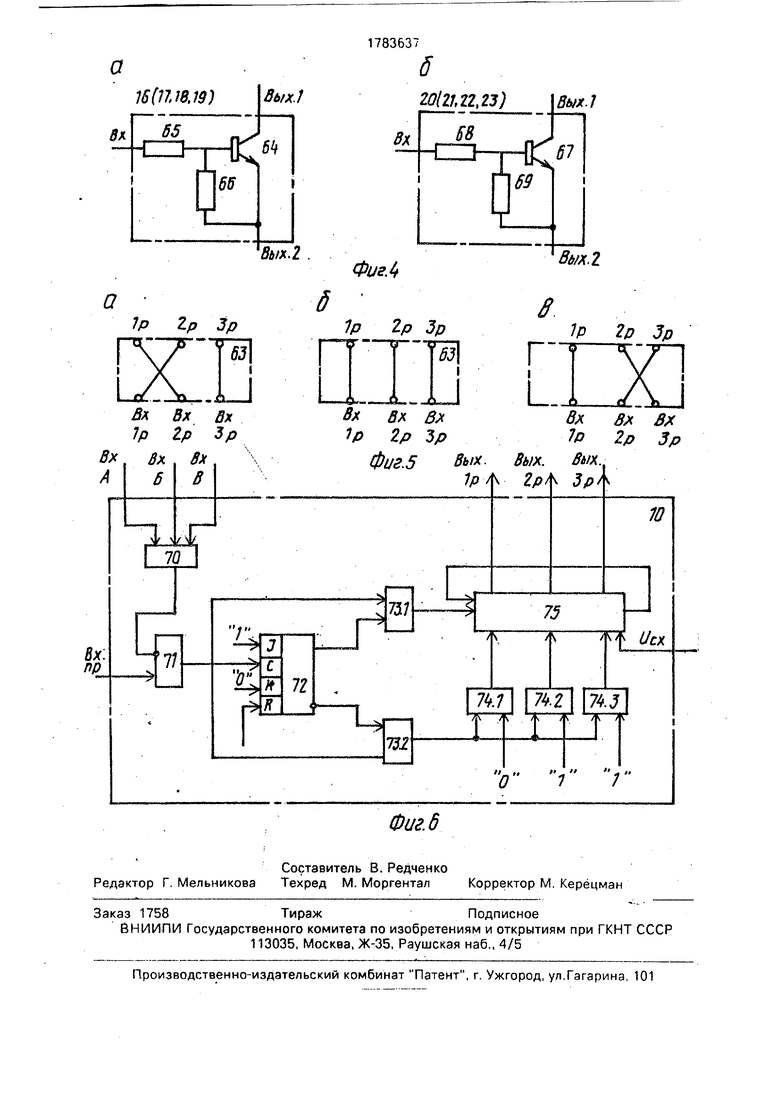

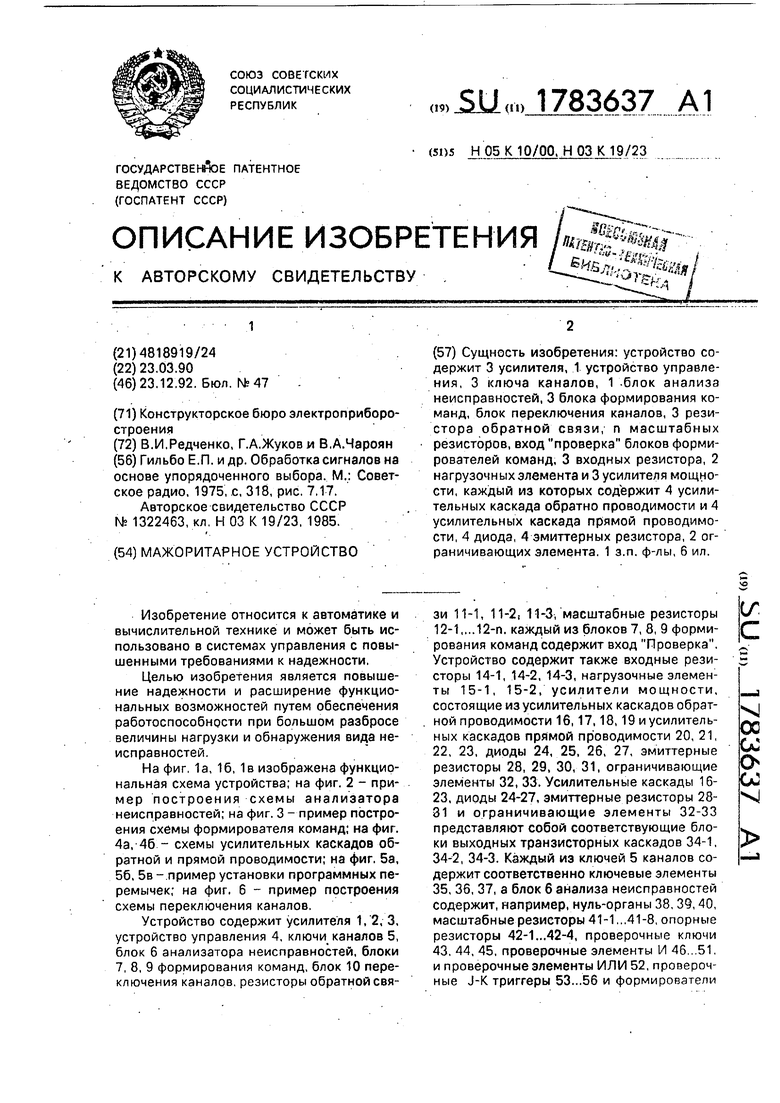

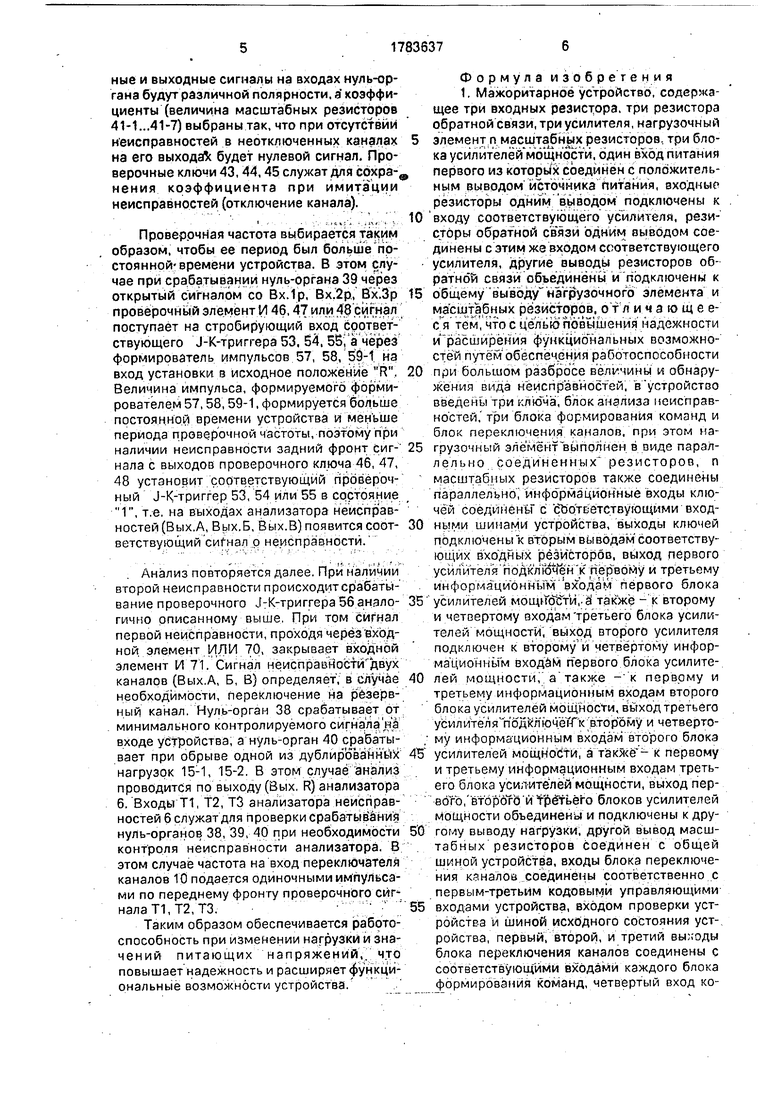

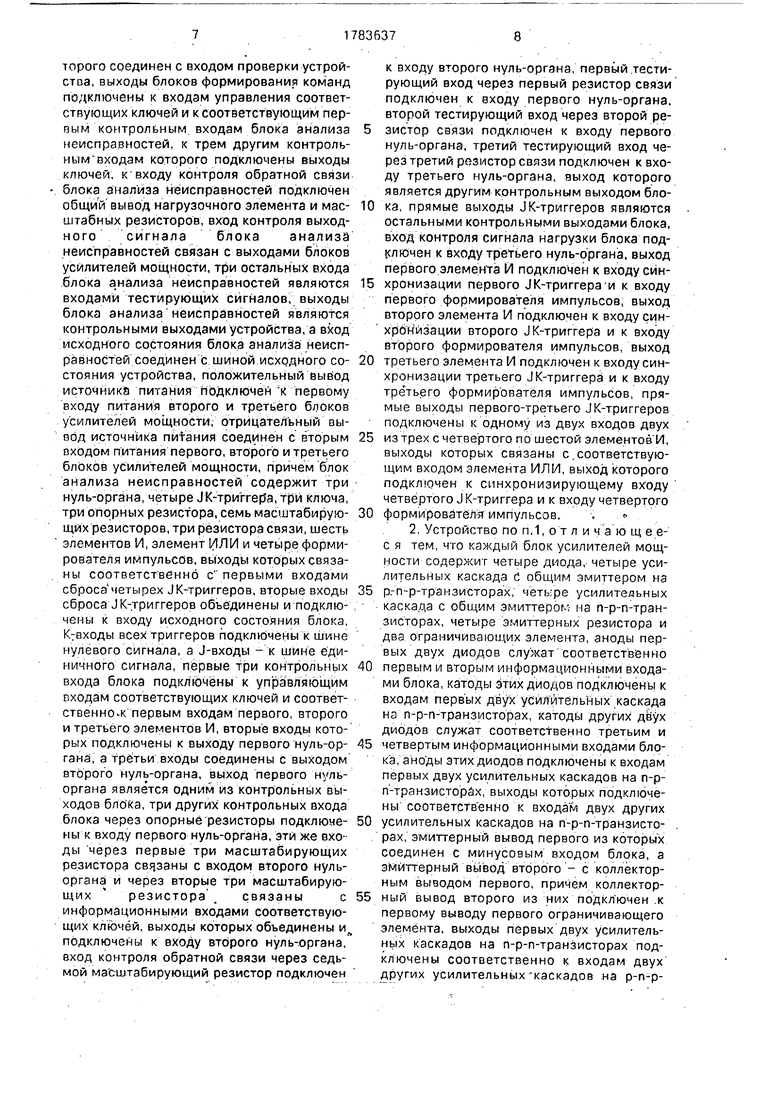

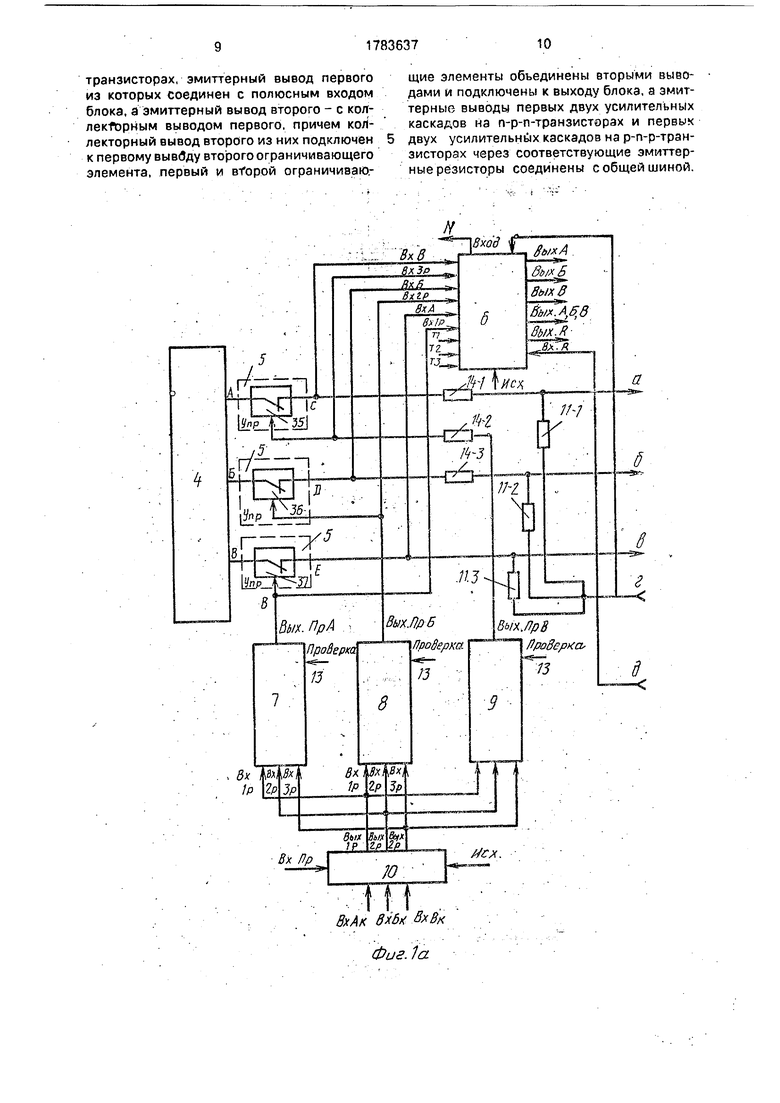

На фиг 1а, 16, 1в изображена функциональная схема устройства; на фиг. 2 - пример построения схемы анализатора неисправностей; на фиг. 3 - пример построения схемы формирователя команд; на фиг. 4а, 46 - схемы усилительных каскадов обратной и прямой проводимости; на фиг. 5а, 56, 5в - пример установки программных перемычек; на фиг. 6 - пример построения схемы переключения каналов.

Устройство содержит усилителя 1, 2, 3, устройство управления 4, ключи каналов 5, блок 6 анализатора неисправностей, блоки 7, 8, 9 формирования команд, блок 10 переключения каналов резисторы обратной связи 11-1, 11-2, 11-3, масштабные резисторы 12-1,...12-п. каждый из блоков 7, 8, 9 формирования команд содержит вход Проверка, Устройство содержит также входные резисторы 14-1, 14-2, 14-3, нагрузочные элементы 15-1, 15-2, усилители мощности, состоящие из усилительных каскадов обратной проводимости 16,17,18,19 и усилительных каскадов прямой проводимости 20, 21,

22,23, диоды 24, 25, 26, 27, эмиттерные резисторы 28, 29, 30, 31, ограничивающие элементы 32, 33. Усилительные каскады 1623,диоды 24-27, эмиттерные резисторы 28- 31 и ограничивающие элементы 32-33 представляют собой соответствующие блоки выходных транзисторных каскадов 34-1, 34-2, 34-3. Каждый из ключей 5 каналов содержит соответственно ключевые элементы 35, 36, 37, а блок 6 анализа неисправностей содержит, например, нуль-органы 38, 39,40, масштабные резисторы 41-1 ..41-8, опорные резисторы 42-1...42-4, проверочные ключи 43, 44, 45, проверочные элементы И 46 51 и проверочные элементы ИЛИ 52, проверочные J-K триггеры 53...56 и формирователи

С/

с

VJ

00

ос о

ОС

X

импульсов 57, 58, 59-1, 59-2, Блоки 7, 8, 9, формирования команд содержат выходной элемент И 60, элементы 2И-ИЛИ 62, инвертор 62, блок программных перемычек 63. Усилительный каскад обратной проводимости 16...19 содержит транзистор n-p-п типа 64, развязывающий резистор 65 и резистор утечки 66. Усилительный каскад прямой проводимости содержит транзистор р-п-р типа 67, развязывающий резистор 68 и резистор утечки 69. Блок 10 переключения каналов содержит, например, входной элемент ИЛИ 70, входной элемент И 71, J-K-триггер 72, элементы 73-1, 73-2 формирования, кодовые элементы 74-1, 74-2, 74-3 и регистр сдвига 75.

Устройство работает следующим образом, При подаче с устройства управления 4 сигнала положительной полярности в усилителях мощности открываются каскады обратной проводимости 16, 17 выходных транзисторных каскадов 34-1, 34-2,34-3, которые представляют собой эмиттерные повторители и обеспечивают усиление потоку. Затем открываются каскады прямой проводимости 20, 21 выходных транзисторных ка- скадов 34-1, 34-2, 34-3, которые представляют собой схему с общим эмиттером и обеспечивают усиление по напряже- нию, которые открываются и по нагрузочным элементам 15-1, 15-2 будет протекать ток. В связи.стем, что коэффициент усиления схем с общим эмиттером намного больше единиць 1, ток нагрузки будет уже ограничен не напряжением на выходах усилителей 1,2,3, а напряжением источника питания Е, которое обычно превышает вы- хрдное напряжение усилителей в несколько раз. Таким образом обеспечивается работоспособность при изменении нагрузки в широком диапазоне. Такое включение не изменяет фазы системы в общем и, несмотря на введение усилительного каскада, в устройстве будет осущестоляться отрицательная обратная связь. При изменении по- лярности входного сигнала на противоположную аналогично работают каскады прямой проводимости 22, 23 и обратной 18,19. При помощи диодов 24,25,26,27 осуществляется развязка входов каскадов от завязки по источникам питания и обеспечивается работоспособность при пробое переходов транзисторов, а также-устраняется подача инверсного напряжения на каскад усиления противоположной полярности. Заданный коэффициент устанавливается регулировкой резистора 12.

Ток нагрузки (JH) определяется по форJH -

U

О+Й,

где DBX - входное напряжение;

Ri - величина входного резистора 14; R2 - величина резистора обратной связи

11;

RG - величина масштабного резистора 12,

Следовательно величина тока не зависит от разбросов величин напряжения питания, а определяется только точностными характеристиками резисторов. Если поляр- ность входного сигнала изменяется с большой скоростью возможно закорачивание

источников питания через транзисторы. Это устраняется включением ограничительных элементов 32, 33, например индуктивно- стей, сопротивление которых при малой длительности велико. Стабильность коэффициента передачи определяется коэффициентом передачи разомкнутой системы, Обычно он велик (до 106), поэтому точность устройства велика, При наличии одной любой неисправности в одном из каналов% величина тока через нагрузку не изменяется и определяется величиной по уравнению (1). Кроме того в процессе работы возможно осуществление контроля работы устройства. В этом случае на вход проверки (Вх.Пр)

подается проверочная частота, a fta вход

5

Проверка блоков формирования команд 7, 8, 9 подается сигнал проверки высоким уровнем. В блоке переключения каналов 10 первый импульс частоты поступая на вход

5 Вхпр. и на вход J-K-триггера 72, проходит через второй элемент И 73-2 формирования, вследствие чего кодовая вставка переписывается через кодовые элементы И 74 на регистр сдвига 75. Задний фронт первого

0 импульса установит J-K-триггер в состояние 1 и следующие импульсы будут сдвигать информацию в регистре сдвига 75. Данный регистр закольцован, поэтому цикл сдвига единицы периодически повторяется.

5 Кодовые перемычки блока программных перемычек 63 набраны таким образом, что если О будет на выходе Вых.1р проверочное оборудование включается в первом канале, на выходе Вых.2р - во втором кана0 ле, на выходе Вых.Зр - в третьем канале, т.е. в этом канале при помощи инвертора 62 и элемента 2И-ИЛИ вырабатывается сигнал на выходе выходного элемента 60 формирователей команд 7, 8, 9. Этот сигнал отключает нормально-замкнутый ключ ключей каналов 5 и замыкает нормально-разомкнутый проверочный ключ 43, 44 или 45. В лубом случае идет сравнение входных и выходных сигналов на нуль-органе 39. Входные и выходные сигналы на входах нуль-органа будут различной полярности, а коэффициенты (величина масштабных резисторов 41-1...41-7) выбраны так, что при отсутствии неисправностей в неотключенных каналах на его выхода будет нулевой сигнал. Проверочные клю«и 43,44,45 служат для сохранения коэффициента при имитации неисправностей (отключение канала).

Проверочная частота выбирается таким образом, чтобы ее период был больше постоянной-времени устройства. В этом случае при срабатывании нуль-органа 39 через открытый сигналом со Вх.1р, Вх.2р, Вх.Зр проверочный элемент И 46,47 или 48 сигнал поступает на стробирующий вход соответствующего J-K-триггера 53, 54,55, а через формирователь импульсов 57, 58, 59-1 на вход установки в исходное положение R. Величина импульса, формируемого формирователем 57,58,59-1, формируется больше постоянной времени устройства и меньше периода проверочной частоты, поэтому при наличии неисправности задний фронт сиг- нала с выходов проверочного ключа 46, 47, 48 устсзновит соответствующий проверочный J-K-триггер 53, 54 или 55 в состояние 1, т е на выходах анализатора неисправностей (Вых А, Вых.Б, Вых.В) появится соот- ветствующий сигнал о неисправности.

Анализ повторяется далее При наличии второй неисправности происходит срабатывание проверочного J-K-триггера 56 знало- гично описанному выше При том сигнал первой неисправности, проходя через входной элемент ИЛИ 70, закрывает входной элемент И 71. Сигнал неисправности двух каналов (Вых А, Б, В) определяет, в случае необходимости, переключение на резервный канал Нуль-орган 38 срабатывает от минимального контролируемого сигнала на входе устройства, а нуль-орган 40 срабатывает при обрыве одной из дублированных нагрузок 15-1, 15-2 В этом случае анализ проводится по выходу (Вых R) анализатора 6. Входы Т1, Т2, ТЗ анализатора неисправностей 6 ел ужат для проверки срабатывания нуль-органов 38, 39, 40 при необходимости контроля неисправности анализатора. В этом случае частота на вход переключателя каналов 10 подается одиночными импульсами по переднему фронту проверочного сигнала Т1, Т2.ТЗ.

Таким образом обеспечивается работоспособность при изменении нагрузки и зна- чений питающих напряжений, что повышает надежность и расширяет функциональные возможности устройства

Формула изобретения 1. Мажоритарное устройство, содержащее три входных резистора, три резистора обратной связи, три усилителя, нагрузочный элемент п масштабных резисторов три блока усилителей мощности, один вход питания первого из которых соединен с положительным выводом источника питания, входные1 резисторы одним выводом подключены к входу соответствующего усилителя, резисторы обратной связи одним выводом соединены с этим же входом соответствующего усилителя, другие выводы резисторов обратной связи объединены и подключены к общему выводу нагрузочного элемента и масштабных резисторов, отличающее- с я тем, что с целью повышения надежности и расширения функциональных возможностей путем обеспечения работоспособности при большом разбросе величины и обнаружения вида неисправностей, в устройство введены три ключа, блок анализа неисправностей, три блока формирования команд и бло переключения каналов, при этом нагрузочный элемент выполнен в виде параллельно соединенных резисторов, п масштабных резисторов также соединены параллельно, информационные входы ключей соединены с боотьетствующими входными шинами устройства, выходы ключей подключенык вторым выводам соответствующих входных резисторов, выход первого усилителя подключен к первому и третьему информационным входам первого блока усилителей мощности, Ј также - к второму и четвертому входам третьего блока усилителей мощности, выход второго усилителя подключен к второму и четвертому инфор- мационньГм входам первого блока усилителей мощности, а также - к первому и третьему информационным входам второго блока усилителей мощности, выход третьего усилителяТюдключеТ-Гк второму и четвертому информационным входам второго блока усилителей мощности, а также - к первому и третьему информационным входам третьего блока усилителей мощности, выход первого, второТо и Третьего блоков усилителей мощности объединены и подключены к другому выводу нагрузки, другой вывод масштабных резисторов соединен с общей шиной устройства, входы блока переключения к налОь соединены соответственно с первым-третьим кодовыми управляющими входами устройства, входом проверки устройства и шиной исходного состояния устройства, первый, второй, и третий вы1.оды блока переключения каналов соединены с соответствующими входами каждого блока формирования команд, четвертый вход которого соединен с входом проверки устройства, выходы блоков формирования команд подключены к входам управления соответствующих ключей и к соответствующим первым контрольным входам блока анализа неисправностей, к трем другим контроль- ным входам которого подключены выходы ключей, к входу контроля обратной связи блока анализа неисправностей подключен общий вывод нагрузочного элемента и мае- штабных резисторов, вход контроля выходного сигнала блока анализа неисправностей связан с выходами блоков усилителей мощности, три остальных входа блока анализа неисправностей являются входами тестирующих сигналов, выходы блока анализа неисправностей являются контрольными выходами устройства, а вход исходного состояния блока анализа неисправностей соединен с шиной исходного со- стояния устройства, положительный вывод источника питания подключен к первому входу питания второго и третьего блоков усилителей мощности, отрицательный вывод источника питания соединен с вторым входом питания первого, второго и третьего блоков усилителей мощности, причем блок анализа неисправностей содержит три нуль-органа, четыре JK-триггера, три ключа, три опорных резистора, семь масштабирую- щих резисторов, три резистора связи, шесть элементов И, элемент ИЛИ и четыре формирователя импульсов, выходы которых связаны соответственно с первыми входами сброса четырех JK-триггеров, вторые входы сброса JK-григгеров объединены и подключены к входу исходного состояния блока, Кгвходы всех триггеров подключены к шине нулевого сигнала, а J-входы - к шине единичного сигнала, первые три контрольных входа блока подключены к управляющим входам соответствующих ключей и соответственное первым входам первого, второго и третьего элементов И, вторые входы которых подключены к выходу первого нуль-ор- гана, а третьи входы соединены с выходом второго нуль-органа, выход первого нуль- органа являе тся одним из контрольных выходов блока, три других контрольных входа блока через опорные резисторы подклюне- ны к входу первого нуль-органа, эти же входы через первые три масштабирующих резистора связаны с входом второго нуль- органа и через вторые три масштабирующих резисторасвязаныс информационными входами соответствующих ключей, выходы которых объединены и подключены к входу второго нуль-органа, вход контроля обратной связи через седьмой масштабирующий резистор подключен

к входу второго нуль-органа, первый тестирующий вход через первый резистор связи подключен к входу первого нуль-органа, второй тестирующий вход через второй резистор связи подключен к входу первого нуль-органа, третий тестирующий вход через третий резистор связи подключен к входу третьего нуль-органа, выход которого является другим контрольным выходом блока, прямые выходы JK-триггеров являются остальными контрольными выходами блока, вход контроля сигнала нагрузки блока подключен к входу третьего нуль-органа, выход первого элемента И подключен к входу синхронизации первого JK-триггера и к входу первого формирователя импульсов, выход второго элемента И подключен к входу синхронизации второго JK-триггера и к входу второго формирователя импульсов, выход третьего элемента И подключен к входу синхронизации третьего JK-триггера и к входу третьего формирователя импульсов, прямые выходы первого-третьего JK-триггеров подключены к одному из двух входов двух из трех с четвертого по шестой элементов И, выходы которых связаны с,соответствующим входом элемента ИЛИ, выход которого подключен к синхронизирующему входу четвертого JK-триггера и к входу четвертого формирователя импульсов. .

2. Устройство по п,1, о т л и ч а ю щ е е- с я тем, чго каждый блок усилителей мощности содержит четыре диода, четыре усилительных каскада с общим эмиттером на p-n-p-транзисторах, четь-ре усилительных каскада с общим эмиттеров на п-р-п-тран- зисторах, четыре эмиттерных резистора и два ограничивающих элемента, аноды первых двух диодов служат соответственно первым и вторым информационными входами блока, катоды этих диодов подключены к входам первых двух усилительных каскада на n-p-n-транзисторах, катоды других двух диодов служат соответственно третьим и четвертым информационными входами блока, аноды этих диодов подключены к входам первых двух усилительных каскадов на п-р- n-транзисторах, выходы которых подключены соответств енно к входам двух других усилительных каскадов на п-р-п-транзисто- рах, змиттерный вывод первого из которых соединен с минусовым входом блока, а эмиттерный вывод второго - с коллекторным выводом первого, причем коллекторный вывод второго из них подключен к первому выводу первого ограничивающего элемента, выходы первых двух усилительных каскадов на n-p-n-транзисторах подключены соответственно к входам двух других усилительных каскадов на р-п-ртранзисторах, эмиттерный вывод первого из которых соединен с полюсным входом блока, а эмиттерный вывод второго - с коллекторным выводом первого, причем коллекторный вывод второго из них подключен к первому вы вид у второго ограничивающего элемента, первый и второй ограничивающие элементы объединены вторыми выводами и подключены к выходу блока, а эмит- терные выводы первых двух усилительных каскадов на n-p-n-транзисторах и первых двух усилительных каскадов на р-п-р-тран- зисторах через соответствующие эмиттер- ные резисторы соединены с общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2002 |

|

RU2226695C1 |

| СИНХРОННЫЙ ГЕНЕРАТОР С ПРЕЦИЗИОННОЙ СИСТЕМОЙ УПРАВЛЕНИЯ | 2005 |

|

RU2295192C1 |

| Релейный ключ | 1983 |

|

SU1091244A1 |

| Устройство дистанционного управления угольным комбайном с пневмоприводом | 1984 |

|

SU1190029A1 |

| Цифроаналоговая вычислительная система | 1987 |

|

SU1483468A1 |

| Усилитель мощности | 1987 |

|

SU1532994A1 |

| Устройство для регулирования давления | 1984 |

|

SU1190370A1 |

| Асинхронный вентильный каскад | 1986 |

|

SU1422359A1 |

| Интегратор с управляемым ограничением выходного сигнала | 1986 |

|

SU1305724A1 |

| Четырехквадрантное множительное устройство | 1980 |

|

SU957225A1 |

Сущность изобретения: устройство содержит 3 усилителя, 1 устройство управления, 3 ключа каналов, 1 блок анализа неисправностей, 3 блока формирования команд, блок переключения каналов, 3 резистора обратной связи, п масштабных резисторов, вход проверка блоков формирователей команд, 3 входных резистора, 2 нагрузочных элемента и 3 усилителя мощности, каждый из которых содержит 4 усилительных каскада обратно проводимости и 4 усилительных каскада прямой проводимости, 4 диода, 4 эмиттерных резистора, 2 ограничивающих элемента. 1 з.п. ф-лы, 6 ил.

Т И

ЗхАк вхбх Вх8к

Фиг. Та

f2-f

l

iФиг 15 +E 9-f +Ј 9

Л/

-

зь-г

Вх.г

/

/ Л

Q&n.

Вы.

О

/га

V

X

&./

vwo gie8 3

34-J

8x.4

Ы

Offm.

Вых.

Физ1в

(№ц 1дац)

Of OZ Ј 9S У

iff iff rg пчд r/vff

7 гпф

iC9C8il

а

1рZp Зр

ГУ Р LA.Li

Вх Вх Вх lp Zp Зр

Вх Вх 8х

1р 2р Зр

Г

L.1

1р 2р Зр

8 Вх ВхВх в Вх

1р 2р Ър7р 2р Зр

Г

L.1

1р 2р Зр

Вх в Вх

| Гильбо Е.П | |||

| и др | |||

| Обработка сигналов на основе упорядоченного выбора | |||

| М.: Советское радио, 1975, с, 318, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Мажоритарное устройство | 1985 |

|

SU1322463A1 |

Авторы

Даты

1992-12-23—Публикация

1990-03-23—Подача