(5) ЧЕТЫРЕХКВАДРАНТНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1982 |

|

SU1119037A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Перемножающее устройство | 1987 |

|

SU1465896A1 |

| Двухквадрантное множительное устройство | 1975 |

|

SU545992A1 |

| Логарифмирующее устройство | 1979 |

|

SU809230A1 |

| Функциональный преобразователь | 1982 |

|

SU1111181A1 |

| Логарифмический преобразователь | 1982 |

|

SU1064283A1 |

| Логарифмический преобразователь | 1979 |

|

SU830419A1 |

| Множительное устройство | 1980 |

|

SU924720A1 |

| Логарифмический преобразователь | 1984 |

|

SU1160446A1 |

Изобретение относится к автомати ке и вычислительной технике. Известно четырехквадрантное устройство умножения, содержащее дифференциальный усилитель, в цепь отрицательной обратной связи которого включен линеаризованный полевой транзистор, к выходу дифференциального усилителя подключен второй линеаризованный полевой транзистор, выполняющий функцию управляемого со прстизления, включенного в цепь рези СТИ9НОГО делителя, сигнал с которого подается на вход второго дифферен циального усилителя Недостаток такого устройства узкий диапазон изменения входных сиг налов, обусловленный тем, что характеристики линеаризованных полевых транзисторов линейны в узком диапазоне напряжений. Наиболее близким по технической сущности к изобретению является множитгяьное устройство, содержащее пер ВЫЙ и второй дифференциальные усилители, семь масштабных.резисторов, два ограничивающих резистора, задающий потенциометру источник опорного напряжения, первый и второй усилительные транзисторы, эмиттеры которых соединены между собой, база первого усилительного транзистора через первый масштабный резистор соединена с первым входом устройства и через первый ограничивающий резистор - с шиной нулевого потенциала, база второго усилительного транзистора через второй масштабный резистор соединена с подвижным контактом t задающего потенциометра, выводы которого подключены к источнику опорного напряжения, и через второй.ограничивающий резистор подключена к шине нулевого потенциала, коллектор первого усилительного транзистора соединен с инвертирующим входом первого дифференциального усилителя и через третий масштабный резистор с шиной нулевого потенциала, в цепь отрицательной обратной связи Первого дифференциального усилителя включен четвертый масштабный резистор, неинвертирующий вход первого дифференциального усилителя псздключен к шине нулевого потенциала, коллектор второго усилительного транзистора подключен к инвертирующему входу второго дифференциального усилителя, чере пятый масштабный резистор - к выходу первого дифференциального усилителя, а через шестой масштабный резистор к выходу второго дифференциэльного усилителя, неинвертирующий вход второго дифференциального усилителя под ключен к шине нулевого потенциала , тре тий и четвертый усилительные транзисторы, базы которых объединены и подключены к шине опорного напряжения устройства, коллектор третьего усилительного транзистора подключен к эмиттерам первого и второго усилительных транзисторов, коллектор четвертого усилительного транзистора подключен к первому выводу седьмого масштабного резистора и к инвертирующему входу третьего дифференциального усилителя, неинвертирующий вход которого подключен к шине нулевого потенциала, а выход подключен к эмит терам третьего и четвертого усилительных транзисторов. Устройство име ет высокую точность умножения, не тр бует применения дополнительных каскадов усиления С2. Недостатком данного устройства является то, что перемножение сигйалов производится лишь в двух квадрантах. Цель изобретения - расширение функциональных возможностей перемножителя за счет перемножения сигналов в четырех квадрантах при сохранении высокой точности перемножения и широкого динамического диапазона входных и выходных сигналов. Поставленная цель достигается тем что в известное устройство введены нуль-орган и два усилителя с дискрет НО изменяемым коэффициентом усиления

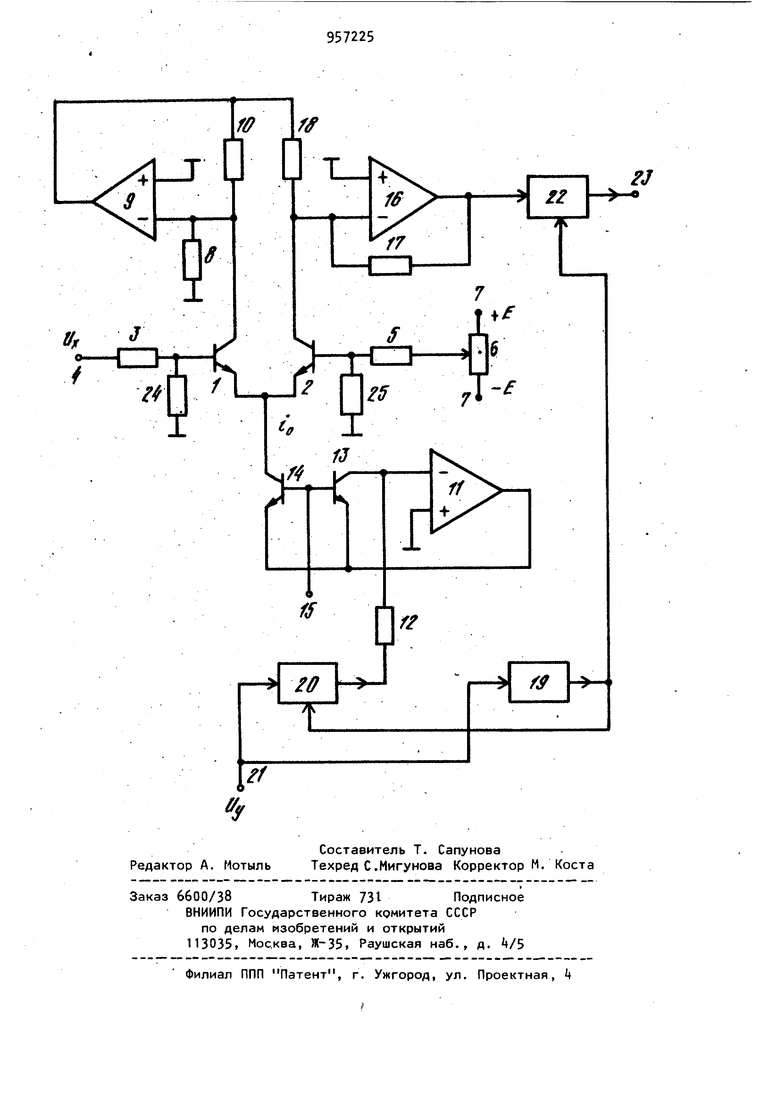

информационныи вход первого усилителя с дискретно изменяемым коэффициентом усиления соединен с входом нуль-органа И является вторым входом устройства, а выход подключен к второму выводу седьмого масштабного резистора, информационный вход второго усилителя с дискретно изменяемым коференциальной пары соединены между собой и с вторым входом 15 устройства по опорному напряжению. Устройство содержит второй дифференциальный усилитель 16, в цепи отрицательной обратной связи которого включен пятый масштабный резистор 17. Неинвертирующий вход второго дифференциального эффициентом усиления подключен к выходу второго дифференциального усилителя, а выход является выходом устройства, выход нуль-органгГпо дключен к управляющим входам усилителей с дискретно изменяемым коэффициентом усиления. На чертеже дана функциональяая схема четырехквадрантного множительного устройства. Множительное устройство содержит первый и второй усилительные транзисторы 1 и 2, которые образуют первую дифференциальную пару транзисторов. База первого усилительного транзистора 1 через первый масштабный резистор 3 соединена с первым входом i устройства, база второго усилительного транзистора 2 через второй масштабный резистор 5 соединена с подвижным контактом задающего потенциометра 6, выводы которого подключены к источнику 7 опорного напряжения. Коллектор первого усилительного транзистора 1 соединен через третий масштабный резистор 8 с шиной нулевого потен циала и непосредственно с инвертирующим входом первого дифференциального усилителя 9, в цепи отрицательной обратной связи которого включен четвертый масштабный резистор 10. Неинвертирующий вход дифференциального усилителя 9 соединен с шиной нулевого потенциала. Неинвертирующий вход третьего дифференциальное о усилителя 11 подключен к шине нулевого потенциала, а инвертирующий вход соединен с седьмым масштабным резистором 12 и с коллектором третьего усилие-ельного транзистора 13, который вместе с четвертым усилительным транзистором 1 образует вторую дифференциальную пару транзисторов. Эмиттеры усилительных транзисторов 1 и 2 соединены между собой и с коллектором четвертого усилительного транзистора 14 второй дифференциальной пары транзисторов. Выход третьего дифференциального усилителя 11 соединен с эмиттерами транзисторов 13 и И второй дифференциальной пары. Базы транзисторов 13 И 1 второй дифусилителя соединен с шиной нулевого потенциала, а инвертирующий вход через шестой,масштабный резистор 18 соединен с выходом первого дифференциального усилителя. Кроме того, устройство содержит нуль-орган 19, вход которого соединен с информационным входом первого усилителя 20 с дискретно изменяемым коэффициентом усиления и непосредственно с третьим входом 21 устройства. Выход первого усилителя с дискретно изменяемым коэффициентом усиления соединен со вторым выводом седьмого масштабного резистора. Информационный вход второго усилителя 22 с дискретно изменяемым коэффициен том усиления соединен с выходом второго дифференциального усилителя. Вх ды управления первого и второго усилителей с дискретно изменяемыми коэф фициентами усиления соединены между собой и с выходом нуль-органа. Выход второго усилителя с дискретно изменяемым коэффициентом усиления соединен непосредственно с выходом 23 уст ройства. На чертеже обозначены ограничиваю щие резисторы 2k kt 25, которые подключены к базам соответственно первого и второго транзисторов. Устройство работает следующим образом. Умножение сигналов производится на дифференциальной паре усилительных транзисторов 1 и 2. Один умножаемый сигнал (любой полярности) подается в базу транзистора 1 первой дифференциальной пары. Второй умножаемый сигнал (также любой полярноети ) подается на вход нуль-органа 19 и одновременно на вход первого усили теля 20 с дискретно изменяемым коэффициентом усиления. Усилитель с дискретно изменяемым коэффициентом усиления представляет собой усилитель, коэффициент усиления которого равен либо +1, либо -1, ь зависимости от величины потенциала поступающего на его вход управления. Когда сигнал на входе нуль-органа 19 имеет положительную полярность, на его выходе (а следовательно, и на входах управления усилителей 20 и 22 присутствует такой потенциал, при ко тором коэффициенты усиления усилителей 20 и 22 равны +1. Когда сигнал на входе нуль-органа 19 становится о рицательным, на выходе (и, соответственно, на входах управления усилителей 20 и 22} присутствует такой потенциал, при котором коэффициенты усиления усилителей 20 и 22 равны -1. Таким образом, сигнал на выходе усилителя 20 всегда имеет положительную полярность. Этот сигнал IUyl4e-. рез резистор 12 подается на инвертирущий вход дифференциального усилителя П, который вместе с усилительными транзисторами 13 и образует генератор тока. Величина тока изменяется при изменении сигнала .. io lU,l/Rin, где сопративление резистора 12. При изменении величины тока IQ .изменяется коэффициент дифференциального усиления КЛ дифференциальной пары транзисторов 1 и 2. Следовательно, можно записать к ,,I/R, что соответствует ибых Ux),,i, где К, Kj - коэффициенты пропорциональности . Питание коллекторов усилительных транзисторов 1, 2 осуществляется через дифференциальный усилитель 9, причем режим схемы выбран таким образом что на коллекторах усилительных транзисторов 1 и 2 постоянно присутствует нулевой потенциал. Слежение за нулевым потенциалом осуществляют усилители 9 и 16. Дифференциальный усилитель 9 отслеживает изменение питания коллектрров пары,, поддерживая его постоянным при изменении окружающей температуры в широком диапазоне. Сигнал произведения двух напряжений снимается с правого коллектора усилительного транзистора 2, усиливается усилителем 16 и подается на вход усилителя 22, знак усиления которого меняется а зависимости от знака напряжения U, как было сказано выше. Следовательно, с выхода усилителя 25 снимается сигнал, пропорциональный произведению напряжений {iy и Uy. Таким образом, предлагаемое устройство расширяет диапазон изменения входных сигналов за счет возможности умножения сигналов в четырех квадрантах. Формула изобретения Четырехквадрантное множительное устройство, содержащее первый и второй дифференциальные, усилители, семь масштабных резисторов, два ограничивающих резистора, задающий потенциометр, источкик опорного напряжения, первый и второй усилительные транзисторы, эйиттеры которых сое-. динены между собой, база первого усилительного транзистора через первый масштабный резистор соединена с первым входом устройства и через пер вый ограничивающий резистор - с шиной нулевого потенциала, база второго усилительного транзистора через второй масштабный резистор, соединена с подвижным контактом задающего потенциометра, выводы которого подключены к источнику опорного напряжения и через второй ограничивающий резистор подключены к шине нулевого потенциала, коллектор первого усилительного транзистора соединен с инвертирующим входом первого дифференциального усилителя и через третий масштабный резистор - с шиной ну левого потенциала, в цепь отрицательной обратной свяаи первого дифференциального усилителя включен чет вертый масштабный резистор, неинвер тирующий вход первого дифференциального усилителя подключен к шине нулевого поте.нциала, коллектор второго усилительного транзистора подключен к инвертирующему входу второго дифференциального усилителя, через . пятый масштабный резистор подключен к выходу первого дифференциального у лителя, а через шестой масштабный ре зистор - к выходу второго дифференци ального усилителя, неинвертирующий вход второго дифференциального усили теля подключен к шине нулевого потен циала, третий и четвертый уси58лительные транзисторы, базы которых объединены и подключены к шине опорного напряжения устройства, коллектор третьего усилительного транзистора подключен к эмиттерам первого и второго усилительных транзисторов, коллектор четвертого усилительного транзистора подключен к первому выводу седьмого масштабного резистора и к инвертирующему входу третьего дифференциального усилителя, неинвертирующий вход которого подключен к шине нулевого потенциала, а выход подключен к эмиттерам третьего и четвертого усилительных транзисторов, отличающееся тем, что,, с целью расширения диапазона изменения входных с;игналов, в него введены нуль-орган и два усилителя с дискретно изменяемым коэффициентом усиления, информационный вход первого усилителя с дискретно изменяемым коэффициентом усиления соединен с входом нуль-органа и является вторым входом устройства, а выход подключен к второму выводу седьмого масштабного резистора, информационный вход второго усилителя с дискретно изменяемым коэффициентом усиления подключен к выходу второго дифференциального усилителя,.а выход явля-. etcя выходом устройства, выход нульоргана подключен к управляющим входам усилителя с дискретно изменяемым коэффициентом усиления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 66797JL. кл. G Об G 7/16, 1977. 2.Авторское свидетельство СССР № 5 5ЭЭ2, кл. G 06 G 7/16, 1975 (прототип).

Авторы

Даты

1982-09-07—Публикация

1980-12-29—Подача