Устройство относится к электроизмерительной технике и может быть использовано для цифрового измерения электрического сопротивления постоянному току.

Известен цифровой омметр, содержащий цифровой блок, управляющий блок, источник питания, к которому присоединены i последовательно включенные образцовый и измеряемый резисторы. Зажимы образцового резистора через переключатель присоединены к входу интегратора, состоящего из двухвходового усилителя,резистора и конденсатора. К выходу интегратора присоединен нуль-орган. Неинвертирующий вход усилителя через ключ соединен с выходом нуль-органа и через конденсатор и переключатель - с зажимами измеряемого резистора.

Управляющий блок имеет входы, соединяющие его с цифровой частью и выходом нуль-органа, и выходы,по которым производится управление цифровой частью, ключом и переключателями.

Недостатком этого цифрового омметра является низкая точность измерения, связанная с изменением напряжения на запоминающем конденсаторе

VJ

I

кэ ел

в процессе измерения из-за его разряда через входное сопротивление усилителя, имеющего конечную величину.

ЦеНью изобретения является повыше- g ние точности измерения.

Поставленная цель достигается тем, что устройство снабжено последовательно соединенными с источником напряжения постоянного тока калибровоч-|0 HiiM сопротивлением и вторым образцо- B|IM сопротивлением, соедййеннь м вторь} концом с общей шиной, измеряемое сопротивление соединено с первым образцовым сопротивлением и первым вхо-15 дом третьего переключателя, второй конец измеряемого сопротивления соединен с источником напряжения, второй конец первого образцового сопротивления соединен с общей шиной, а 20 место соединения калибровочного и второго образцового сопротивлений

соединено с вторым входом третьего переключателя, повторителем напряжения, неинвертирующий вход которо- 25

го соединен с выходом первого переключателя, инвертирующий вход - с выходом второго переключателя, а вы- ход - с входом интегратора, вторые входы первого и второго переключате- 30 лей соединены с общей шиной, последовательно соединёнными с Шходом делители частоты второй схемой совпадения и первым триггером, последовательно соединенными с выходом лителя частоты четвертой схемой совпадения и вторым триггером, причем, вторые входы второй и четвертой схем совпадения соединены , соответственно, с инверсным и прямым выходами 40 первого триггера, инверсный выход первого триггера соединен с управляющим входом первого переключателя, а прямой выход управляющим входом второго переключателя, прямой 45

выход второго триггера соединен с первым входом блока управления и третьим входом третьей схемы совпа- дения, а инверсный выход - с вторым входом первой схемы срвпадения, вхо- 50 ды R первого и второго триггеров динены с выходом компаратора напря- - жения, последовательно соединенными с вторым выходом блока управления инвертором, пятой схемой совпадения, gg вторым счетчиком и схемой сравнения ; кодов, причем, второй и третий вхо- ды пятой схемы совпадения соединены, соответственно, с прямым выходом

второго триггера, и генератором счетных импульсов, дифференцирующей цепью, вход которой соединен с прямым выходом первого триггера, а выход - с входом т Сброс второго счетчика, задатчиком кода, выход которого соединен с вторым входом схемы сравнения кодов, третьим реверсивным счетчиком, счетный вход которого соединен с выходом компаратора напряжения, а вхЪй управления реверсом счета и вход запрета счета - соответст- , с выходом БОЛЬШЕ и с выходом РАВНО схемы сравнения кодов, цифро- аналоговым преобразователем, вход /

которого соединен с выходом треть- его счетчика, а выход - с вторым входом интегратора.

Поставленная цель достигается также тем, что блок управления содержит последовательно соединенные третий триггер, линию задержки, шестую схему совпадения, четвертый триггер и вход Сброс четвертого счетчика соединены с генератором тактовых импульсов, выход шестой схемы совпадения соединен со счетным входом четвертого триггера, срабатывающего по спаду счетного импульса, инверсный выход четвертого триггера соединен с входом ЗАПРЕТ СЧЕТА четвертого счетчика и вторым входом - шестой схемы совпадения, третий вход шестой Схемы совпадения и счетный вход четвертого счетчика соединены с прямым выходом второго триггера, выход четвертого счетчика соединен со входами R третьего и четвертого триггеров, прямой выход третьего триггера соединен с управляющим входом третьего переключателя, а прямой выход четвертого триггера соединен с входом третьей сХемы совпадения и входом инвертора.

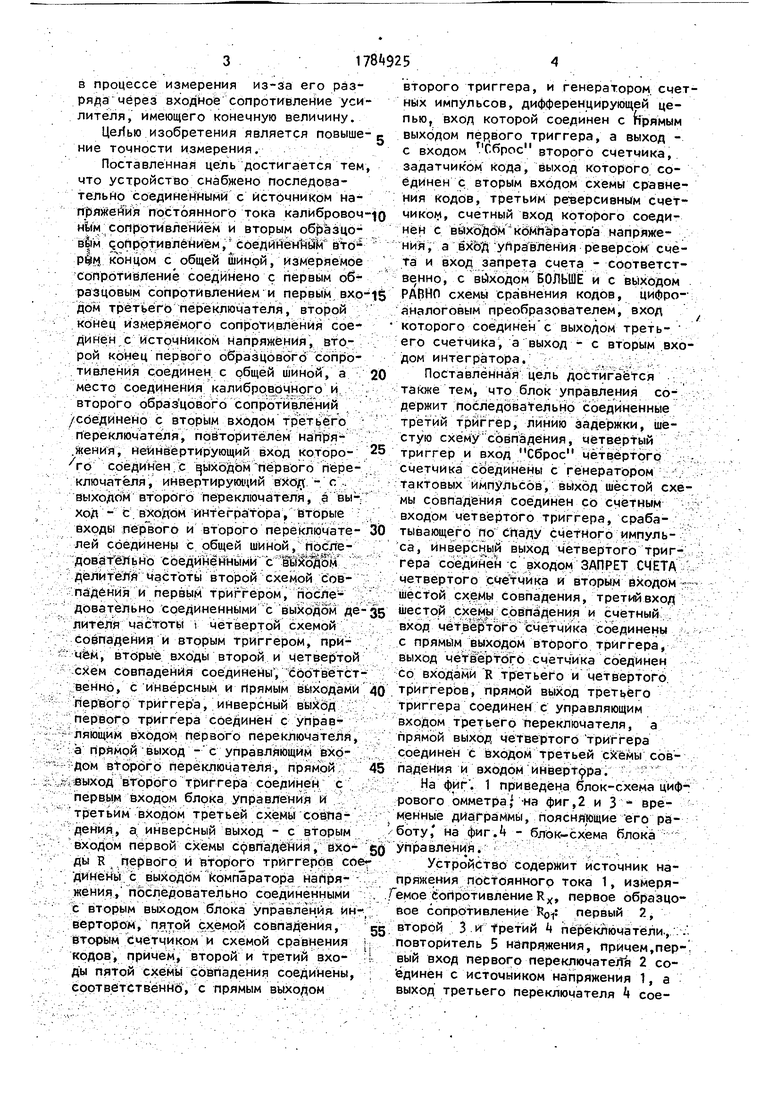

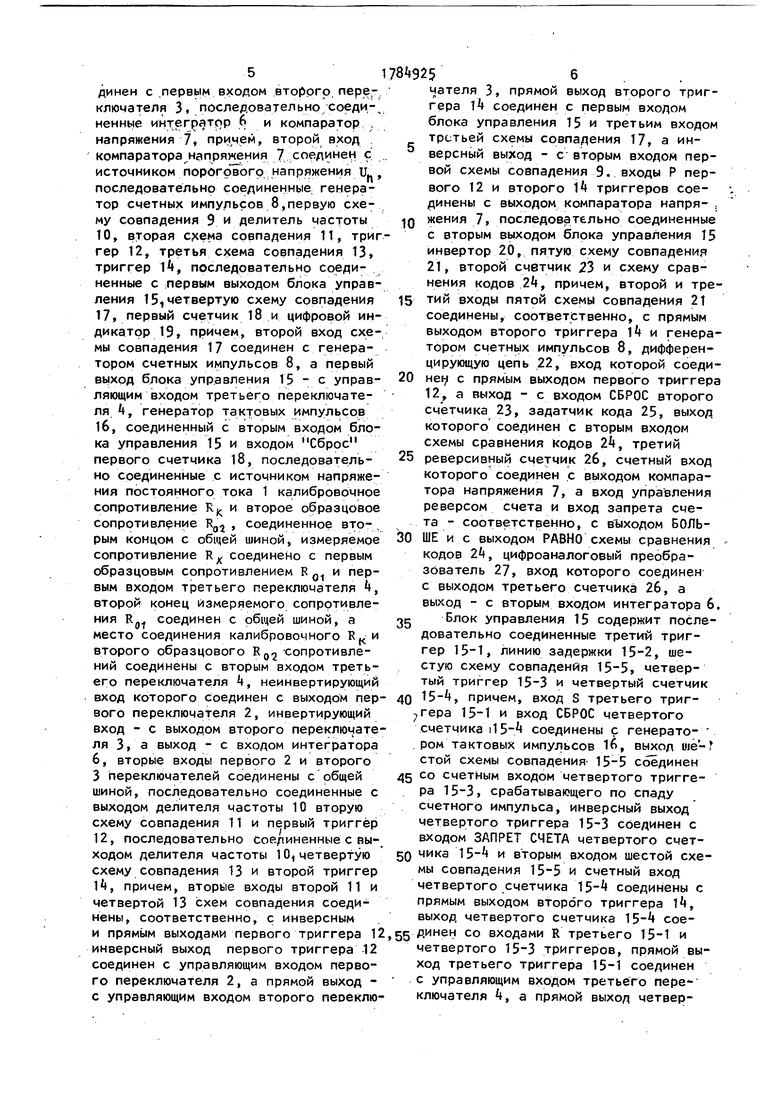

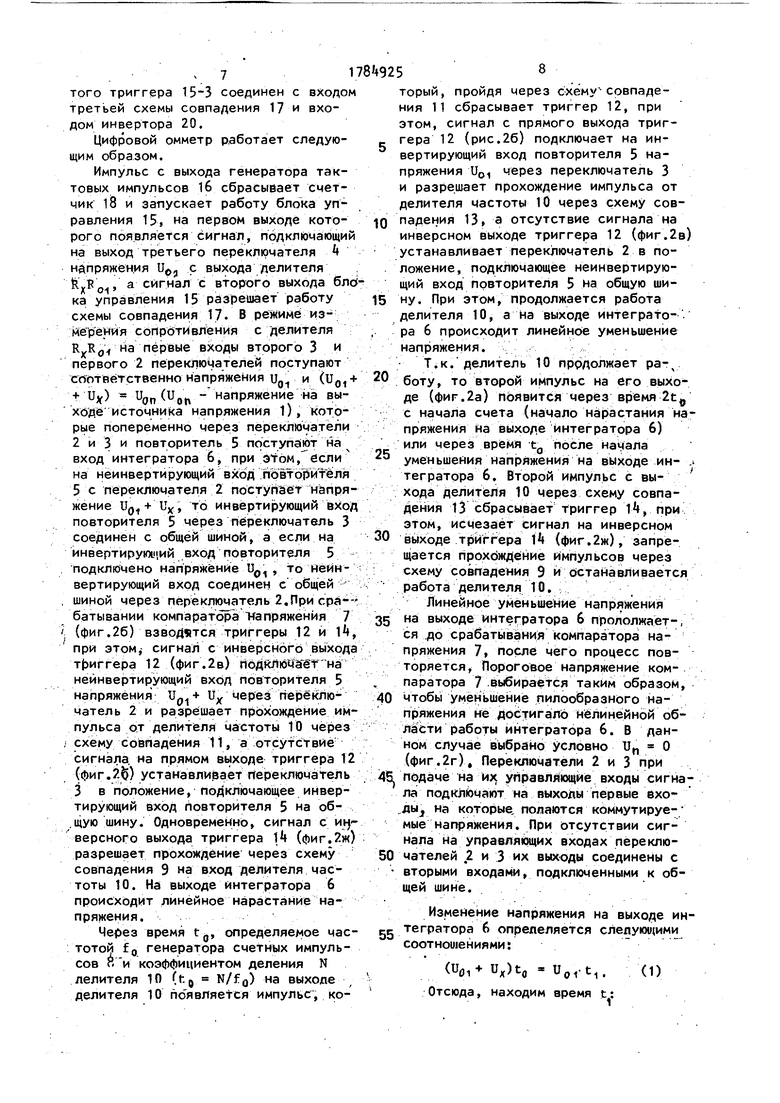

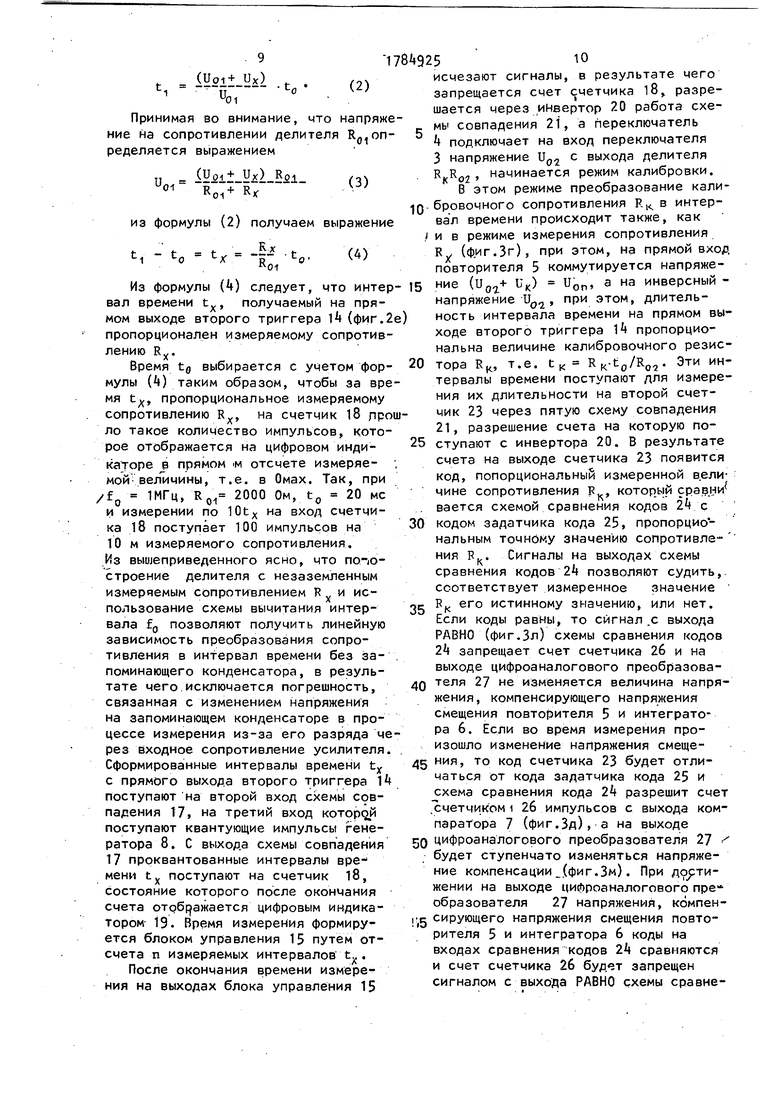

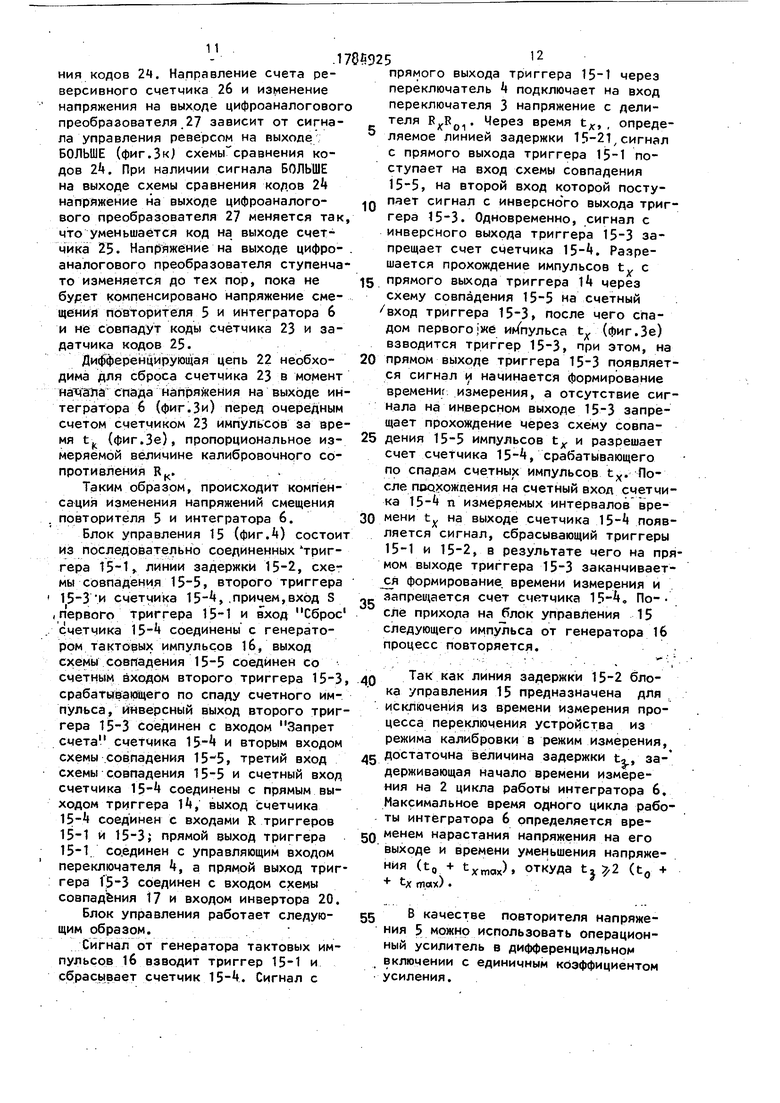

На фиг. 1 приведена блок-схема цифрового омметра; -на фиг,2 и 3 - временные диаграммы, поясняющие его работу, на фиг.k - блок-схема блока управления.

Устройство содержит источник напряжения постоянного тока 1, измеряемое сопротивление Rx, первое образцовое сопротивление RO-,: первый 2, второй 3 и Третий Ц переключатели,, . повторитель 5 напряжения, причем,первый вход первого переключателя 2 соединен с источником напряжения 1, а выход третьего переключателя А сое

5

динен с первым входом второго переключателя 3, последовательно соединенные интегратор 6 и компаратор напряжения 7, причем, второй вход компаратора напряжения 7 соединен с источником порогового напряжения Uft последовательно соединенные генератор счетных импульсов 8,первую схему совпадения 9 и делитель частоты 10, вторая схема совпадения 11, тригер 12, третья схема совпадения 13, триггер 14, последовательно соединенные с первым выходом блока управления 15,четвертую схему совпадения 17, первый счетчик 18 и цифровой индикатор 19, причем, второй вход схемы совпадения 17 соединен с генератором счетных импульсов 8, а первый выход блока управления 15 - с управляющим входом третьего переключателя 4, генератор тактовых импульсов 16, соединенный с вторым входом блока управления 15 и входом Сброс первого счетчика 18, последовательно соединенные с источником напряжения постоянного тока 1 калибровочно сопротивление Кк и второе образцово сопротивление RQ2 , соединенное вторым концом с общей шиной, измеряемо

сопротивление Rx соединено с первым образцовым сопротивлением R 01 и первым входом третьего переключателя 4, второй конец измеряемого сопротивления Rfl. соединен с общей шиной, а место соединения калибровочного Р«и второго образцового R02 сопротивлений соединены с вторым входом третьего переключателя 4, неинвертирующий вход которого соединен с выходом первого переключателя 2, инвертирующий вход - с выходом второго переключателя 3, а выход - с входом интегратора 6, вторые входы первого 2 и второго 3 переключателей соединены с общей шиной, последовательно соединенные с выходом делителя частоты 10 вторую схему совпадения 11 и первый триггер 12, последовательно соединенные с выходом делителя частоты 10,четвертую схему совпадения 13 и второй триггер 14, причем, вторые входы второй 11 и четвертой 13 схем совпадения соединены, соответственно, с инверсным

чателя 3, прямой выход второго триггера 14 соединен с первым входом блока управления 15 и третьим входом третьей схемы совпадения 17, а инверсный выход - с вторым входом первой схемы совпадения 9. входы Р первого 12 и второго 14 триггеров соединены с выходом компаратора напряжения 7, последовательно соединенные с вторым выходом блока управления 15 инвертор 20, пятую схему совпадения 21, второй счетчик 23 и схему сравнения кодов 24, причем, второй и третий входы пятой схемы совпадения 21 соединены, соответственно, с прямым выходом второго триггера 14 и генератором счетных импульсов 8, дифференцирующую цепь 22, вход которой соединен с прямым выходом первого триггера 12, а выход - с входом СБРОС второго счетчика 23, задатчик кода 25, выход которого соединен с вторым входом схемы сравнения кодов 24, третий 25 реверсивный счетчик 26, счетный вход которого соединен с выходом компаратора напряжения 7, а вход управления реверсом счета и вход запрета счета - соответственно, с выходом БОЛЬ- 30 ШЕ и с выходом РАВНО схемы сравнения кодов 24, цифроаналоговый преобразователь 27, вход которого соединен с выходом третьего счетчика 26, а выход - с вторым входом интегратора 6 35 Блок управления 15 содержит последовательно соединенные третий триггер 15-1, линию задержки 15-2, шестую схему совпадения , четвертый триггер и четвертый счетчик 40 15-4, причем, вход S третьего триг- гера 15-1 и вход СБРОС четвертого счетчика i15-4 соединены с генерато- ром тактовых импульсов 16, выход uie-f стой схемы совпадения 15-5 соединен 45 со счетным входом четвертого триггера 15-3, срабатывающего по спаду счетного импульса, инверсный выход четвертого триггера 15-3 соединен с входом ЗАПРЕТ СЧЕТА четвертого счет- 50 чика 15-4 и вторым входом шестой схемы совпадения и счетный вход четвертого счетчика соединены с прямым выходом второго триггера 14,

выход четвертого счетчика 15-4 сое- и прямым выходами первого триггера 12,55 Динен с° входами R третьего 15-1 и инверсный выход первого триггера 12 четвертого 15-3 триггеров, прямой вы- соединен с управляющим входом перво- ход третьего триггера 15-1 соединен го переключателя 2, а прямой выход - с управляющим входом третьего пере- с управляющим входом второго переклю- ключателя 4, а прямой выход четвер10

4925

5

0

6

чателя 3, прямой выход второго триггера 14 соединен с первым входом блока управления 15 и третьим входом третьей схемы совпадения 17, а инверсный выход - с вторым входом первой схемы совпадения 9. входы Р первого 12 и второго 14 триггеров соединены с выходом компаратора напряжения 7, последовательно соединенные с вторым выходом блока управления 15 инвертор 20, пятую схему совпадения 21, второй счетчик 23 и схему сравнения кодов 24, причем, второй и третий входы пятой схемы совпадения 21 соединены, соответственно, с прямым выходом второго триггера 14 и генератором счетных импульсов 8, дифференцирующую цепь 22, вход которой соединен с прямым выходом первого триггера 12, а выход - с входом СБРОС второго счетчика 23, задатчик кода 25, выход которого соединен с вторым входом схемы сравнения кодов 24, третий 5 реверсивный счетчик 26, счетный вход которого соединен с выходом компаратора напряжения 7, а вход управления реверсом счета и вход запрета счета - соответственно, с выходом БОЛЬ- 0 ШЕ и с выходом РАВНО схемы сравнения кодов 24, цифроаналоговый преобразователь 27, вход которого соединен с выходом третьего счетчика 26, а выход - с вторым входом интегратора 6. 5 Блок управления 15 содержит последовательно соединенные третий триггер 15-1, линию задержки 15-2, шестую схему совпадения , четвертый триггер и четвертый счетчик 0 15-4, причем, вход S третьего триг- гера 15-1 и вход СБРОС четвертого счетчика i15-4 соединены с генерато- ром тактовых импульсов 16, выход uie-f стой схемы совпадения 15-5 соединен 5 со счетным входом четвертого триггера 15-3, срабатывающего по спаду счетного импульса, инверсный выход четвертого триггера 15-3 соединен с входом ЗАПРЕТ СЧЕТА четвертого счет- 0 чика 15-4 и вторым входом шестой схемы совпадения и счетный вход четвертого счетчика соединены с прямым выходом второго триггера 14,

того триггера 15-3 соединен с входом третьей схемы совпадения 17 и входом инвертора 20.

Цифровой омметр работает следующим образом.

Импульс с выхода генератора тактовых импульсов 16 сбрасывает счетчик 18 и запускает работу блока управления 15, на первом выходе которого появляется сигнал, подключающий на выход третьего переключателя 4 напряжения 3Су с выхода делителя RXR ол, а сигнал с второго выхода блка управления 15 разрешает работу схемы совпадения 17. В режиме измерения сопротивления с делителя Rj,R0 на первые входы второго 3 и первого 2 переключателей поступают соответственно напряжения и., и (и„,

01

Joi

+ Uy) Uon(Uon - напряжение на выходе источника напряжения 1), которые попеременно через переключатели 2 и 3 и повторитель 5 поступают йа вход интегратора 6, при этом, если v на неинвертирующий вход повторителя 5 с переключателя 2 поступает напря

жение

+

JX

то инвертирующий вход

повторителя 5 через переключатель 3 соединен с общей шиной, а если на инвертирующий вход повторителя 5 подключено напряжение U01 , то неинвертирующий вход соединен с общей шиной через переключатель 2.При ера-- батывании компаратора Напряжения 7 (фиг.26) взводятся триггеры 12 и И, при этом, сигнал с инверсного выхода триггера 12 (фиг.2в) подключает на нейнвертирующий вход повторителя 5 напряжения U01+ Ux через переключатель 2 и разрешает прохождение импульса от делителя частоты 10 через схему совпадения 11, а отсутствие сигнала, на прямом выходе триггера 12 (фиг.2$) устанавливает переключатель 3 в положение, подключающее инвертирующий вход повторителя 5 на общую шину. Одновременно, сигнал с ин/- версного выхода триггера И (фиг.2ж) разрешает прохождение через схему совпадения 9 на вход делителя частоты 10. На выходе интегратора 6 происходит линейное нарастание напряжения.

t0, определяемое час-

Через время

тотой Ј0 генератора счетных импульсов Р. и коэффициентом деления N лелителя 10 (г. 0 N/f0) на выходе делителя 10 появляется импульс, ко0

0

5

торый, пройдя через схему совпадения 11 сбрасывает триггер 12, при этом, сигнал с прямого выхода триггера 12 (рис.26) подключает на инвертирующий вход повторителя 5 напряжения U01 через переключатель 3 и разрешает прохождение импульса от делителя частоты 10 через схему совпадения 13, а отсутствие сигнала на инверсном выходе триггера 12 (фиг.2в) устанавливает переключатель 2 в положение, подключающее неинвертирующий вход повторителя 5 на общую шину. При этом, продолжается работа делителя 10, а на выходе интегратора 6 происходит линейное уменьшение напряжения.

Т.к. делитель 10 продолжает ра-% боту, то второй импульс на его выходе (фиг.2а) появится через время 2te с начала счета (начало нарастания напряжения на выходе интегратора 6) или через время t0 после начала уменьшения напряжения на выходе ин- .. тегратора 6. Второй импульс с вы- хода делителя 10 через схему совпадения 13 сбрасывает триггер 1, при этом, исчезает сигнал на инверсном выходе триггера И (фиг.2ж), запрещается прохбждение импульсов через схему совпадения 9 и останавливается работа делителя 10.

Линейное уменьшение напряжения на выходе интегратора 6 продолжает-, ся до срабатывания компаратора напряжения 7, после чего процесс повторяется, Пороговое напряжение компаратора 7 выбирается таким образом, чтобы уменьшение пилообразного напряжения не достигало нелинейной области работы интегратора 6. В данном случае выбрано условно Un О (фиг.2г). Переключатели 2 и 3 при 5j подаче на их управляющие входы сигнала подключают на выходы первые ехо- „ды на которые полаются коммутируе- мые напряжения. При отсутствии сигнала на управляющих входах переклю- 50 чателей 2 и 3 их выходы соединены с вторыми входами, подключенными к общей шине.

0

5

0

Изменение напряжения на выходе интегратора 6 определяется следующими соотношениями:

н+ ux)t0 - U01-t1§

Отсюда, находим время t:

(1)

(Uoi+ Ux)

и,

(2)

01

Принимая во внимание, что напряжение на сопротивлении делителя R01определяется выражением

U OL

oi +

Ux)

R

R

:01

(3)

з формулы (2) получаем выражение i to - Ч- Г te. (4)

Л ИПОВТ

з формулы (4) следует, что интер- 15 ние (и

В эт 10 бровочн вал вре i и в реж

Ry (фи повтор напряж ность и ходе в нальна тервал ния их чик 23 21, ра 25 ступаю счета код, п чине со вается кодом нальным

вал времени tx, получаемый на прямом выходе второго триггера И (фиг.2е) пропорционален измеряемому сопротивлению Rx.

Время t0 выбирается с учетом фор- 20 тора RK; мулы (k) таким образом, чтобы за время t, пропорциональное измеряемому сопротивлению RX, на счетчик 18 прошло такое количество импульсов, которое отображается на цифровом индикаторе в прямом м отсчете измеряв- ; мой величины, т.е. в Омах. Так, при Ј0 - 1МГц, R01 2000 Ом, t0 20 мс и измерении по 10tx на вход счетчика 18 поступает 100 импульсов на 10 м измеряемого сопротивления. Из вышеприведенного ясно, что по-ю- строение делителя с незаземленным

Ry (фиг. повторит ог напряжен ность ин ходе вто нальна в тервалы ния их д чик 23 ч 21, разр 25 ступают счета на код, поп чине соп вается с кодом за нальным

30

ния РК.

сравнени соответс Рк его и Если код РАВНО (ф 2k запре выходе ц теля 27 жения, к смещения ра 6. Ес изошло и

измеряемым сопротивлением R и использование схемы вычитания интервала Ј0 позволяют получить линейную зависимость преобразования сопротивления в интервал времени без запоминающего конденсатора, в результате чего исключается погрешность, связанная с изменением напряжения на запоминающем конденсаторе в процессе измерения из-за его разряда чрез входное сопротивление усилителя Сформированные интервалы времени tx с прямого выхода второго триггера поступают на второй вход схемы совпадения 17, на третий вход которой поступают квантующие импульсы генератора 8. С выхода схемы совпадения 17 проквантованные интервалы времени tx поступают на счетчик 18, состояние которого после окончания счета отображается цифровым индикатором 19. Время измерения формируется блоком управления 15 путем отсчета п измеряемых интервалов t...

После окончания времени измерения на выходах блока управления 15

ПОВТ

15 ние (и

81 92510

исчезают сигналы, в результате чего запрещается счет счетчика 18, разрешается через инвертор 20 работа схемы совпадения 21, а переключатель k подключает на вход переключателя 3 напряжение U02 с выхода делителя R R02, начинается режим калибровки.

В этом режиме преобразование кали- 10 бровочного сопротивления Р.к в интервал времени происходит также, как i и в режиме измерения сопротивления

) 20 тора RK;

Ry (фиг.Зг), при этом, на прямой вход повторителя 5 коммутируется напряже- ог+ UK) Uon, а на инверсный - напряжение , при этом, длительность интервала времени на прямом выходе второго триггера k пропорциональна величине калибровочного резис- т.е. tK RK-t0/R02. Эти интервалы времени поступают для измерения их длительности на второй счетчик 23 через пятую схему совпадения 21, разрешение счета на которую по- 25 ступают с инвертора 20. В результате счета на выходе счетчика 23 появится код, попорциональный измеренной величине сопротивления БК, который сравни вается схемой сравнения кодов 2ч с кодом задатчика кода 25, пропорциональным точному значению сопротивле™

30

тора RK;

ния РК. Сигналы на выходах схемы

сравнения кодов 2k позволяют судить, соответствует измеренное значение Рк его истинному значению, или нет. Если коды равны, то сигнал .с выхода РАВНО (фиг.Зл) схемы сравнения кодов 2k запрещает счет счетчика 26 и на выходе цифроаналогового преобразователя 27 не изменяется величина напряжения, компенсирующего напряжения смещения повторителя 5 и интегратора 6. Если во время измерения произошло изменение напряжения смещения, то код счетчика 23 будет отличаться от кода задатчика кода 25 и схема сравнения кода 2k разрешит счет .Счетчиком 1 26 импульсов с выхода компаратора 7 (фиг.Зд), а на выходе

цифроаналогового преобразователя 27 s будет ступенчато изменяться напряжение компенсации(фиг.Зм). При достижении на выходе цисЬроаналогового преобразователя 27 напряжения, компенсирующего напряжения смещения повторителя 5 и интегратора 6 коды на входах сравнения кодов 2k сравняются и счет счетчика 26 будет запрещен сигналом с выхода РАВНО схемы сравне11

ния кодов 24. Направление счета реверсивного счетчика 26 и изменение напряжения на выходе цифроаналогового преобразователя.27 зависит от сигнала управления реверсом на выходе БОЛЬШЕ (фиг.Зк) схемьГсравнения кодов 2. При наличии сигнала БОЛЬШЕ на выходе схемы сравнения ко/юв 2 напряжение на выходе цифроаналогового преобразователя 27 меняется так, что уменьшается код на выходе счетчика 25. Напряжение на выходе цифро- аналогового преобразователя ступенчато изменяется до тех пор, пока не будет компенсировано напряжение смещения повторителя 5 и интегратора 6 и не совпадут коды счетчика 23 и за- датчика кодов 25.

Дифференцирующая цепь 22 необходима для сброса счетчика 23 в момент начала спада напряжения на выходе интегратора 6 (фиг.Зи) перед очередным счетом счетчиком 23 импульсов за время

t (фиг.Зе), пропорциональное измеряемой величине калибровочного сопротивления RK.

Таким образом, происходит компенсация изменения напряжений смещения повторителя 5 и интегратора 6.

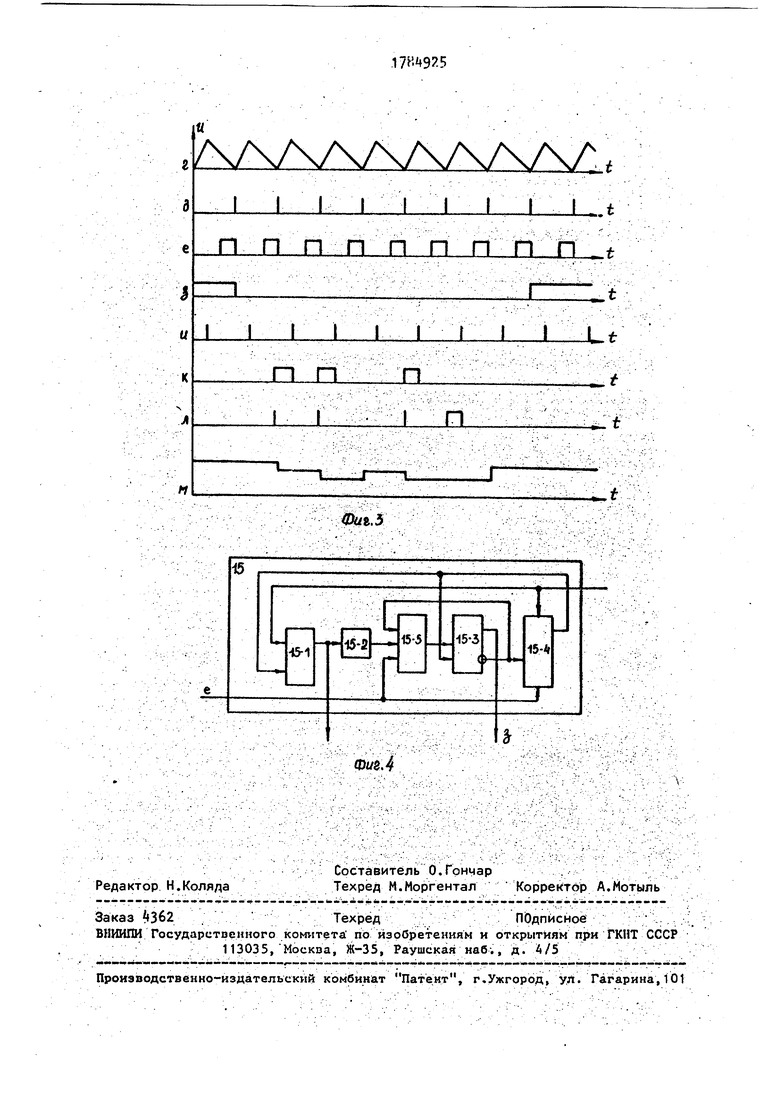

Блок управления 15 (фиг.А) состоит из последовательно соединенных триггера 15-1 линии задержки 15-2, схемы совпадения , второго триггера 15-3 и счетчика 15-, причем,вход S .первого триггера 15-1 и вход Сброс счетчика 15- соединены с генератором тактовых импульсов 16, выход схемы совпадения 15-5 соединен со счетным входом второго триггера 15-3 срабатывающего по спаду счетного импульса, инверсный выход второго триггера 15-3 соединен с входом Запрет счета счетчика 15- и вторым входом схемы совпадения , третий вход схемы совпадения 15-5 и счетный вход счетчика 15- соединены с прямым выходом триггера 1, выход счетчика 15- соединен с входами R триггеров 15-1 и 15-3; прямой выход триггера 15-1 соединен с управляющим входом переключателя , а прямой выход триггера 15-3 соединен с входом схемы совпадения 17 и входом инвертора 20.

Блок управления работает следующим образом.

Сигнал от генератора тактовых импульсов 16 взводит триггер 15-1 и сбрасывает счетчик 15-. Сигнал с

12

прямого выхода триггера 15-1 через переключатель подключает на вход переключателя 3 напряжение с делителя

Через время tx,, опреде0

ляемое линией задержки 15-21,сигнал с прямого выхода триггера 15-1 поступает на вход схемы совпадения 15-5, на второй вход которой поступает сигнал с инверсно го выхода триггера 15-3. Одновременно, сигнал с инверсного выхода триггера 15-3 запрещает счет счетчика 15-. Разрешается прохождение импульсов tx с прямого выхода триггера 1 через схему совпадения 15-5 на счетный /вход триггера 15-3 после чего спадом первого;же импульса tx (йиг.Зе) взводится триггер , при этом, на

0 прямом выходе триггера появляется сигнал и начинается Формирование времениг измерения, а отсутствие сигнала на инверсном выходе 15-3 запрещает прохождение через схему совпа5 дения 15-5 импульсов tx и разрешает счет счетчика 15-, срабатывающего по спадам счетных импульсов tx. После поохождения на счетный вход счетчика 15- п измеряемых интервалов вре0 мени tx на выходе счетчика 15- появляется сигнал, сбрасывающий триггеры 15-1 и 15-2, в результате чего на прямом выходе триггера 15-3 заканчивает- ся формирование времени измерения и запрещается счет счетчика 15-. По- еле прихода на блок управления 15 следующего импульса от генератора 16 процесс повторяется.

5

Так как линия задержки 15-2 блока управления 15 предназначена для исключения из времени измерения процесса переключения устройства из режима калибровки в режим измерения,

достаточна величина задержки t., за- держивающая начало времени измерения на 2 цикла работы интегратора 6. Максимальное время одного цикла работы интегратора 6 определяется временем нарастания напряжения на его выходе и времени уменьшения напряжения (t0 + txmaj, откуда tj (t0 + ix) «

+ tx rnax)

В качестве повторителя напряжения 5 можно использовать операционный усилитель в дифференциальном включении с единичным коэффициентом усиления.

Формулэ изобретения

1. Цифровой омметр, содержащий источник напряжения постоянного то- ка, измеряемое сопротивление, первое образцовое сопротивление, первый, второй и третий переключатели, причем первый вход первого переключателя соединен с источником напряжения, а ВЫ-JQ ход третьего переключателя соединен с первым входом второго . переключателя, последовательно соединенные интегратор и компаратор напряжения, причем

второй вход компаратора напряжения 15 соединен с источником порогового напряжения, последовательно соединенные генератор счетных импульсов, первую схему совпадения и делитель частоты, последовательно соединенные с пер- 20 вым выходом блока управления т ретью схему совпадения, первый счетчик и цифровой индикатор, причем второй

вход третье схемы совпадения соединен с генератором счетных импульсов, 25 а первый выход блока управления - с управляющим входом третьего переключателя, генератор тактовых импульсов, соединенный с вторым входом блока управления и входом Сброс первого 30 счетчика, отличающийся тем что, с целью повышения точности измерения, в него введены последовательно соединенные с источником напряжения постоянного тока калибровоч-gg ное сопротивление и второе образцовое сопротивление, соединенное вторым кон цом с общей шиной, измеряемое сопротивление соединено с первым образцовым сопротивлением и первым входом 40 третьего переключателя, второй конец измеряемого сопротивления соединен с источником напряжения, второй конец первого образцового сопротивления с общей шиной, а место соединения ка- 45 либровочного и второго образцового сопротивлений - с вторым входом третьего переключателя, повторитель напряжения, неинвертирующий вход которого соединен с выходом первого en переключателя, инвертирующий вход - с выходом второго переключателя, а выход - с входом интегратора, вторые входы .первого и второго переключателей соединены с общей шиной, по- ее следовательно соединенные с выходом делителя частоты вторая схема совпадения и первый триггер, последовательно соединенные с выхогом делителя

частоты четвертая схема совпадения и второй триггер, причем вторые входы второй и четвертой схем совпадения соединены соответственно с инверсным и прямым выходами первого / триггера, инверсный выход первого триггера соединен с управляющим входом второго переключателя, а прямой вы ход - с управляющим входом второго преключателя, прямой выход второго триггера соединен с первым входом блока управления и третьим входом третьей схемы совпадения, а инверсный выход - с вторым входом первой схемы совпадения, R-входы первого и второго триггеров соединены с выходом компаратора напряжения, последовательно соединенные с вторым выходом блока управления инвертор, пятая схема совпадения, второй счетчик и схема сравнения кодов, причем второй и третий входы пятой схемы совпадения соединены соответственно с прямым выходом второго триггера и , генератором счетных импульсов, дифференцирующая цепь, вход которой соединен с прямым выходом первого триггера, а выход - с входом Сброс второго счетчика, задатчик кода, выход которого соединен с вторым входом схемы сравнения кодов, третий реверсивный счетчик, счетный вход которого соединен с выходом компаратора напряжения, а вход управления реверсом счета и вход запрета сче- та - соответственно с выходами Боль ше и Равно схемы сравнения кодов, цифроаналоговый преобразователь, вход которого соединей с выходом третьего счетчика, а выход - с вторым входом интегратора.

2. Омметр поп.1,отличаю- щ и и с я тем, что блок управления содержит последовательно соединенные третий триггер, линию задержки, ше-: стую схему совпадения, четвертый триггер и четвертый счетчик,причем i S-вход третьего триггера и вход Сброс четвертого счетчика соединены с генератором тактовых импульсов, выход шестой схемы совпадения соединен со счетным входом четвертого триггера, срабатывающего по спаду счетного импульса, инверсный выход четвертого триггера соединен с входом Запрет счета четвертого счетчика и вторым входом шестой схемы совпадения, третий вход шестой схемы совпадения и

счетный вход четвертого счетчика соединены с прямым выходом второго триггера, выход четвертого счетчика - с 4Е-входами третьего и четвертого триггеров, прямой выход третьего триггера соединен с управляющим входом третьего переключателя, а прямой выход четвертого триггера - с входами третьей схемы совпадения и инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Устройство для измерения сопротивления | 1988 |

|

SU1649468A1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU942095A1 |

| Устройство для измерения произведения двух напряжений | 1983 |

|

SU1195265A1 |

| Цифровой тахометр | 1986 |

|

SU1352371A2 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Цифровой измеритель температуры | 1985 |

|

SU1278622A1 |

| Цифровой измеритель CLR-параметров двухполюсников | 1986 |

|

SU1370613A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1697265A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

Использование: в измерительной технике для цифрового измерения электрического сопротивления постоянному току. Сущность изобретения: устройство содержит источник напряжения постоянного тока 1, измеряемое сопротивление Rx, два образцовых сопротивления R . R 2, калибровочное сопротивление R, три переключателя 2, 3, , повторитель напряжения 5, интегратор 6, компаратор напряжения 7, генератор счетных импульсов 8, четыре схемы совпадения 9, 11, 13, 17, 21, делитель частоты 10, два триггера 12, , блок управления 15, генератор тактовых импульсов 16, три счетчика 18, 23, 26, индикатор 19, инвертор 20, схему сравнения коров 2k, задатчик кода 25, цифроана- логовый преобразователь 27. Особенность изобретения - построение преобразователя сопротивления в напряжение в виде делителя напряжения с незаземленным Ry и вычитание из измеряемого интервала времени, после преобразования напряжения в интервал времени опорного интервала времени t, а также компенсация напряжения смещения повторителя 5 и интегратора 6 в режиме измерения калибровочного сопротивления. А ил.

к. ° -aajm °

Д-

Фиг2

Фиг.1

1-Г.

Лч/ЧЛч/Ч/Ч/Ч/Ч/Ч/Ч.,

I I I I I I I I I f

ППППППППП.

и

I I I I I I I I I I,

n n

JL

Фиг.5

n

J0.

| Авторское свидетельство СССР № , кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| ( ЦИФРОВОЙ ОММЕТР | |||

Авторы

Даты

1992-12-30—Публикация

1990-08-03—Подача