Изобретение относится к измерительной технике, а именно к средствам измерения угловых скоростей и может найти применение в машиностроении и приборостроении.

Целью изобретения является расширение верхнего предела измерений и уменьшение динамической погрешности

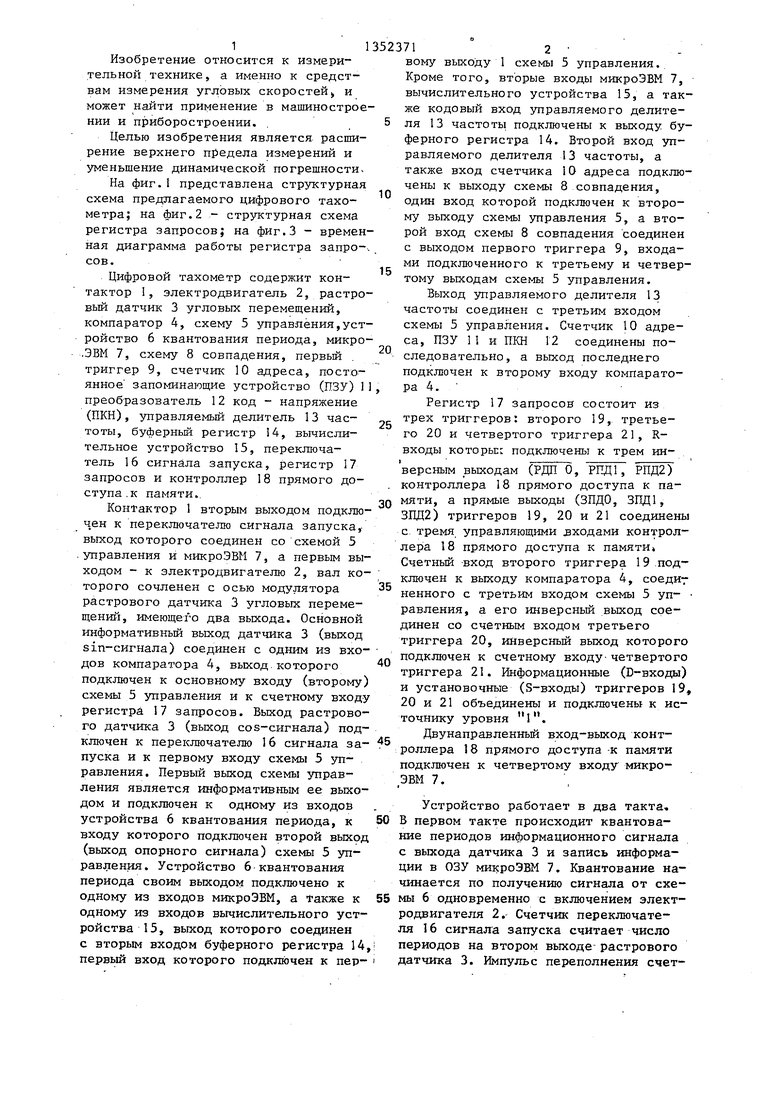

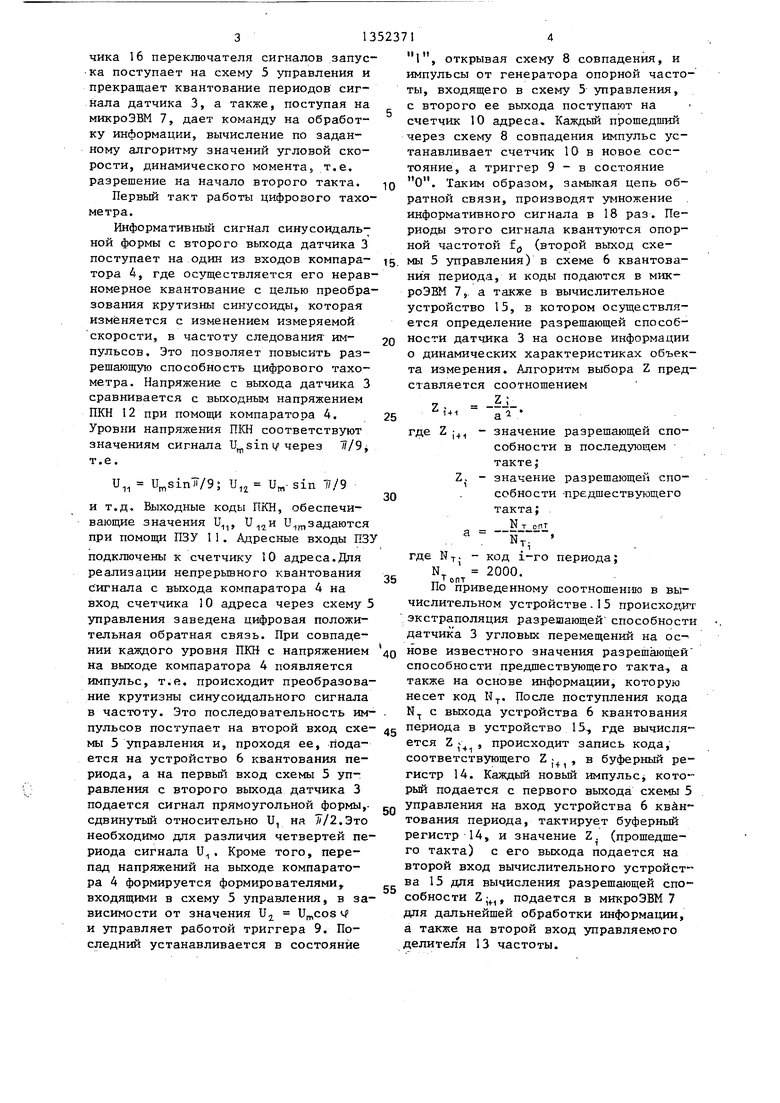

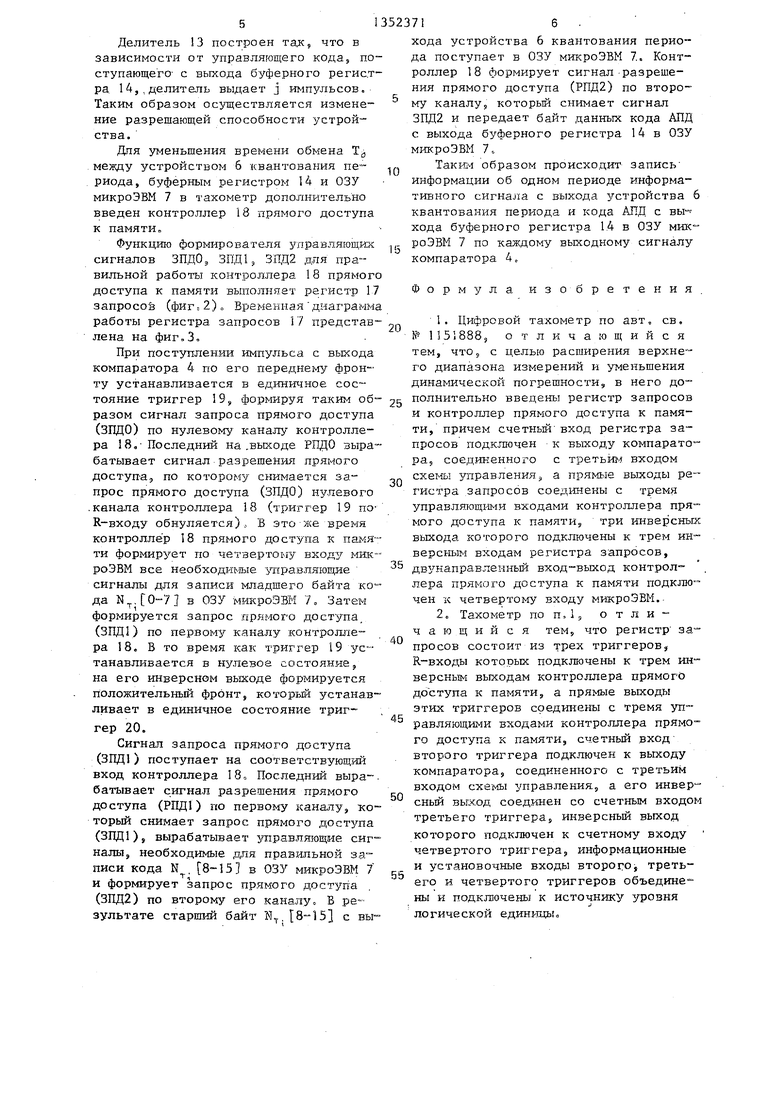

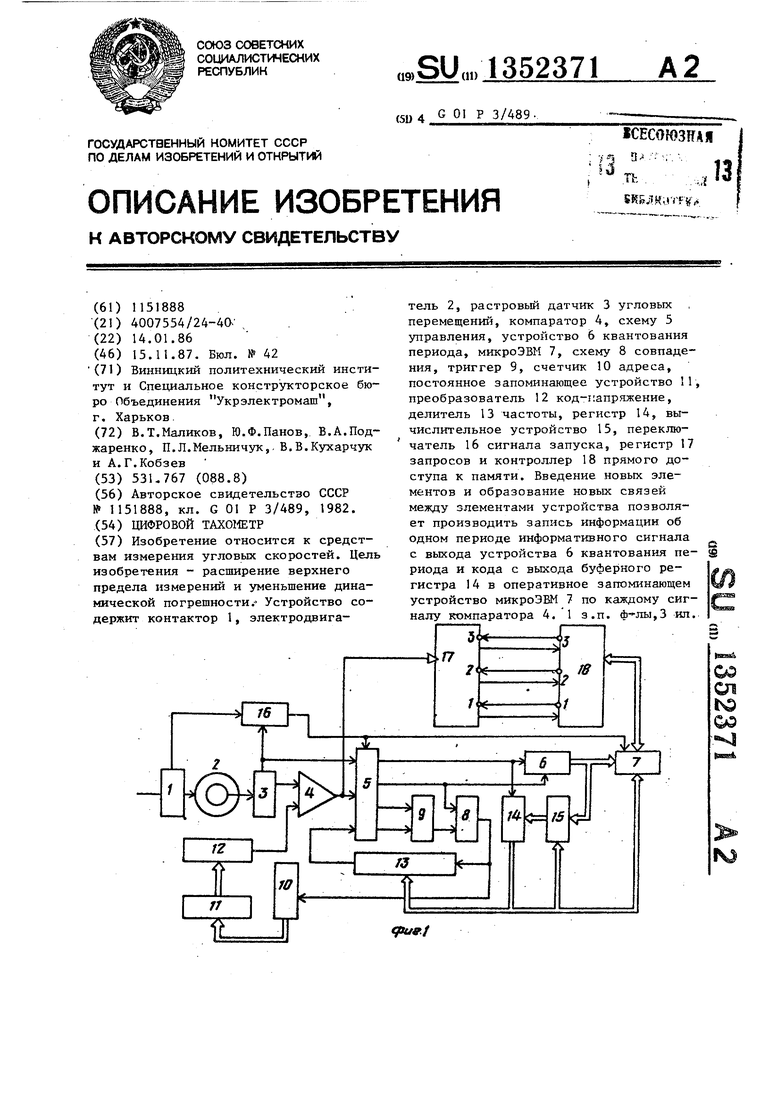

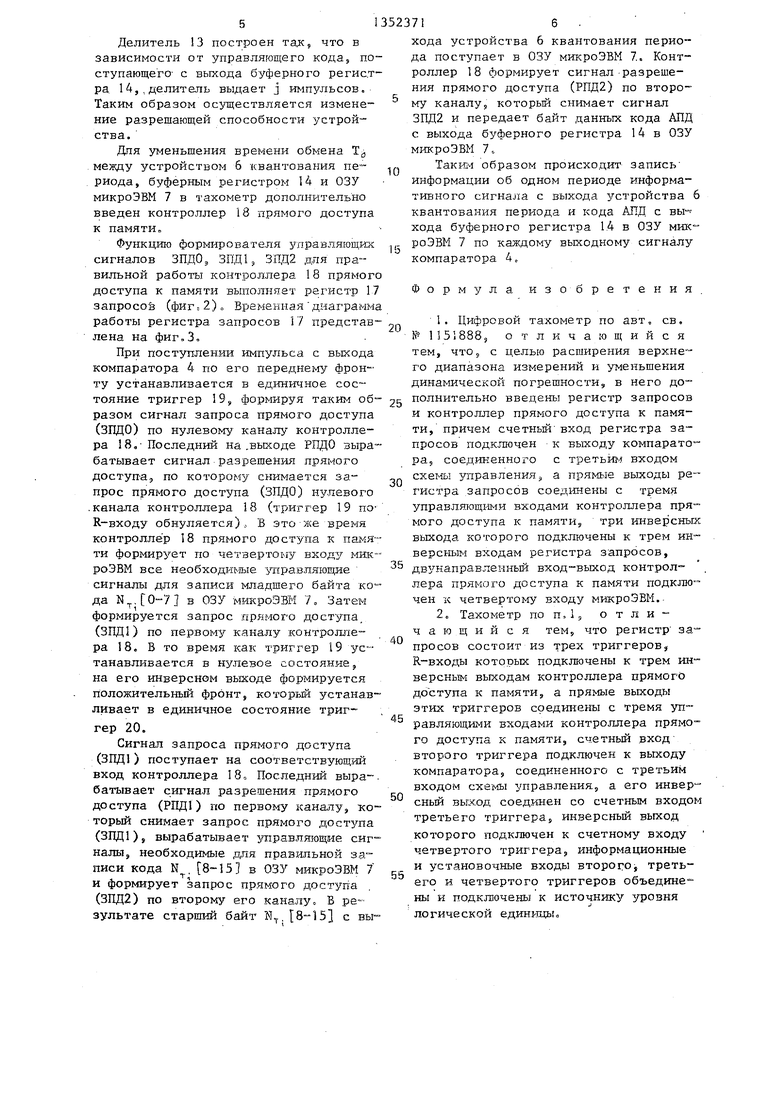

На фиг.1 представлена структурная схема предлагаемого цифрового тахометра; на фиг.2 - структурная схема регистра запросов; на фиг.З - временная диаграмма работы регистра запро-. сов.

Цифровой тахометр содержит контактор 1, электродвигатель 2, растровый датчик 3 угловых перемещений, компаратор 4, схему 5 управления,устройство 6 квантования периода, микро- ,ЭВМ 7, схему 8 совпадения, первьй триггер 9, счетчик 10 адреса, постоянное запоминающие устройство (ПЗУ) 1 преобразователь 12 код - напряжение (ПКН), управляемый делитель 13 частоты, буферньш регистр 14, вычислительное устройство 15, переключатель 16 сигнала запуска, регистр 17 запросов и контроллер 18 прямого доступа, к памяти..

Контактор I вторым выходом подклю- ч.ен к переключателю сигнала запуска,- выход которого соединен со схемой 5 .управления и микроЭВМ 7, а первым выходом - к электродвигателю 2, вал которого сочленен с осью модулятора растрового датчика 3 угловых перемещений, имеющего два выхода. Основной информативный выход датчика 3 (выход sin-сигнала) соединен с одним из входов компаратора 4, выход.которого подключен к основному входу (второму) схемы 5 управления и к счетному входу регистра 17 запросов. Выход растрового датчика 3 (выход соз-сигнала) подключен к переключателю 16 сигнала запуска и к первому входу схемы 5 управления. Первый выход схемы управления является информативным ее выходом и подключен к одному из входов устройства 6 квантования периода, к входу которого подключен второй выход (выход опорного сигнала) схемы 5 управления. Устройство 6 квантования периода своим выходом подключено к одному из входов микроэвм, а также к Одному из входов вычислительного устройства 15, выход которого соединен с вторым входом буферного регистра 14 первый вход которого подключен к пер-

,

10

523712

вому выходу 1 схемы 5 управления. Кроме того, вторые входы микроЭВМ 7, вычислительного устройства 15, а также кодовый вход заправляемого делителя 13 частоты подключены к выходу буферного регистра 14. Второй вход управляемого делителя 13 частоты, а также вход счетчика Ш адреса подключены к выходу схемы 8 совпадения, один вход которой подключен к второму выходу схемы управления 5, а второй вход схемы 8 совпадения соединен с выходом первого триггера 9, входами подключенного к третьему и четвертому выходам схемы 5 управления.

Выход управляемого делителя 13 частоты соединен с третьим входом схемы 5 управления. Счетчик 10 адреса, ПЗУ I1 и ПКН 12 соединены последовательно , а вьпсод последнего подключен к второму входу компаратора 4.

Регистр 17 запросов состоит из трех триггеров: второго 19, третьего 20 и четвертого триггера 21, R- входы которьс: подключены к трем ин15

20

25

версным выходам (РДП О, РПД1, РПД2) контроллера 18 прямого доступа к памяти, а прямые выходы (ЗПДО, ЗПД1, ЗПД2) триггеров 19, 20 и 21 соединены с тремя управляющими зходами контроллера 18 прямого доступа к памяти. Счетный -вход второго триггера 19 .подключен к выходу компаратора 4, соедиг ненного с третьим входом схемы 5 уп- равления, а его инверсньй выход соединен со счетным входом третьего триггера 20, инверсньш выход которого подключен к счетному входу-четвертого триггера 21. Информационные (D-входы) и установочные (S-входы) триггеров 19, 20 и 21 объединены и подключены к источнику уровня l.

Двунаправленньй вход-выход контроллера 18 прямого доступа -к памяти подключен к четвертому входу микро- ЭВМ 7.

Устройство работает в два такта, В первом такте происходит квантование периодов информационного сигнала с выхода датчика 3 и запись информации в ОЗУ микроэвм 7. Квантование начинается по получению сигнала от схе- мы 6 одновременно с включением электродвигателя 2. Счетчик переключателя 16 сигнала запуска считает число периодов на втором выходе растрового датчика 3. Импульс переполнения счет313

чика 16 переключателя сигналов запуска поступает на схему 5 управления и прекращает квантование периодов сигнала датчика 3, а также, поступая на микроэвм 7, дает команду на обработку информации, вычисление по задан- ному алгоритму значений угловой скорости, динамического момента т.е. разрешение на начало второго такта.

Первый такт работы цифрового тахометра.

Информативный сигнал синусоидальной формы с второго выхода датчика 3

поступает на один из входов компаратора 4, где осуществляется его неравномерное квантование с целью преобразования крутизны синусоиды, которая изменяется с изменением измеряемой скорости, в частоту следования- импульсов. Это позволяет повысить разрешающую способность цифрового тахометра. Напряжение с выхода датчика 3 сравнивается с выходным напряжением ПКН 12 при помощи компаратора 4. Уровни напряжения ПКН соответствуют значениям сигнала U sin i/через 7/9 j т.е.

и

11

)i/9; U, и„-31п Т//9

и т.д. Выходные коды ПКН, обеспечивающие значения U, и задаются при помощи ПЗУ 11. Адресные входы ПЗУ

подключены к счетчику 10 адреса.Для реализации непрерьтного квантования сигнала с выхода компаратора 4 на вход счетчика 10 адреса через схему 5 управления заведена цифровая положительная обратная связь. При совпадении каждого уровня ПКН с напряжением на выходе компаратора 4 появляется импульс, т.е. происходит преобразование крутизны синусоидального сигнала в частоту. Это последовательность импульсов поступает на второй вход схе- 45 п РИ°Да в устройство 15-, где вычислямы 5 управления и, проходя ее, подается на устройство 6 квантования периода, а на первый вход схемы 5 управления с второго выхода датчика 3 подается сигнал прямоугольной формы,- сдвинутый относительно U, на J/2,3ro необходимо дпя различия четвертей периода сиг нала U . Кроме того, перепад напряжений на вьпсоде компаратора 4 формируется формирователями.

ется

2 i.. .

происходит запись кода.

50

55

соответствующего Z j , в буферный регистр 14. Каждый новый импульс, кото рый подается с первого выхода схемы 5 управления на вход устройства 6 квйн- тования периода, тактирует буферньй регистр 14, и значение Z. (прошедшего такта) с его выхода подается на второй вход вычислительного устройст ва 15 для вычисленри разрешающей сповходящими в схему 5 управления, в за- собности Z j,, подается в микроЭВМ 7

висимости от значения U Un,cos и управляет работой триггера 9. Последний устанавливается в состояние

0

5

|| II

, открывая схему 8 совпадения, и импульсы от генератора опорной частоты, входящего в схему 5 управления, с второго ее выхода поступают на счетчик 10 адреса. Каждый прошедший через схему 8 совпадения импульс устанавливает счетчик 10 в новое сос, а триггер 9 - в состояние Таким образом, замыкая цепь обратной связи, производят умножение . информативного сигнала в 18 раз. Периоды этого сигнала квантуются опорной частотой f(j (второй выход схетояниеО

5. мы 5 управления) в схеме 6 квантования периода, и коды подаются в мик- роЭВМ 7,. а также в вычислительное устройство 15, в котором осуществляется определение разрешающей способности датчика 3 на основе информации о динамических характеристиках объекта измерения. Алгоритм выбора Z представляется соотношением

Z . да

где Z j - значение разрешающей способности в последующем такте J

Z. - значение разрешающей спо- Q . собности -предшествующего такта; .

К т опт

0

5

N

т.

где NT- - код i-ro периода; N 2000.

TT onT

Но приведенному соотношению в вычислительном устройстве . 15 происход.ит ;экстраполяция разрешающей способности датчик а 3 угловых перемещений на ос- нове известного значения разрешающей способности предшествующего такта, а также на основе информации, которую несет код N.. После поступления кода N с выхода устройства 6 квантования

п РИ°Да в устройство 15-, где вычисляется

2 i.. .

происходит запись кода.

соответствующего Z j , в буферный регистр 14. Каждый новый импульс, кото рый подается с первого выхода схемы 5 управления на вход устройства 6 квйн- тования периода, тактирует буферньй регистр 14, и значение Z. (прошедшего такта) с его выхода подается на второй вход вычислительного устройст ва 15 для вычисленри разрешающей способности Z j,, подается в микроЭВМ 7

для дальнейшей обработки информации, а также на второй вход управляемого делител я 13 частоты.

Делитель 3 построен тад, что в зависимости от управляющего кода, поступающего- с выхода буферного регистра 14,,делитель выдает j импзшьсов. Таким образом осуществляется изменение разрешающей способности устройства.

Для уменьшения времени обмена Т . между устройством 6 квантования пе™ . риода, буферным регистром 14 и ОЗУ микроэвм 7 в тахометр дополнительно введен контроллер 18 прямого доступа к памяти.

Функцию формирователя улравляЕощшг сигналов ЗПДО, ЗДЩ, ЗЩ2 для правильной работы контроллера 18 прямого доступа к памяти выполняет регистр 17 запросов ()о Временная диаграмма работы регистра запросов i 7 представлена на фиг,3

При поступлении импульса с выхода компаратора 4 по его nepeAHeivry фронту устанавливается в единичное состояние триггер 19,, формируя таким образом сигнал запроса прямого доступа (ЗПДО) по нулевому каналу контроллера 18,-Последний на .выходе РПДО вырабатывает сигнал разр ешения лрямого доступ-а, по которому снимается запрос прямого доступа (ЗПДО) нулевого .канала контроллера 18 (триггер 19 по- R-входу обнуляется), В это же время контроллер 18 прямого доступа к памя-- ти формирует по четвертому входу мик- роЭВМ все необходимые втравляющие сигналы для записи младшего байта кода N,.,0--7 в ОЗУ микроэвм 7, Затем формируется запрос прямого доступа, (ЗПД1) по первому каналу контроллера 18« В то время как триггер 19 устанавливается в нулевое состояние, на его инверсном выходе формируется положительный фронтj который устанавливает в единичное состояние триггер 20.

Сигнал запроса прямого доступа (ЗПД1) поступает на соответствующий вход контроллера 18 Последний вырабатывает сигнал разрешения прямого доступа (РПД1) по первому каналу, -который снимает запрос прямого достзша (ЗПД1), вырабатывает управляющие сигналы, необходимые дд1Я правильной за™ писи кода N, 8-15 в ОЗУ микроЭВМ 7 и формирует запрос прямого доступа (ЗПД2) по второму его каналу, Б результате старший байт й,8-15 с вы523716 .

хода устройства 6 квантования периода поступает в ОЗУ микроЭВМ 7. Контроллер 18 формирует сигнал-разрешения прямого доступа (РПД2) по второму каналу5 который снимает сигнал ЗПД2 и передает байт данных кода АИД с выхода буферного регистра 14 в ОЗУ микроэвм 7.

Таким образом происходит запись информации об одном периоде информативного сигнала с выхода устройства 6 квантования периода и кода АПД с выхода буферного регистра 1.4 в ОЗУ мик- роЭВМ 7 по каждому выходному сигналу компаратора 4.

0

15

0

5

0

0

5

0

5

Формула изобретения.

1. Цифровой тахометр по авт, св. № 11518885 отличающийся тем, что, с целью расширения верхнего диапазона измерений и уменьшения динамической погрешности, в него дополнительно введены регистр запросов и контроллер прямого доступа к памяти, причем счетный вход регистра запросов подключен к выходу компаратора, соединенного с третьй л- входом схегФ управления, а прямьле выходы регистра запросов соединены с тремя управляющими входами контроллера прямого доступа к памяти, три инверсньо ; выхода которого подключены к трем инверсным входам регистра запросов, 5 двунаправленньш вход-выход контрол- . лера прямого доступа к памяти подключен к четвертому входу микроЭВМ.2„ Тахометр по п,, отличающийся тем, что регистр запросов состоит из трех триггеров, R-входы которых подключены к трем инверсным выходам контроллера прямого доступа к памяти, а прямые выходы этих триггеров соединены с тремя управляющими входами контроллера прямого доступа к памяти, счетный вход второго триггера подключен к выходу компаратора, соединенного с третьим входом схемы управления, а его инверсный выход соединен со счетным входом третьего триггера, инверсный выход которого подключен к счетному входу четвертого триггера, информационные и установочные входы второго, третьего и четвертого триггеров объединены и подклзочены к источнику уровня

J

логической ).

зпло

Фие.У

Составитель Ю. Мручко Редактор И. Рыбченко Техред А.Кравчук Корректор М.Максимишинец

Заказ 5560/43Тираж 776Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой тахометр | 1983 |

|

SU1151888A1 |

| Контроллер прямого доступа к памяти | 1991 |

|

SU1789987A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для считывания изображений | 1987 |

|

SU1481816A2 |

| Станция локальной сети | 1990 |

|

SU1824640A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для ввода информации от аналоговых датчиков | 1988 |

|

SU1578706A1 |

| Устройство для ввода информации в память микроЭВМ с общей шиной | 1982 |

|

SU1290336A1 |

Изобретение относится к средствам измерения угловых скоростей. Цель изобретения - расширение верхнего предела измерений и уменьшение динамической погрешности. Устройство содержит контактор 1, электродвигатель 2, растровый датчик 3 угловых перемещений, компаратор 4, схему 5 управления, устройство 6 квантования периода, микроЭВМ 7, схему 8 совпадения, триггер 9, счетчик 10 адреса, постоянное запоминающее устройство II, преобразователь 12 код-напряжение, делитель 13 частоты, регистр 14, вычислительное устройство 15, переключатель 16 сигнала запуска, регистр 17 запросов и контроллер 18 прямого доступа к памяти. Введение новых элементов и образование новых связей между элементами устройства позволяет производить запись информации об одном периоде информативного сигнала с вькода устройства 6 квантования периода и кода с выхода буферного регистра 14 в оперативное запоминающем устройство микроэвм 7 по каждому сигналу компаратора 4. 1 з.п. ф- лы,3 шт.

| Цифровой тахометр | 1983 |

|

SU1151888A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-11-15—Публикация

1986-01-14—Подача