(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Устройство для ввода информации | 1985 |

|

SU1305692A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для формирования характеристических матриц | 1988 |

|

SU1596334A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для вывода информации | 1986 |

|

SU1377849A1 |

| Устройство для определения максимальных путей в графах | 1984 |

|

SU1280380A2 |

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1348895A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при приеме и обработке информации от оптоэлектронных датчиков, работающих по принципу приборов с зарядовой связью, в автоматических системах управления фокусированием изображения в оптических устройствах. Целью изобретения является повышение быстродействия устройства, Устройство содержит первый, второй и третий блоки памяти, блок формирования адресов, блок синхронизации, блок обработки информации, блок контроля, блок определения координат светового пятна ПЗС-матрицы, первый и второй регистры, первый и второй триггеры, генератор тактовых импульсов, первый и второй дешифраторы, мультиплексор, первый, второй и третий элементу И. 11 ил.

Изобретение относится к автоматике и вычислительной технике и может быть использовано при приеме и обработке информации от опто-электронных датчиков, работающих по принципу приборов с зарядовой связью, в автоматических системах управления фокусирования изображения в оптических устройствах.

Целью изобретения является повышение быстродействия устройства.

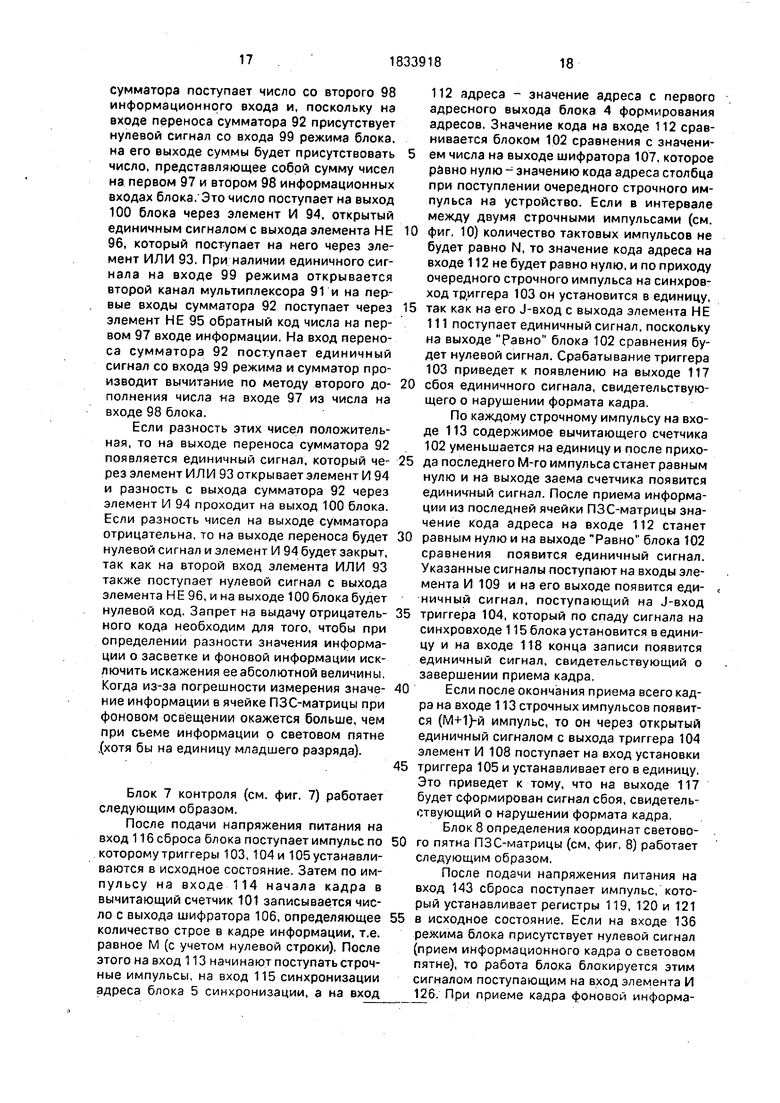

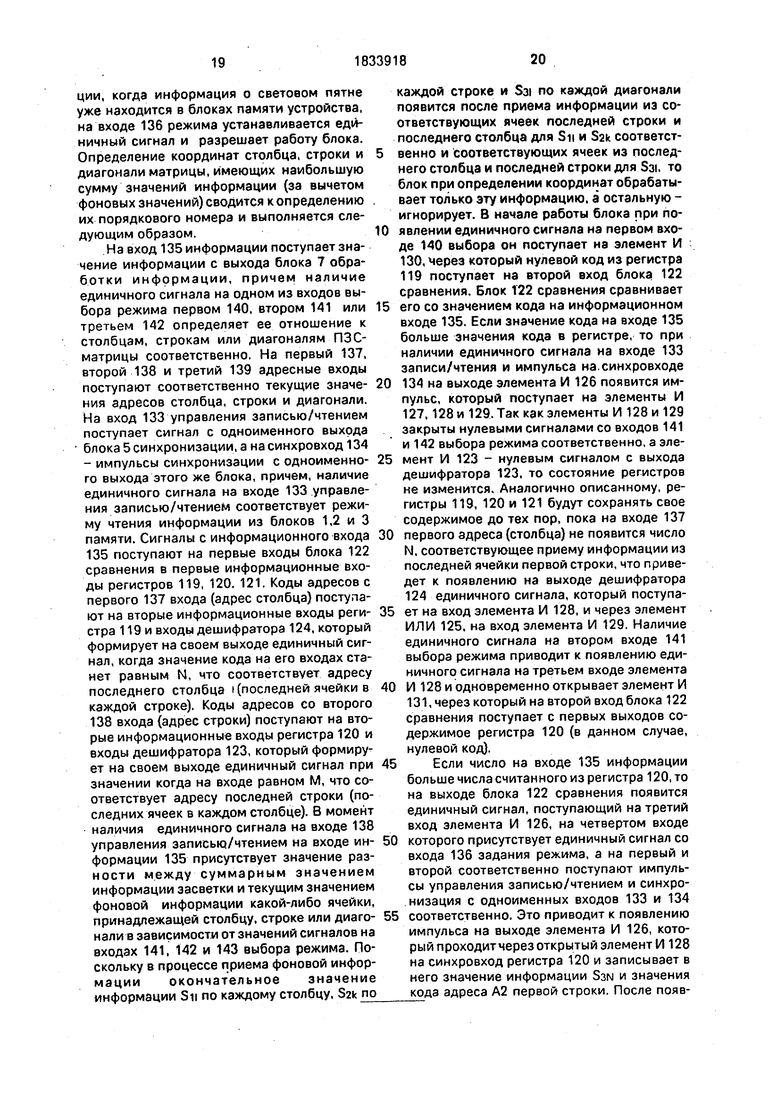

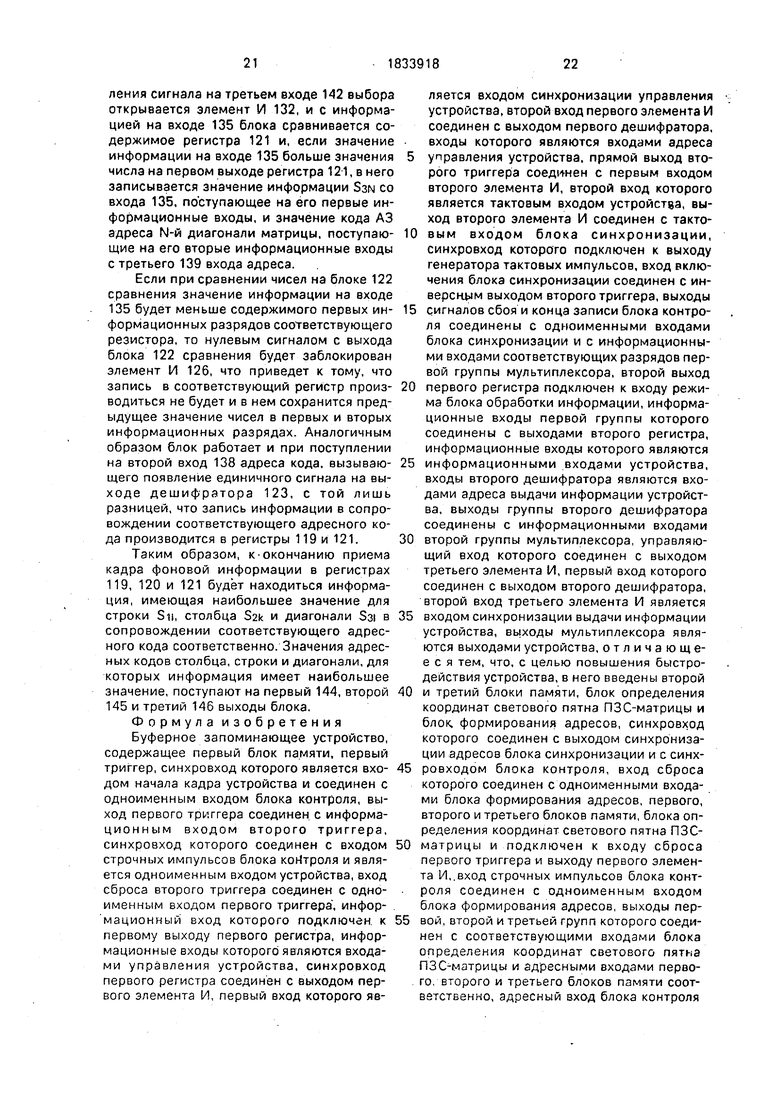

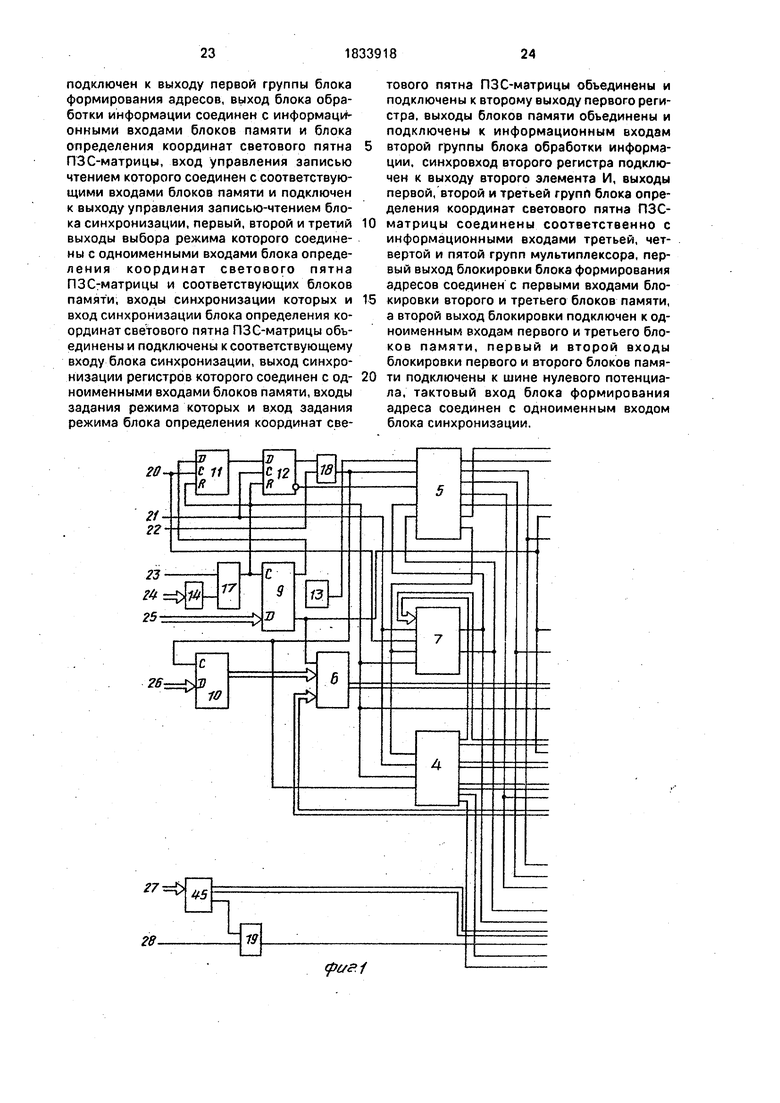

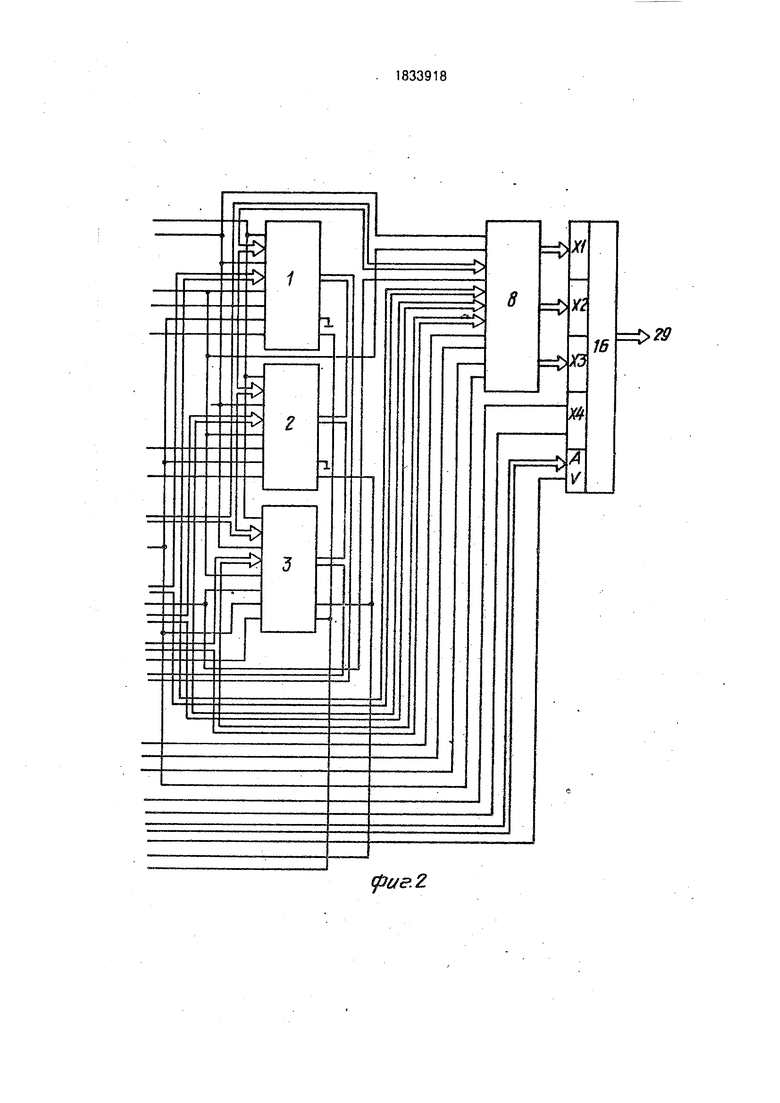

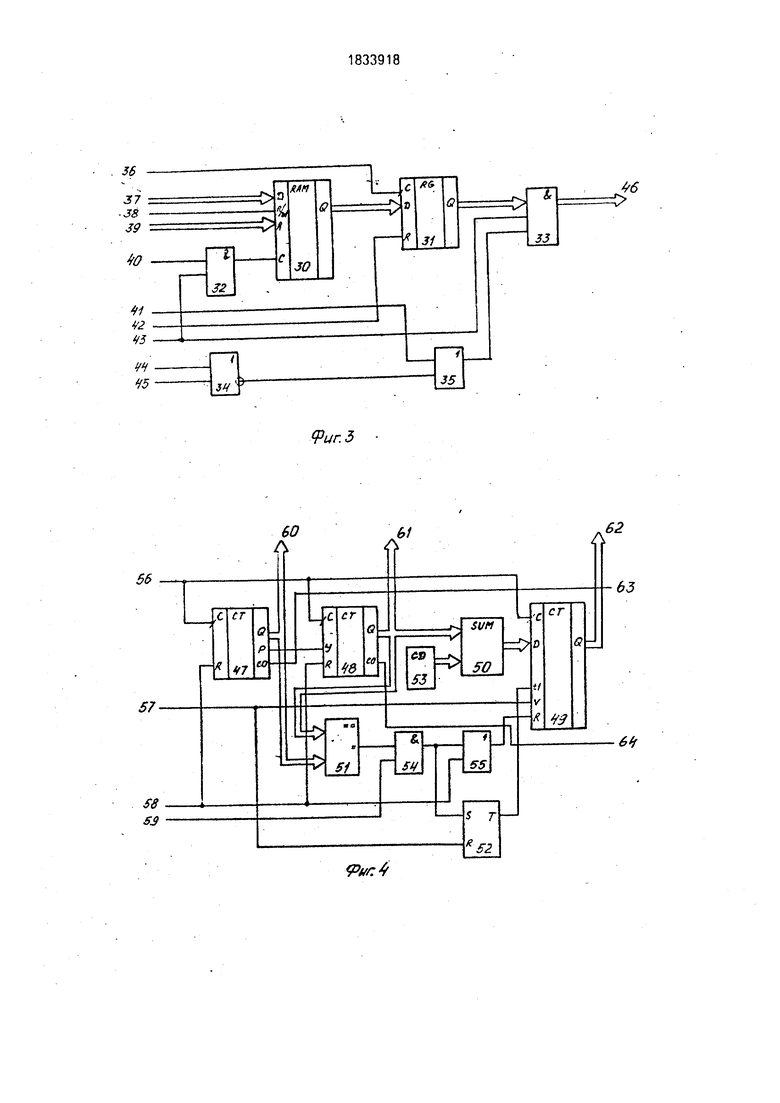

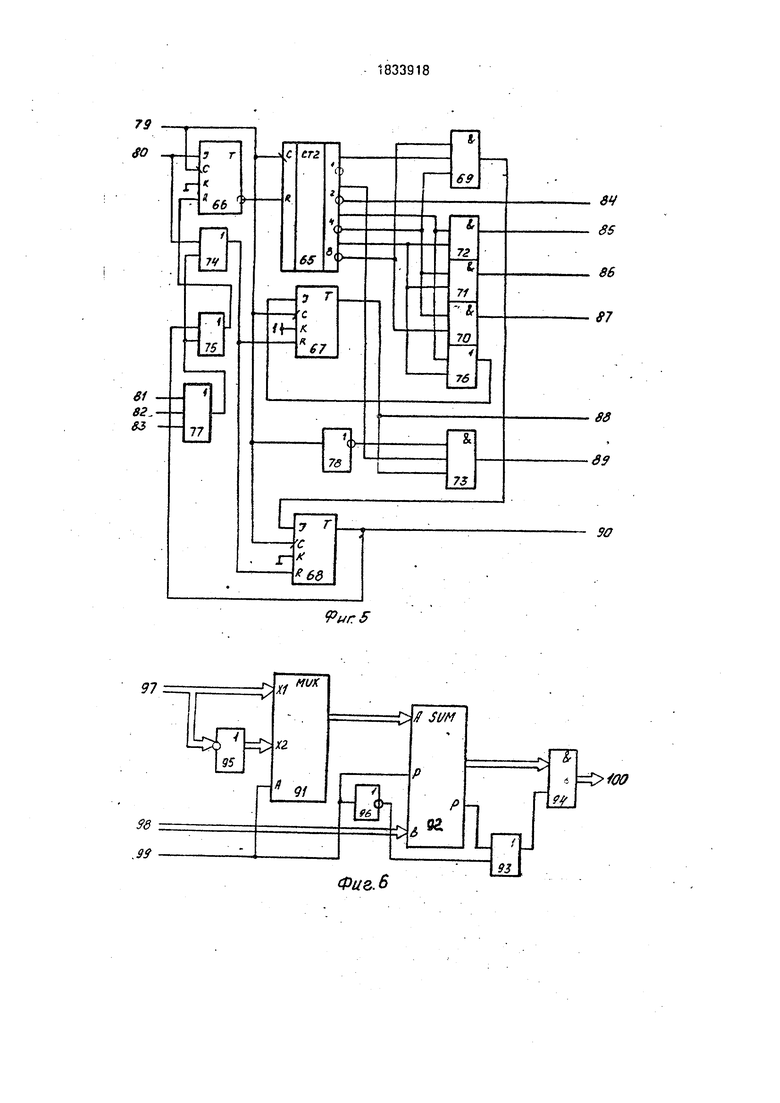

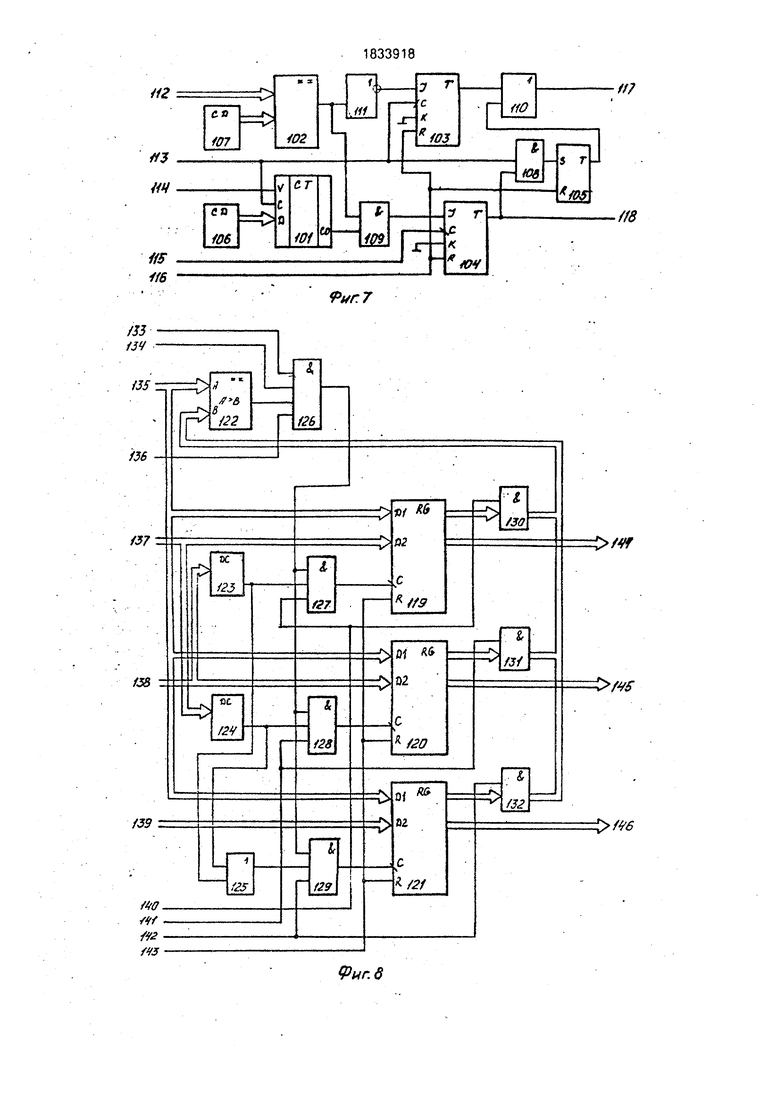

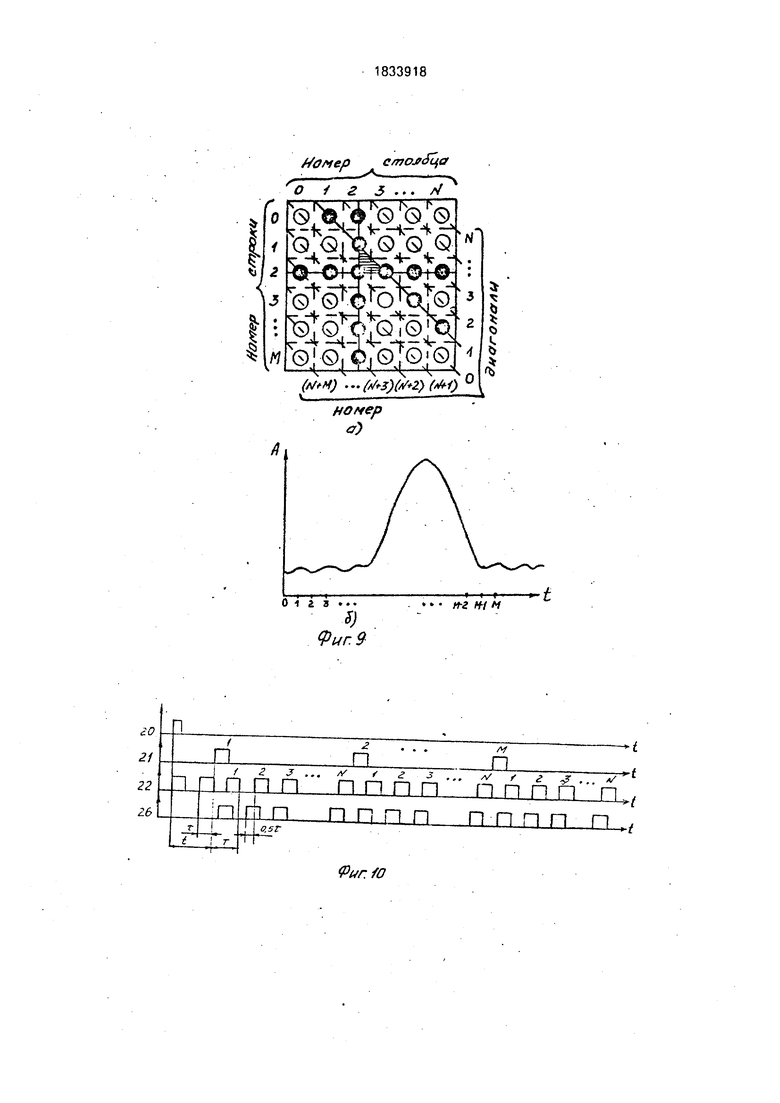

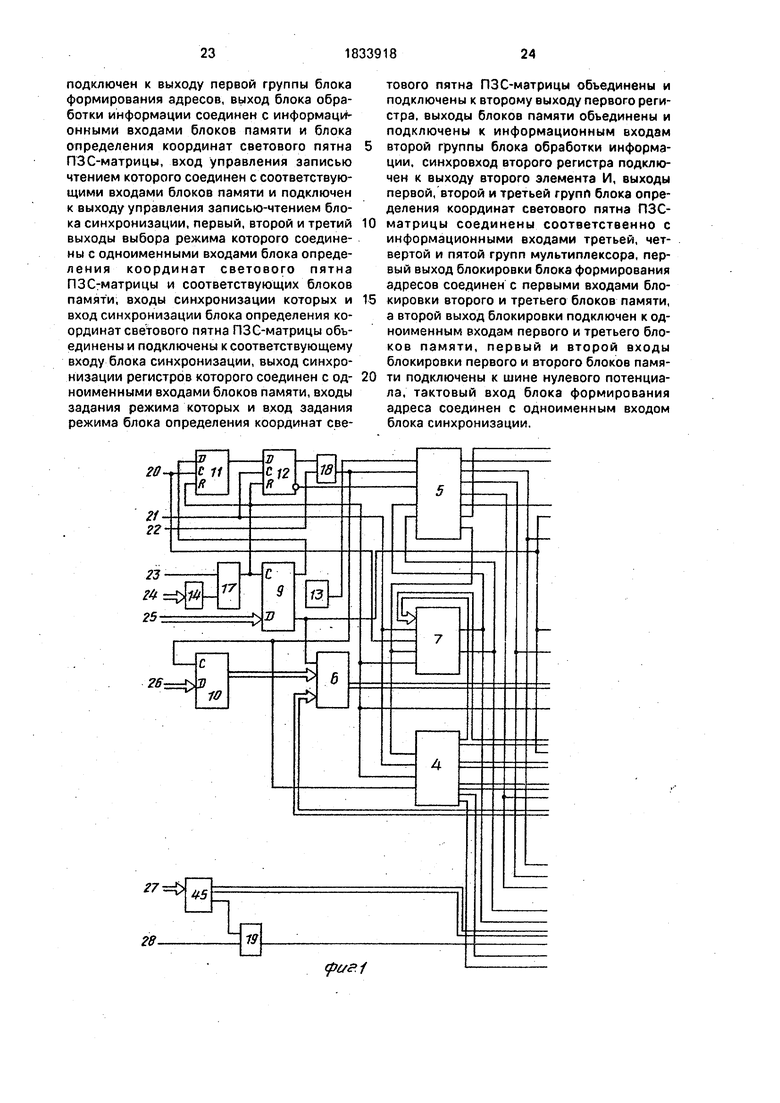

На фиг. 1,2 представлена функциональная схема предлагаемого устройства; на фиг. 3 представлена функциональная схема блока памяти; на фиг. 4 представлена функциональная схема блока формирования адресов; на фиг. 5 - функциональная схема блока синхронизации; на фиг. 6 - функциональная схема блока обработки информации; на фиг. 8 - функциональная схема

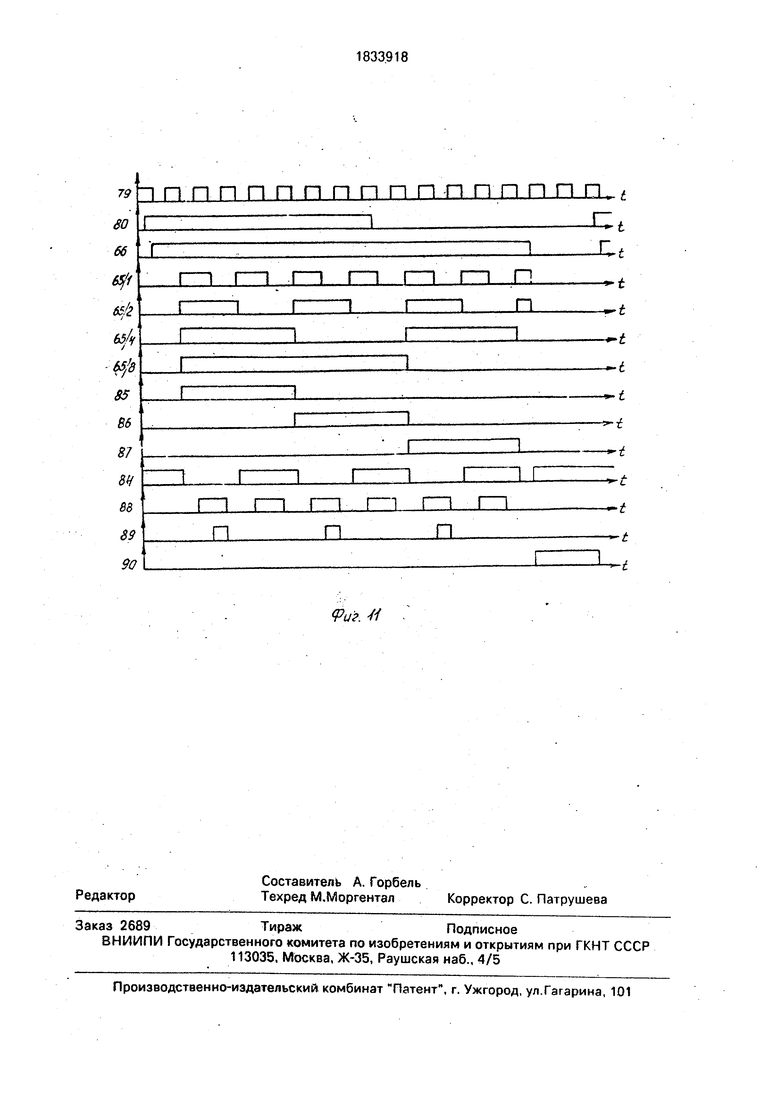

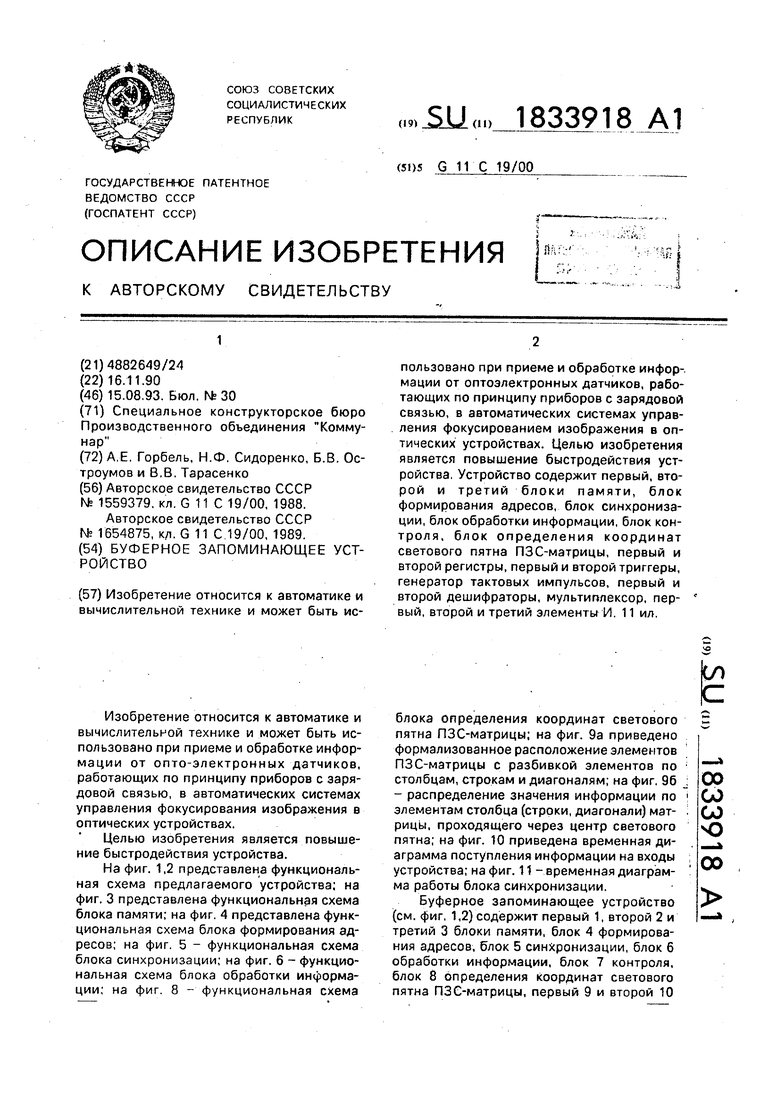

блока определения координат светового пятна ПЗС-матрицы; на фиг. 9а приведено формализованное расположение элементов ПЗС-матрицы с разбивкой элементов по столбцам, строкам и диагоналям; на фиг. 96 j - распределение значения информации по элементам столбца (строки, диагонали) мат- рицы, проходящего через центр светового пятна; на фиг. 10 приведена временная ди- . аграмма поступления информации на входы ; устройства; на фиг. 11 - временная диаграм- ма работы блока синхронизации.

Буферное запоминающее устройство (см. фиг, 1,2) содержит первый 1, второй 2 и третий 3 блоки памяти, блок 4 формирования адресов, блок 5 синхронизации, блок 6 обработки информации, блок 7 контроля, блок 8 определения координат светового пятна ПЗС-матрицы, первый 9 и второй 10

оо

(л GJ Ю

00

регистры, первый 11 и второй 12 триггеры, генератор тактовых импульсов 13, первый 14 и второй 15 дешифраторы, мультиплек сор 16 и первый 17, второй 18 и третий 19 элементы И.

На фиг. 1,2 приняты также следующие условные обозначения:

20- вход начала кадра устройства;

21- вход строчных импульсов;

22- вход тактовых импульсов;

23- вход синхронизации управления;

24- вход адреса управления;

25- вход управления;

26- вход информации;

27- выход адреса выдачи информации;

28- вход синхронизации выдачи информации;

29- выход устройства.

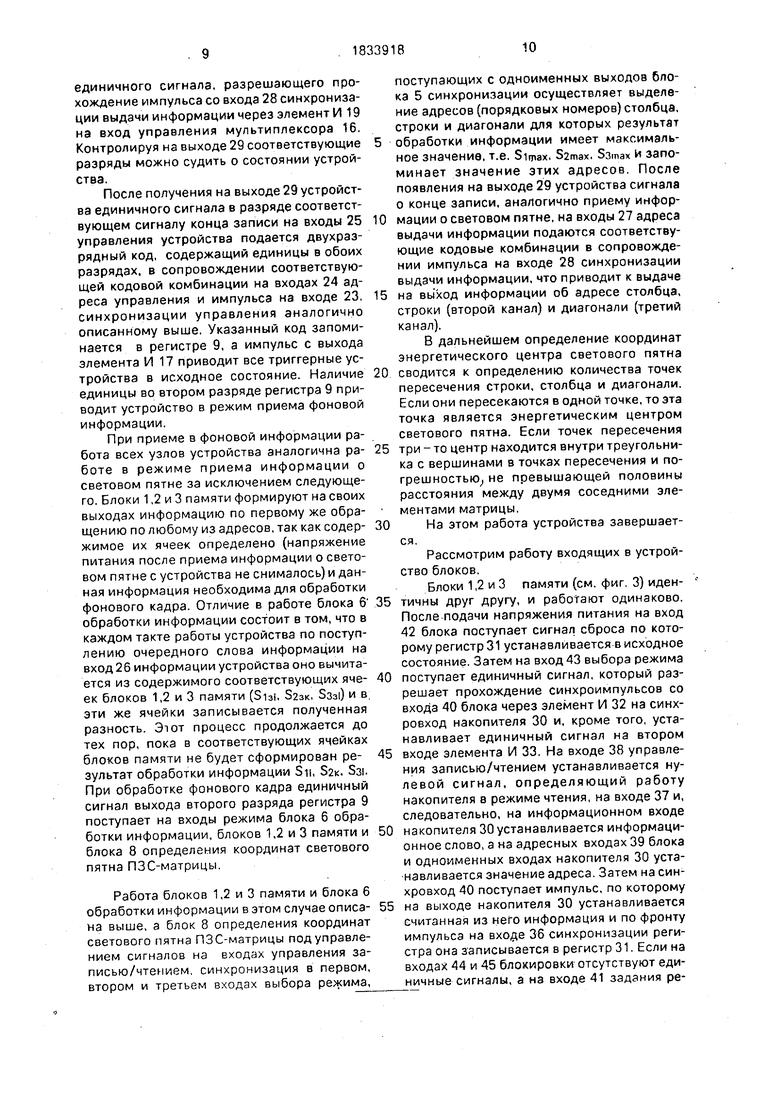

Блоки памяти 1,2 и 3 (см. фиг. 3) содержат накопитель 30, регистр 31, первый 32 и второй 33 элементы И, первый элемент ИЛИ-НЕ 34 и второй 35 элемент ИЛ И, входы 36 синхронизации регистров, 37 информации, 38 управления записью-чтением, 39 адреса, 40 синхронизации, 41 задания режима, 42 сброса, 43 выбора режима, первый 44 и второй 45 входы блокировки и выход 46.

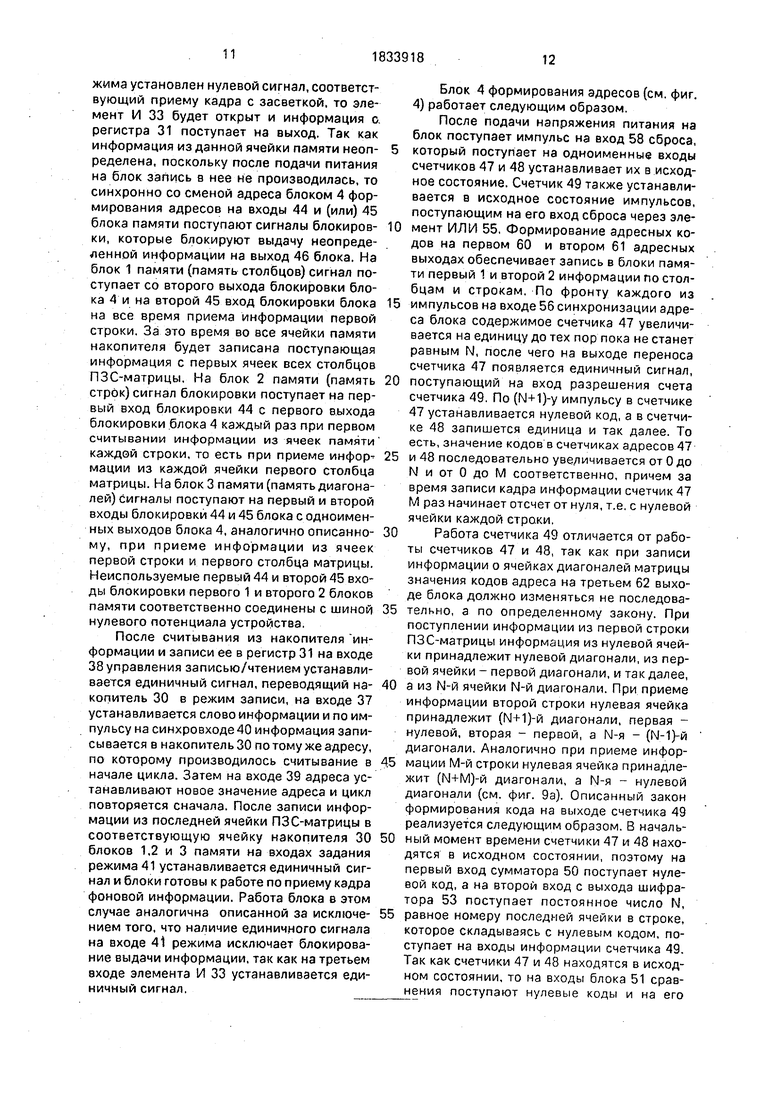

Блок 4 формирования адресов содержит первый 47 и второй 48 счетчики, третий 49 реверсивный счетчик, сумматор 50, блок 51 сравнения, триггер 52, шифратор 53, элемент И 54, элемент ИЛИ 55, вход 56 синхро- низации адреса, вход 57 строчных импульсов, вход 58 сброса, тактовый 59 вход, выходы группы первый 60, второй 61 и третий 62 адреса блока и первый 63 и второй 64 выходы блокировки блока. Синх- ровходы первого 47, второго 48 и третьего 49 счетчиков соединены между собой и яв- ляются входом 56 синхронизации адреса блоха.- .

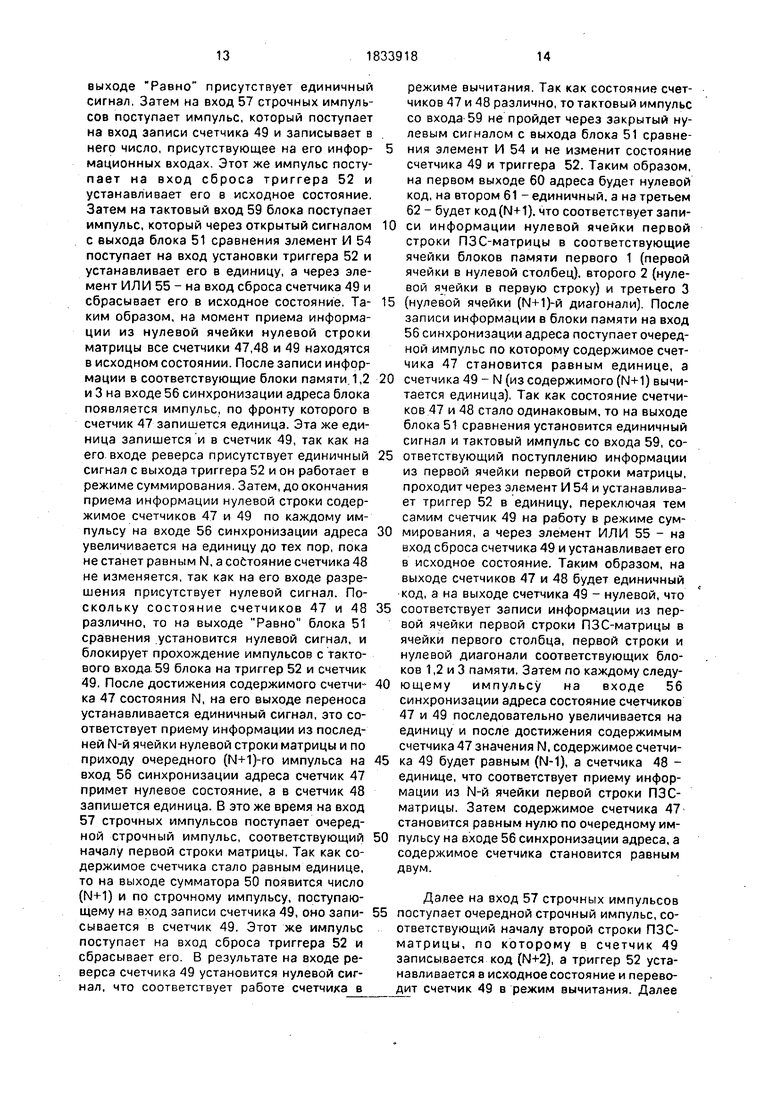

Блок 5 синхр онизации (см. фиг. 5) содержит вычитающий счетчик 65: первый 66, второй 67 и третий 68 триггеры, элементы И с первого 69 по пятый 73, элементы ИЛИ с первого 74 по четвертый 77, элемент НЕ 78, вход 79 синхронизации, вход 80 тактовУх импульсов, вход 81 включения, вход 82 конца записи и вход 83 сбоя, выход 84 управле- ния записью/чтением, первый 85, второй 86 и третий 87 выходы выбора режима, выход 88 синхронизации, выход 89 синхронизации регистров и выход 90 синхронизации адреса блока.

Блок 6 обработки информации (см, фиг, 6) содержит мультиплексор 91, сумматор 92, элемент ИЛИ 93, элемент И 94, первый 95 и второй 96 элементы НЕ, первый 97 и второй

98 входы информации, вход 99 режима и выход 100,

Блок 7 контроля (см. фиг. 7) содержит вычитающий счетчик 101, блок 102 сравнения, первый 103, второй 104 и третий 105 триггеры, первый 106 и второй 107 шифраторы, первый 108 и второй 109 элементы И, элемент ИЛИ 110, элемент НЕ 111. вход 112 адреса, вход 113 строчных импульсов, вход 114 начала кадра, вход 115 синхронизации, вход 116 сброса, выход 117 сбоя и выход 118 конца записи.

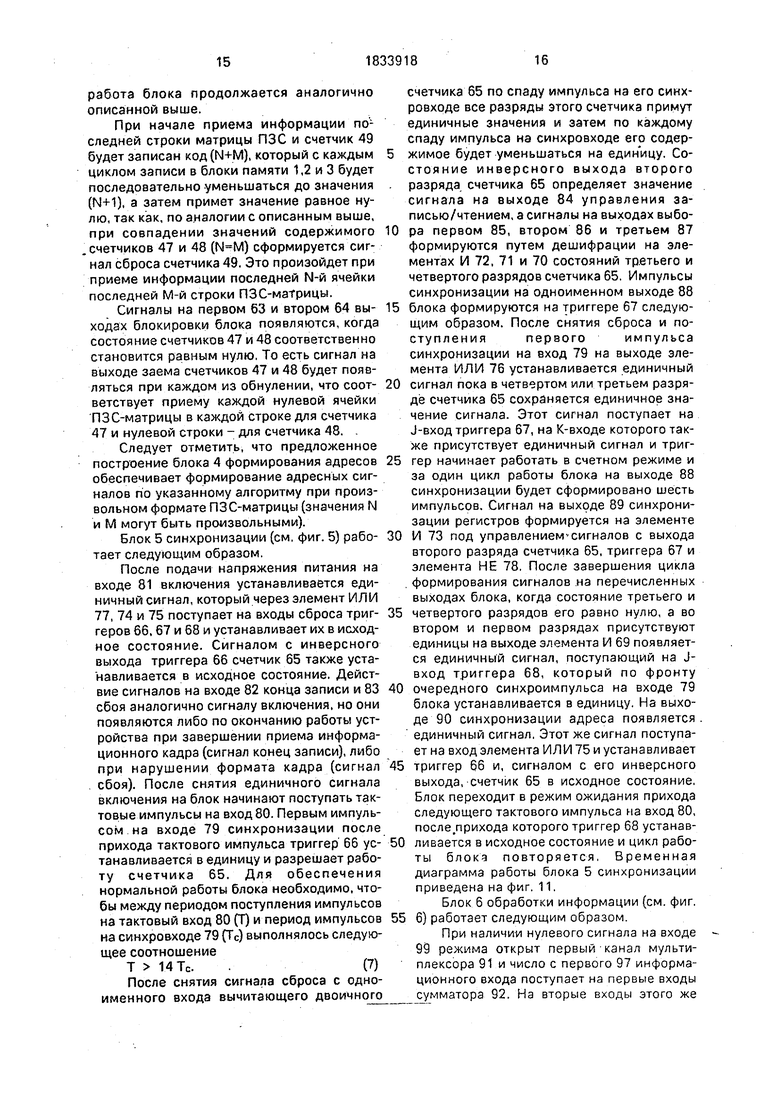

Блок 8 определения координат.светово- го пятна ПЗС-матрицы (см. фиг. 8) содержит три регистра с первого 119 по третий 121, блок 122 сравнения, первый 123 и второй 124 дешифраторы, элементы ИЛИ 125, элементы И с первого 126 по седьмой 132, входы 133 управления записью/чтением, 134 синхронизации, 135 информации, 136 задания режима, первый 137, второй 138 и третий 139 адреса, первый 140, второй 141 и третий 142 выбора режима, вход 143 сброса и первый 144, второй 145 третий 146 выходы.

Обработка информации, поступающей от ПЗС-матрицы,заключается в следующем.

На фиг, 96 приведено распределение значений информации по ячейкам столбца матрицы, проходящего через световое пятно. Аналогичную форму имеет распределение значений информации по ячейкам строки и диагонали матрицы, проходящих через световое пятно. Алгоритм обработки информации о световом пятне имеет два этапа. На первом этапе при приеме информации о засветке определяются суммы значений информации в каждой из ячеек по столбцам, строкам и диагоналям.

Siai Ј I3j(1)

I 0 N

52зк Ј (2)

I 0

DI

53з1 2 laj(3)

I 0

где S 1з1 - сумма значений информации, где о засветке по ячейкам столбца (O...N-номер столбца);

$2зк сумма значений информации о засветке по ячейкам строки (...М-номер строки);

5зз1 - сумма значений информации по ячейкам диагонали (...(N+M) - номер диагонали);

I3j - значение информации о засветке в j-й ячейке столбца строки или диагонали;

ре - качество ячеек в 1-ой диагонали.

Полученные суммы запоминаются в устройстве. На втором этапе при приеме информации о фоновом освещении выполняется последовательное вычитание из полученных сумм Siaj, 52з« и 8зэ значений фоновой информации.соответствующих ячеек столбцов, строк и диагоналей. Вычитание фоновой информации необходимо для исключения влияния дефективных ячеек ПЗС-матрицы и условий фоновой освещенности на результаты определения энергети- ческого центра светового пятна. В результате обработки информации будут определены значения выражений

Sn Si3rSi4 i(4)

S2k S23K-S2 j K(5)

8зг5зз1-5зф1,(6)

где , $2фк, 5зф1 - сумма фоновых значе- ний информации по столбцам, строкам и диагоналям.

Sii, 52к, 5з - результат обработки информации по столбцам, строкам и диагоналям.

Одновременно с определением значений Sn, S2k, Sai производится определение столбца, строки и диагонали в которых значение сумм имеют максимальную величину

Simax. S2max, Ззтах И запОМИНЭЮТСЯ НОМвр Столбца imax, СТрОКИ КтаХ И ДИЭГОНЭЛИ Imax.

Если, местоположение энергетического центра светового пятна совпадает с одной из ячеек ПЗС-матрицы, то эта ячейка может быть определена как точка пересечения столбца, строки и диагонали матрицы, имеющих максимальные значения Simax, S2max, Ssmax. Если центр светового пятна не совпадает с одной из ячеек матрицы, то он будет находиться внутри треугольника, вершины которого расположены в точках пересечения строки, столбца и диагонали матрицы,

имеющих значения Slmax, S2max, Ззтпах.

На фиг. 9а приведен пример определения энергетического центра светового пятна при его несовпадении с одной из ячеек ПЗС-матрицы. Заштрихованными кругами изображены ячейки матрицы, входящие в столбец, строку и диагональ матрицы, которые имеют наибольшее значения Simax, S2max, Samax. В этом случае центр светового пятна будет находиться внутри заштрихованного треугольника. Приняв, что центр пятна находится в центре треугольника, можно определить координаты его центра с погрешностью меньшей, чем расстояние между двумя соседними элементами матрицы.

Устройство работает следующим образом.

После подачи напряжения питания на устройство начинает работать генерат.ор 13

тактовых импульсов и на его выходе формируются импульсы для синхронизации работы устройства. Затем на входы 24 адреса 5 управления поступает соответствующий код, вызывающий появление единичного сигнала на выходе дешифратора 14. на входы управления 25 поступает код с нулевым

0 значением разрядов, а на вход 23 синхронизации управления поступает синхроимпульс по которому в разряды регистра 9 запишется нулевой код и, кроме того импульсом с выхода элемента И 17 триггеры 11

5 и 12 установятся у исходное состояние. Этим же сигналом, поступающим на входы сброса блоков 1,2 и 3 памяти, блока 4 формирования адресов,блока 7 контроля и блока 8 определения координат светового

0 пятна ПЗС - матрицы все триггерные устройства указанных блоков устанавливаются в исходное состояние и устройство оказывается готовым к работе. На вход 22 тактовых импульсов начинают поступать тактовые

5 импульсы. Затем на вход 24 адреса управления устройства поступает кодовая комбинация, вызывающая появление единичного сигнала на выходе дешифратора 14, на входы 25 управления поступает двухразрядный

0 код, значение первого разряда которого равно единице и определяет запуск устройства в работу, а второго, определяющего режим - равно нулю. Указанный код записывается в соответствующие разряды реги5 стра 9 и сигнал с выхода его первого разряда разрешает по приходу импульса на вход 20 начала кадра установиться триггеру

0 11 в единичное состояние, а с выхода второго разряда определяет режим работы устройства по приему информации о засветке либо фоновой информации. Нулевое значение сигнала на выходе второго разряда ре5 гистра 9 определяет работу устройства в режиме приема информации о световом пятне. После установки триггера 11 в единичное состояние появляется разрешение на информационном входе триггера 12, ко0 торый устанавливается в единичное состояние фронтом первого импульса на входе 21 строчных импульсов устройства и сигналом со своего инверсного выхода, поступающем на вход включения блока 8 синхронизации

5 разрешает его работу, а сигналом с прямого выхода разрешает прохождение тактовых импульсов со входа 22 устройства через элемент И 18. Импульс со входа 20 начала кадра поступает так же на одноименный вход блока 7 контроля и подготавливает его к работе. Тактовые импульсы с выхода элемента И 18 поступает на синхровход регистра 10, на информационные входы которого со входа 26 информации поступает информация из нулевой ячейки ПЗС-матрицы в параллельном коде.

Эта информация записывается в ре гистр 10 и хранится в нем до поступления информации из следующей ячейки ПЗС- матрицы. Блок 5 синхронизации по поступлению каждого тактового импульса на его одноименный вход формирует на своих выходах последовательность синхроимпульсов и сигналов управления. На выходе управления записью/чтением вначале устанавливается нулевой сигнал, по которому блоки 1,2,3 памяти переводятся в режим чтения, а сигнал с первого выхода выбора режима этого же блока включает в работу первый блок 1 памяти информации о столбцах. Блоки 1,2,3 работают таким образом, что при первом обращении по чтению по любому из адресов к этим блокам в режиме приема информации о засветке, на выход информации этих блоков будет выдаваться нулевой код, а при любом последующем обращении по этому же адресу будет выдаваться содержимое ячейки памяти сданным адресом. Это необходимо для того, чтобы исключить участие в обработке информации неопределенного кода, хранящегося в блоке памяти после подачи питания на устройство до первой записи информации по этому адресу. Управление работой блоков памяти по блокированию выдачи информации при первом обращении по чтению к очередной ячейке памяти осуществляется при помощи сигналов с первого и второго выходов блокировки блока 4 формирования адреса.

Информация, считанная из блока Гпа- мяти поступает на второй информационный вход блока 6 обработки информации, на первом входе которого присутствует информация с выхода регистра 10 и блок формирует на своих выходах суммарный результат. На выходе управления записью/чтением блока 5 синхронизации появляется единичный сигнал, определяющий запись результирующей информации с выхода блока 6 обработки информации в блок 1 памяти. Затем, аналогично описанному, последовательно на первом и втором выходах выбора режима блока 5 синхронизации появляются единичные сигналы, которые поочередно включат в работу блоки 2 и 3 памяти, в результате чего из каждого из них вначале считывается информация, затем складывается с информацией, хранящейся в регистре 10, а потом снова записывается в эту же ячейку блоков памяти. Считывание и запись информации сопровождается формированием на выходах синхронизации и синхронизации регистров блока 5 синхро

низации синхроимпульсов, поступающих на блоки 1,2,3 памяти и обеспечивающих их синхронизацию. Блок 8 определения координат светового пятна ПЗС-матрицы отключен нулевым сигналом на входе задания режима и в приеме информации о засветке не участвует. После завершения записи результата обработки первого информационного слова в блоки 1,2,3 памяти на выходе

0 синхронизации адреса блока 5 синхронизации формируется импульс, поступающий на вход синхронизации адреса блока 4, по которому на первом, втором и третье м выходах адреса устанавливается очередное

5 значение адресов для соответствующих блоков памяти. Далее по каждому очередному импульсу на входе 22 тактовых импульсов устройства повторяется цикл работы устройства, а в каждом цикле работы блок 4

0 формирования адресов под воздействием сигналов с выхода синхронизации адресов блока 5 синхронизации и импульсов со входа 21 строчных импульсов устанавливает на своих выходах соответствующие коды адре5 сов, а блок 7 контроля контролирует последовательность смены адресов на первом адресном выходе блока 4 формирования адресов в течение интервала между двумя строчками импульсами, поступающими на

0 одноименный вход блока со входа 21 устройства. Синхронизация работы блока осуществляется импульсами синхронизации адреса поступающими на синхровход блока 7 с выхода блока 5 синхронизации. Если в

5 течение приема кадра информации о световом пятне нарушения формата кадра не было зафиксировано, то по окончанию обработки последнего информационного слова на выходе конца записи блока 7 конт0 роля появится сигнал, который поступает на один из входов мультиплексора 16 и на вход конца записи блока 5 синхронизации и появление указанного сигнала вызывает прекращение работы блока и устройства в

5 целом. Если в процессе приема информационного кадра обнаружено нарушение формата кадра, то на выходе сбоя блока 7 контроля появляется сигнал поступающий на вход сбоя блока 5 синхронизации, что

0 вызывает прекращение его работы, и на вход мультиплексора 16. В процессе приема информации контроль за работой устройства осуществляется путем подачи на вход 27 адреса выдачи информации устройства со5 ответствующей кодовой комбинации, вызывающей появление на первом выходе дешифратора 15 такого кода, который, поступая на адресные входы мультиплексора 16, открывает его входы первой группы, а на втором выходе дешифратора - появление

единичного сигнала, разрешающего прохождение импульса со входа 28 синхронизации выдачи информации через элемент И 19 на вход управления мультиплексора 16. Контролируя на выходе 29 соответствующие разряды можно судить о состоянии устройства.

После получения на выходе 29 устройства единичного сигнала в разряде соответствующем сигналу конца записи на входы 25 управления устройства подается двухразрядный код, содержащий единицы в обоих разрядах, в сопровождении соответствующей кодовой комбинации на входах 24 адреса управления и импульса на входе 23, синхронизации управления аналогично описанному выше. Указанный код запоминается в регистре 9, а импульс с выхода элемента И 17 приводит все триггерные устройства в исходное состояние. Наличие единицы во втором разряде регистра 9 приводит устройство в режим приема фоновой информации.

При приеме в фоновой информации работа всех узлов устройства аналогична работе в режиме приема информации о световом пятне за исключением следующего. Блоки 1,2 и 3 памяти формируют на своих выходах информацию по первому же обращению по любому из адресов, так как содержимое их ячеек определено (напряжение питания после приема информации о световом пятне с устройства не снималось) и данная информация необходима для обработки фонового кадра. Отличие в работе блока б обработки информации состоит в том, что в каждом такте работы устройства по поступлению очередного слова информации на вход 26 информации устройства оно вычитается из содержимого соответствующих ячеек блоков 1,2 и 3 памяти (Si3i, Зазк, 5зз|) и в; эти же ячейки записывается полученная разность. Этот процесс продолжается до тех пор, пока в соответствующих ячейках блоков памяти не будет сформирован результат обработки информации Зц, $2к, S3I. При обработке фонового кадра единичный сигнал выхода второго разряда регистра 9 поступает на входы режима блока б обработки информации, блоков 1,2 и 3 памяти и блока 8 определения координат светового пятна ПЗС-матрицы.

Работа блоков 1,2 и 3 памяти и блока б обработки информации в этом случае описана выше, а блок 8 определения координат светового пятна ПЗС-матрицы под управлением сигналов на входах управления записью/чтением, синхронизация в первом, втором и третьем входах выбора режима,

поступающих с одноименных выходов блока 5 синхронизации осуществляет выделение адресов (порядковых номеров) столбца, строки и диагонали для которых результат 5 обработки информации имеет максимальное значение, т.е. Siniax, S2max, Ззтах и запоминает значение этих адресов. После появления на выходе 29 устройства сигнала о конце записи, аналогично приему инфор0 мации о световом пятне, на входы 27 адреса выдачи информации подаются соответствующие кодовые комбинации в сопровождении импульса на входе 28 синхронизации выдачи информации, что приводит к выдаче

5 на выход информации об адресе столбца, строки (второй канал) и диагонали (третий канал).

В дальнейшем определение координат энергетического центра светового пятна

0 сводится к определению количества точек пересечения строки, столбца и диагонали. Если они пересекаются в одной точке, то эта точка является энергетическим центром светового пятна. Если точек пересечения

5 три - то центр находится внутри треугольника с вершинами в точках пересечения и погрешностью, не превышающей половины расстояния между двумя соседними элементами матрицы.

0На этом работа устройства завершается.

Рассмотрим работу входящих в устройство блоков.

Блоки 1,2 и 3 памяти (см. фиг. 3) идеи-

5 тичны друг другу, и работают одинаково. После подачи напряжения питания на вход 42 блока поступает сигнал сброса по которому регистр 31 устанавливается в исходное состояние. Затем на вход 43 выбора режима

0 поступает единичный сигнал, который разрешает прохождение синхроимпульсов со входа 40 блока через элемент И 32 на синх- ровход накопителя 30 и. кроме того, устанавливает единичный сигнал на втором

5 входе элемента И 33. На входе 38 управления записью/чтением устанавливается нулевой сигнал, определяющий работу накопителя в режиме чтения, на входе 37 и, следовательно, на информационном входе

0 накопителя 30 устанавливается информационное слово, а на адресных входах 39 блока и одноименных входах накопителя 30 устанавливается значение адреса. Затем на син- хровход 40 поступает импульс, по которому

5 на выходе накопителя 30 устанавливается считанная из него информация и по фронту импульса на входе 36 синхронизации регистра она записывается в регистр 31. Если на входах 44 и 45 блокировки отсутствуют единичные сигналы, а на входе 41 задания режима установлен нулевой сигнал, соответствующий приему кадра с засветкой, то элемент И 33 будет открыт и информация о. регистра 31 поступает на выход. Так как информация из данной ячейки памяти неопределена, поскольку после подачи питания на блок запись в нее не производилась, то синхронно со сменой адреса блоком 4 формирования адресов на входы 44 и (или) 45 блока памяти поступают сигналы блокировки, которые блокируют выдачу неопределенной информации на выход 46 блока. На блок 1 памяти (память столбцов) сигнал поступает со второго выхода блокировки блока 4 и на второй 45 вход блокировки блока на все время приема информации первой строки. За это время во все ячейки памяти накопителя будет записана поступающая информация с первых ячеек всех столбцов ПЗС-матрицы. На блок 2 памяти (память строк) сигнал блокировки поступает на первый вход блокировки 44 с первого выхода блокировки блока 4 каждый раз при первом считывании информации из ячеек памяти каждой строки, то есть при приеме инфор- мации из каждой ячейки первого столбца матрицы. На блок 3 памяти (память диагоналей) Сигналы поступают на первый и второй входы блокировки 44 и 45 блока с одноименных выходов блока 4, аналогично описанному, при приеме информации из ячеек первой строки и первого столбца матрицы. Неиспользуемые первый 44 и второй 45 входы блокировки первого 1 и второго 2 блоков памяти соответственно соединены с шиной нулевого потенциала устройства.

После считывания из накопителя информации и записи ее в регистр 31 на входе 38 управления записью/чтением устанавливается единичный сигнал, переводящий накопитель 30 в режим записи, на входе 37 устанавливается слово информации и по импульсу на синхровходе 40 информация записывается в накопитель 30 по тому же адресу, по которому производилось считывание в начале цикла. Затем на входе 39 адреса устанавливают новое значение адреса и цикл повторяется сначала. После записи информации из последней ячейки ПЗС-матрицы в соответствующую ячейку накопителя 30 блоков 1,2 и 3 памяти на входах задания режима 41 устанавливается единичный сигнал и блоки готовы к работе по приему кадра фоновой информации. Работа блока в этом случае аналогична описанной за исключением того, что наличие единичного сигнала на входе 41 режима исключает блокирование выдачи информации, так как на третьем входе элемента И 33 устанавливается единичный сигнал.

Блок 4 формирования адресов (см. фиг. 4) работает следующим образом.

После подачи напряжения питания на блок поступает импульс на вход 58 сброса,

который поступает на одноименные входы счетчиков 47 и 48 устанавливает их в исходное состояние. Счетчик 49 также устанавливается в исходное состояние импульсов, поступающим на его вход сброса через эле0 мент ИЛИ 55, Формирование адресных кодов на первом 60 и втором 61 адресных выходах обеспечивает запись в блоки памяти первый 1 и второй 2 информации по столбцам и строкам. По фронту каждого из

5 импульсов на входе 56 синхронизации адреса блока содержимое счетчика 47 увеличивается на единицу до тех пор пока не станет равным N, после чего на выходе переноса счетчика 47 появляется единичный сигнал,

0 поступающий на вход разрешения счета счетчика 49. По (N+1)-y импульсу в счетчике 47 устанавливается нулевой код, а в счетчике 48 запишется единица и так далее. То есть, значение кодов в счетчиках адресов 47

5 и 48 последовательно увеличивается от 0 до N и от 0 до М соответственно, причем за время записи кадра информации счетчик 47 М раз начинает отсчет от нуля, т.е. с нулевой ячейки каждой строки.

0 Работа счетчика 49 отличается от работы счетчиков 47 и 48, так как при записи информации о ячейках диагоналей матрицы значения кодов адреса на третьем 62 выходе блока должно изменяться не последова5 тельно, а по определенному закону. При поступлении информации из первой строки ПЗС-матрицы информация из нулевой ячейки принадлежит нулевой диагонали, из первой ячейки - первой диагонали, и так далее,

0 а из N-й ячейки N-й диагонали. При приеме информации второй строки нулевая ячейка принадлежит (N+IJ-й диагонали, первая - нулевой, вторая - первой, а N-я - (М-1)-й диагонали. Аналогично при приеме инфор5 мации М-й строки нулевая ячейка принадлежит (Ы+М)-й диагонали, а N-я - нулевой диагонали (см. фиг. 9а). Описанный закон формирования кода на выходе счетчика 49 реализуется следующим образом. В началь0 ный момент времени счетчики 47 и 48 находятся в исходном состоянии, поэтому на первый вход сумматора 50 поступает нулевой код, а на второй вход с выхода шифратора 53 поступает постоянное число N,

5 равное номеру последней ячейки в строке, которое складываясь с нулевым кодом, поступает на входы информации счетчика 49. Так как счетчики 47 и 48 находятся в исходном состоянии, то на входы блока 51 сравнения поступают нулевые коды и на его

выходе Равно присутствует единичный сигнал. Затем на вход 57 строчных импульсов поступает импульс, который поступает на вход записи счетчика 49 и записывает в него число, присутствующее на его информационных входах. Этот же импульс поступает на вход сброса триггера 52 и устанавливает его в исходное состояние. Затем на тактовый вход 59 блока поступает импульс, который через открытый сигналом с выхода блока 51 сравнения элемент И 54 поступает на вход установки триггера 52 и устанавливает его в единицу, а через элемент ИЛИ 55 - на вход сброса счетчика 49 и сбрасывает его в исходное состояние. Таким образом, на момент приема информации из нулевой ячейки нулевой строки матрицы все счетчики 47,48 и 49 находятся в исходном состоянии. После записи информации в соответствующие блоки памяти, 1,2 и 3 на входе 56 синхронизации адреса блока появляется импульс, по фронту которого в счетчик 47 запишется единица. Эта же единица запишется и в счетчик 49, так как на его входе реверса присутствует единичный сигнал с выхода триггера 52 и он работает в режиме суммирования. Затем, до окончания приема информации нулевой строки содержимое счетчиков 47 и 49 по каждому импульсу на входе 56 синхронизации адреса увеличивается на единицу до тех пор, пока не станет равным N, а состояние счетчика 48 не изменяется, так как на его входе разрешения присутствует нулевой сигнал. Поскольку состояние счетчиков 47 и 48 различно, то на выходе Равно блока 51 сравнения установится нулевой сигнал, и блокирует прохождение импульсов с тактового входа. 59 блока на триггер 52 и счетчик 49. После достижения содержимого счетчика 47 состояния N, на его выходе переноса устанавливается единичный сигнал, это соответствует приему информации из последней N-й ячейки нулевой строки матрицы и по приходу очередного (N+1)-ro импульса на вход 56 синхронизации адреса счетчик 47 примет нулевое состояние, а в счетчик 48 запишется единица. В это же время на вход 57 строчных импульсов поступает очередной строчный импульс, соответствующий началу первой строки матрицы. Так как содержимое счетчика стало равным единице, то на выходе сумматора 50 появится число (N+1) и по строчному импульсу, поступающему на вход записи счетчика 49, оно записывается в счетчик 49. Этот же импульс поступает на вход сброса триггера 52 и сбрасывает его. В результате на входе реверса счетчика 49 установится нулевой сигнал, что соответствует работе счетчика в

режиме вычитания. Так как состояние счетчиков 47 и 48 различно, то тактовый импульс со входа 59 не пройдет через закрытый нулевым сигналом с выхода блока 51 сравне- 5 ния элемент И 54 и не изменит состояние счетчика 49 и триггера 52. Таким образом, на первом выходе 60 адреса будет нулевой код, на втором 61 - единичный, а на третьем 62 - будет код (N+1). что соответствует запи- 0 си информации нулевой ячейки первой строки ПЗС-матрицы в соответствующие ячейки блоков памяти первого 1 (первой ячейки в нулевой столбец), второго 2 (нулевой ячейки в первую строку) и третьего 3 5 (нулевой ячейки (N+IJ-й диагонали). После записи информации в блоки памяти на вход 56 синхронизации адреса поступает очередной импульс по которому содержимое счетчика 47 становится равным единице, а

0 счетчика 49 - N (из содержимого (N+1) вычитается единица), Так как состояние счетчиков 47 и 48 стало одинаковым, то на выходе блока 51 сравнения установится единичный сигнал и тактовый импульс со входа 59, со5 ответствующий поступлению информации из первой ячейки первой строки матрицы, проходит через элемент И 54 и устанавливает триггер 52 в единицу, переключая тем самим счетчик 49 на работу в режиме сум0 мирования, а через элемент ИЛИ 55 - на вход сброса счетчика 49 и устанавливает его в исходное состояние. Таким образом, на выходе счетчиков 47 и 48 будет единичный код, а на выходе счетчика 49 - нулевой, что

5 соответствует записи информации из первой ячейки первой строки ПЗС-матрицы в ячейки первого столбца, первой строки и нулевой диагонали соответствующих блоков 1,2 и 3 памяти. Затем по каждому следу0 ющему импульсу на входе 56 синхронизации адреса состояние счетчиков 47 и 49 последовательно увеличивается на единицу и после достижения содержимым счетчика 47 значения N, содержимое счетчи5 ка 49 будет равным (N-1), а счетчика 48 - единице, что соответствует приему информации из N-й ячейки первой строки ПЗС- матрицы. Затем содержимое счетчика 47 становится равным нулю по очередному им0 пульсу на входе 56 синхронизации адреса, а содержимое счетчика становится равным двум.

Далее на вход 57 строчных импульсов 5 поступает очередной строчный импульс, соответствующий началу второй строки ПЗС- матрицы, по которому в счетчик 49 записывается код (N+2), а триггер 52 устанавливается в исходное состояние и переводит счетчик 49 в режим вычитания. Далее

работа блока продолжается аналогично описанной выше.

При начале приема информации последней строки матрицы ПЗС и счетчик 49 будет записан код(М+М), который с каждым циклом записи в блоки памяти 1,2 и 3 будет последовательно уменьшаться до значения (N+1), а затем примет значение равное нулю, так как, по аналогии с описанным выше, при совпадении значений содержимого .счетчиков 47 и 48 () сформируется сигнал сброса счетчика 49, Это произойдет при приеме информации последней N-й ячейки последней М-й строки ПЗС-матрицы.

Сигналы на первом 63 и втором 64 вы- ходах блокировки блока появляются, когда состояние счетчиков 47 и 48 соответственно становится равным нулю, То есть сигнал на выходе заема счетчиков 47 и 48 будет появляться при каждом из обнулении, что соот- ветствует приему каждой нулевой ячейки ПЗС-матрицы в каждой строке для счетчика 47 и нулевой строки - для счетчика 48. .

Следует отметить, что предложенное построение блока 4 формирования адресов обеспечивает формирование адресных сигналов по указанному алгоритму при произвольном формате ПЗС-матрицы (значения N и М могут быть произвольными).

Блок 5 синхронизации (см, фиг. 5) рабо- тает следующим образом.

После подачи напряжения питания на входе 81 включения устанавливается единичный сигнал, который через элемент ИЛИ 77, 74 и 75 поступает на входы сброса триг- геров 66,67 и 68 и устанавливает их в исходное состояние. Сигналом с инверсного выхода триггера 66 счетчик 65 также устанавливается в исходное состояние. Действие сигналов на входе 82 конца записи и 83 сбоя аналогично сигналу включения, но они появляются либо по окончанию работы устройства при завершении приема информационного кадра (сигнал конец записи), либо при нарушении формата кадра (сигнал сбоя). После снятия единичного сигнала включения на блок начинают поступать тактовые импульсы на вход 80. Первым импульсом на входе 79 синхронизации после прихода тактового импульса триггер 66 ус- танавливается в единицу и разрешает работу счетчика 65. Для обеспечения нормальной работы блока необходимо, чтобы между периодом поступления импульсов на тактовый вход 80 (Т) и период импульсов на синхровходе 79 (Тс) выполнялось следующее соотношение

Т 1.4 Тс. .(7)

После снятия сигнала сброса с одноименного входа вычитающего двоичного

счетчика 65 по спаду импульса на его синхровходе все разряды этого счетчика примут единичные значения и затем по каждому спаду импульса на синхровходе его содержимое будет уменьшаться на един ицу. Состояние инверсного выхода второго разряда счетчика 65 определяет значение сигнала на выходе 84 управления записью/чтением, а сигналы на выходах выбора первом 85, втором 86 и третьем 87 формируются путем дешифрации на элементах И 72, 71 и 70 состояний третьего и четвертого разрядов счетчика 65. Импульсы синхронизации на одноименном выходе 88 блока формируются на триггере 67 следующим образом. После снятия сброса и поступленияпервогоимпульсасинхронизации на вход 79 на выходе элемента ИЛИ 76 устанавливается единичный сигнал пока в четвертом или третьем разряде счетчика 65 сохраняется единичное значение сигнала. Этот сигнал поступает на J-вход триггера 67, на К-входе которого также присутствует единичный сигнал и триггер начинает работать в счетном режиме и за один цикл работы блока на выходе 88 синхронизации будет сформировано шесть импульсов. Сигнал на выходе 89 синхронизации регистров формируется на элементе И 73 под управлением сигналов с выхода второго разряда счетчика 65, триггера 67 и элемента НЕ 78. После завершения цикла формирования сигналов .на перечисленных выходах блока, когда состояние третьего и четвертого разрядов его равно нулю, а во втором и первом разрядах присутствуют единицы на выходе элемента И 69 появляется единичный сигнал, поступающий на J- вход триггера 68, который по фронту очередного синхроимпульса на входе 79 блока устанавливается в единицу. На выходе 90 синхронизации адреса появляется единичный сигнал. Этот же сигнал поступает на вход элемента ИЛИ 75 и устанавливает триггер 66 и, сигналом с его инверсного выхода, счетчик 65 в исходное состояние. Блок переходит в режим ожидания прихода следующего тактового импульса на вход 80, после .прихода которого триггер 68 устанавливается в исходное состояние и цикл работы блока повторяется, Временная диаграмма работы блока 5 синхронизации приведена на фиг. 11.

Блок 6 обработки информации (см. фиг. 6) работает следующим образом.

При наличии нулевого сигнала на входе 99 режима открыт первый-канал мультиплексора 91 и число с первого 97 информационного входа поступает на первые входы сумматора 92. На вторые входы этого же

сумматора поступает число со второго 98 информационного входа и, поскольку на входе переноса сумматора 92 присутствует нулевой сигнал со входа 99 режима блока, на его выходе суммы будет присутствовать число, представляющее собой сумму чисел на первом 97 и втором 98 информационных входах блока. Это число поступает на выход 100 блока через элемент И 94, открытый единичным сигналом с выхода элемента НЕ 96, который поступает на него через элемент ИЛИ 93. При наличии единичного сигнала на входе 99 режима открывается второй канал мультиплексора 91 и на первые входы сумматора 92 поступает через элемент НЕ 95 обратный код числа на первом 97 входе информации. На вход переноса сумматора 92 поступает единичный сигнал со входа 99 режима и сумматор производит вычитание по методу второго дополнения числа на входе 97 из числа на входе 98 блока.

Если разность этих чисел положительная, то на выходе переноса сумматора 92 появляется единичный сигнал, который через элемент ИЛИ 93 открывает элемент И 94 и разность с выхода сумматора 92 через элемент И 94 проходит на выход 100 блока. Если разность чисел на выходе сумматора отрицательна, то на выходе переноса будет нулевой сигнал и элемент И 94 будет закрыт, так как на второй вход элемента ИЛИ 93 также поступает нулевой сигнал с выхода элемента НЕ 96, и на выходе 100 блока будет нулевой код. Запрет на выдачу отрицательного кода необходим для того, чтобы при определении разности значения информации о засветке и фоновой информации исключить искажения ее абсолютной величины. Когда из-за погрешности измерения значение информации в ячейке ПЗС-матрицы при фоновом освещении окажется больше, чем при съеме информации о световом пятне .(хотя бы на единицу младшего разряда).

Блок 7 контроля (см. фиг. 7) работает следующим образом.

После подачи напряжения питания на вход 116 сброса блока поступает импульс по которому триггеры 103,104 и 105 устанавливаются в исходное состояние. Затем по им- пульсу на входе 114 начала кадра в вычитающий счетчик 101 записывается число с выхода шифратора 106, определяющее количество строе в кадре информации, т.е. равное М (с учетом нулевой строки). После этого на вход 113 начинают поступать строчные импульсы, на вход 115 синхронизации адреса блока 5 синхронизации, а на вход

112 адреса - значение адреса с первого адресного выхода блока 4 формирования адресов. Значение кода на входе 112 сравнивается блоком 102 сравнения с значени- 5 ем числа на выходе шифратора 107, которое равно нулю - значению кода адреса столбца при поступлении очередного строчного импульса на устройство. Если в интервале между двумя строчными импульсами (см.

0 фиг, 10) количество тактовых импульсов не будет равно N, то значение кода адреса на входе 112 не будет равно нулю, и по приходу очередного строчного импульса на синхров- ход триггера 103 он установится в единицу,

5 так как на его J-вход с выхода элемента НЕ 111 поступает единичный сигнал, поскольку на выходе Равно блока 102 сравнения будет нулевой сигнал. Срабатывание триггера 103 приведет к появлению на выходе 117

0 сбоя единичного сигнала, свидетельствующего о нарушении формата кадра.

По каждому строчному импульсу на входе 113 содержимое вычитающего счетчика 102 уменьшается на единицу и после прихо5 да последнего М-ro импульса станет равным нулю и на выходе заема счетчика появится единичный сигнал. После приема информации из последней ячейки ПЗС-матрицы значение кода адреса на входе 112 станет

0 равным нулю и на выходе Равно блока 102 сравнения появится единичный сигнал. Указанные сигналы поступают на входы элемента И 109 и на его выходе появится еди- с ничный сигнал, поступающий на J-вход

5 триггера 104, который по спаду сигнала на синхровходе 115 блока установится в единицу и на входе 118 конца записи появится единичный сигнал, свидетельствующий о завершении приема кадра.

0 Если после окончания приема всего кадра на входе 113 строчных импульсов появится (М+1)-й импульс, то он через открытый единичный сигналом с выхода триггера 104 элемент И 108 поступает на вход установки

5 триггера 105 и устанавливает его в единицу. Это приведет к тому, что на выходе 117 будет сформирован сигнал сбоя, свидетельствующий о нарушении формата кадра.

Блок 8 определения координат светово- .

0 го пятна ПЗС-матрицы (см, фиг, 8) работает следующим образом.

После подачи напряжения питания на вход 143 сброса поступает импульс, который устанавливает регистры 119, 120 и 121

5 в исходное состояние. Если на входе 136 режима блока присутствует нулевой сигнал (прием информационного кадра о световом пятне), то работа блока блокируется этим сигналом поступающим на вход элемента И 126. При приеме кадра фоновой информации, когда информация о световом пятне же находится в блоках памяти устройства, на входе 136 режима устанавливается единичный сигнал и разрешает работу блока. Определение координат столбца, строки и 5 иагонали матрицы, имеющих наибольшую сумму значений информации (за вычетом фоновых значений) сводится к определению . их порядкового номера и выполняется следующим образом.10

Навход 135 информации поступает значение информации с выхода блока 7 обработки информации, причем наличие единичного сигнала на одном из входов выбора режима первом 140, втором 141 или 15 третьем 142 определяет ее отношение к столбцам, строкам или диагоналям ПЗС- матрицы соответственно. На первый 137, второй 138 и третий 139 адресные входы поступают соответственно текущие значе- 20 ния адресов столбца, строки и диагонали. На вход 133 управления записью/чтением поступает сигнал с одноименного выхода блока 5 синхронизации, а насинхровход 134 - импульсы синхронизации с одноименно- 25 го выхода этого же блока, причем, наличие единичного сигнала на входе 133 управления записью/чтением соответствует режиму чтения информации из блоков 1,2 и 3 памяти. Сигналы с информационного входа 30 135 поступают на первые входы блока 122 сравнения в первые информационные входы регистров 119, 120. 121. Коды адресов с первого 137 входа (адрес столбца} поступают на вторые информационные входы реги- 35 стра 119 и входы дешифратора 124, который формирует на своем выходе единичный сигнал, когда значение кода на его входах станет равным N, что соответствует адресу последнего столбца ((последней ячейки в 40 каждой строке). Коды адресов со второго 138 входа (адрес строки) поступают на вторые информационные входы регистра 120 и входы дешифратора 123, который формирует на своем выходе единичный сигнал при 45 значении когда на входе равном М, что соответствует адресу последней строки (последних ячеек в каждом столбце). В момент наличия единичного сигнала на входе 138 управления записью/чтением на входе ин- 50 формации 135 присутствует значение разности между суммарным значением информации засветки и текущим значением фоновой информации какой-либо ячейки, принадлежащей столбцу, строке или диаго- 55 нали в зависимости от значений сигналов на входах 141, 142 и 143 выбора режима. Поскольку в процессе приема фоновой информации окончательное значение информации Sii по каждому столбцу, $2k по

каждой строке и Sai по каждой диагонали появится после приема информации из соответствующих ячеек последней строки и последнего столбца для Sn и Sak соответственно и соответствующих ячеек из последнего столбца и последней строки для Sa, то блок при определении координат обрабатывает только эту информацию, а остальную - игнорирует. В начале работы блока при появлении единичного сигнала на первом входе 140 выбора он поступает на элемент И

130,через который нулевой код из регистра 119 поступает на второй вход блока 122 сравнения. Блок 122 сравнения сравнивает его со значением кода на информационном входе 135. Если значение кода на входе 135 больше значения кода в регистре, то при наличии единичного сигнала на входе 133 записи/чтения и импульса на.синхровходе 134 на выходе элемента И 126 появится импульс, который поступает на элементы И 127.128 и 129. Так как элементы И 128 и 129 закрыты нулевыми сигналами со входов 141 и 142 выбора режима соответственно, а элемент И 123 - нулевым сигналом с выхода дешифратора 123, то состояние регистров не изменится. Аналогично описанному, регистры 119, 120 и 121 будут сохранять свое содержимое до тех пор, пока на входе 137 первого адреса (столбца) не появится число N, соответствующее приему информации из последней ячейки первой строки, что приведет к появлению на выходе дешифратора 124 единичного сигнала, который поступает на вход элемента И 128, и через элемент ИЛИ 125, на вход элемента И 129. Наличие единичного сигнала на втором входе 141 выбора режима приводит к появлению единичного сигнала на третьем входе элемента И 128 и одновременно открывает элемент И

131,через который на второй вход блока 122 сравнения поступает с первых выходов содержимое регистра 120 (в данном случае, нулевой код).

Если число на входе 135 информации больше числа считанного из регистра 120, то на выходе блока 122 сравнения появится единичный сигнал, поступающий на третий вход элемента И 126, на четвертом входе которого присутствует единичный сигнал со входа 136 задания режима, а на первый и второй соответственно поступают импульсы управления записью/чтением и синхронизация с одноименных входов 133 и 134 соответственно. Это приводит к появлению импульса на выходе элемента И 126, который проходитчерез открытый элемент И 128 на синхровход регистра 120 и записывает в него значение информации SSN и значения кода адреса А2 первой строки. После появлемия сигнала на третьем входе 142 выбора открывается элемент И 132, и с информацией на входе 135 блока сравнивается содержимое регистра 121 и, если значение информации на входе 135 больше значения числа на первом выходе регистра 121, в него записывается значение информации SSN со входа 135, поступающее на его первые информационные входы, и значение кода A3 адреса N-й диагонали матрицы, поступаю- щие на его вторые информационные входы с третьего 139 входа адреса.

Если при сравнении чисел на блоке 122 сравнения значение информации на входе 135 будет меньше содержимого первых ин- формационных разрядов соответствующего резистора, то нулевым сигналом с выхода блока 122 сравнения будет заблокирован элемент И 126, что приведет к тому, что запись в соответствующий регистр произ- водиться не будет и в нем сохранится предыдущее значение чисел в первых и вторых информационных разрядах. Аналогичным образом блок работает и при поступлении на второй вход 138 адреса кода, вызываю- щего появление единичного сигнала на выходе дешифратора 123, с той лишь разницей, что запись информации в сопровождении соответствующего адресного кода производится в регистры 119 и 121.

Таким образом, к-окончанию приема кадра фоновой информации в регистрах 119, 120 и 121 будет находиться информация, имеющая наибольшее значение для строки Sit, столбца S2k и диагонали 5з в сопровождении соответствующего адресного кода соответственно. Значения адресных кодов столбца, строки и диагонали, для которых информация имеет наибольшее значение, поступают на первый 144, второй 145 и третий 146 выходы блока.

Формула изобретения

Буферное запоминающее устройство, содержащее первый блок памяти, первый триггер, синхровход которого является вхо- дом начала кадра устройства и соединен с одноименным входом блока контроля, выход первого триггера соединен с информа- ционным входом второго триггера, синхровход которого соединен с входом строчных импульсов блока контроля и является одноименным входом устройства, вход сброса второго триггера соединен с одно- именным входом первого триггера, инфор- мзционный вход которого подключен, к первому выходу первого регистра, информационные входы которого являются входами управления устройства, синхровход первого регистра соединен с выходом первого элемента И, первый вход которого является входом синхронизации управления устройства, второй вход первого элемента И соединен с выходом первого дешифратора, входы которого являются входами адреса управления устройства, прямой выход второго триггера соединен с первым входом второго элемента И, второй вход которого является тактовым входом устройства, выход второго элемента И соединен с тактовым входом блока синхронизации, синхровход которого подключен к выходу генератора тактовых импульсов, вход включения блока синхронизации соединен с инверсным выходом второго триггера, выходы сигналов сбоя и конца записи блока контроля соединены с одноименными входами блока синхронизации и с информационными входами соответствующих разрядов первой группы мультиплексора, второй выход первого регистра подключен к входу режима блока обработки информации, информационные входы первой группы которого соединены с выходами второго регистра, информационные входы которого являются информационными входами устройства, входы второго дешифратора являются входами адреса выдачи информации устройства, выходы группы второго дешифратора соединены с информационными входами второй группы мультиплексора, управляющий вход которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом второго дешифратора, второй вход третьего элемента И является входом синхронизации выдачи информации устройства, выходы мультиплексора являются выходами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй и третий блоки памяти, блок определения координат светового пятна ПЗС-матрицы и блок, формирования адресов, синхровход которого соединен с выходом синхронизации адресов блока синхронизации и с синх- ровходом блока контроля, вход сброса которого соединен с одноименными входами блока формирования адресов, первого, второго и третьего блоков памяти, блока определения координат светового пятна ПЗС- матрицы и подключен к входу сброса первого триггера и выходу первого элемента И,.вход строчных импульсов блока контроля соединен с одноименным входом блока формирования адресов, выходы первой, второй и третьей групп которого соединен с соответствующими входами блока определения координат светового пятна ПЗС-матрицы и адресными входами первого, второго и третьего блоков памяти соответственно, адресный вход блока контроля

подключен к выходу первой группы блока формирования адресов, выход блока обработки информации соединен с информационными входами блоков памяти и блока определения координат светового пятна ПЗС-матрицы, вход управления записью чтением которого соединен с соответствующими входами блоков памяти и подключен к выходу управления записью-чтением блока синхронизации, первый, второй и третий выходы выбора режима которого соединены с одноименными входами блока опреде- ления координат светового пятна ПЗС-матрицы и соответствующих блоков памяти, входы синхронизации которых и вход синхронизации блока определения координат светового пятна ПЗС-матрицы объединены и подключены к соответствующему входу блока синхронизации, выход синхронизации регистров которого соединен с одноименными входами блоков памяти, входы задания режима которых и вход задания режима блока определения координат светового пятна ПЗС-матрицы объединены и подключены к второму выходу первого регистра, выходы блоков памяти объединены и подключены к информационным входам второй группы блока обработки информации, синхровход второго регистра подключен к выходу второго элемента И, выходы первой, второй и третьей групп блока определения координат светового пятна ПЗС- й 10 матрицы соединены соответственно с информационными входами третьей, четвертой и пятой групп мультиплексора, первый выход блокировки блока формирования адресов соединен с первыми входами бло- 15 кировки второго и третьего блоков памяти, а второй выход блокировки подключен к одноименным входам первого и третьего блоков памяти, первый и второй входы блокировки первого и второго блоков памя- 20 ти подключены к шине нулевого потенциала, тактовый вход блока формирования адреса соединен с одноименным входом блока синхронизации.

Ј Ј

ЛУ ft

OHM

dx3

A

Й /

/5

36

37

-38

Jff

fa

41

42 45

W 45

Фиг. 5

60

S8 S3

Ы

A

62

Фик4

PurЈ

Фив. В

иг

#з //v

its т

Фиг. 7

Фнг.д

ft

f/омер столбца

I

Фиг. fO

Ч

Фиг. tf

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-08-15—Публикация

1990-11-16—Подача