Фиг.7

Вых. 2

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в универсальных и специальных средствах измерения.

Известен преобразователь тока в интервал времени с предварительным преобразованием напряжения в ток, содержащий два конденсатора, операционный усилитель, аналоговый инвертор, компаратор, три ключа, источник образцового тока, триггер и генератор импульсов.

Недостатком данного устройства является низкая точность из-за наличия погрешности установления выходного интервала времени при скачкообразном изменении входного сигнала, а также накопления погрешности от краевых эффектов при сумми- последовательного ряда непримыкающих выходных интервалов времени йТЧизкая чувствительность.

Наиболее близким по технической сущности к предлагаемому устройству является преобразователь тока в интервал времени, содержащий три конденсатора, два операционных усилителя, компаратор, четыре ключа, два транзистора, два источника образцового тока, генератор импульсов, делитель частоты, два триггера, элемент И, одновибратор и диод.

В известном устройстве отсутствует первая из указанных выше погрешностей, а влияние второй погрешности существенно уменьшено за счет возможности учета влияния краевых эффектов. Однако, данное устройство построено таким образом, что в течение одного из полупериодов его работы отсутствует интегрирование входного тока, что приводит к потере информации о его размере и снижает достоверность информации. Кроме того, оно характеризуется низкой чувствительностью. Указанные свойства являются существенными недостатками устройства-прототипа.

Цель изобретения - повышение достоверности и повышение чувствительности устройства.

Поставленная цель достигается тем, что в известный преобразователь тока в интервал времени, содержащий входную шину, которая соединена с первым выводом первого конденсатора, первый и второй источники образцового тока, выходы которых подключены соответственно через первый и второй ключи к первым выводам второго и третьего конденсаторов, первый м второй операционные усилители, выходы которых соединены с выходами третьего и четвертого ключей, соответственно, управляющий вход третьего ключа подсоединен к инверсному выходу делителя частоты, вход которого соединен с выходом генератора импульсов и объединен с С-входом первого триггера, прямой выход которого подключен к первому входу элемента И, второй вход которого соединен с прямым выходом делителя частоты, а выход элемента И - к управляющему входу первого ключа и является первой выходной шиной, первый компаратор, первый вход которого является

0 шиной нулевЪго потенциала, а выход - соединен с R-входом второго триггера, выход которого подключен к управляющему входу второго ключа и является второй выходной шиной, первый одновибратор, дополни5 тельно введены пятый, шестой, седьмой, восьмой и девятый ключи, второй компаратор, третий операционный усилитель, второй одновибратор и третий триггер, при этом выход седьмого ключа соединен со

0 входом третьего ключа и с инвертирующим входом перового операционного усилителя, вход пятого ключа объединен со входом седьмого ключа и с перЁым выводом первого конденсатора, второй вывод которого со5 единен с выходом первого операционного усилителя, управляющие входы третьего, пятого и седьмого ключей объединены с С-входом второго триггера, выход пятого ключа соединен со входами шестого и вось0 мого ключей и подключен к первому выводу второго конденсатора, второй вывод которого соединен с выходом второго операционного усилителя, и с первым входом второго компаратора, выход которого под5 ключей к D-входу первого триггера, управляющий вход четвертого ключа объединен с управляющими входами шестого и восьмого ключей и подключен к инверсному выходу первого триггера, выход шестого ключа со0 единен С входом девятого ключа, первым выводом третьего конденсатора и инвертирующим входом третьего операционного усилителя, выход которого подключен к второму входу первого компаратора, второму

5 выводу третьего конденсатора и объединен с выходом девятого ключа, управляющий вход которого соединен с выходом третьего триггера, R- и S-входы которого соответс венно через первый и второй одновибратс

0 ры подключены к выходам элемента И и второго триггера, D-вход последнего из которых объединен с его R-входом, выход восьмого ключа подключен ко входу четвертого ключа и к инвертирующему входу вто5 рого операционного усилителя, неинвертирующие входы первого, второго и третьего операционных усилителей и второй вход второго компаратора являются шиной нулевого потенциала, при этом первый, второй, третий, четвертый, пятый, шестой и

девятый ключи выполнены с проводимостью, противоположной типу проводимости седьмого и восьмого ключей.

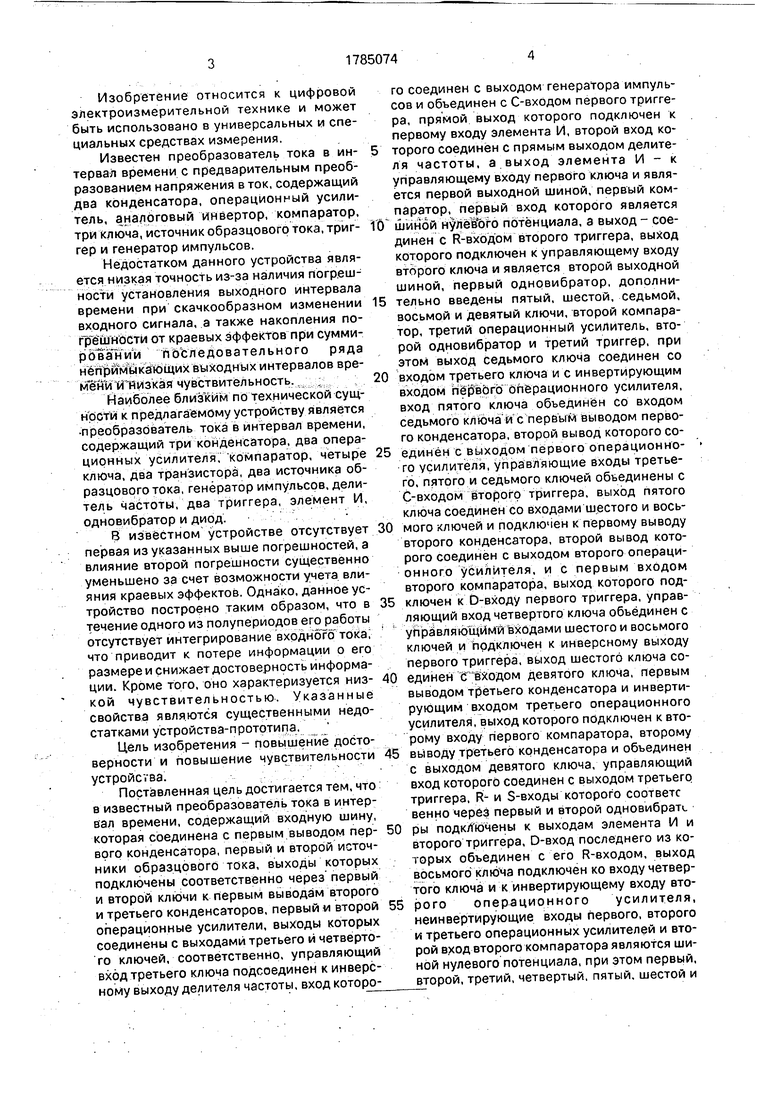

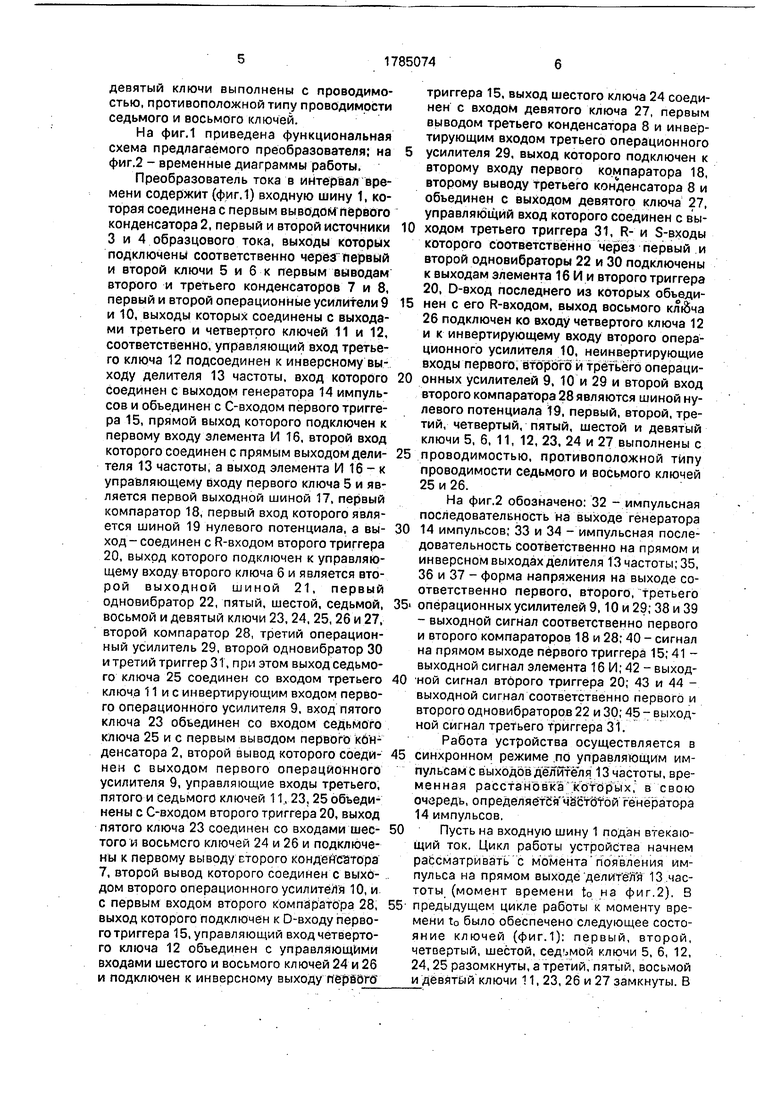

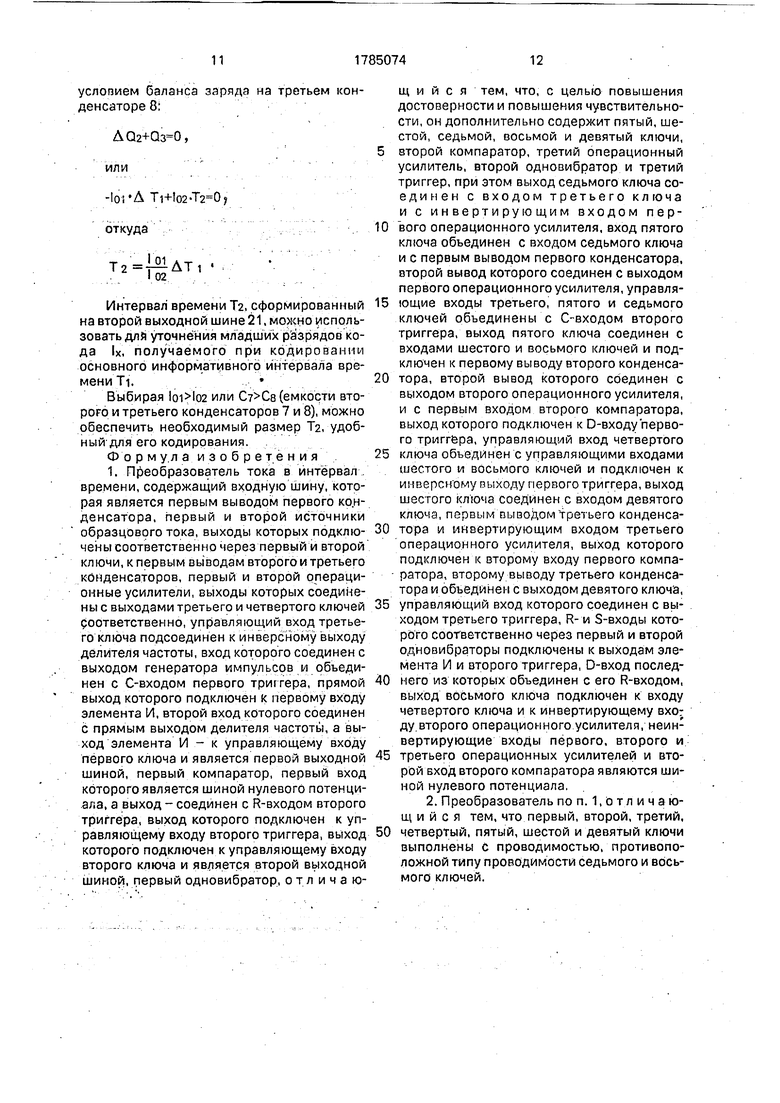

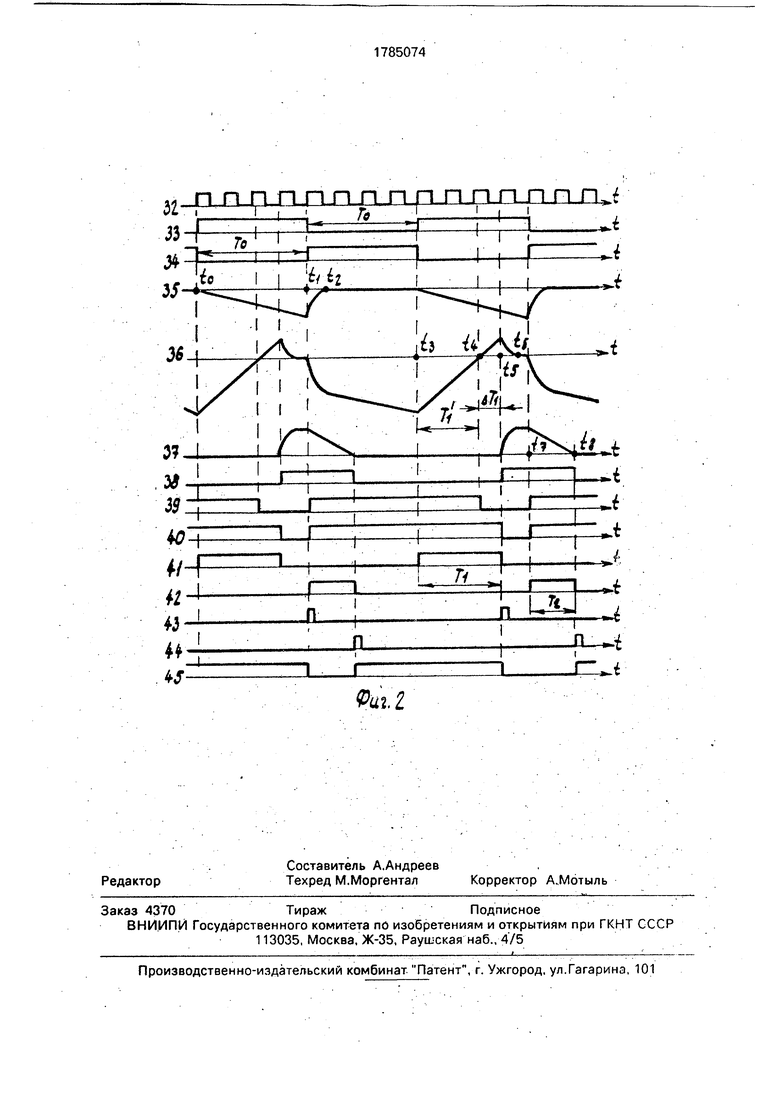

На фиг.1 приведена функциональная схема предлагаемого преобразователя; на фиг.2 - временные диаграммы работы.

Преобразователь тока в интервал времени содержит (фиг.1) входную шину 1, которая соединена с первым выводом первого конденсатора 2, первый и второй источники 3 и 4 образцового тока, выходы которых подключены соответственно через первый и второй ключи 5 и б к первым выводам второго и третьего конденсаторов 7 и 8, первый и второй операционные усилители 9 и 10, выходы которых соединены с выходами третьего и четвертого ключей 11 и 12, соответственно, управляющий вход третьего ключа 12 подсоединен к инверсному выходу делителя 13 частоты, вход которого соединен с выходом генератора 14 импульсов и объединен с С-входом первого триггера 15, прямой выход которого подключен к первому входу элемента И 16, второй вход которого соединен с прямым выходом делителя 13 частоты, а выход элемента И 16 - к управляющему входу первого ключа 5 и является первой выходной шиной 17, первый компаратор 18, первый вход которого является шиной 19 нулевого потенциала, а выход-соединен с R-входом второго триггера 20, выход которого подключен к управляющему входу второго ключа 6 и является второй выходной шиной 21, первый одновибратор 22, пятый, шестой, седьмой, восьмой и девятый ключи 23,24, 25, 26 и 27, второй компаратор 28, третий операционный усилитель 29, второй одновибратор 30 и третий триггер 31, при этом выход седьмого ключа 25 соединен со входом третьего ключа 11 и с инвертирующим входом первого операционного усилителя 9, вход пятого ключа 23 объединен со входом седьмого ключа 25 и с первым выводом первого конденсатора 2, второй вывод которого соединен с выходом первого операционного усилителя 9, управляющие входы третьего, пятого и седьмого ключей 11, 23, 25 объединены с С-входом второго триггера 20, выход пятого ключа 23 соединен со входами шестого и восьмого ключей 24 и 26 и подключены к первому выводу сторого конденсатора 7, второй вывод которого соединен с выходом второго операционного усилителя 10, и с первым входом второго компаратора 28, выход которого подключен к D-входу первого триггера 15, управляющий вход четвертого ключа 12 объединен с управляющими входами шестого и восьмого ключей 24 и 26 и подключен к инверсному выходу первого

триггера 15, выход шестого ключа 24 соединен с входом девятого ключа 27, первым выводом третьего конденсатора 8 и инвертирующим входом третьего операционного 5 усилителя 29, выход которого подключен к второму входу первого компаратора 18, второму выводу третьего конденсатора 8 и объединен с выходом девятого ключа 27, управляющий вход которого соединен с в ы0 ходом третьего триггера 31, R- и S-входы которого соответственно через первый и второй одновибраторы 22 и 30 подключены к выходам элемента 16 И и второго триггера 20, D-вход последнего из которых объеди5 нен с его R-входом, выход восьмого клича 26 подключен ко входу четвертого ключа 12 и к инвертирующему входу второго операционного усилителя 10, неинвертирующие входы первого, второго и третьего операци0 онных усилителей 9, 10 и 29 и второй вход второго компаратора 28 являются шиной нулевого потенциала 19, первый, второй, третий, четвертый, пятый, шестой и девятый ключи 5, 6, 11, 12, 23, 24 и 27 выполнены с

5 проводимостью, противоположной типу проводимости седьмого и восьмого ключей 25 и 26.

На фиг.2 обозначено: 32 - импульсная последовательность на выходе генератора

0 14 импульсов; 33 и 34 - импульсная последовательность соответственно на прямом и инверсном выходах делителя 13 частоты; 35, 36 и 37 - форма напряжения на выходе соответственно первого, второго, третьего

5 операционных усилителей 9,10 и 29; 38 и 39 - выходной сигнал соответственно первого и второго компараторов 18 и 28; 40 - сигнал на прямом выходе первого триггера 15; 41 - выходной сигнал элемента 16 И; 42 - выход0 ной сигнал второго триггера 20; 43 и 44 - выходной сигнал соответственно первого и второго одновибраторов 22 и 30; 45 - выходной сигнал третьего триггера 31.

Работа устройства осуществляется в

5 синхронном режиме по управляющим импульсам с выходов дёЖтеля 13 частоты, временная расстановка которых, в свою очередь, определяётся ча сто ой генератора 14 импульсов.

0 Пусть на входную шину 1 подан втекающий ток. Цикл работы устройства начнем рассматривать с момента появления импульса на прямом выходе делит ел я 13 частоты (момент времени to на фиг.2). В

5 предыдущем цикле работы к моменту времени t0 было обеспечено следующее состояние ключей (фиг.1): первый, второй, четвертый, шестой, седьмой ключи 5, 6, 12, 24,25 разомкнуты, а третий, пятый, восьмой и девятый ключи 11, 23, 26 и 27 замкнуты. В

результате этого к моменту времени to на выходе первого и третьего операционных усилителей 9 и 29 напряжение равно нулю, а на выходе второго операционного усилителя 10 - некоторому отрицательному значению. При этом на выходе первого компаратора 18, будет логический ноль (О), а на выходе второго компаратора 28 - логическая единица (1). Следовательно, первый триггер 15 будет в состоянии 1, а второй триггер 20 - О.

В момент времени t0 появляется импульс на прямом выходе делителя 13 частоты (на инверсном соответственно пауза). Вследствие этого размыкаются третий и пятый ключи 11 и 23 и замыкается седьмой ключ 25, имеющий противоположную про- водимо сть по сравнению с третьим и пятым ключами 11 и 23. В результате входной ток Ix устройства начнет заряжать первый конденсатор 2, включенный в цепь отрицатель- ной обратной связи (ООС) первого операционного усилителя 9. При втекающем токе 1Х за время действия импульса с прямого выхода делителя 13 частоты длительностью ti-to To первый конденсатор 2 примет заряд Qr.

ti

Ql J , to

To

где lx / Ix dt - среднее значение тока Jx

о за интервал ti-to T0.

Так как в процессе работы устройства в течение одного цикла осуществляется последовательное преобразование заряда Qi на перовом, втором и третьем конденсаторах 2, 7 и 8, то изменение заряда на втором конденсатора 7 за время ti-t0 и на третьем конденсаторе 8 за время ts-to, а также связанные с этим другие процес сй в схеме, рассматривать не будем, поскольку преобразование заряда на конденсаторах 2, 7 и 8 за указанные временные интервалы характеризуют 1Х за предыдущий цикл. Отметим лишь, что к моменту времени ti окончания импульса на прямом выходе делителя 13 частоты заряд второго конденсатора 7 будет .равен нулю.

В момент времени ti заканчивается импульс на прямом выходе делителя 13 частоты и возникает на его инверсном выходе. Вследствие этого размыкаются третий и пятый ключи 11 и 23, а седьмой ключ 25 размыкается. В это же время размыкаются четвертый и шестой ключи 12 и 24 и замыкается восьмой ключ 26. В результате на обоих

выводах заряженного первого конденсатора 2 обеспечивается нулевой потенциал: на первом выводе (левый на фиг.1) - за счет подключения через пятый и восьмой ключи

23 и 26 инвертирующего входа второго операционного усилителя 10, охваченного ООС через второй конденсатор 7; на втором выводе (п равый на фиг.2) - за счет обеспечения нуля на выходе первого операционного усилителя 9 путем его охвата ОС С через замкнутый третий ключ 11. Таким образом создаются условия для полного разряда первого конденсатора 2 на второй конденсатор 7. В результате заряд Qi полностью

переносится на второй конденсатор 7 (без учета паразитных параметров первого и второго операционных усилителей 9 и 10). Одновременно через замкнутый пятый ключ 23 второй конденсатор 7 заряжается током

1Х с входной шины 1.

Пусть к моменту времени ta разряд первого конденсатора 2 на второй конденсатор 7 закончился. Тогда в оставшееся до окончания импульса время на инверсном выходе

делителя 13 частоты второй конденсатор 7 будет заряжаться лишь током 1Х.

Одновременно с началом заряда второго конденсатора 7 второй компаратор 28 переводится в состояние 1, которое переписывается на прямой выход первого триггера 15.

За время действия импульса с инверсного выхода делителя 13 частоты длительностью t3-ti T0 второй конденсатор 7, до этого

разряженный, примет заряд Оз:

t3

0..1+ J lxdt 2lxT0 . ч

В момент времени t3 заканчивается импульс на инверсном и возникает на прямом выходе делителя 13 частоты. Это приводит к появлению на выходе элемента 16 И. В

результате описанных процессов первый и седьмой ключи 5 и 25 замыкаются, а третий и пятый ключи 11 и 23 размыкаются. Тогда ток 1Х с входной шины 1 вновь начинает заряжать первый конденсатор 2 в течение

интервала времени ty-t3i а ток loi первого источника 3 образцового тока начинает разряжать второй конденсатор 7 через замкнутый первый ключ 5 (направление тока ioi берут противоположным направлению тока

Ix). Вследствие этого в момент времени t4 выходное напряжение второго операционного усилителя 10 достигает нуля, что приводит к переходу второго компаратора 28 в состояние О и свидетельствует о полном разряде второго конденсатора 7. С одной

стороны, за время t4-t3 второй конденса 7 принял заряд Q2 :

Q.2 -loi Ti ,

з с другой, его начальный заряд к менту времени t3 был равен 0.2. Значит

/ Q2+Q2 0,

или

2lx-T0 oiTi , откуда

1х 101

То есть, интервал времени Ti несет ин- формацию о среднем значении тока Ix на входной шине 1. Однако, в общем случае момент времени t4 окончания Ti не совпадает с началом ближайшего импульса генератора 14 импульсов, что приводит при суммировании последовательного ряда непримыкающих информативных интервалов времени TI к накоплению погрешности от краевых эффектов, которая может достигать максимального значения n-Т (п - число сум- мированных интервалов времени Ti , Т - период следования импульсов генератора 14 импульсов).

Поэтому в устройстве продолжается заряд второго конденсатора 7 током loi до момента времени ts прихода ближайшего импульса с выхода генератора 14 импульсов. В момент времени ts по фронту этого импульса первый триггер 15 переходит в состояние О, отключая тем самым ток 9 от второго конденсатора 7 и фиксируя окончание информативного интервала времени Ti на выходе первого элемента 16 И, выход которого является первой выходной шиной 17.

Тогда интервал времени Ti определится как

Т1 ТЈ Т°+АТ1

Переход первого триггера 15 в состояние О в момент времени ts вызывает замыкание четвертого и шестого ключей 12 и 24 и размыкание восьмого ключа 26, который имеет противоположную проводимость по сравнению с указанными ключами 12 и 24,

Одновременно по окончании интервала времени Ti первый одновибратор 22 форми

5

0 5 0

5 0 5

0

5

рует короткий импульс, которым третий триггер 31 переводится в состояние О, что вызывает размыкание девятого ключа 27.

В результате на обоих выводах заряженного до значения A Q. второго конденсатора 7 обеспечивается нулевой потенциал: на первом выводе (левый на фиг.1) - за счет подключения через шестой ключ 24 инвертирующего входа третьего операционного усилителя 29, охваченного ООС через третий конденсатор 8; на втором выводе (правый на фиг,2) - за счет обеспечения нуля на выходе второго операционного усилителя 10 путем его охвата ООС через замкнутый четвертый ключ 12. Таким образом создаются условия для полного разряда второго конденсатора 7 на третий конденсатор 8. В результате заряд Л 02 полностью переносится на третий конденсатор 8.

Одновременно в момент времени ts первый компаратор 18 выходным напряжением третьего операционного усилителя 29 переводится в состояние 1.

Пусть к моменту времени te процесс разряда второго конденсатора 7 закончился. Тогда йторой конденсатор 7, полностью разряженный, окажется готовым к принятию новой порции заряда Qi от первого конденсатора 2, а третий конденсатор 8 хранит полученный заряд Д0.2.

В момент времени ty заканчивается импульс на прямом выходе делителя 13 частоты и начинается на инверсном его выходе. Это приводит к повторению процессов, происходящих на интервале времени и относящихся к заряду-разряду первого и второго конденсаторов 2 и 7 в новом цикле преобразования х. В частности, ключи 11, 23, 26 замыкаются, а ключи 24 и 25 размыкаются. Одновременно продолжается текущий цикл преобразования. По фронту импульса на инверсном выходе делителя 13 частоты второй триггер 20 переводится в состояние 1. Это вызывает замыкание второго ключа 6 и разряд третьего конденсатора 8 током Io2 с выхода второго источника 4 образцового тока (знак тока Io2 противоположен знаку тока loi).

В момент времени ts на третьем конден- саторе 8 суммарный зарядД0., где Q.(t8-t7), становится равным нулю, что вызывает переход первого компаратора 18 в состояние О. Это приводит к переходу второго триггера 20 в состояние О, а, следовательно, к размыканию второго ключа 6 и замыканию девятого ключа 27. Информативный интервал времени на второй выходной шине 21 устройства определяется

условием баланса заряда на третьем конденсаторе 8:

Ad2+Q3 0, или

-101 А Т1+102 Т2 0;

откуда

т шдт

Интервал времени Та, сформированный на второй выходной шине 21, можно использовать дли уточнения младших ра зрядов кода Ix, получаемого при кодировании основного информативного интервала времени TL

Выбирая или (емкости второго и третьего конденсаторов 7 и 8), можно обеспечить необходимый размер J2, удобный для его кодирования.

Формула изобретения

1. Преобразователь тока в интервал времени, содержащий входную шину, которая является первым выводом первого конденсатора, первый и второй источники образцового тока, выходы которых подключены соответственно через первый и второй ключи, к первым выводам второго и третьего конденсаторов, первый и второй операционные усилители, выходы которых соединены с выходами третьего и четвертого ключей соответственно, управляющий вход третьего ключа подсоединен к инверсйому выходу делителя частоты, вход которого соединен с выходом генератора импульсов и объединен с С-входом первого триггера, прямой выход которого подключен k первому входу элемента И, второй вход которого соединен с прямым выходом делителя частоты, а выход элемента И - к управляющему входу первого ключа и является первой выходной шиной, первый компаратор, первый вход которого является шиной нулевого потенциала, а выход - соединен с R-входом второго триггера, выход которого подключен к управляющему входу второго триггера, выход которого подключен к управляющему входу второго ключа и является второй выходной шиной, первый одновибратор, отличающийся тем, что, с целью повышения достоверности и повышения чувствительности, он дополнительно содержит пятый, шестой, седьмой, восьмой и девятый ключи,

второй компаратор, третий операционный усилитель, второй одновибратор и третий триггер, при этом выход седьмого ключа со- единен с входом третьего ключа и с инвертирующим входом первого операционного усилителя, вход пятого ключа объединен с входом седьмого ключа и с первым выводом первого конденсатора, второй вывод которого соединен с выходом первого операционного усилителя, управляющие входы третьего, пятого и седьмого ключей объединены с С-входом второго триггера, выход пятого ключа соединен с входами шестого и восьмого ключей и подключен к первому выводу второго конденсатора, второй вывод которого соединен с выходом второго операционного усилителя, и с первым входом второго компаратора, выход которого подключен к D-входу первого триггера, управляющий вход четвертого

ключа объединен с управляющими входами шестого и восьмого ключей и подключен к инверсному выходу первого триггера, выход шестого ключа соединен с входом девятого ключа, первым выводом третьего конденсатора и инвертирующим входом третьего операционного усилителя, выход которого подключен к второму входу первого компаратора, второму выводу третьего конденсатора и объединен с выходом девятого ключа,

управляющий вход которого соединен с выходом третьего триггера, R- и S-входы которого соответственно через первый и второй одновибраторы подключены к выходам элемента И и второго триггера, D-вход последнего из которых объединен с его R-входом, выход восьмого ключа подключен к входу четвертого ключа и к инвертирующему входу второго операционного усилителя, неинвертирующие входы первого, второго и

третьего операционных усилителей и второй вход второго компаратора являются шиной нулевого потенциала.

2. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что первый, второй, третий,

четвертый, пятый, шестой и девятый ключи выполнены с проводимостью, противоположной типу проводимости седьмого и восьмого ключей.

J

JlTin-nJTJTTl П

Го Л -1-1

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1988 |

|

SU1728871A1 |

| Устройство для измерения среднего значения тока | 1988 |

|

SU1550432A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Преобразователь напряжения в интервал времени | 1989 |

|

SU1621177A2 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| НУЛЬ-ОРГАН | 2020 |

|

RU2754963C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Преобразователь сигнала тензомоста в интервал времени | 1987 |

|

SU1580260A1 |

| Устройство для управления электромагнитом | 1989 |

|

SU1665413A1 |

Изобретение относится к цифровой электроизмерительной технике и моэрет быть использовано в универсальных и специальных средствах измерения. Цель изобретения - повышение достоверности информации и повышение чувствительности. Преобразователь содержит входную клемму 1, три конденсатора 2, 7 и 8, два источника 3 и 4 образцового тока, девять ключей 5,6,11,12,20-24, три операционных усилителя 9, 10 и 26, делитель 13 частоты, генератор 14 импульсов, три триггера 15,18 и 28, элемент И 16, два компаратора 17 и 25, два одновибратора 19 и 27. 1 з.п. ф-лы, 2 ил.

0U2.2

| Преобразователь напряжения в интервал времени | 1985 |

|

SU1285599A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1529459A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-30—Публикация

1990-09-06—Подача