второго передающих регистров, о т.л и ;Ч а ю щ е е с я тем, что, с целью повышения пропускной способности устройства, в него введены К-1 матриц каналов обмена, а в каждый канал обмена введены третьи приемный и передающий регис тры, пер вый, второй, третий и четвертый мультиплексоры, регистр,управления четвертым мультиплексором, блок управления первым, вторым и третьим мультиплексор миу третий блок элеметов И, распределитель имп льсов и счетчик, причем четвертый информационный выход канала обмена m -ой строки 1 -го столбца к-ой матрицы (к t: 1,К) соединен с четвертым информационным входом канала обмена т-ой строки п -го столбца (к+1)-ой матрицы, четвертый информационный выход канала обмена hi -ой строки столбца к-ой матрицы соединен с четвертым информационным входом канала обмена Ип-ой строки п -го столбца первой матрицы, в каждом канале обмена выход счетчика соединен с первым управляющимм входом блока управления первым/ вторым и третьим мультиплексорами, второй управляющи вход которого соединен с входом распределителя и шyльcoв, первым управляющим входом канала обмена, первыми входами регистра управления четБпртым мультиплексором и счетчика, вторым входом соединенного с первым выходом распределителя импулсов, второй и третий выходы которог соединены соответственно с третьим управляющим входом блока управления первым, вторым и третьим мультиплексорами и управляющими входами первого, второго и- третьего передающих регистров, а четвертый и пятый выходы - соответственно с пятым входом узла коммутации управляющих с; гналов и третьим входом упра.вляющего регистра, вторым выходом соединенного с четвертым управляющим входом блока управления, первым, вторым и третьим мультиплексорами, первый выход которого соединен с шестым входом узла коммутации управляюии.1х сигналов, шестым, четвертым, н седьмым выходами соединенного сооветственно с вторым входом регистра управления четвертым мультиплексором, управляющим входом третьего блока элементов И и пятым управляющим входом блока, управления первым, вторым и третьим мультиплексорами, четвертый информационный вход блока сравнения соединен с информационным выходом третьего приемного регистра а инфорг-шционный выход - с информационными входами первого, второго и третьего блоков элементов И, информационными выходами соединенных соответственно с первым, вторым итретьим информационными входами блока управления мультиплексорами, второй, третий и четвертый выходы которого соединены с управляющими входами, соответственно первого, второго и третьего мультиплексоров, управляющий вход четвертого мультиплексора соединен с выходом регистра управления четвертым мультиплексором, информационные входы первого, второго .и третьего передающих регистров и второго буферного регистра соединены соответственно с выходами первого, второго, третьего и четвертого мультиплексоров, первыми, вторыми и третими информационными входами соединенных соответственно с информационными выходами первого, второго и третьего приемных регистров,, информационный . выход первого буфернохо регистра соединен с четвертыми информационными входами первого, второго и третьего мультиплексоров, управляющий вход третьего приемного регистра соединен с первьам управляющим входом канала обмена, четвертые информационные вход и выход которого связаны соответственно с информационным входом третьего приемного регистра и информационным выходом третьего передающего регистра.

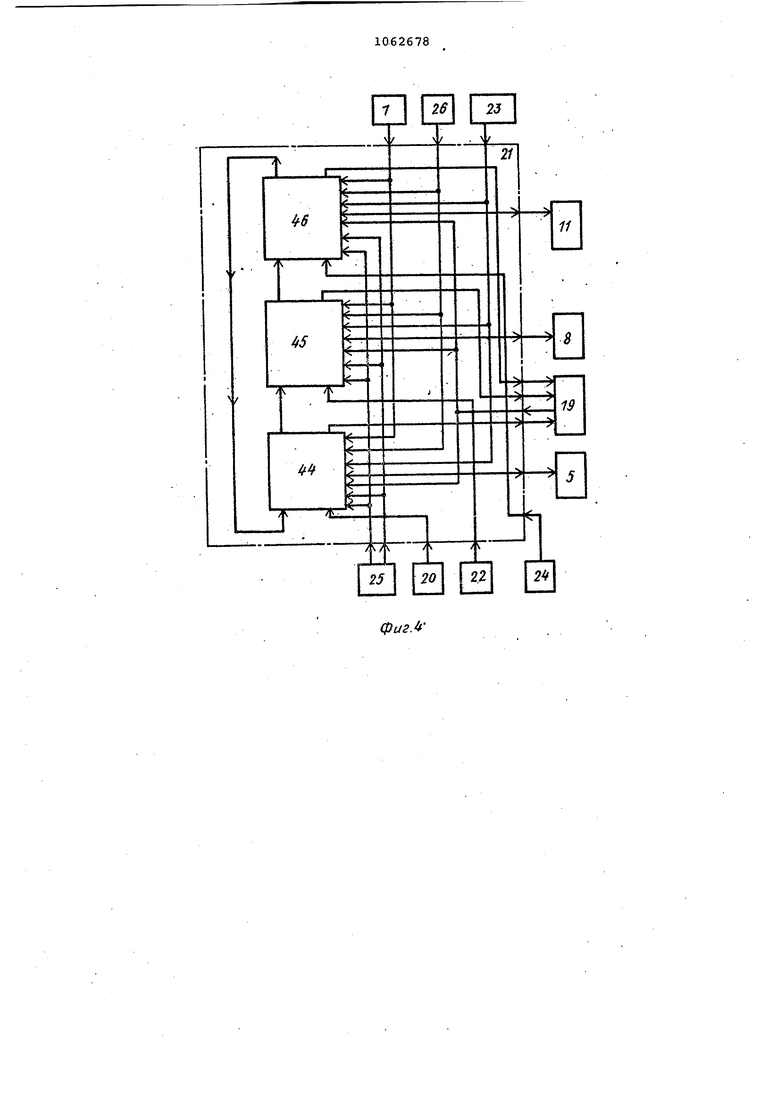

2. Устройство по п, 1, отличающееся тем, что блок управле ия первым, вторым и третьим мультиплексорами содержит первый, второй и третий узлы управления мультиплексором, каждый из которых содержит входной и выходной регистры, схему сравнения, триггер занятости узла и регистр управления мультиплексором, причем первые информационные входы входных регистров первого, второго и третьего узлов управления мультиплексором соединены соответственно с выходами выходных регистров третьего, первого и второго узлов управления мультиплексором, вторые информационные входы - соответственно с первым, вторым и третьим информационными входами блока, а первые и вторые управляющие входы - соответственно с третьим и четвертым управляющими входами блока, в каждом узле управления мультиплексором выход входного регистра соединен с информационными входам - выходного регистра, схемы сравнения и регистра управления мультиплексором, первые управляющие входы которых подключены соответственно к третозму, первому и второму управляющим входам блока, а вторые управляющие входы - соответственно к первому выходу схемы сравнения, первому выходу триггера занятости узла и пятому управляющему входу блока, третий управляющий вход выходного регистра соединен с вторым выходом схемы сравнения, третьим управляющим входом регистра управления мультиплексором и первым входом триггера занятости узла, вторые вход и выход которого подключены соо гветственно к, второму управляющему входу

и первому выходу блока, выход регистров управления мультиплексорами первого, второго и третьего узлов управления мультиплексором являются соответственно вторым, третьим и четвертым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1981 |

|

SU983699A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU924694A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство связи для вычислительной системы | 1984 |

|

SU1164722A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство связи для вычислительной системы | 1988 |

|

SU1624469A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Устройство для сопряжения процессоров в однородной вычислительной системе | 1984 |

|

SU1179364A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1042008A1 |

1. УСТРОЙСТВО СВЯЗИ ДЛЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее первую матрицу каналов обмена .размерностью M-N (где М - количество строк, (i - количество столбцов матрицы) , первый управляющий вход каждого из которых соединен с выходом генератора тактовых импульсов, первый информационный выход канала обмена tn -ой строки п -го столбца первой матрицы (,М; п-1 ) связан с первым информационным входом канала обмена (т+1)-ой строки,tt -го столбца первой матрицы, первый информационный выход канала обмена М-ой строки П -го столбца первой матрицы соединен с первым информационным входом канала обмена первой строки ti -го столбца первой матрицы, второй информационный выход канала обмена Щ -ой строки fit-го столбца первой матрицы соединен с вторым информационнь м входом канала, обменат-ой строки (ц-И)-го столбца первой матрицы, второй информацион- ный выход канала обмена tn-ой строки. N-ro столбца первой матрицы соединен с вторым информационным входом канала обмена п-ой строки первого столбца первой матрицы,третьи информационные вход и выход, второй управляющий и управляющий выход канала обмена W -ой строки Л1 -го столбца первой матрицы являются соответствующей подгруппой первой группы входов и выходов устройства, причем каждый канал обмена содержит первые и втсфые приемные, передающие и буферные регистры, регистр адреса, блок сравнения, узел коммутации управляющих сигналов, первый и второй блоки элементов И и управляющий регистр, первым входом соединенный с первым управдянвдим входом канала обмена, первым входом узла коммутации управляющих сигналов и управляющими входами первого и второго приемных регистров, информационные взводы которых соединены соответственно с первым и вторым информационными входами канала обмена, а инфор1 мационные выходы - соответственно с первым и вторым информационными СЛ входами блока сравнения, третий информационный вход которого соединен с выходом регистра адреса и первым информационным входом первого бу.а ферного регистра, второй информацион ный вход которого и информационный выход второго буферного регистра соединены соответственно с третьими. О информационными входом и выходом з:) канала обмена, а управляющие входы соответственно с первым и вторым ю з: выходами узла коммутации управляющих сигналов, вторым и третьим входами соединенного соответственно с Nl Ж управляющим выходом блока сравнения и первым выходом управляющего регистра, второй вход которого соединен с третьим выходом узла коммутации управляющих сигналов,четвертым выходом соединенного с управляющими входами первого и второго блоков элементов И, а четвертым входом и пятым выходом - соответственно с вторым управляющим входом и управляющим выходом кансша обмена, первый и второй информационные выходы которого соединены с информационными выходами соответственно первого и

Изобретение отнрсится к вычислительной технике и может быть использовано в мультипроцессорных вычислительных системах.

Известны устройства связи для вычислительной системы, содержащие бло синхронизации и М блоков сопряжения, каждый из которых включает приемный и передающий регистры/ распределител импульсов, управляющий регистр, узел коммутации управляющих сигналов, схему сравнения, узел синхронизации, первый, второй и третий буферные регистры, элементы ИЛИ, регистр адреса, регистр состояния и коммутатор информации Г .

Недостаток этих устройств состоит в низком быстродействии.

Наиболее близким по технической сущности к предлагаемому является устройство связи для вычислительной системы, содержащее блок формирования тактовых импульсов и матрицу каналов обмена размерностью М N (где М - количество строк, VI - количество столбцов матрицы), причем каждый канал обмена содержит первые приемный и передающий регистры, вторые приемный и передающий регистры, первый и второй элементы ИЛИ, первый и второй элементы И, блок сравнения, регистр адреса, управляющий регистр, блок выбора магистрали, регистр признака передачи, блок коммутации-управляющи сигналов и первый, второй,третий и . четвертый и пятый буферные регистры 2 .

Недостаток этого устройства состоит в низкой пропускной способности которая снижается по мере увеличения числа подключаемых модулей, в результате чего увеличивается время обмена сообщениями между модулями вычислительной системы.

Целью изобретения является повышение пропускной способности устройства.

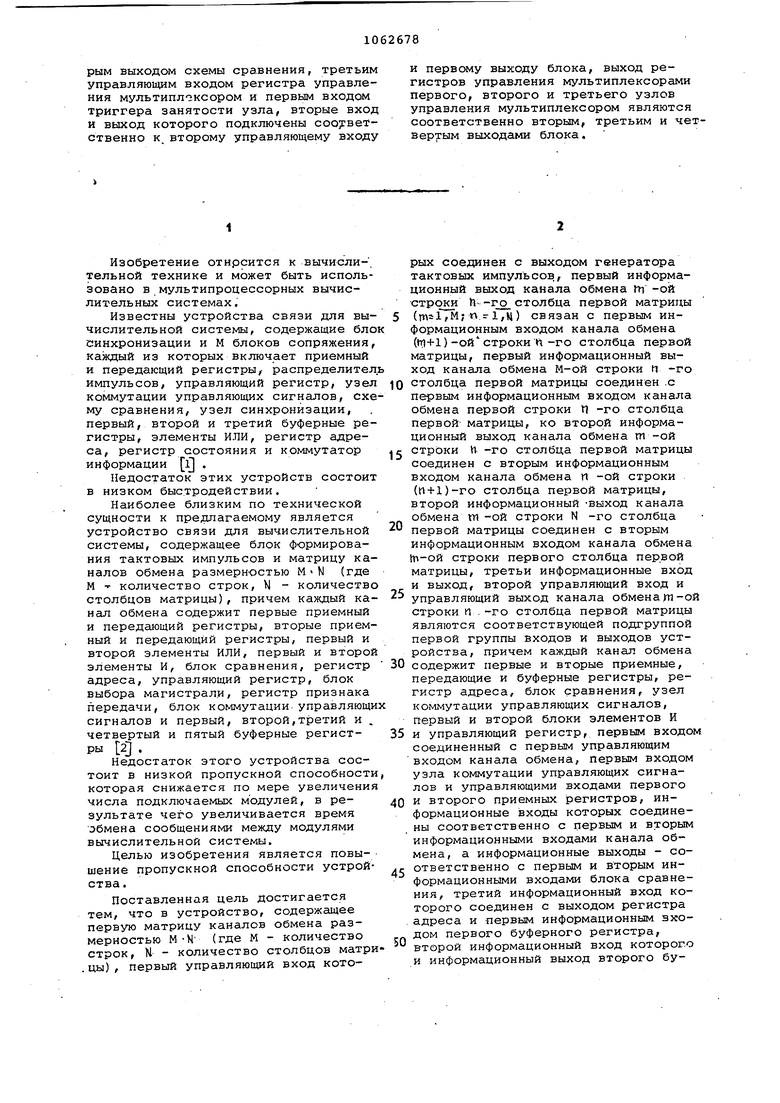

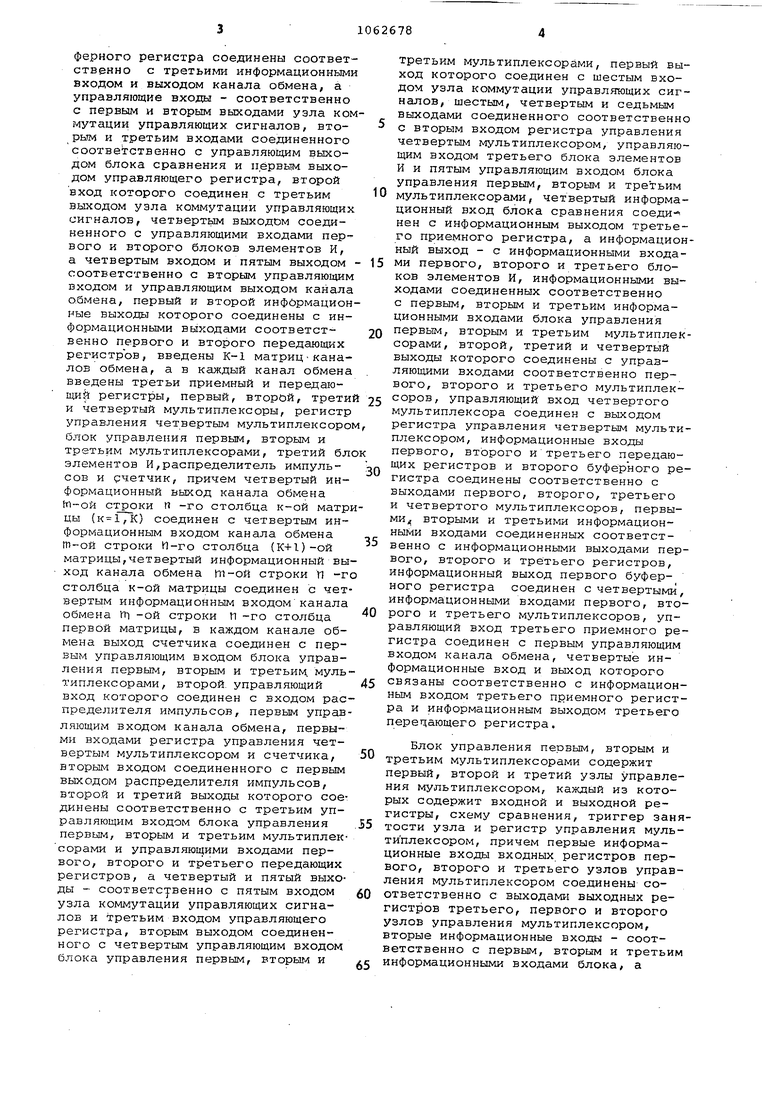

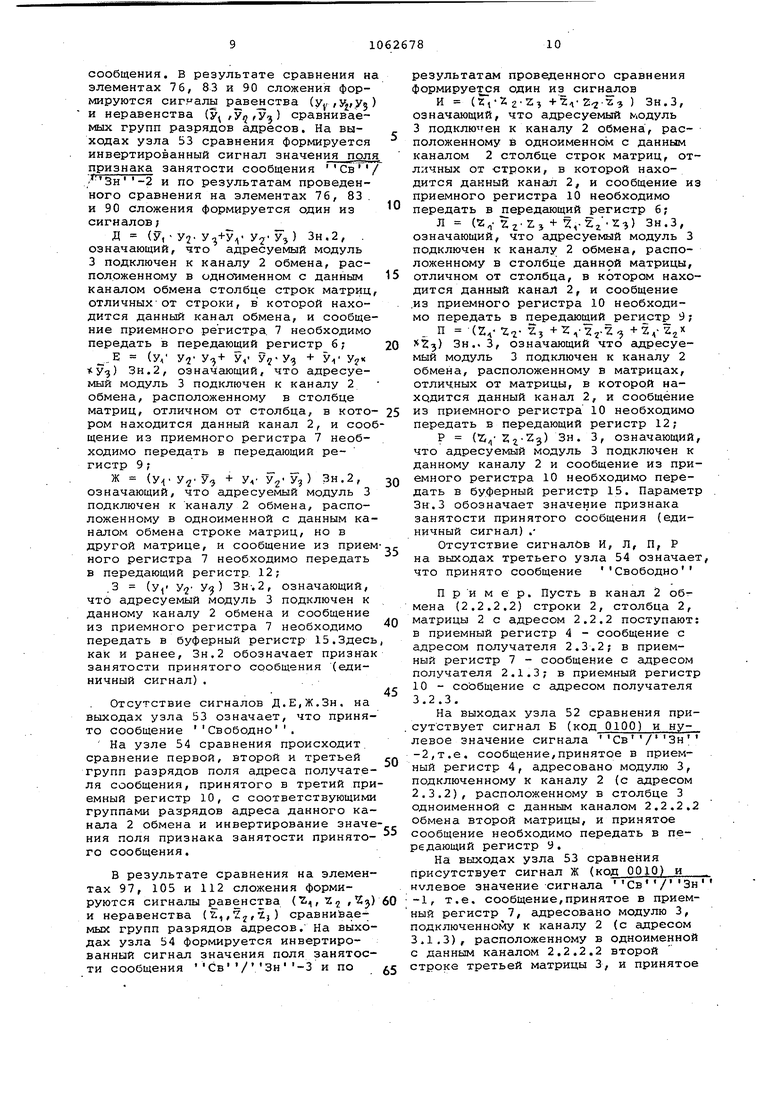

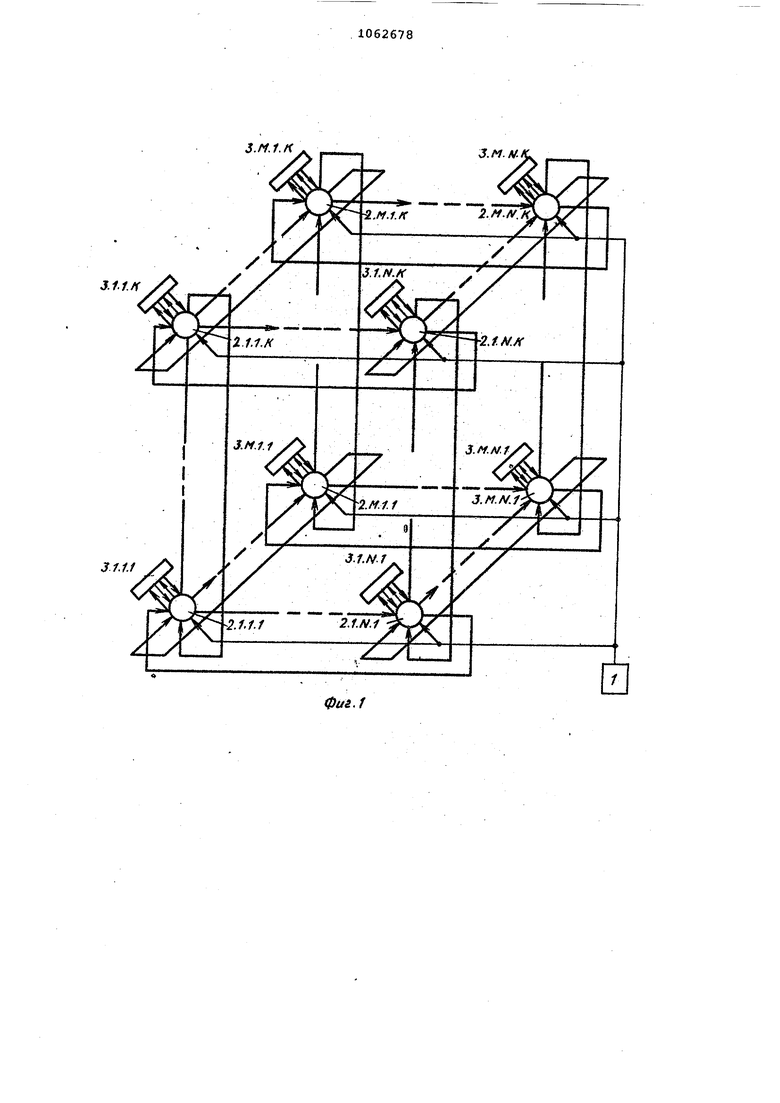

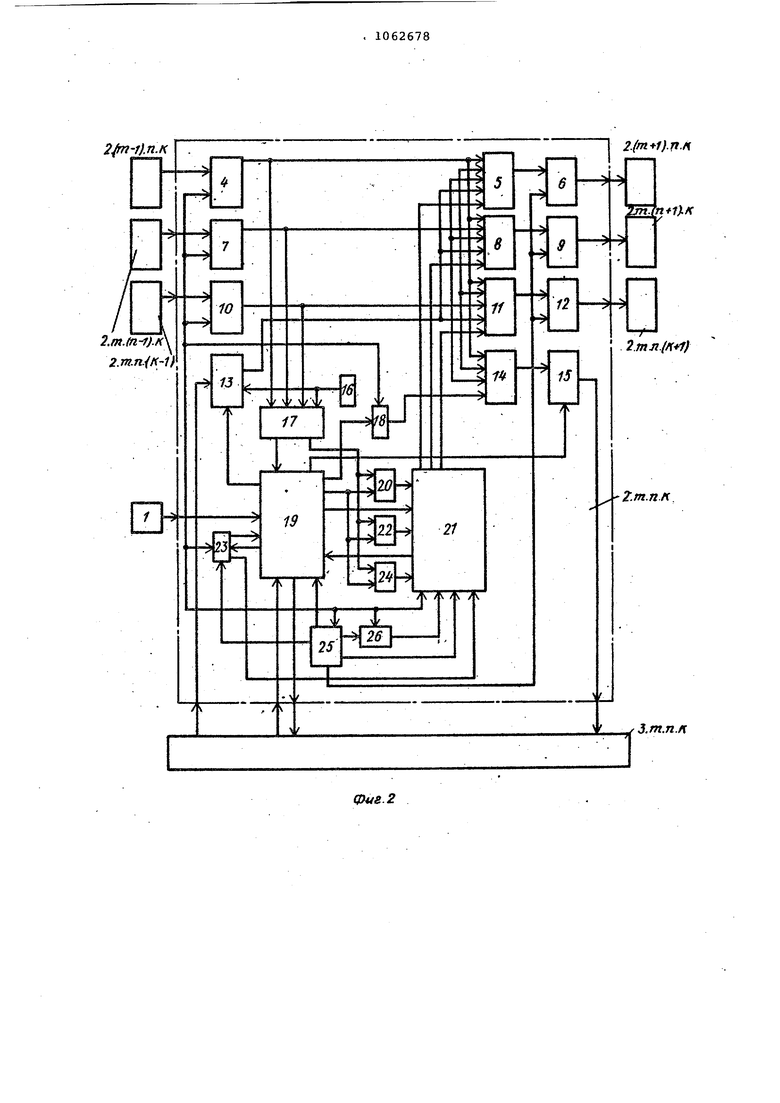

Поставленная цель достигается тем, что в устройство, содержащее первую матрицу каналов обмена размерностью M-N (где М - количество строк, N - количество столбцов матри.цы), первый управляющий вход которых соединен с выходом генератора тактовых импульсов., первый информационный выход канала обмена Гц -oift строки й--го столбца первой матрицы ( п - 1,ц ) связан с первым информационным входом канала обмена (П+1)-ойстроки ft-го столбца первой матрицы, первый информационный выход канала обмена М-ой строки И -го столбца первой матрицы соединен .с первым информационным входом канала обмена первой строки И -го столбца первой матрицы, ко второй информационный выход канала обмена m -ой строки tt -го столбца первой матрицы соединен с вторым информационным входом канала обмена п -ой строки (n + D-ro столбца первой матрицы, второй информационный Выход канала обмена tn -ой строки N -го столбца первой матрицы соединен с вторым информационным входом канала обмена tn-ой строки первого столбца первой матрицы, третьи информационные вход и выход, второй управляющий вход и управляющий выход канала обмена )11-о строки п .-го столбца первой матрицы являются соответствующей подгруппой первой группы входов и выходов устройства, причем каждый канал обмена содержит первые и вторые приемные, передающие и буферные регистры, регистр адреса, блок сравнения, узел коммутации управляющих сигнгшов, первый и второй блоки элементов И и управляющий регистр, первым входо соединенный с первым управляющим входом канала обмена, первым входом узла коммутации управляющих сигналов и управляющими входами первого и второго приемных регистров, информационные входы которых соединены соответственно с первым и вторым информационными входами канала обмена, а информационные выходы - соответственно с первым и вторым информационными входами блока сравнения, третий информационный вход которого соединен с выходом регистра адреса и первым информационным входом первого буферного регистра, второй информационный вход которого и информационный выход второго буферного регистра соединены соответственно с третьими информационными входом и выходом канала обмена, а управляющие входы - соответственно с первым и вторым выходами узла ком мутации управляющих сигналов, вторым и третьим входами соединенного соответственно с управляющим выходом блока сравнения и первым выходом управляющего регистра, второй вход которого соединен с третьим выходом узла коммутации управляющих сигналов, четвертым выходом соединенного с управляющими входами первого и второго блоков элементов И, а четвертым входом и пятым выходом соответственно с вторым управляющим входом и управляющим выходом канала о.бмена, первый и второй информацион ные выходы которого соединены с информационными выходами соответствеяно первого и второго передающих регистров, введены К-1 матрицканалов обмена, а в каждый канал обмена введены третьи приемный и передающи регистры, первый, второй, трети и четвертый мультиплексоры, регистр управления четвертым мультиплексоро блок управления первым, вторым и третьим мультиплексорами, третий бл элементов И,распределитель импульсов и рчетчик, причем четвертый информационный выход канала обмена tn-ой строки п -го столбца к-ой матр цы () соединен с четвертым информационным входом канала обмена т-ой строки П-го столбца {К+1)-ой матрицы,четвертый информационный вы ход канала обмена т-ой строки и -г столбца к-ой матрицы соединен с чет вертым информационным входом канала обмена П -ой строки 11 -го столбца первой матрицы, в каждом канале обмена выход счетчика соединен с первым управляющим входом блока управления первым, вторым и третьим, муль типлексорами, второй, управляющий вход которого соединен с входом рас пределителя импульсов, первым управ ляющим входом канала обмена, первыми входами регистра управления четвертым мультиплексором и счетчика, вторым входом соединенного с первым выходом распределителя импульсов, второй и третий выходы которого сое динены соответственно с третьим управляющим входом блока управления первым, вторым и третьим мультиплек сорами и управляющими входами первого, второго и третьего передающих регистров, а четвертый и пятый выходы - соответственно с пятым входом узла коммутации управляющих сигналов и третьим входом управляющего регистра, вторым выходом соединенного с четвертым управляющим входом блока управления первым, вторым и третьим мультиплексорами, первый выход которого соединен с шестым входом узла коммутации управляющих сигналов, шестым, четвертьом и седьмым выходами соединенного соответственно с вторым входом регистра управления четвертым мультиплексором, управляющим входом третьего блока элементов И и пятым управляющим входом блока управления первым, вторым и третьим мультиплексорами, четвертый информационный вход блока сравнения соединен с информационным выходом третьего приемного регистра, а информационный выход - с информационными входами первого, второго и третьего блоков элементов И, информационными выходами соединенных соответственно с первым, вторым и третьим информационными входами блока управления первым, вторым и третьим мультиплексорами, второй, третий и четвертый выходы которого соединены с управляющими входами соответственно первого, второго и третьего мультиплексоров, управляющий вход четвертого мультиплексора соединен с выходом регистра управления четвертым мультиплексором, информационные входы первого, второго и третьего передающих регистров и второго буферного регистра соединены соответственно с выходами первого, второго, третьего и четвертого мультиплексоров, первыми вторыми и третьими информационными входами соединенных соответственно с информационными выходами первого, второго и третьего регистров, информационный выход первого буферного регистра соединен с четвертыми, информационными входами первого, второго и третьего мультиплексоров, управляющий вход третьего приемного регистра соединен с первым управляющим входом канала обмена, четвертые информационные вход и выход которого связаны соответственно с информационным входом третьего приемного регистра и информационным выходом третьего перетающего регистра. Блок управления первым, вторым и третьим мультиплексорами содержит первый, второй и третий узлы управления мультиплексором, каждый из которых содержит входной и выходной регистры, схему сравнения, триггер занятости узла и регистр управления мультиплексором, причем первые информационные входы входных регистров первого, второго и третьего узлов управления мультиплексором соединены соответственно с выходами выходных регистров третьего, первого и второго узлов управления мультиплексором, вторые информационные входы - соответственно с первым, вторым и третьим информационными входами блока, а первйе и вторые управляющие входы соответственно с третьим и четвертым управляющими входами блока, в каждом узле управления мультиплексором выг ход входного регистра соединенсс информационными входами выходного регистра, схемы сравнения и регистра управления мультиплексором, первые управляющие входы которых подключены соответственно к третьему, первому и второму управляющим входам блока, а вторые управляющие входы - соотве ственно к первому выходу схемы срав нения, первому выходу триггера заня тости узла и пятому управляющему входу блока, третий управляющий вход выходного регистра соединен с вторы выходом схемы сравнения, третьим управляющим входом регистра управле ния мультиплексором и первым входом триггера занятости узла, вторые вход и выход которого подключены соответственно к второму управляюще му входу и первому выходу блока, вы ходы регистров управления мультиплек сорами первого, второго и третьего узлов управления мультиплексором являются соответственно вторым, третьим и четвертым выходами блока. На фиг.1 представлена блок-схема устройства связи для -вычислительной системы; на фиг 2 - схема канал обмена; на фиг.3 - схема узла коммутации управляющих сигналов; на фиг.4 - схема блока управления пер вым, вторым и третьим мультиплексора ми; на фиг,5 - схема узла управления; на фиг.6 - схема блока сравнения; на фиг. - схема первого узла сравнения; на фиг.8 - схема второго узла сравнения; на фиг.9 - схема третьего узла сравнения. В состав устройства(фиг Л) входя генератор 1 тактовых импульсов и К матриц каналов 2 обмена по М- . каналов обмена в каждой матрице. Каж дый канал 2 обмена соединен информационными и управляющими входами и выходами с соответствующим модулем 3 вычислительной системы. В состав каждого канала 2 обмена (на фиг.2 показан канал 2 обмена ги-ой строки г -го столбца к-ой матрицы) входят первый приемный регистр 4, первый мультиплексор 5, первый передающий регистр б, второй приемный регистр 7, второй мультиплексор 8, второй передающий регистр 9, третий приемный регистр 10, третий мультиплексор 11, третий передак)щий регистр 12, первый буферный регистр 13,четвертый мультиплексор 14, второй буферный регистр 15, регистр 16 адреса, блок 17 сравнения, регистр 18 управления четвертым мультиплексором, узел 19 коммутации управляющих сигналов, первый блок 20 элементов И, блок 21 управления первым, вторым и третьим мультиплексорами, второй блок 22 элементов и, управляющий регистр 23, третий блок 24 элементов И, распределитель 25 импульсов и счетчик 26. Приемные регистры 4, 7, 10 и передающие регистры 6, 9, 12 предназначены для передачи сообщений между каналами 2 обмена. Формат сообщений, передаваемых между каналами 2 обмена, содержит адрес получателя, адрес отправителя, признак занятости сообщения (Свободно / Занято ), данные (адрес ячейки памяти,- признак Запрос/ Ответ , признак Чтение / За.пись , собственно данные). Первый буферный регистр13 предназначен для приема адреса отправителя из регистра 16 адреса и информации (адрес.получателя, данные) из модуля 3 вычислительной системы, формирования сообщения и передачи его в один из передающих регистров 6, 9, 12. Второй буферный регистр 15 предназначен для приема информации (адрес отправителя, данные) из одного из приемных регистров 4, 6, 10 и передачи ее в модуль 3 вычислительной системы. Регистр 16 адреса содержит первую группу из а триггеров, представляющую собой номер Строки матрицы в двоичном представлении, вторую группу из Ъ Триггеров, представляющую собой номер столбца матрицы в двоичном представлении, третью группу из С триггеров, представляющую собой номер матрицы в двоичном представлении и предназначен для хранения адреса канала 2 обмена. Адрес канала 2 обмена в регистр 16 адреса заносится с помощью тумблерного набора с пульта управления (не показан) . Регистр 18 управления четвертым мультиплексором содержит три триггера, служит для выдачи сигналов управления четвертым мультиплексором 14, Узел 19 коммутации управляющих сигналов предназначен .для коммутации управляющих сигналов и содержит (фиг.З) первый элемент И 27, первый элемент НЕ 28, первый элемент ИЛИ-НЕ 29, второй элемент И 30, второй элемент НЕ 31, второй элемент ИЛИ-НЕ 32, третий элемент И 33, третий элемент ИЛИ-НЕ 34,четвертый элемент И 35, .первый элемент ИЛИ 36, пятый, шестой, седьмой и восьмой элементы И 37 - 40, второй элемент ИЛИ 41, девятый и десятый элементь. И 42 и 43.

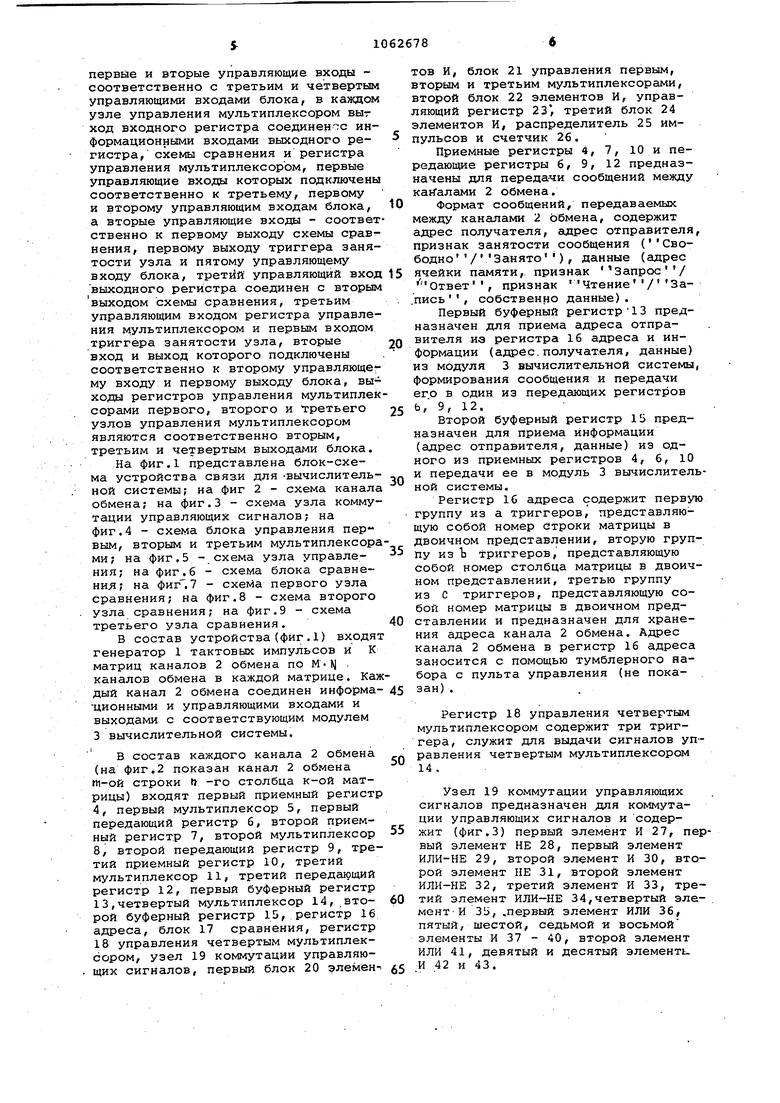

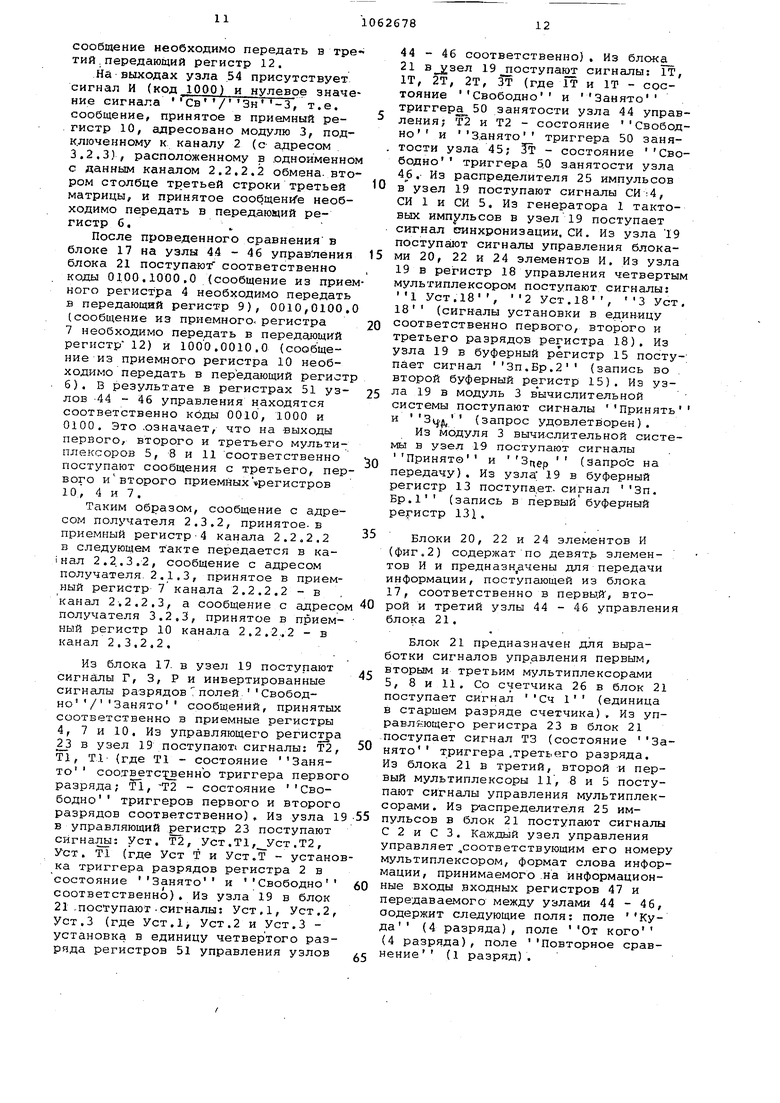

Блок 21 управления (фиг.4) содержит, первый,второй и третий узлы 44 46 управления, каждый из которых состоит (фиг.5) из входного (приемного) регистра 47, выходного (передающего) регистра 48, схемы 49 сравнения, триггера 50 занятости узла и регистра 51 управления мультиплексором,

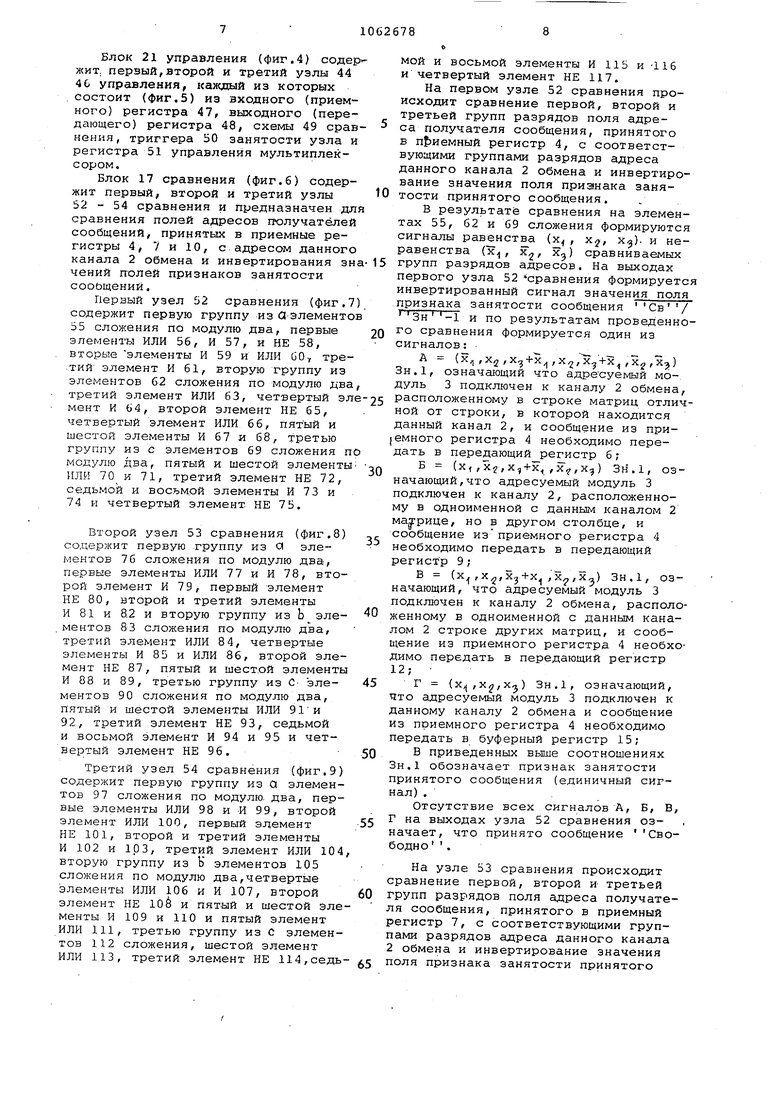

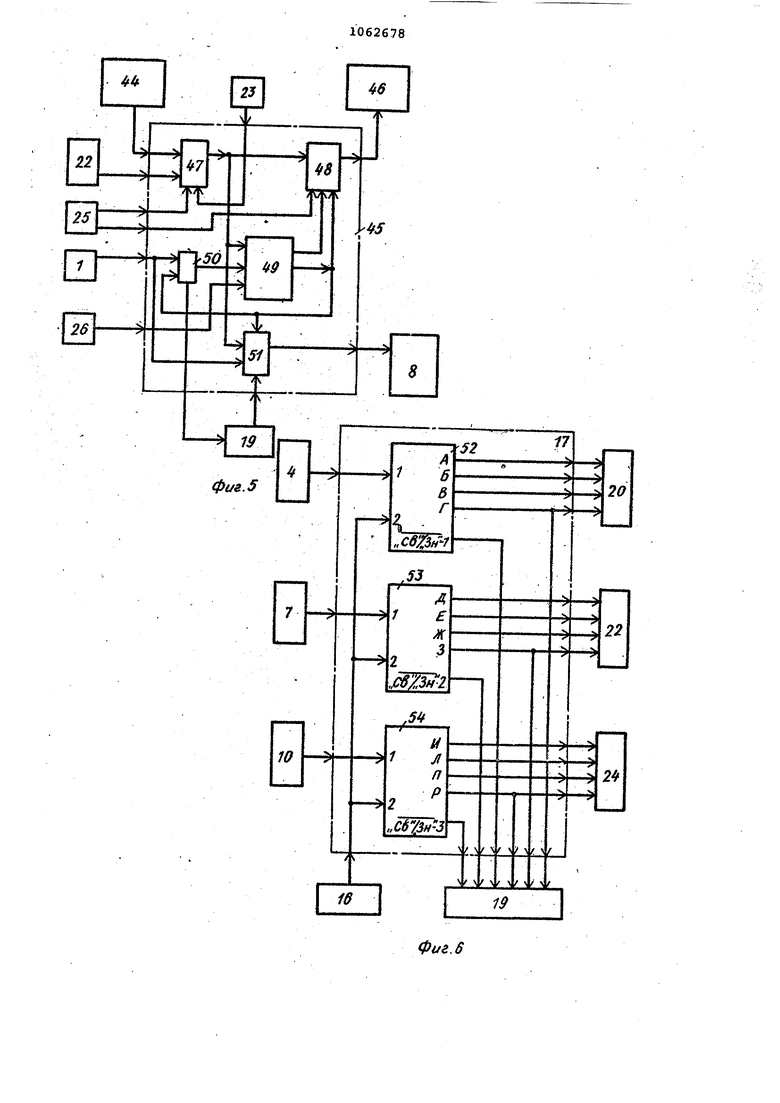

Блок 17 сравнения (фиг.б) содержит первый, второй и третий узлы 52 - 54 сравнения и предназначен дл сравнения полей адресов шэлучатёлей сообщений, принятых в приемные регистры 4, 7 и 10, с адресом данного канала 2 обмена и инвертирования зн чений полей признаков занятости сообщений.

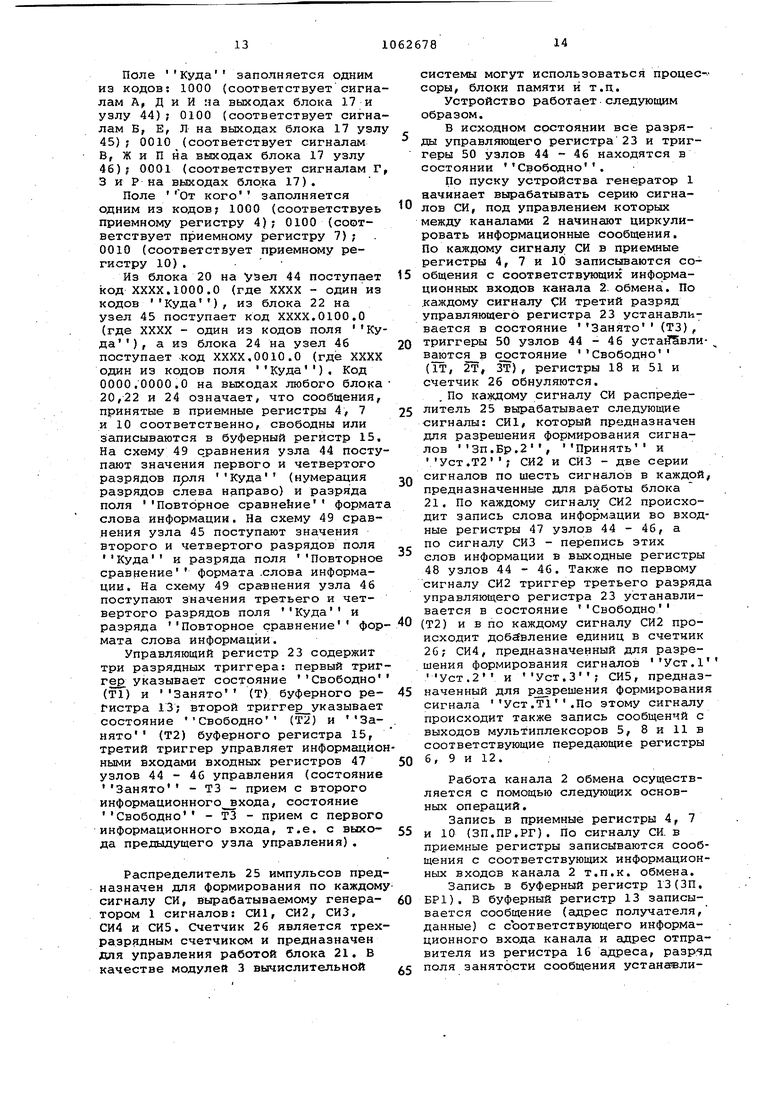

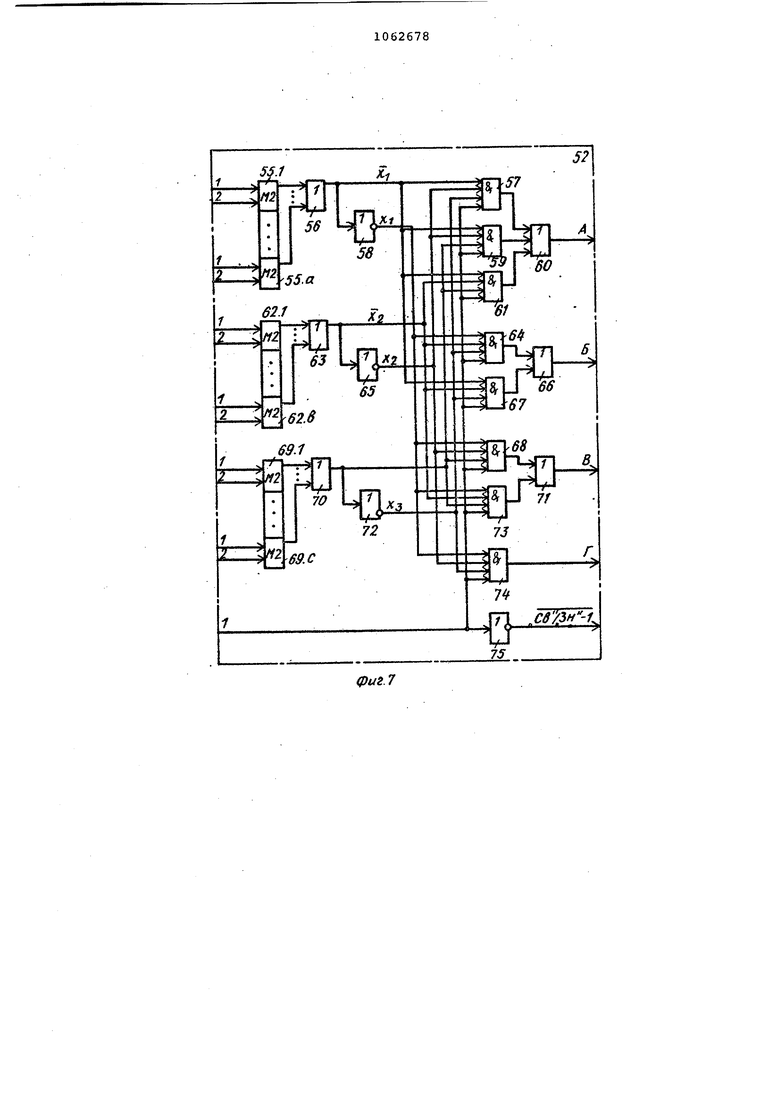

Первый узел 52 сравнения (фиг,7 содержит первую группу из С элементо 55 сложения по модулю два, первые элементы ИЛИ 56, И 57, и НЕ 58, BTCpBie элементы И 59 и ИЛИ GO у третий элемент И 61, вторую группу из элементов 62 сложения по модулю два третий элемент ИЛИ 63, четвертый эл мент И 64, второй элемент НЕ 65, четвертый элемент ИЛИ 66, пятый и шестой элементы И 67 и 68, третью группу из с элементов 69 сложения п модулю два, пятый и шестой элементы ИЛИ 71, третий элемент НЕ 72, седьмой и восьмой элементы И 73 и 74 и четвертый элемент. НЕ 75.

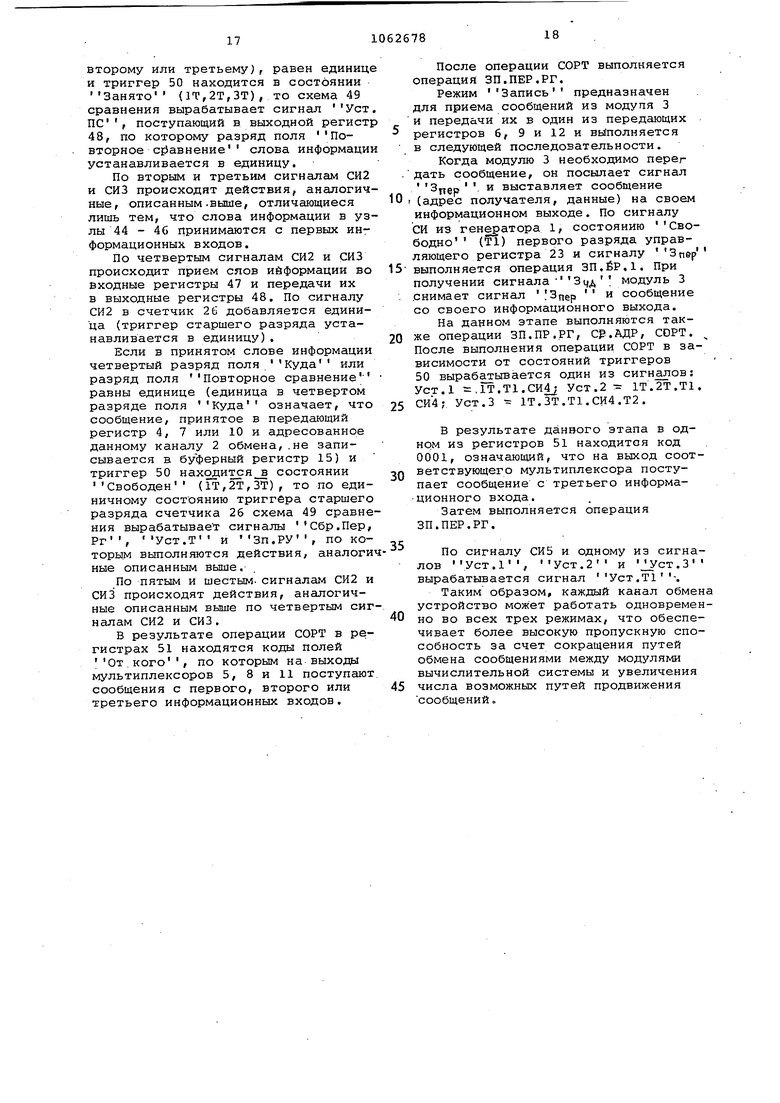

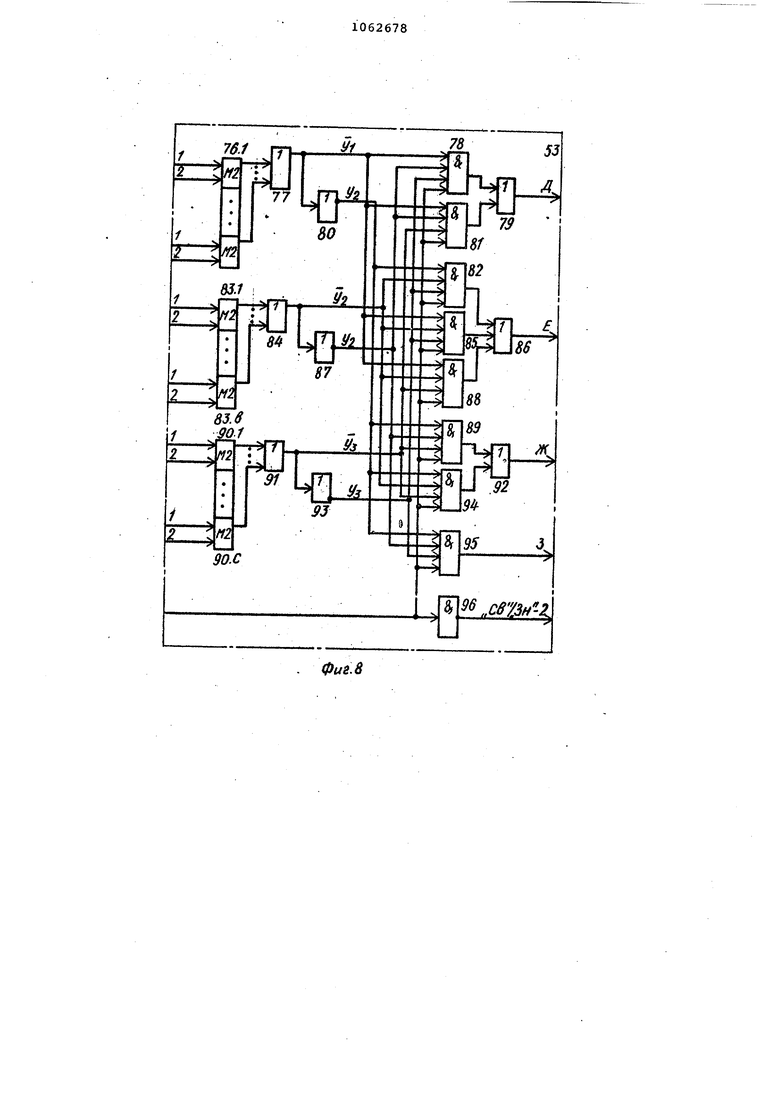

Второй узел 53 сравнения (фиг.8) содержит первую группу из а элементов 76 сложения по модулю два, первые элементы ИЛИ 77 и И 78, второй элемент И 79, первый элемент НЕ 80, второй и третий элементы И 81 и 8.2 и вторую группу из Ь элементов 83 сложения по модулю два, третий элемент ИЛИ 84, четвертые элементы И 85 и ИЛИ 86, второй элемент НЕ 87, пятый и шест.ой элементы И 88 и 89, третью группу из С- элементов 90 сложения по модулю два, пятый и шестой элементы ИЛИ 91и 92, третий элемент НЕ 93, седьмой и восьмой элемент И 94 и 95 и четвертый элемент НЕ 96.

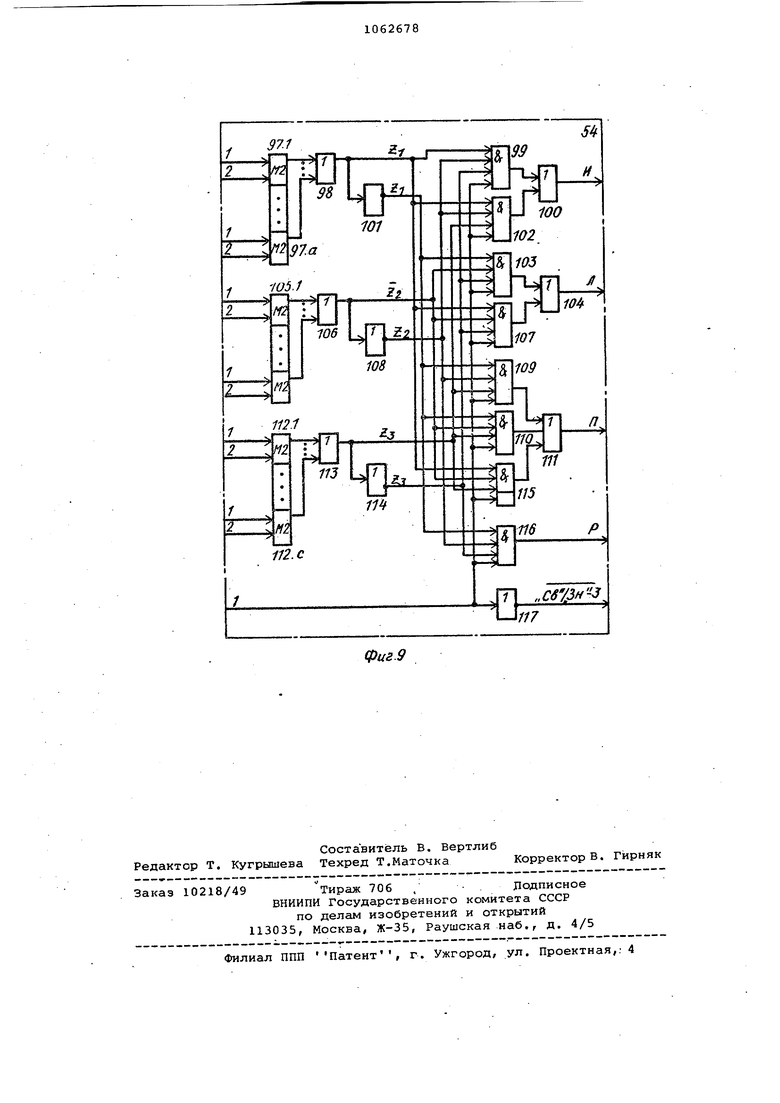

Третий узел 54 сравнения (фиг.9) содержит первую группу из Q элементов 97 сложения по модулю, два, первые элементы ИЛИ 98 и -И 99, второй элемент ИЛИ 100, первый элемент НЕ 101, второй и третий элементы И 102 и 103, третий элемент ИЛИ 104, вторую группу из К элементов 105 сложения по модулю два,четвертые элементы ИЛИ 106 и И 107, второй элемент НЕ 10ё и пятый и шестой элементы И 109 и 110 и пятый элемент ИЛИ 111, третью группу из с элементов 112 сложения, шестой элемент ИЛИ 113, третий элемент НЕ 114,седьмой и восьмой элементы И 115 и -116 ичетвертый элемент НЕ 117.

На первом узле 52 сравнения происходит сравнение первой, второй и третьей групп разрядов поля адреса получателя сообщения, принятого в п&иемный регистр 4, с соответствующими группами разрядов адреса данного канала 2 обмена и инвертирование значения поля признака занятости принятого сообщения.

В результате сравнения на элементах 55, 62 и 69 сложения формируются сигналы равенств а (х , х, х). и неравенства (Зс, х, Xj) сравниваемых групп разрядов адресов. На выходах первого узла 52 сравнения формируетс инвертированный сигнал значени я поля .признака занятости сообщения Св/ Зн -1 и по результатам проведенного сравнения формируется один из сигналов: .

А (Х.,Х,2,,Х, fXy ,Х-)}

Зн.1, означающий что адресуемый мо-. дуль 3 подключен к каналу 2 обмена, расположенному в строке матриц отличной от строки, в которой находится данный канал 2, и сообщение из при(емного регистра 4 необходимо передать в передающий регистр 6;

Б (х, ,Х2,х,+х ,х,х) Зн.1, означающий, что адресуемый модуль 3 подключен к каналу 2, расположенному в одноименной с данным каналом 2 матрице, но в другом столбце, и сообщение из приемного регистра 4 необходимо передать в передающий регистр 9 ;

В (х,х, ,Xy,Xj) Зн.1, означающий, что адресуемый модуль 3 подключен к каналу 2 обмена, расположенному в одноименной с данным каналом 2 строке других матриц, и сообщение из приемного регистра 4 необходимо передать в передающий регистр 12;

Г (х,(,х,х) Зн.1, означающий, что адресуемый модуль 3 подключен к данному каналу 2 обмена и сообщение из приемного регистра 4 необходимо передать в буферный регистр 15;

В приведенных вы1.ие соотношениях Зн.1 обозначает признак занятости принятого сообщения (единичный сигнал) . . .

Отсутствие всех сигналов А, Б, В, Г на выходах узла 52 сравнения означает, что принято сообщение Свободно .

На узле 53 сравнения происходит сравнение первой, второй и третьей групп разрядов поля адреса получателя сообщения, принятого в приемный регистр 7, с соответствующими группами разрядов адреса данного канала 2 обмена и инвертирование значения поля признака занятости принятого сообщения. В результате сравнения н элементах 76, 83 и 90 сложения формируются сигналы pasejicTBa (уу,у,,у8 и неравенства (у,у, сравниваемых групп разрядов адресов. На выходах узла 53 сравнения формируется инвертированный сигнал значения пол признака занятости сообщения Св / Зн-2 и по результатам проведенного сравнения на элементах 76, 83 . и 90 сложения формируется один из сигналов; Д (у, - У2 ) Зн.2, . означающий, что адресуемый модуль 3 подключен к каналу 2 обмена, расположенному в одноименном с данным каналом обмена столбце строк матриц отличныхОТ строки, в которой находится данный канал обмена, и сообще ние приемного регистра. 7 необходимо передать в передающий регистр 6; Е (у, у. у,. + У у) Зн.2, означающий, что адресуемый модуль 3 подключен к каналу 2 обмена, расположенному в столбце матриц, отличном от столбца, в кото ром находится данный канал 2, и соо щение из приемного регистра 7 необходимо передать в передающий регистр 9; Ж (у.у.у, + Ул У2 УЗ ) Зн.2, означающий, что адресуемый модуль 3 подключен к каналу 2 обмена, расположенному в одноименной с данным ка налом обмена строке матриц, но в другой матрице, и сообщение из прием ного регистра 7 необходимо передать в передающий регистр. 12; .3 ( у) Зн-.2, означающий, что адресуемый модуль 3 подключен к данному каналу 2 обмена и сообщение из приемного регистра 7 необходимо передать в буферный регистр 15.Здесь как и ранее, Зн.2 обозначает признак занятости принятого сообщения (единичный сигнал).. Отсутствие сигналов Д.Е,Ж.Зн. на выходах узла 53 означает, что принято сообщение Свободно. На узле 54 сравнения происходит, сравнение первой, второй и третьей групп разрядов поля адреса получателя сообщения, принятого в третий при емный регистр 10, с соответствующими группами разрядов адреса данного канала 2 обмена и инвертирование значе ния поля признака занятости принятого сообщения. В результате сравнения на элементах 97, 105 и 112 сложения формируются сигналы равенства ,5 и неравенства (S,,;,,) сравниваемых групп разрядов адресов. На выходах узла 54 формируется инвертированный сигнал значения поля занятости сообщения Св/Зн-3 и по результатам проведенного сравнения формируется один из сигналов И (Г,-2г2з - гv2:-г ) Зн.З, означающий, что адресуемый модуль 3 подключен к каналу 2 обмена, расположенному в одноименном с данным каналом 2 столбце строк матриц, отличных от строки, в которой находится данный канал 2, и сообщение из приемного регистра 10 необходимо передать в передающий регистр 6; Л ( .J + 5,) Зн.З, означающий, что адресуемый модуль 3 подключен к каналу 2 обмена, расположенному в столбце данной матрицы, отличном от столбца, в котором находится данный канал 2, и сообщение .из приемного регистра 10 необходимо передать в передающий регистр 9; . П (Zv 3 +Z, Z-}) Зн.. 3, означающий что адресуемый модуль 3 подключен к каналу 2 обмена, расположенному в матрицах, отличных от матрицы, в которой находится данный канал 2, и сообщение из приемного регистра 10 необходимо передать в передающий регистр 12; Р ( Zj-Zj) Зн. 3, означающий, что адресуемый модуль 3 подключен к данному каналу 2 и сообщение из приемного регистра 10 необходимо передать в буферный регистр 15. Параметр . Зн.З обозначает значение признака занятости принятого сообщения (единичный сигнал) . Отсутствие сигналив И, Л, П, Р на выходах третьего узла 54 означает, что принято сообщение Свободно П р и м е р. Пусть в канал 2 об мена (2.2.2.2) строки 2, столбца 2, матрицы 2 с адресом 2.2.2 поступают: в приемный регистр 4 - сообщение с адресом получателя 2.3.2 в приемный регистр 7 - сообщение с адресом получателя 2.1.3; в приемный регистр 10 - сообщение с адресом получателя 3.2.3. На выходах узла 52 сравнения присутствует сигнал Б (код 0100) и ну- левое значение сигнала Св/Зн -2,т.е. сообщение,принятое в приемный регистр 4, адресовано модулю 3, подключенному к каналу 2 (с адресом 2.3.2), расположенному в столбце 3 одноименной с данным каналом 2.2.2.2 обмена второй матрицы, и принятое сообщение необходимо передать в передающий регистр 9. На выходах узла 53 сравнения присутствует сигнал Ж (код 0010) и нулевое значение сигнала Св/Зн -1, т.е. сообщение,принятое в приемный регистр 7, адресовано модулю 3, подключенному к каналу 2 (с адресом 3.1.3), расположенному в одноименной с данным каналом 2.2.2,2 второй троке третьей матрицы 3, и принятое сообщение необходимо передать в тр тий . передающий регистр 12. На выходах узла 54 присутствует сигнал И () и нулевое знач ние сигнала Св /Зн-3, т.е. сообщение, принятое в приемный регистр 10, адресовано модулю 3, под ключенному к каналу 2 (с- адресом 3.2.3), расположенному в одноименн с данным каналом 2.2.2.2 обмена, вт ром столбце третьей строки третьей матрицы, и принятое сообщен1 е необ ходимо передать в передающий регистр б. После проведенного сравнения в блоке 17 на узлы 44 - 46 управлени блока 21 поступают соответственно коды 0100.1000.0 (сообщение из при ного регистра 4 необходимо передать в передающий регистр 9), 0010,0100 (сообщение из приемного, регистра 7 необходимо передать в передающий регистр 12) и 1000.0010.0 (сообщение из приемного регистра 10 необходимо передать в передающий регист 6). В результате в регистрах 51 уз лов -44 46 управления находятся соответственно коды 0010, 1000 и 0100. Это .означает, что на -выходы первого, второго и третьего мультиплексоров 5, 8 и 11 соответственно поступают сообщения с третьего, пер вого ивторого приемных«регистров 10) 4 и 7. Таким образом, сообщение с адресом получателя 2.3.2, принятое- в приемный регистр4 канала 2.2.2.2 в следующем такте передается в 2.2..3.2, сообщение с адресом получателя 2.1.3, принятое в приемный регистр 7 канала 2.2.2.2 - в канал 2-.2.2.3, а сообщение с адресо получателя 3.2,3, принятое в приемный регистр 10 канала 2.2.2..2 - в канал 2.3.2,2. Из блока 17. в узел 19 поступают сигналы г, 3, Р и инвертированные сигналы разрядов 7 полей Свободно/Занято сообщений, принятых соответственно в приемные регистры 4, 7 и 10. Из управляющего регистра 23 в узел 19 поступают сигналы: Т2, Т1, Т1 (где Т1 - состояние Занято соо,тветс: веннЬ триггера первог разряда; , Т2 - состояние Свободно триггеров первого и второго разрядов соответственно), Из узла 1 в управляющий регистр 23 поступают сйгна.лы: Уст, Т2, Уст .Т1,Уст .Т2 , Уст, Т1 (где Уст Т и Уст.Т - устано ка триггера разрядов регистра 2 в состояние Занято и Свободно соответственно), Из узла 19 в блок 21-поступают.сигналы: Уст,1, Уст.2 УСТ.З (где Уст,1, Уст.2 и Уст.З установка в единицу четвертого разряда регистров 51 управления узлов 44 - 46 соответственно), Из блока 21 Bji/зел 19 jiocTynaioT сигналы: IT, IT, 2Т, 2Т, ЗТ (где IT и IT - сосЗанятоСвободно тояние триггер 50 занятости узла 44 управления; Т2 и Т2 - состояние Свободно и Занято триггера 50 занятости узла 45; Зт - состояние Свободно триггера 5,0 занятости узла 46. Из распределителя 25 импульсов в узел 19 поступают сигналы СИ;4, СИ 1 и СИ 5, Из генератора 1 тактовых имп льсов в узел 19 поступает сигнал синхронизации. СИ, Из узла 19 поступают сигналы управления блоками 20, 22 и 24 элементов И, Из узла 19 в регистр 18 управления четвертым мультиплексором поступают сигналы: 1 Уст.18, 2 Уст,18, 3 Уст, 18 (сигналы установки в единицу соответственно первого, второго и третьего разрядов регистра 18). Из узла 19 в буферный регистр 15 посту-; пает сигнал Зп.Бр.2 (запись во второй буферный регистр 15). Из узла 19 в модуль 3 вычислительной системы поступают сигналы Принять и Зц- (запрос удовлетворен). Из модуля 3 вычи.слительной системы в узел 15 поступают сигналы Принят© и Зг5ер (Эапрос на передачу) , Из узла; 19 в буферный регистр 13 поступает- сигнал Зп, Бр.1 (запись в первый буферный регистр 131. Блоки 20, 22 и 24 элементов И (фиг.2) содержат по девяти элементов И и предназн,ачены для передачи информации, поступающей из блока 17, соответственно в первы.й, второй и третий узлы 44-46 управления блока 21. Блок 21 предназначен для выработки сигналов управления первым, вторым и третьим мультиплексорами 5, 8 и 11, Со счетчика 26 в блок 21 поступает сигнал Сч 1 (единица в старшем разряде счетчика). Из управлйющего регистра 23 в блок 21 поступает сигнал ТЗ (состояние Занято триггера .третьего разряда. Из блока 21 в третий, второй и первый мультиплексоры 11, 8 и 5 поступают сигналы управления мультиплексорами. Из распределителя 25 импульсов в блок 21 поступают сигна.71ы С 2 и С 3. Каждый узел управления управляет соответствующим его номеру мультиплексором, формат слова информации, принимаемого .на информационные входы входных регистров 47 и передаваемого между узлами 44 - 46, содержит следующие поля; поле Куда (4 разряда), поле От кого (4 разряда), поле Повторное сравнение (1 разряд). Поле Куда заполняется одним из кодов: 1000 (соответствует сигна лам А, д и И на выходах блока 17 и узлу 44); 0100 (соответствует сигна лам Б, Е, Л на выходах блока 17 узл 45); 0010 (соответствует сигналам В, Ж и П на ниходах блока 17 узлу 46); 0001 (соответствует сигналам Г 3 и Р на выходах блока 17). Поле От кого заполняется одним из кодов; 1000 (соответствуеь приемному регистру 4); 0100 (соответствует приемному регистру 7); 0010 (соответствует приемному регистру 10) . Из блока 20 на узел 44 поступает код ХХХХ.1000.0 (где ХХХХ - один из кодов Куда), из блока 22 на узел 45 поступает код ХХХХ.О100.О (где ХХХХ - один из кодов поля Ку да), а из блока 24 на узел 46 поступает код ХХХХ,0010.0 (где ХХХХ один из кодов поля Куда). Код 0000.0000.0 на выходах любого блока 20,22 и 24 означает, что сообщения, принятые в приемные регистры 4,7 и 10 соответственно, свободны или записываются в буферный регистр 15. На схему 49 с.равнения узла 44 посту пают значения первого и четвертого разрядов прля Куда (нумерация разрядов слева направо) и разряда поля Повторное сравнение формат слова информации. На схему 49 сравнения узла 45 поступают значения второго и четвертого разрядов поля Повторное и разряда поля сравнение формата .слова информации. На схему 49 сравнения узла 46 поступают значения третьего и четвертого разрядов поля Куда и разряда Повторное сравнение фор мата слова информации. Управляющий регистр 23 содержит три разрядных триггера: первый триг Свободно гер указывает состояние (Т1) и Занято (Т) буферного реГистра 13; второй триггер указывает состояние Свободно (Т2) и Занято (Т2) буферного регистра 15, третий триггер управляет информацио ными входами входных регистров 47 узлов 44 - 46 управления (состояние Занято - ТЗ - прием с второго информационного входа, состояние Свободно - ТЗ - прием с первого информационного входа, т.е. с выхода предыдущего узла управления). Распределитель 25 импульсов пред назначен для формирования по каждом сигналу СИ, вырабатываемому генератором 1 сигналов: СИ1, СИ2, СИЗ, СИ4 и СИ5. Счетчик 26 является трех разрядным счетчиком и предназначен для управления работой блока 21. В качестве модулей 3 вычислительной системы могут использоваться процессоры, блоки памяти и т.д. Устройство работает следующим образом. В исходном состоянии всё разряды управл5пощего регистра 23 и триггеры 50 узлов 44 - 46 находятся в состоянии Свободно. По пуску устройства генератор 1 начинает вырабатывать серию сигналов СИ, под управлением которых между каналами 2 начинают циркулировать информационные сообщения. По каждому сигнсшу СИ в приемные регистры 4, 7 и 10 записываются сообщения с соответствующих информационных входов канала 2. обмена. По .каждому сигналу СИ третий разряд управляющего регистра 23 устанавливается в состояние Занято (ТЗ), триггеры 50 узлов 44-46 уста1 5вливаются в состояние Свободно (IT, 2Т, ЗТ), регистры 18 и 51 и счетчик 26 обнуляются. . По каждому сигналу СИ распределитель 25 вырабатывает следующие сигналы: СИ1, который предназначен для разрешения формирования сигналов Зп.Бр.2, Принять и УСТ.Т2; СИ2 и СИЗ - две серии сигналов по шесть сигналов в каждой, предназначенные для работы блока 21. По каждому сигналу СИ2 происходит запись слова информации во входные регистры 47 узлов 44 - 46, а по сигналу СИЗ - перепись этих слов информации в выходные регистры 48 узлов 44 - 46. Также по первому сигналу СИ2 триггер третьего разряда управляющ его регистра 23 устанавливается в состояние Свободно (Т2) и в по каждому сигналу СИ2 происходит добавление единиц в счетник 2G; СИ4, предназначенный для разрешения формирования сигналов Уст.1 Уст.2 и Уст.З; СИ5, предназначенный для р решения формирования сигнала Уст.Т1.По этому сигналу происходит также запись сообщений с выходов мультиплексоров 5, 8 и 11 в соответствующие передающие регистры 6, 9 и 12. . Работа канала 2 обмена осуществляется с помощью следующих основных операций. Запись в приемные регистры 4, 7 и 10 (ЗП.ПР.РГ). По сигналу СИ. в приемные регистры записываются сообщения с соответствующих информационных входов канала 2 т.п.к. обмена. Запись в буферный регистр 13(ЗП. БР1). В буферный регистр 13 записывается сообщение (адрес получателя, данные) с соответствующего информационного входа канала и адрес отправителя из регистра 16 адреса, разряд поля занятости сообщения устанаявлиBaetCH в единицу (Занято), пер вый; разряд управляющего регистра 2 устанавливается в состояние Заня то (Т1) и в модуль 3 вычислитель ной системы пошылается сигнал Зуд Запись в буферный регистр 15(ЗП.БР2). В буферный регистр 15 записывается сообщение (адрес отпр вителя, данные) с выхода мультиплек сора 14, второй разряд управляющего регистра 23 устанавливается в состо ние Занято 4,7 и 10 модуль 3 вы числительной системы посы 1ается сиг нал Принять- i Запись в передающие регистры б, и 12 (ЗП.ПЕР.РГ). В передающие регистры 6, 9 и 12 по сигналу СИ5 зап сываются сообщения с выходов мульти плексоров 5, 8 и 11. Сравнение адресов (СР.АДР). Посл исполнения операции ЗП.ПР.РГ в блоке 17 происходит сравнение адресов ,получателей принятых сообщений с адресом данного канала 2 т.п.к обмена. Сортировка (СОРТ), После выполнения операции СР.АДР и возможного исполнения операции ЗП.БР2 происходит прием слов информации из блока 17 в узлы 44 - 4G и выработка сигна лов управления мультиплексорами 5, 8 и 11,. Операция СОРТ выполняется в два этапа. Па первом этапе по первым сигналам СИ2 и СИЗ происходит обработка слов информации на установку прямых связей для передачи сообщений из приемных регистров 4,7 и 10, в. передающие регистры 5, 8 и 11. На втором этапе по вторым, третьим, четвертым, пятым и щестым сигналам СИ2 и СИЗ происходит обработка слов информации на установку перекрестных связей для передачи сообщений из приемных регистров 4,7 и 10 в передающие регистры 5, 8 и 11. канал 2 т.п.к. обмена . работает в трех режимах: Чтение Передача, Запись . Чтение предназначен для приема сообщений, адресованных данному каналу 2 т.п.к. обмена и пе редачи их модулю 3 т.п.к. вычислительной системы. При этом выполняют ся операции ЗП.ПР.РГ и СР.АДР. После выполнения операции СР.АДР может выработаться один из cигнaлoвJ Уст.18 Г.Т2; Уст. .З.Т2; Уст. 18 Г.З.Р.Т2. Если сигналы отсутствуют, выраба тываются сигналы для управления бло ками 20, 22 ц 24 элементов И. После выработки сигналов 1Уст. ЗУст.18 в 2УСТ.18 регистре 18 находится один из следу щих кодов: 100 - означает, что через мультиплексор 14 проходит сообщение из приемного регистра 4; i3lO означает, что через мультиплексор 14 проходит сообщение из приемного регистра 7; 001 - означает, что через мультиплексор 14 проходит сообщение из приемного регистра 10, По сигналу СИ1 и при наличии одного из сигналов 1Уст.18,2Уст. ЗУст.18 выполняется операция ЗП.БР.2. По сигналу Принять модуль 3 т.п,к, вычислительной системы переписывает на свои рез1 истры сообщение из буферного регистра 15 и формирует сигнал Принято. По сигналу СИ из генераогора 1 и сигналу Принято формируется сигнал Уст.Т2, по которому второй разряд управляющего регистра 23 п ереходит в состояние Свободно (Т2). ,Режим Передача предназначен для перераспределения сообщений, принятых в приемные регистры 4,7 и 10 и не- -переданных в буферный регистр 15, между первым, вторым и третьим передающими регистрами б, 9 и 12. При этом последовательно выполняются операции ЗП.ПР .РГ, СР.АДР, вырабатываются сигналы управления блоками 20, 22 и 24 элементов И, что описано в режиме Чтение, затем выполняется операция СОРТ следующим -образом. По первому сигналу СИ2 и состоянию Занято (ТЗ) третьего разряда У ря вляющего регистра 23 происходит (тЗ) третье гр разряда прием слов информации во входные регистры 47 узлов 44 - 4.fj с выходов соответствующих блоков 20,- 22 и 24 элементов И. По первому сигналу СИ2 третий разряд управляющего регистра 23 переходит в состояние Свободно (ТЗ), которое обеспечивает переключение информационных входов входных регистров 47, в счетчик 26 добавляется единица. По сигналу СИЗ происходит передача -слов информации из входных регистров 47 в выходные передающие регистры 48. Если в принятом слове информации разряд поля Куда, соответствующий номеру данного узла (первому, второму или третьему) управления, равен единице и триггер 50 на годится в состоянии Свободен (IT, 2Т, ЗТ), то схема 49 сравнения вырабатывает сигнал Сбр. Пер .Р)г , по которому, выходной регистр 48 обнуляется, сигнал Уст.Т, по которому триггер 50 переходит в состояние.Занято (IT, 2Т, ЗТ) и сигнал Зп.РУ, по которому в регистр 51 записывается значение поля От кого слова информации. Если в принятом слове информации разряд поля Куда, соответствующий номеру данного узла (первому. второму или третьему), равен единиц и триггер 50 находится в состоянии Занято (1Т,2Т,ЗТ), то схема 49 сравнения вырабатывает сигнал Уст ПС, поступающий в выходной регист 48, по которому разряд поля Повторное с авнение слова информаци устанавливается в единицу. По вторым и третьим сигналам СИ2 и СИЗ происходят действия, аналогич ные, описанным .выше, отличающиеся лишь тем, что слова информации в уз лы 44 - 46 принимаются с первых информационных входов. По четвертым сигналам СИ2 и СИЗ происходит прием слов ийформации во Входные регистры 47 и передачи их в выходные регистры 48. По сигналу СИ2 в счетчик 26 добавляется единица (триггер старшего разряда устанавливается в единицу). Если в принятом слове информации четвертый разряд поля Куда или разряд поля Повторное сравнение равны единице (единица в четвертом разряде поля Куда означает, что сообщение, принятое в передающий регистр 4, 7 или 10 и адресованное данному каналу 2 обмена,.не записывается в буферный регистр 15) и триггер 50 нaxoдитcяJв состоянии Свободен (1Т,2Т,ЗТ), то по единичному состоянию триггера старшего разряда счетчика 26 схема 49 сравне ния вырабатывает сигналы Сбр.Пер, Рг, Уст.Т и Зп.РУ, по которым выполняются действия, аналоги ные описанным выше. По пятым и шестым, сигналам СИ2 и СИЗ происходят действия, аналогичные описанным выше по четвертым сиг налам СИ2 и СИЗ. В результате операции СОРТ в регистрах 51 находятся коды полей От.кого, по которым на выходы мультиплексоров 5, 8 и 11 поступают сообщения с первого, второго или третьего информационных входов. После операции СОРТ выполняется операция ЗП.ПЕР.РГ. Запись предназначен для приема сообщений из модупя 3 и передачи их в один из передающих регистров 6, 9 и 12 и выполняется в следующей последовательности. Когда модулю 3 необходимо перег дать сообщение, он посылает сигнал выставляет сообщение (адрес получателя, данные) на своем информационном выходе. По сигналу СИ из генератора 1, состоянию Свободно (Т1) первого разряда управляющего регистра 23 и сигналу Зпер выполняется операция ЗП.ЁР.1. При получении сигналаЗцд модуль 3 .снимает сигнал 3пер и сообщение со своего информационного выхода. На данном этапе выполняются также операции ЗП.ПР.РГ, СР.АДР, СОРТ. После выполнения операции СОРТ в зависимости от состояний триггеров 50 вырабатывается один из сигналов; УСТ.1 :,1Т.Т1.СИ42 Уст.2 - 1Т.2Т.Т1. СИ4; Уст.З - 1Т.ЗТ.Т1.СИ4.Т2. В результате данного этапа в одHQM из регистров 51 находится код 0001, означающий, что на выход соответствующего мультиплексора поступает сообщение с третьего информационного входа. Затем выполняется операция ЗП.ПЕР.РГ. По сигналу СИ5 и одному из сигналов Уст.1, Уст.2 и .З вырабатывается сигнал Уст.Т -. Таким образом, каждый канал обмена устройство может работать одновременно во всех трех режимах, что обеспечивает более высокую пропускную способность за счет сокращения путей обмена сообщениями между модулями вычислительной системы и увеличения числа возможных путей продвижения сообщений. 3.1.1 Л

0uS.f З.М.1.К

.2

фиг Л

фиг. 6

фив.8

Фиг.9

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3313515/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-23—Публикация

1982-03-23—Подача