ния временньгх битов и битов данных, информационный вход которого соединен с выходом первого 7риггера блока вьтеления временных битов и битов данных вход установки в ноль которого соединен с первым выходом блока синхронизации и входом сдвига регистра сдвига, информационный вход которого сое динен с выходом второго триггера блока вьщеления временных битов и битов данных, вход синхронизации которого соединен с первым входом синхронизации блока вьщеления идентификаци символа и вторым выходом блока синхронизации, третий выход которого соединен с вторым входом синхронизации блока вьщеления и идентификации символа и с первым входом установки в единицу первого триггера блока вьщеления временных битов и битов данных, второй вход установки в единицу которого соединен с информационным входом устройства и входом запуска блока синхронизации, четвертый и пятый выходы которого соединены соответственно с третьим и четвертым входами синхронизации блока вьщеления и идентификации символа, отличающееся тем, что, с целью увеличения быстродействия за счет обеспечения возможности оперативного изменения информации в памяти микропрограмм, оно дополнительно содержит коммутатор данных, блок памяти, счетчик адреса памяти,регистр данных памяти, блок управления памятью, содержащий шесть триггеров, девять элементов И, пять элементов ИЖ, элемент НЕ, счетчик и генератор импульсов и блок связи с процессором, содержащий четыре триггера, четыре элемента И и коммутатор, выход которого соединен с входом установки в единицу первого триггера блока связи с процессором, выход которого соединен с первыми входами первого, второго и третьего элементов И блока связи,с процессором и с выходом управления началом загрузки процессора устройства, второй вход первого элемента И блока связи с процессором соединен с нулевым выходом второго триггера блока связи с процессором, информационный вход которого соединён с выходом первого элемента И блока связи с процессором, входы синхронизации второго и третьего триггеров

9019

блока связи с процессором соединены с вторыми входами второго и третьего элементов И блока связи с процессором и входом синхронизации устройства, третий вход второго элемента И блока связи с процессором соединен с единичным выходом третьего триггера блока связи с процессором, нулевой выход и информационный вход которого соединены с третьим входом третьего элемента И блока связи с процессором, вьосод которого соединен с первьм входом первого элемента ИЛИ блока управления памятью,выход второго элемента И блока связи с процессором соединен с выходом управления передачей данных устройства, единичный выход второго триггера, блока связи с процессором соединен с jiepBbiM входом второго элемента ИЛИ блока управления памятью, первый и второй информационные входы коммутатора блока связи с процессором соединены соответственно с входом начальной установки режима работы устройства и с выходом четвертого элемента И блока связи с процессором, первьй и второй входы которого соединены соответственно с выходом переполнения счетчика символов и с выходом четвертого триггера блока связи с процессором, информационный вход и вход синхронизации которого соединены соответт ственно с информационным выходом регистра сдвига и с четвертым управляющим выходом блока вьщеления и идентификации символа, управляющий вход коммутатора блока связи с процессором соединен с входом признака ручного режима устройства, с управляющим входом коммутатора данных и с первыми входами первого, второго и третьего элементов И блока управления памятью, вход установки в ноль четвертого триггера блока связи с прицессором соединен с выходом переполнения счетчика адреса, памяти, вход записи регистра данных памяти соединен с вькодом четвертого элемента И блока управления памятью, первый прямой вход которого соединен с выходом третьего элемента ИЛИ блока управления памятью, с информационным входом первого триггера блока управления памятью и вторым входом второго элемента ИЛИ блока управления памятью, выход которого соединен с инверсным входом четвертого элемента ИЛИ блока управления памятью и входом синхронизации второго триггера блока управления памятью, выход которого соединен с входом установки в ноль третьего триггера блока .управления памятью и с прямым вхо;дом четвертого элемента ИЛИ блока I управления памятью, выход которого 1 соединен с первым входом пятого элемета И блока управления памятью, второй вход которого соединен с нулевым выходом третьего триггера бло управления памятью, информационный вход которого соединен с выходом генератора импульсов блока управления памятью, с информационными входами четвертого, пятого и шестого триггеров блока управления памятью и чере элементы НЕ блока управления память с информационным входом второго триггера блока управления памятью, вход установки в единицу которого .соединен с выходом шестого элемента И блока управления памятью и с входами установки в ноль четвертого и пятого триггеров блока управления памятью, выход пятого элемента И блока управления памятью соединен с входом установки в ноль счетчика блока управления памятью, счетньй вход которого соединен с шестым выходом блока синхронизации, с вторым прямым входом четвертого элемента И блока управления памятью и с первыми прямыми входами шестого, седьмого и восьмого элементов И блока управления памятью, первый информационный выход счетчика блока управления памятью соединен с первыми инверсными входами четвертого и восьмого элементов И блока управления памятью и с вторыми прямыми входами шестого и седьмого элементов И блока управления памятью, второй информационньй выход счетчика блока управления памятью соединен с третьим прямым входом четвертого элемента И блока управления памятью, с вторь1ми инверсными вхо;дами седьмого и восьмого элемен:Тов И блока управления памятью и с инверсным входом шестого элеменiта И блока управления памятью, тре:тий информационньй выход счетчика блока управления памятью соединен с вторыми инверсными входами четвертого и седьмого элементов И блока управления памятью, с вторым прямым входом восьмого элемен019

. та И блока управления памятью и третьим прямым входом шестого элемента И блока управления памятью, выход седьмого элемента И блока управления памятью соединен - с входами синхронизации первого, третьего и шестого триггеров блока управления памятью, выход восьмого элемента И блока управления памятью соединен с входами установки в ноль первого и шестого триггеров блока управления памятью и с первым входом девятого элемента И блока управления памятью, второй вход которого соединен с пятым управляющим выходом Ъпо ка вьделения и идентификации символа и с первьм входом третьего элемента ИЛИ блока управления памятью, второй вход которого соединен с выходом пятого триггера блока управления памятью, вход синхронизации которого соединен с выходом второго элемента И блока управления памятью, второй вход которого соединен с входом управления записью символа устройства и первым входом пятого элемента ИЖ блока управления памятью, второй вход которого соединен с входом управления считыванием символа устройства и с вторым входом третьего элемента И блока управления памятью, выход которого соединен с входом синхронизации четвертого триггера блока управления памятью, выход которого соединен с третьим вхрдом второго, элемента ИЛИ блока управления памятью, выход девятого элемента И блока управления памятью соединен с вторым входом первого элемента ИЛИ блока управления па.мятью, выход которого соединен с счетным входом счетчика адреса т мяти, выходы первого и шестого триггеров блока управления памятью соединены соответственно с входом записи блока памяти и входом чтения блока памяти, выход пятого элемента ИЛИ блока управления памятью соединен с вторым входом первого элемента И блока управления памятью, выход которого соединен с входом разрешения записи счетчика адреса памяти, информационньй выход которого соединен с адресным входом блока.памяти, информационный вход которого соединен с выходом коммутатора данных, первый и второй информационные входы которого соединены соответственно с - входом данных устройства и с выходом регистра данных, информационный вход счетчика адреса памяти соединен с входом адреса данных устройства,выход памяти через регистр данных соединен с информационным выходом устройства, причем блок вьщеления и идентификации символа содержит три триггера, семь элементов И и элемейт ИЛИ-НЕ, первый вход которого соединен с первыми входами первого, второго и третьего элементов И и с единичным выходом первого триггера, нулевой выход которого соединен с первым входом четвертого элемента И, выход которого соединен с информационным входом второго триггера, единичный выход которого соединен с первым входом пятого элемента И, вторым входом элемента ИЛИ-НЕ и с первьм входом установки в единицу первого триггера, второй вход установки в единицу которого соединен с третьи входом синхронизации блока и с первым входом шестого элемента И, второй вход которого соединен с вторыми входами первого, второго и пятого элементов И, с выходом третьего триггера и вторым входом четвертого элемента И, вход синхронизации второго триггера соединен с третьими входами второго и пятого элементов И и вторым входом синхронизации блока, нулевой выход второго триггера соединен с вторым входом третьего элемента И,- третий вход которого соединен с третьим управляющим выходом блока, с выходом шестого элемента И и с первым входом седьмого элемента И, второй вход и выход которого соединены соответственно с выходом элемента ИЛИ-НЕ и с первым управляющим выходом блока, третий вход первого элемента И соединен с четвертым входом синхронизации блока и входом синхронизации третьего триггера, информационный вход которого Ьоединен с информационным входом блока, вход установки в ноль третьего триггера соединен с первым входом синхронизации блока, третий вход четвертого элемента И и вход установки в ноль первого триггера соединены соответственно d первым управляющим входом блока и входом сброса блока,второй,четвертьй и пятые управляющие вькоды блока соединены соответственно с выходом второ1ГО элемента И,с выходом пятого элеiмента И и с выходом третьего элемен9019

та И, выход первого элемента И с5единен с выходом вьщеления символов блока,

2. Устройство по п.1, отличающееся тем, что блок синхронизации содержит десять элементов И, четыре триггера, два генератора импульсов, элемент ИЛИ и счетчик, первый информационный выход которого соединен с первым инверсным входом первого элемента И, с первыми прямыми входами второго, третьего и четвертого элементов И и с инверсным входом пятого элемента И, второй информационный выход счетчика соединен с вторым инверсным входом первого элемента И с первым инверсным входом второго элемента И, с вторыми прямыми входами третьего и четвертого элементов И, с инверсным входом шестого элемента И, и с первым прямым входом пятого элемента И, выход которого соединен с четвертым выходом блока, третий информационньй выход счетчика соединен с третьим инверсным входом первого элемента И, с вторым инверсным входом второго элемента И, с инверсным входом третьего элемента И, с прямым входом шестого элемента И, с вторым прямым входом пятого элемента И и с третьим прямым входом четвертого элемента И, выход первого генератора импульсов соединен с входом синхронизации первого триггера, с прямым входом первого элемента И, с вторым прямым входом второго элемента И и с третьим прямым входом пятого элемента И, с инверсными входами четвертого и седьмого элементов И и с первыми входами восьмого, девятого и десятого элементов И, второй вход десятого элемента И соединен с выходом первого триггера, входы установки в ноль и в единицу которого соединены с выходом второго генератора импульсов, первый прямой вход седьмого элемента И соединен с нулевым выходом второго триггера, единичный выход которого соединен с входом установки в единицу третьего триггера, единичный и нулевой выходы которого соединены соответственно с вторым входом восьмого элемента И и с вторьм входом девятого элемента И, выход которого соединен с входом установки в единицу счетчика, счетный вход которого соединен с выходом

восьмого элемента И и с входом установки в ноль четвертого триггера, нулевой выход которого соединен с входом установки в ноль второго триггера, цервьй вход установки в единицу которого соединен с вторым выходом блока, с единичным выходом четвертого триггера и с вторым прямым входом седьмого элемента И, выход KOTopforo соединен с входом установки в ноль третьего триггера, выход четвертого элемента И соединен с входом установки в единицу

четвертого триггера, выходы третьего и шестого элементов И соединены соответственно с первым и вторым вхо дами элемента ИЛИ, выход которого соединен с третьим вькодом блока« второй вход установки в единицу второго триггера соединен с входом запуска блока, парный, пятый и шестой выходы блока соединены соответственно с выходом первого элемента И, с выходом второго элемента И и с выходом десятого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления загрузкой микропрограмм | 1983 |

|

SU1136175A2 |

| Устройство управления загрузкой микропрограмм | 1982 |

|

SU1042025A1 |

| Устройство для запоминания состояний процессора | 1985 |

|

SU1278858A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для орфографического контроля текстов | 1985 |

|

SU1278851A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Микропрограммное устройство управления | 1984 |

|

SU1262516A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

УСТРОЙСТВО УПРАВЛЕНИЯ ЗАГРУЗКОЙ МИКРОПРОГРАММ, содержащее блок вьделения временных битов и битов данных, содержащий первый и второй триггеры, блок синхронизации, регистр сдвига, регистр данных,блок вьщеления и идентификации символа, счетчик символов, счетчик адреса дорожки и блок управления движением головки, содержащий первый и втор.ой элементы И, первый и второй триггеры и схему сравнения, первый и второй выходы неравенства которой соответственно подключены к первому входу первого элемента И блока управления движением головки и к первому входу второго элемента И блока управле- ния движением головки, второй вход которого соединен с вторым входом первого элемента И блока управления движением головки и первым управляющим входом блока вьделения и идентификации символа, выходы первого и второго элементов И блока управления движением головки соединены соответственно с входом установки в единицу первого триггера блока управления движением головки и входом установки в единицу второго триггера блока управления движением головки, вход установки в ноль которого соединен с входом установки в ноль первого триггера блока управления движением головки и входом начала дорожки устройства, выходы первого и второго триггеров блока управления движением головки соединены соответственно с первым и вторым выходами управления внешним накопителем дорожек устройства, выход равенства схемы сравнения соединен с первым управляющим входом блока выделения и чцентификации символа, первый и второй информационные входы схемы сравнения соединены (Л соответственно с информационным выходом регистра сдвига и с информас ционным выходом счетчика адреса дорожки, информационный вход которого § соединен с входом начального адреса дорожки устройства, счетный вход счетчика адреса дорожки соединен с выходом переполнения счетчика символов CD и входом сброса блока вьщеления и о идентификации символа, счетный вход счетчика символов соединен с выходом выделения символа блока вьщёления и со идентификации символа, второй управляющий выход которого соединен с входом записи регистра данных, информационный вход которого соединен с информационным вькодом регистра сдвига, выход старшего разряда которого соединен с информационным входом блока вьщеления и идентификации символа, третий управляющий выход которого соединен с входом, начальнойустановки регистра сдвига и входом установки в ноль второго триггера блока вьщеле

Изобретение относится к области вычислительной техники и может быть применено для отладки микропрограммной ЭВМ. Известно устройство, содержащее сдвигающий регистр, сепаратор,счетчик байтов 1 . Недостаток устройства - невозмож ность его использования для загрузки микропрограмм в процессор, так как информация, считанная с пультов го накопителя, может использоваться только для диагностических и сервис ных функций. Известно также устройство, содержащее регистр данных накопителя, регистр данных, счетчик символов и сепаратор С2 1. Недостатком этого устройства flBJtflfotcH избыточные затраты оборудо вания, связанные с реализацией возможности модификаций адреса дорожки на произвольную величину, а с наличием сложного оборудования дл определения конца массива данных н окончания процесса загрузки.Кроме того,избыточные затраты оборудования требуются для идентификации счи ваемой с носителя информации и для реализации довольно сложного алгоритма связи этого устройства с процессоромНаиболее близким к предложенному является устройство управления загрузкой микропрограмму содержащее блок вьтеления временных битов и битов данных, содержащий первый и второй триггеры, блок синхронизации регистр сдвига, регистр данных, бло вьделения и идентификации символа, счетчик символов, счетчик адреса Дорожки и блок управления движением головки, содержащий первый и второй элементы И, первый и второй триггеры и схему сравнения, первый и второй выходы неравенства которой соответственно подключены к первому входу первого элемента И блока управления движением головки и к первому входу второго элемента И блока управления движением головки,второй вход которого соединен с вторым входом первого элемента И блока управления движением головки и первым Управляющим входом блока вьщеления и идентификации символа, выходы первого и второго элементов И блока управления движением головки соединены соответственно с входом установки в единицу первого триггера блока управления движением головки и входом установки в единицу второго триггера блоки ущ авлен1ет движением головки, вход установки в ноль которого соединен с входом установки в ноль первого триггера блока управления движением головки и входом начала дорожки устройства, выходы, первого и второго.триггеров блока управления движением головки соединены соответственно с и вторым выходами управления внешним накопителем дорожек устройства, выход равенства схемы сравнения соединен с первым управляющим входом блока выделения и идентификации символа, первый и второй информационные входы схемы сравнения соединены соответственно с информационным выходом регистра сдвига и информационным выходом счетчика адреса дорожки, ин формационный вход которого соединен с входом начального адреса дорожки устройства, счетный вход счетчика адреса дорожки соединен с выходом переполнения счетчика символов и входом сброса блока ньделения и идентификации символа, счетный вход счетчика символов соединен с выходо вьделения символа блока ввделения и идентификации символа, второй управлянлций выход которого соединен с входом записи регистра данных, информационный вход которого соединен с информационным выходом регистра сдвига, выход старшего разряда кото рого соединен с информа1щоннь м вход блока вьделенил и идентификации сим вола, третий управляюп1ий выход кото рого соединен с входом начальной установки регистра сдвига и входом установки в ноль второго триггера блока вьделения временных битов и битов данных, информационный вход которого соединен с выходом первого триггера блока вьделения временных бит и битов данных, вход установки в ноль которого соединен с первьм выходом блока синхронизации и входом сдвига регистра сдвига, инфо мационный вход которого соединен с выходом второго триггера блока вьще ления временных битов и битов данных, вход синхронизации которого соединен с первым входом синхронизации блока вьщеления и идентификации символа и вторым выходом блока синхронизации, третий выход которого соединен с вторым входом синхронизации блока вьщеления и идентификации СИМВОЛА и первым входом установки в единицу первого триггера блока вьделения временных битов и битов данных, второй вход установки в единицу которого соединен с ин формационным входом устройства и входом запуска блока синхронизации, четвертый и пятый выходы которого соединены соответственно с третьим и четвертым входами синхронизации блока вьдепения и идентифик ции символа СзЗ. Недостаток этого устройства - не возможность оперативного изменения информации в памяти микропрограмм, что значительно замедляет процесс наладки ЭВМ, так как исправленную микропрограмму необходимо записать на внешний носитель (пультовой диск) и лишь затем ее можно ввести в память микропрограмм ЭВМ. Цель Изобретения - повьшение быстродействия устройства путем возможности оперативного изменения микрокоманд в памяти микропрограмм ЭВМ, что значительно ускорит процесс наладки ЭВМ, так как отпадает необходимость записи исправленной микропрограммы на внешншЧ носитель (пультовый диск). Поставленная цель достигается тем, что в устройство управления загрузкой микропрограмм, содержащее блок вьделения временных битов и битов данных, содержащий первый и второй триггеры, блок синхронизации, регистр сдвига, регистр данных,блок вьделения и идентификации символа, счетчик символов, счетчик адреса дорожки и блок управления движением головки, содержащий первьй и второй элементы И, первый и второй триггеры и схему сравнения, первый и второй вькоды неравенства которой соответственно подключены к первому входу первого элемента И блока управления движением головки и первому входу второго элемента И блока управления движением головки второй вход которого соединен с вторым входом первого элемента И блока управления движением головки и первым управляющим входом блока, вьщеления и идентификации символа, выходы первого и второго элементов И блока управления движением головки соединены соответственно с входом установки в единицу первого триггера блока управления движением головки и входом установки в единицу второго триггера блока управления движением головки, вход установки в ноль которого соединен с входом установки в ноль первого триггера блока управления движением головки и входом начала дорожки устройства, выходы первого и второго триггеров блока управления движением головКи соединены соответственно с первым и вторым выходами зтфавления внешним накопителем дорожек устройства,выход равенства схемы сравнения соедийен с первым управляющим входом блока вьделения и идентификации символа.

5

первый и второй информационные входы схемы сравнения соединены соответственно с информационным выходом регистра сдвига и с информационным выходом счетчика адреса дорожки, информационный вход которого соединен с входом начального адреса дорожки устройства, счетный вход счетчика адреса дорожки соединен с выходом переполнения счетчика символов и входом сброса, блока вьделения и идентификации символа, счетный вход счетчика символов соединен с выходом вьщеления символа блока вьделения и идентификации символа, второй управляющий выход которого соединен с входом записи регистра данных, информационный вход которого соединен с информационным выходом регистра сдвига, выход старшего разряда которого соединен с информационньм вхо дом блока вьщеления и идентификации символа, третий управляющий выход которого соединен с входом начальной установки регистра сдвига и входом установки в ноль второго триггера блока вьщеления временных битов и битов данных, информационньй вход которого соединен с выходом первого триггера блока вьщеления временных битов и битов данных, вход установки в ноль которого соединен с первым выходом блока синхронизации и входом сдвига регистра сдвига, информационный вход которого соединен с выходом второго триггера блока вьщеления временных битов и битов данных, вход синхронизации которого соединен с первым входом синхронизации блока вьщеления и идентификации символа и вторым выходом блока синхронизации, третий выход которого соединен с BTopbiM входом синхронизации блока вьщеления и идентификации символа и с первым входом установки .в единицу первого триггера блока вьщеления временных битов и битов данных,второй вход установки в единицу которого соединен с информационным входом устройства и вхсздом запуска блока синхронизации, четвертый и пятый выходы которого соединены соответственно с третьим и четвертью входами синхронизации блока вьщеления и идентификации символа, введены коммутатор данных, блок памяти, счетчик аг-реса памяти, регистр данных памяти, блок управления памятью, содержащий

19019 , 6

шесть триггеров, девять элементов И, пять элементов КПИ, элемент НЕ,счетчик и генератор импульсов и блок связи с процессором, содержащий четыре 5 триггера, четыре элемента И и коммутатор , выход которого соединен с входом установки в единицу первого триггера блока связи с процессором, выход которого соединен с первыми входами первого, второго и третьего элементов И блока связи с процессором и с выходом управления началом загрузки процессора устройства, второй вход первого элемента И блока связи с процессором соединен с нулевьм выходом второго триггера блока связи с процессором, информационный вход которого соединен с выходом первого элемента И блока связи с процессором, входы синхронизации второго и третьего триггеров блока связи с процессором соединены с.вторыми входами второго и третьего эле|Ментов И блока связи с процессором и входом синхронизации устройства,третий вход второго элемента И рлока связи с процессорном соединен с единичным выходом третьего триггера блока связи с процессором, нулевой выход и информациониьй вход которого соединены с третьим входом третьего элемента И блока связи с процессором, выход которого соединен с первым входом первого элемента ИЛИ блока управления памятью, выход второго элемента И блока связи с процессором соединен с выходом управления передачей данных устройства,, единичный выход второго триггера блока связи с процессором соединен с первым входом второго элемента И.ПИ блока управления памятью, первьй и второй информационные входы коммутатора блока связи с процессором соединены соответственно с входом начальной . установки ручного режима работы устройства и с выходом четвертого элемента И блока связи с- процессором, первый и второй входы которого соединены соответственно с выходом переполнения счетчика символа и с выходом четвертого триггера блока связи с процессором, информационный вход и вход синхронизации которого соединены соответственно с информационным выходом регистра сдвига и с четвертым управляющим выходом блока ныщеления и идентифика1р1и символа, управляю щий вход ком:-гут с ор а блока спязи с процессором соединен с входом признака ручного режима устройства, с управляющим входом коммутатора данных и с первьми входами первого, втброго и третьего элементов И блока управления памятью, вход установки в ноль четвертого триггера блока связи с процессором соединен с выходом переполнения счетчика адреса памяти, вход записи регистра данных памяти соединен с выходом четвертого элемента И блока управления памятью, первый прямой вход которого соединен с выходом третьего элемента ИЛИ бло ка управления памятью, с информацион ньм входом первого триггера блока управления памятью и вторым входом второго элемента ИЛИ блока управления памятью, выход которого соединен с инверсрым входом четвертого элемента ИЛИ блока управления память и входом синхронизации второго триггера блока управления памятью, выход которого соединен с входом установки в ноль третьего триггера блока управления памятью и с прямым входом четвертого элемента ИЛИ блока з правления памятью, выход которого соединен с первым входом пятого элемента И блока управления памятью, второй вход которого соединен с нулевым выходом третьего триггера блока управления памятью, информационный вхо которого соединен с выходом генерато ра импульсов блока управления памятью, с информационными входами четвертого, пятого и шестого триггеров блока управления памятью и через элемент НЕ блока управления памятью с информационным входом второго, триггера блока управления памятью, вход установки в единицу которого соединен с выходом шестого элемента И блока управления памятью и входами установки в ноль четвертого и пятого триггеров блока, управления памятью, выход пятого элемента И блока управления памятью соединен с входом установки в ноль счетчика блока управления памятью, счетньй вход которого соединен с шестым выходом блока синхронизации, вторым прямым входом четвертого элемента И блока управления, памятью и с пе выми прямыми входами шестого, седьмого и восьмого элементов И и блока управления памятью,первьй информационный выход счетчика блока управления памятью соединен с первыми инверсными входами четвертого и восьмого элементов И блока .управления паг/атъюп вторыми прямыми входами шестого и седьмого элементов И блока управления памятью, второй информационный выход счетчика блока управления памятью соединен с третьим прямым входом четвертого элемента И блока управления памятью, с вторыми инверсными входами седьмого и восьмого элементов И блока управления памятью и с инверсным входом шестого элемен- . та И блока управления памятью, третий информационный выход счетчика блока управления памятью соединен с вторыми инверсными входами четвертого и седьмого элементов И блока управления памятью, с вторым прямым входом восьмого элемента И блока управления памятью и с третьим прямым входом шестого элемента И блока управления памятью, выход седьмого элемента И блока управления памятью соединен с входами синхронизации первого, третьего и шестого триггеров блока управления памятью, выход восьмого элемента И блока управления памятью соединен с входами установки в ноль первого и шестого триггеров блока управления памятью и с первым входом девятого элемента И блока управления памятью, второй вход которого соединен с пятым управляюш;им выходом блока вьщеления и идентификации символа и с первым входом третьего элемента ИЛИ блока управления памятью, второй вход которого соединен с выходом пятого триггера блока управления памятью,вход синхронизации которого соединен с выходом второго элемента И блока управления памятью, второй вход ко- . торого соединен с входом управления записью символа устройства и первым входом пятого элемента ИЛИ блока управления памятью, второй вход которого соединен с входом управления считыванием символа устройства и с вторым входом третьего элемента И блока управления памятью, выход которого соединен с входом синхронизации четвертого триггера блока управления памятью, выход которого соединен с третьим входом второго элемента ИЛИ блока управления памятью,выход девятого элемента И блока управления памятью соединен с вторым входом первого элемента ИЛИ блока управления памятью, выход которого срёдинён со счетным входом счетчика адреса памяти, выходы первого и шес того триггеров блока управления памятью соединены соответственно с вх дом записи блока памяти и входом чтения блока памяти, выход пятого элемента ИЛИ блока управления памятью соединен с вторьп входом первого элемента И блока управления па мятью, выход которого соединен с входом разрешения записи счетчика адреса памяти, информационный выход которого соединен с адресным входом блока памяти,информационный вход которого соединен с выходом коммутатора данных первьй и второй информационные входы которого соединены соответственно с входом данных устройства и с выходом регистра данных, информационный вход счетчик адреса памяти соединен с входом адреса данных устройства, выход памят через регистр данных соединен с информационным выходом устройства,при чем блок вьделения и идентификации символа содержит три триггера, семь элементов И и элемент ИЛИ-НЕ,первый вход которого соединен с первьми входами первого, второго и третьего элементов И и с единичным выходом первого триггера, нулевой выход которого соединен с первым входом четвертого элемента И, выход которо го соединен с информационным входом второго триггера, единичный выход которого соединен с первым входом пятого элемента И, с вторым входом элемента ИЛИ-НЕ и с первым входом установки в единицу первого триггер второй вход установки в единицу которого соединен с третьим входом си хронизации блока и с первым входом шестого элемента И, второй вход которого соединен с вторыми входами первого, второго и пятого элементов И, с вьпсодом третьего триггера и вторым входом четвертого элемента И, вход синхронизации второго .триггера соединен с третьими входам второго и пятого элементов И и вторым входом синхронизации блока, нул вой выход второго Триггера соединен с вторым входом третьего элемента И третий вход которого соединен с третьим управляющим выходом блока, с выходом шестого элемента И и с первым входом седьмого элемента И, второй вход и выход которого соеди нены соответственно с выходом элемента ИПИ-НЕ и с первым управляющим выходом блока, третий вход первого ,элемента И соединен с четвертым входом синхронизации блока и входом синхронизации третьего тригге.ра, информационный вход которого- соединен с информационные входом блока, i вход установки в ноль третьего триггера соединен с первым входом синхронизации блока, третий вход четвертого элемента И и вход установки в ноль первого триггера соединены соответственно с первым управляющим входом блока и входом сброса блока, второй, четвертый и пятые управляющие выходы блока соединены соответственно с выходом второго элемента И, с выходом пятого элемента И и выходом третьего элемента И, выход первого элемента И соединен с выходом вьиеления символов блока. Кроме того, блок синхронизации содержит десять элементов И, четыре триггера, два генератора импульсов, элемент ИЛИ и счетчик, первый информационньп выход которого соединен с первьм инверсным входом первого элемента И, с первыми прямыми входами второго, третьего и четвертого элементов И и с инверсным входом пятого элемента И, второй информационный выход счетчика соединен с вторым инверсным входом первого элемента Иj с первым инверсным входом второго элемента И, с вторыми прямыми входами третьего и четвертого элементов И, с инверсным входом шестого элемента И, и с первым прямым входом пятого элемента И, выход которого соединен с четвертым выходом блока, третий информационный выход счетчика соединен с третьим инверсным входом первого элемента И, с вторым инверсным входом второго элемента И, с инверсным входом третьего элемента И, с прямым входом шестого элемента И, с вторьм прямым входом пятого элемента И и с третьим прямым входом четвертого элемента И, выход первого генератора импульсов соединен с входом синхронизации первого триггера, с прямым входом первого элемента И, с вторым прямым входом второго элемента И и с третьим прямым входом пятого элемента И, с инверсными входами четвертого и седьмого элементов И и с первыми входами восьмого, девятого и десятого элементов И,вто11 1

рой вход десятого элемента И соединен с выходом первого триггера,входы установки в ноль и в единицу которого соединены с выходом второго генератора импульсов, первый прямой вход седьмого элемента И соединен с нулевым выходом второго триггера, единичный выход которого соединен с входом установки в единицу третьего триггера, единичный и нулевой выходы которого соединены соответственно с вторым входом восьмого элемента И и с,вторым входом девятого элемента И, выход которого соединен с входом установки в единицу счетчика, счетный вход которого соединен с выходом восьмого элемента И и с входом установки в ноль четвертого триггера, нулевой выход которого соединен с входом установки в ноль второго триггера, первьй вход установки в едицину которого соединен с вторым выходом блока, с единичным выходом четвертого триггера и с вторым прямым входом седьмого элемента И, выход которого соединен с входом установки в ноль третьего триггера, выход четвертого элемента И соединен с входом установки в единицу четвертого триггера, выходы третьего и шестого элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с третьим выходом блока, второй вход установки, в единицу второго триггера соединен с входом запуска блока, первьй, пятый и шестой выходы блока соединены Соответственно с выходом первого элемента И , с выходом второго элемента И и свыходом десятого элементам.

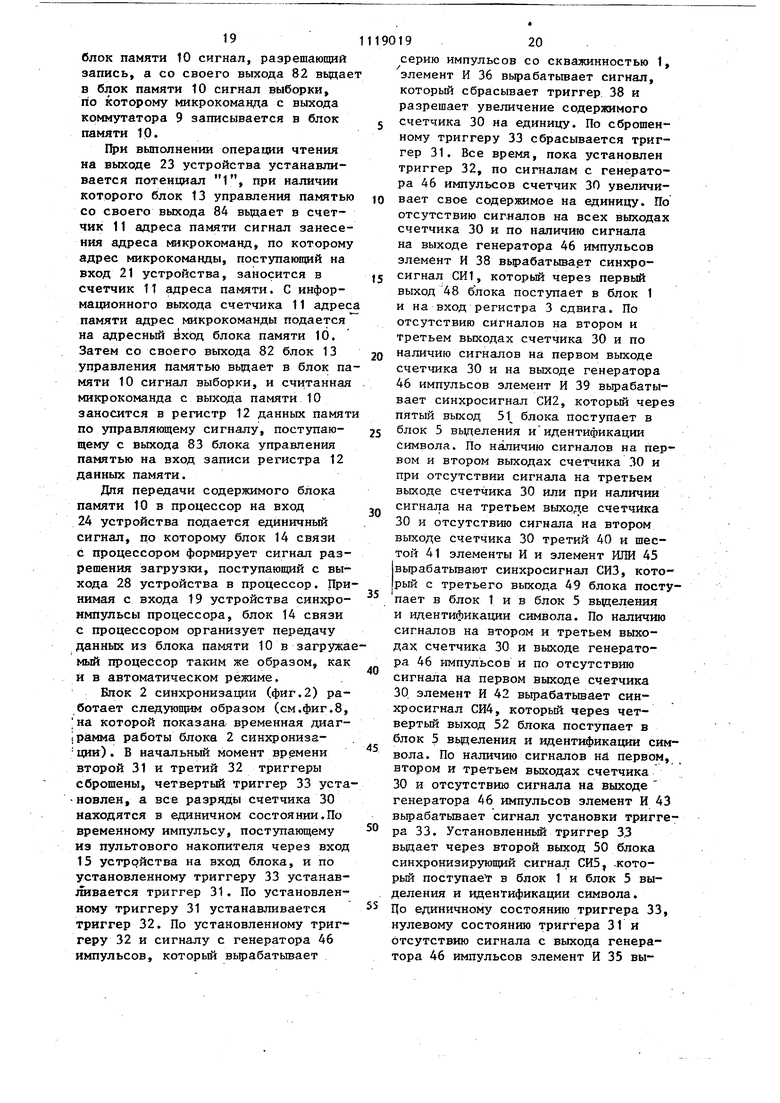

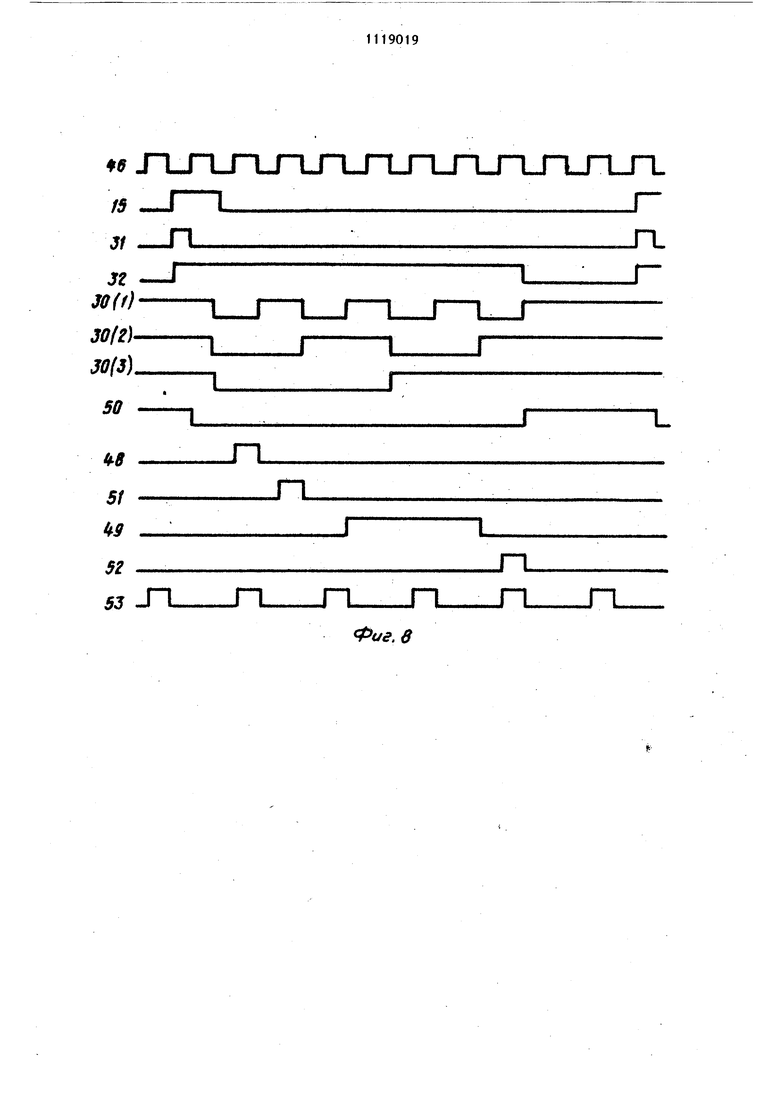

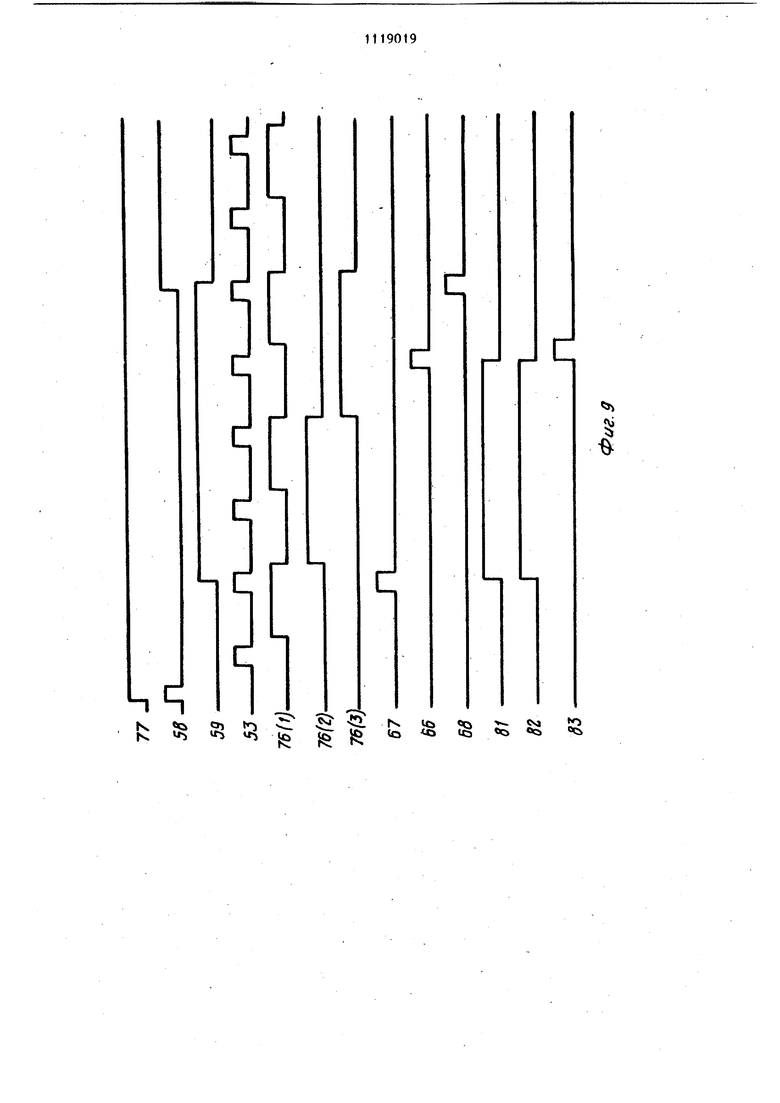

На фиг. 1 иэображена схема устроства управления загрузкой микропрограмм; на фиг. 2 - схема блока синхронизации; на фиг. 3 - схема блка управления памятью; на фиг. 4 - схема блока вьделения и идентификации символа; на фиг. 5 - схема блок связи с процессором; на фиг. 6 схема блока управления движением головки; на фиг. 7 - схема блока вьщеления временных битов и битов данных, на фиг. 8 - временная диаграмма работы блока синхронизации; н фиг. 9 - временная диаграмма работы блока управления памятью в режиме записи; на фиг. 10 - временная диаграмма работы блока управления памятью в режиме чтения.

901912

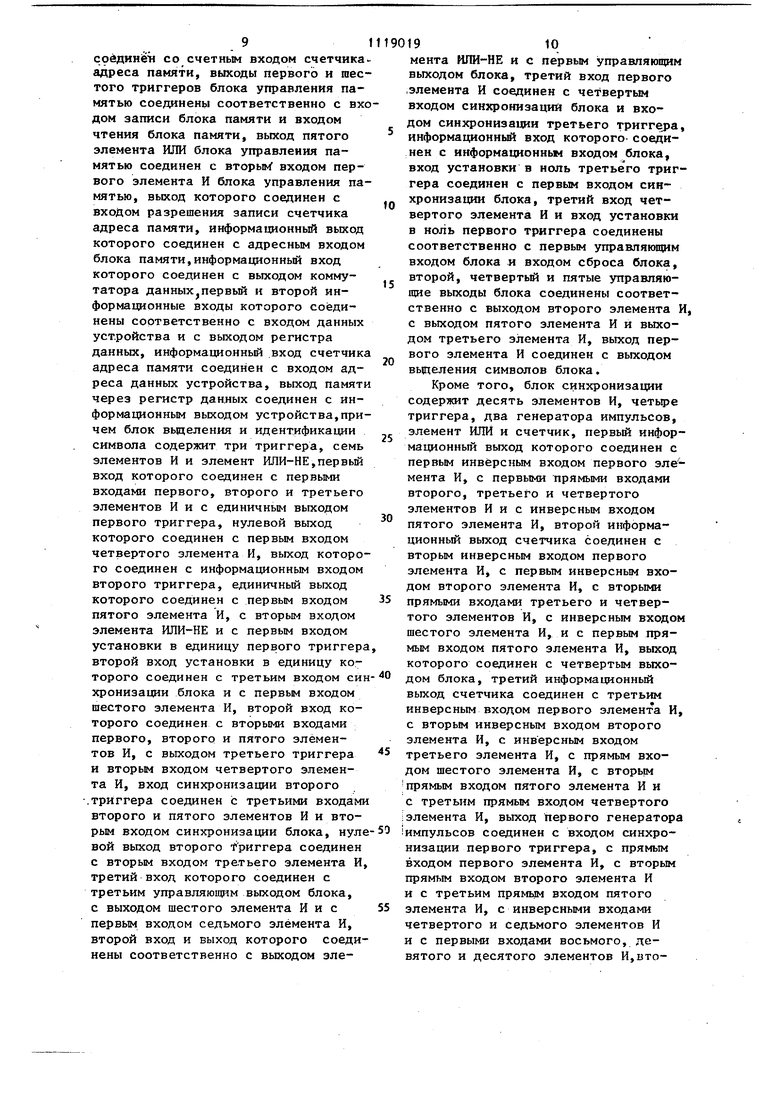

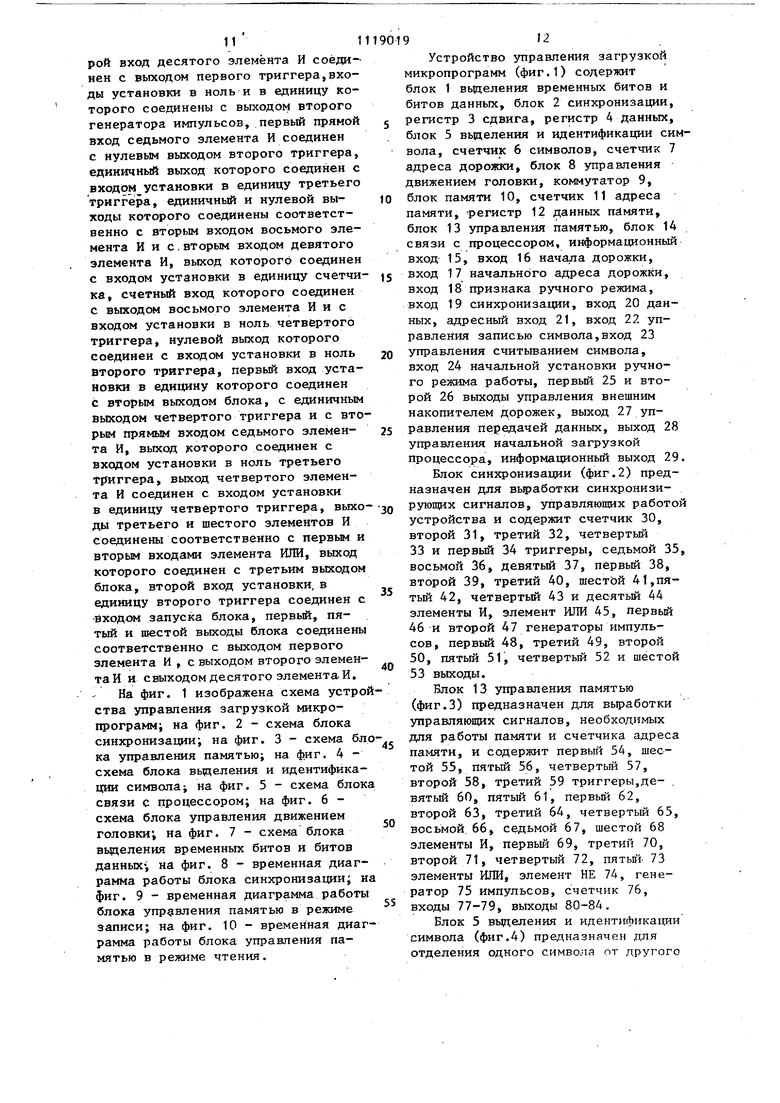

Устройство управления загрузкой микропрограмм (фиг.1) содержит блок 1 вьделения временных битов и битов данных, блок 2 синхронизации, 5 регистр 3 сдвига, регистр 4 данных, блок 5 вьделения и идентификации символа, счетчик 6 символов, счетчик 7 адреса дорожки, блок 8 управления движением головки, коммутатор 9, 0 блок памяти 10, счетчик 11 адреса памяти, -регистр 12 данных памяти, блок 13 управления памятью, блок 14 связи с процессором, информационный вход 15, вход 16 начала дорожки, 5 вход 17 начального адреса дорожки, вход 18 признака ручного режима, вход 19 синхронизации, вход 20 данных, адресный вход 21, вход 22 управления записью символа,вход 23

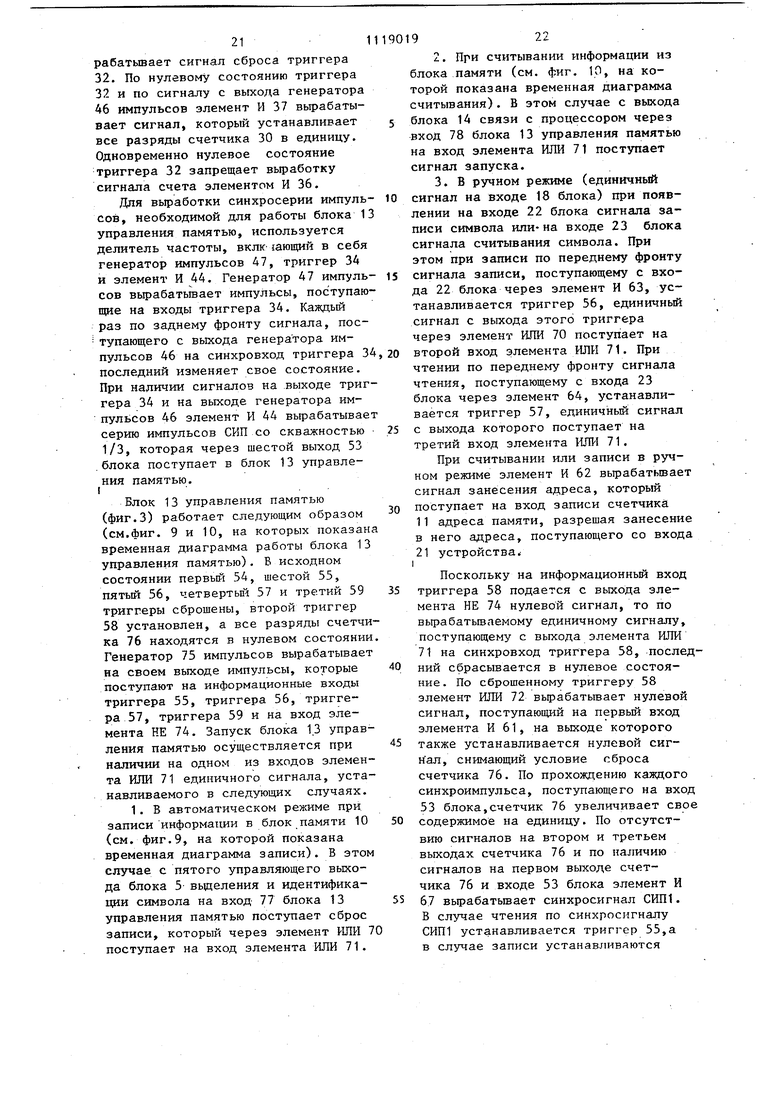

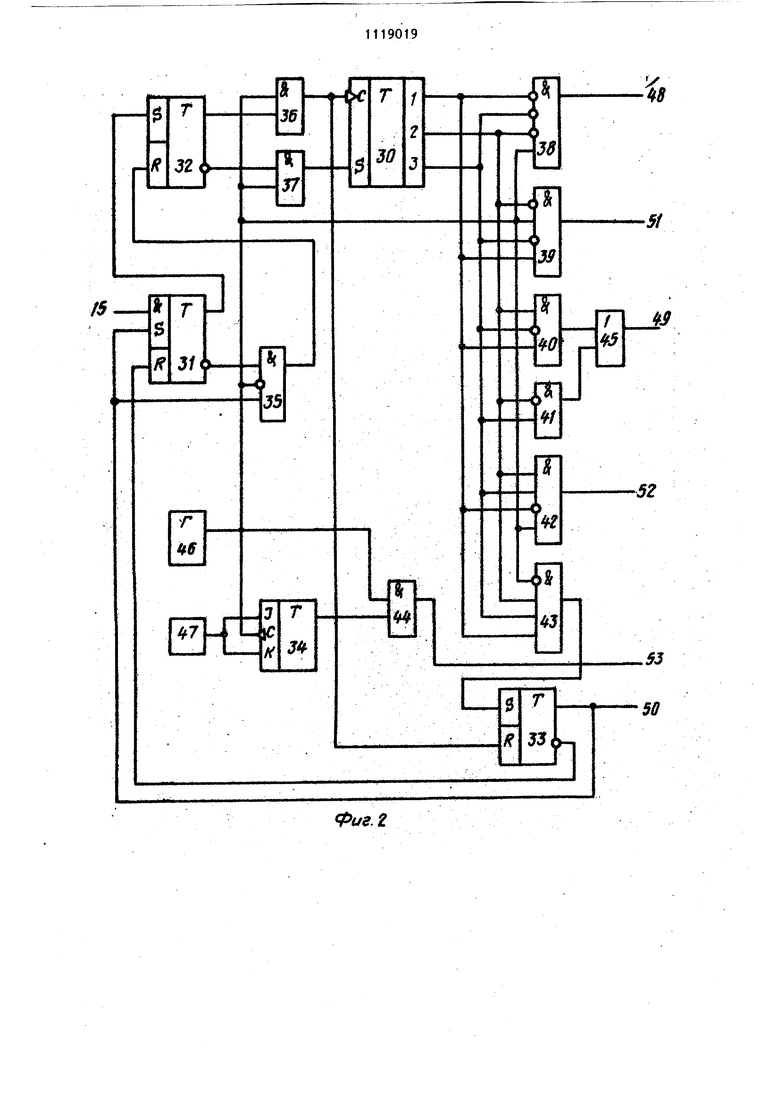

0 управления считыванием символа, вход 24 начальной установки ручного режима работы, первый 25 и второй 26 выходы управления внешним накопителем дорожек, выход 27 уп5 равления передачей данных, выход 28 управления начальной загрузкой процессора, информационный выход 29. Клок синхронизации (фиг.2) предназначен для вьфаботки синхронизи0 РУОЩНзс сигналов, управляющих работой устройства и содержит счетчик 30, второй 31, третий 32, четвертый 33 и первый 34 триггеры, седьмой 35, восьмой 36, девятьй 37, первый 38, второй 39, третий 40, шестой 41,пятый 42, четвертый 43 к десятьй 44 элементы И, элемент ИЛИ 45, первьй 46 и второй 47 генераторы импульсов, первый 48, третий 49, второй 50, пятый 51, четвертьй 52 и шестой 53 выходы.

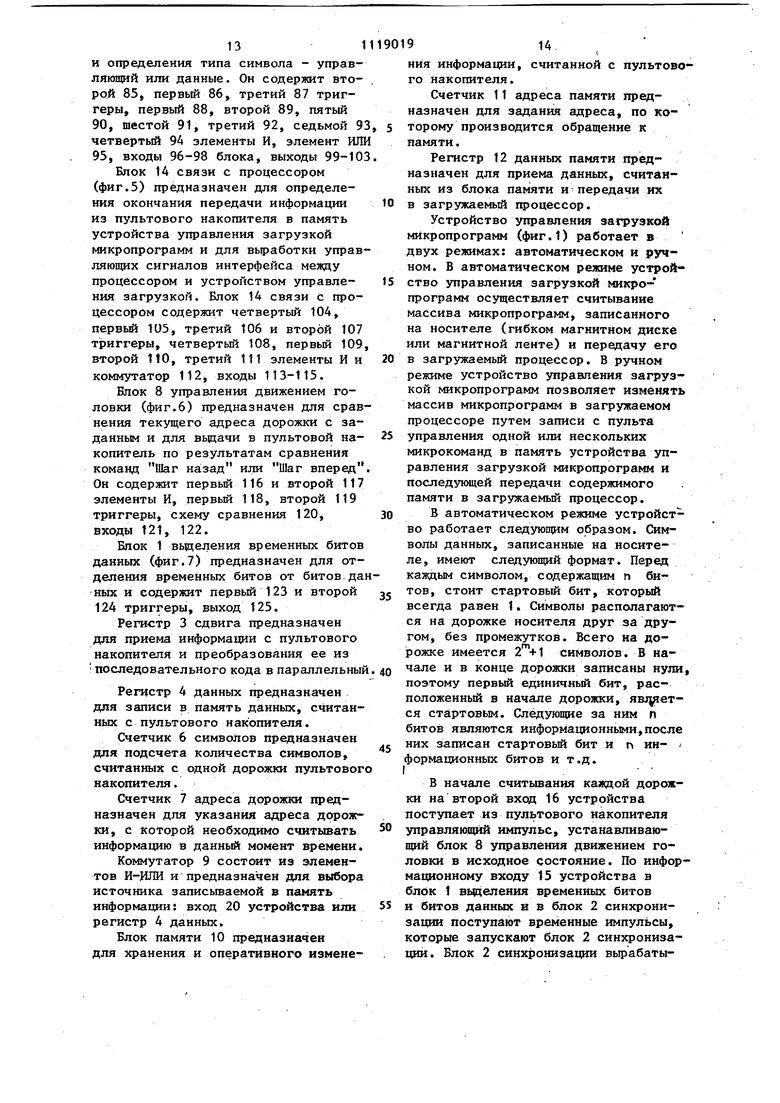

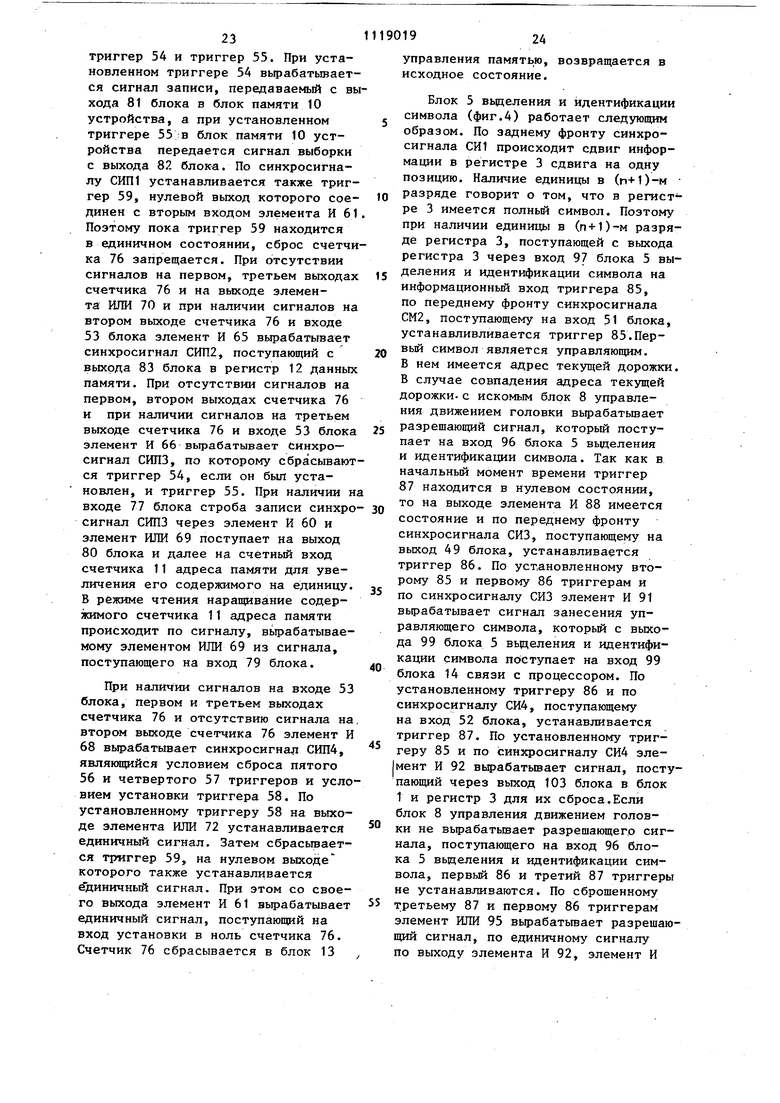

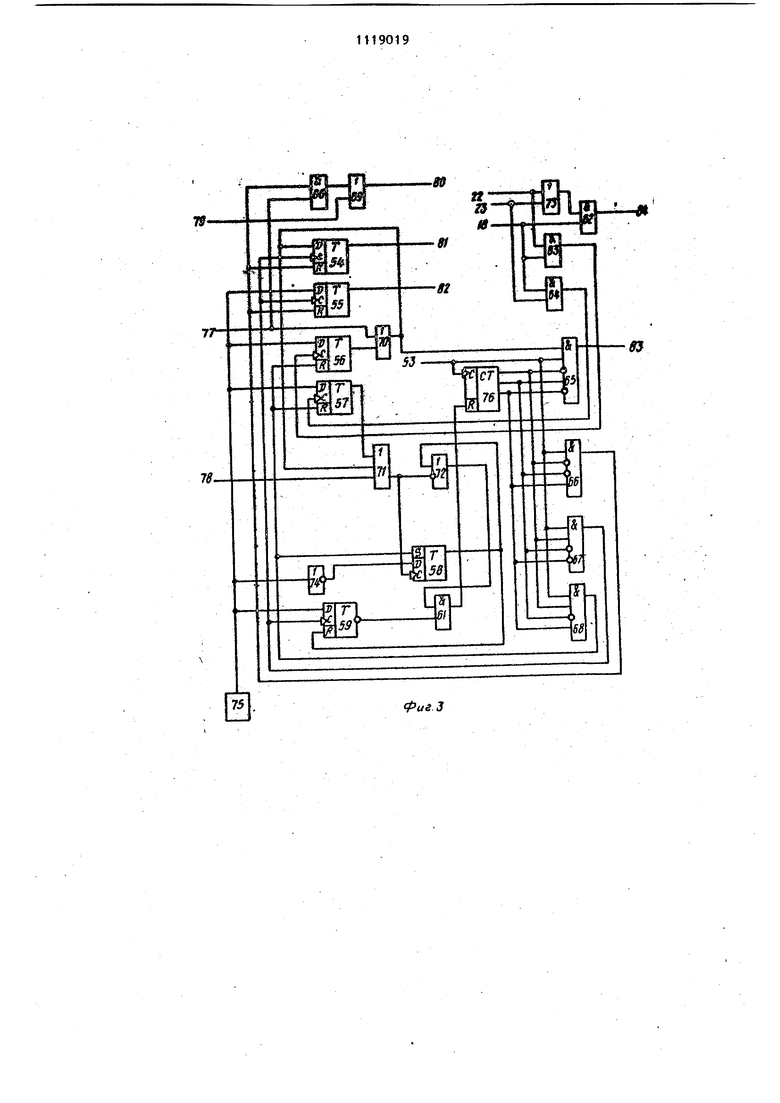

Блок 13 управления памятью (фиг.З) предназначен для выработки управляющих сигналов, необходимых для работы памяти и счетчика адреса памяти, и содержит первый 54, шестой 55, пятый 56, четвертьй 57, второй 58, третий 59 триггеры,девятьй 60, пятьй 61, первьй 62, второй 63, третий 64, четвертьй 65, восьмой. 66, седьмой 67, шестой 68 элементы И, первьй 69, третий 70, второй 71, четвертый 72, пятьй 73 элементы ИЛИ, элемент НЕ 74, генератор 75 импульсов, счетчик 76,

входы 77-79, выходы 80-84.

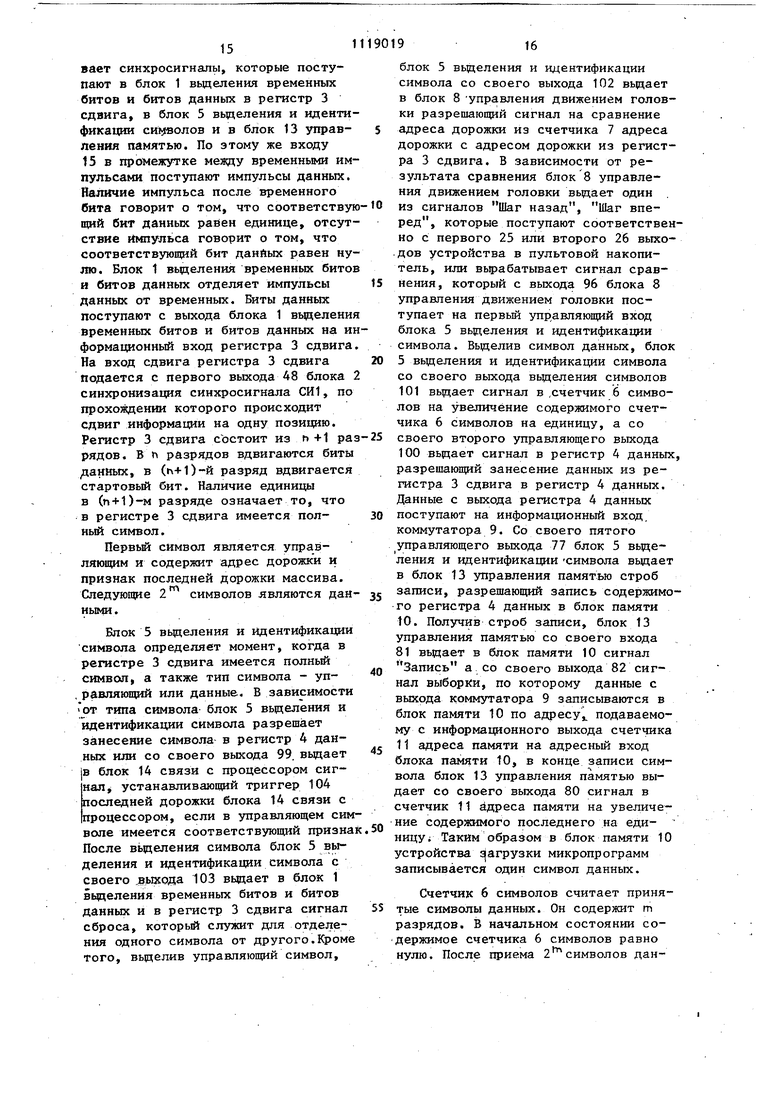

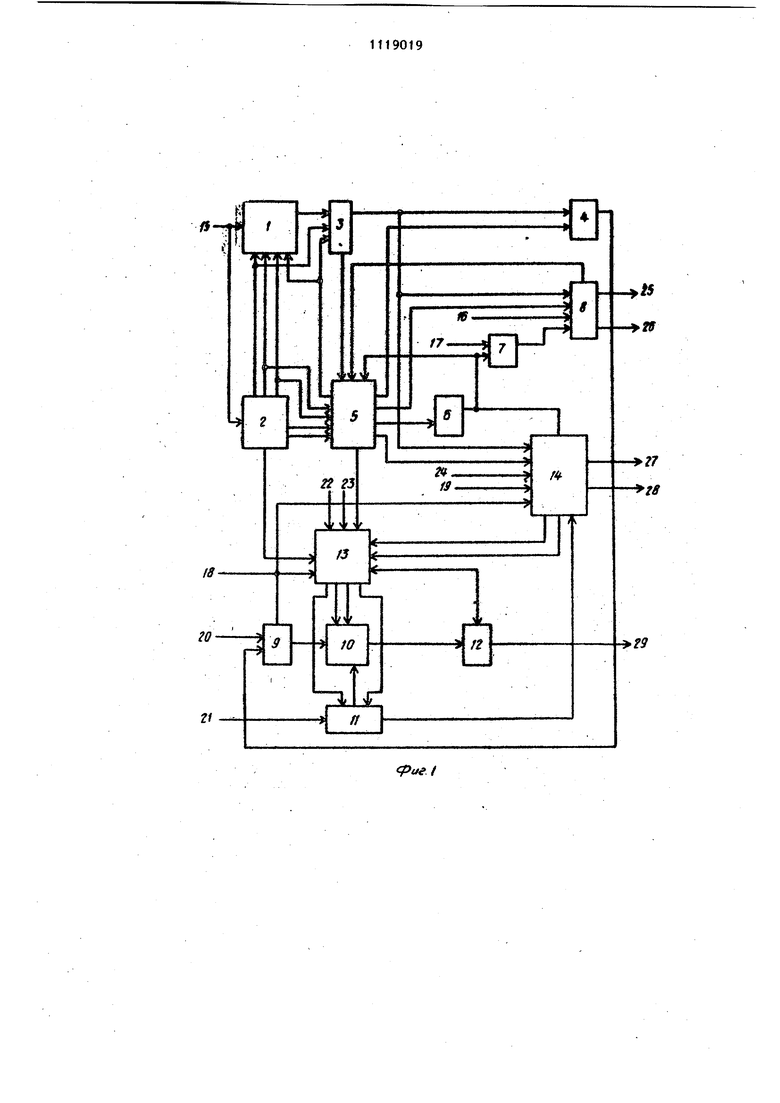

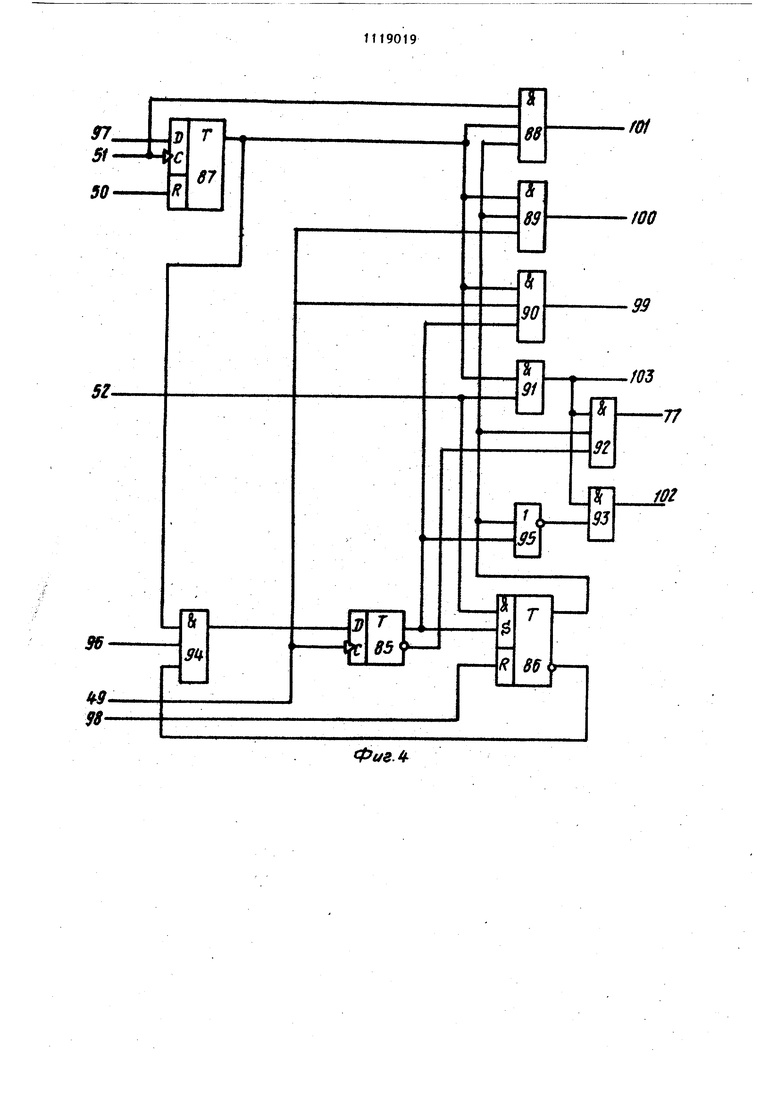

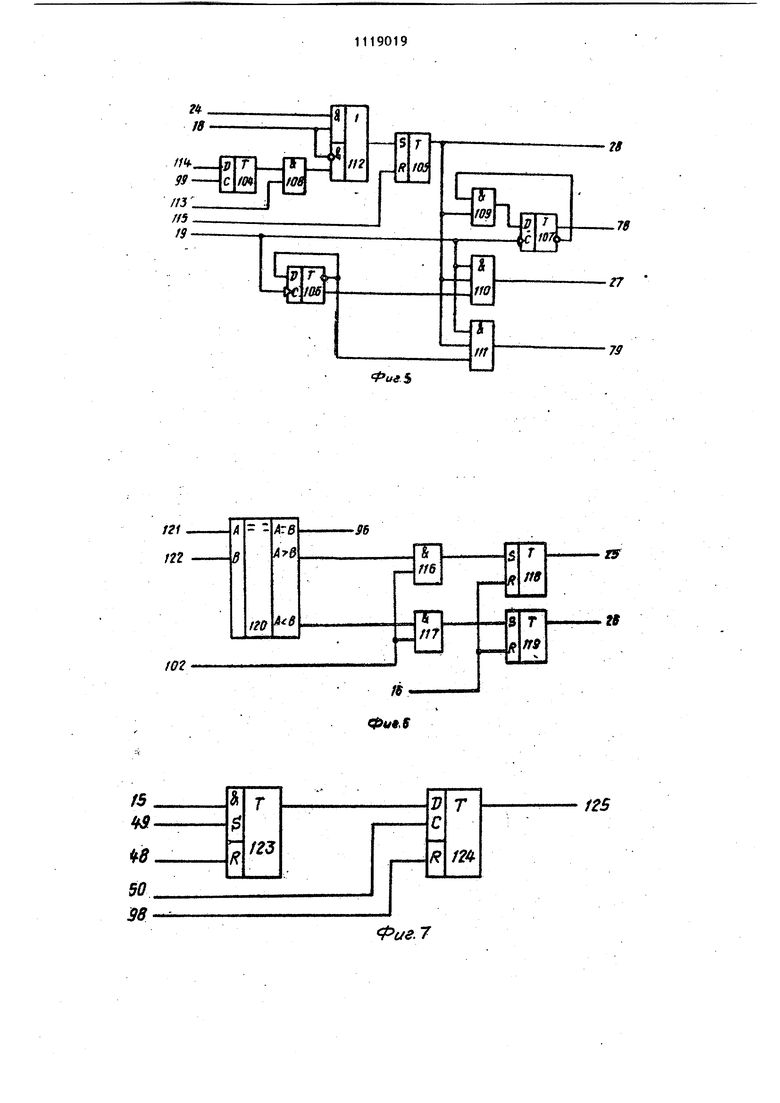

Блок 5 вьщеления и идентификации символа (фиг.4) предназначен для отделения одного символа от лругого и определения типа символа - управляющий или данные. Он содержит второй 85, первый 86, третий 87 триггеры, первый 88, второй 89, пятый 90, шестой 91, третий 92, седьмой 9 четвертый 94 элементы И, элемент ИЛ 95, входы 96-98 блока, выходы 99-10 Блок 14 связи с процессором (фиг.5) предназначен для определения окончания передачи информации из пультового накопителя в память устройства управления загрузкой микропрограмм и для выработки управ ляющих сигналов интерфейса между процессором и устройством управления загрузкой. Блок 14 связи с процессором содержит четвертый 104, первьй 105, третий ТОб и второй 107 триггеры, четвертый 108, первый 109 второй ttO, третий 111 элементы И и коммзтатор 112, входы 113-115. Блок 8 управления движением головки (фиг.6) предназначен для срав нения текущего адреса дорожки с заданным и для вьдачи в пультовой накопитель по результатам сравнения команд Шаг назад или Шаг вперед Он содержит первый 116 и второй 117 элементы И, первый 118, второй 119 триггеры, схему сравнения 120, входы 121, 122. Бпок 1 вьделения временных битов данных (фиг.7) предназначен для отделения временных битов от битов да ных и содержит первьй 123 и второй 124 триггеры, выход 125. Регистр 3 сдвига предназначен для приема информации с пультового накопителя и преобразования ее из последовательного кода в параллельны Регистр 4 данных предназначен для записи в память данных, считанных с пультового накопителя. Счетчик 6 символов предназначен для подсчёта количества символов, считанных с одной дорожки пультовог накопителя. Счетчик 7 адреса дорожки предназначен для указания адреса дорожки, с которой необходимо считывать информацию в данный момент времени Коммутатор 9 состоит из элементов И-ИЛИ и предназначен для выбора источника записываемой в память информации: вход 20 устройства или регистр 4 данных. Блок памяти 10 предназначен для хранения и оперативного изменени:я информации, считанной с пультового накопителя. Счетчик 11 адреса памяти предназначен для задания адреса, по которому производится обращение к памяти. Регистр 12 данных памяти предназначен для приема данных, считанных из блока памяти и передачи их в загружаемый процессор. Устройство управления загрузкой микропрограмм (фиг.1) работает в двух режимах: автоматическом и ручном. В автоматическом режиме устройство управления загрузкой микро- программ осуществляет считывание массива микропрограмм, записанного на носителе (гибком магнитном диске или магнитной ленте) и передачу его в загружаемый процессор. В ручном режиме устройство управления загрузкой микропрограмм позволяет изменять массив микропрограмм в загружаемом процессоре путем записи с пульта управления одной или нескольких микрокоманд в память устройства управления загрузкой микропрограмм и последующей передачи содержимого памяти в загружаемый процессор. В автоматическом режиме устройство работает следующим образом. Символы данных, записанные на носителе, имеют следующий формат. Перед каядым символом, содержащим п битов, стоит стартовый бит, который всегда равен 1. Символы располагаются на дорожке носителя друг за другом, без промежутков. Всего на дорожке имеется 2 +1 символов. В начале и в конце дорожки записаны нули, поэтому первый единичный бит, рас- положенньй в начале дорожки, явд ;1ется стартовым. Следующие за ним п битов являются информационными,после них записан стартовьй бит и п информационных битов и т.д. I В начале считывания каждой дорожки на второй вход 16 устройства поступает из пультового накопителя управляющий импульс, устанавливающий блок 8 управления движением головки в исходное состояние. По информационному входу 15 устройства в блок 1 наделения временных битов и битов данных и в блок 2 синхронизации поступают временные импульсы, которые запускают блок 2 синхронизации. Блок 2 синхронизации вырабатывает синхросигналы, которые поступают в блок 1 вьщеления временных битов и битов данных в регистр 3 сдвига, в блок 5 вьщеления и иденти фикации си волов и в блок 13 управяения памятью. По этому же входу 15 в промежутке между временными им пульсами поступают импульсы данных Наличие импульса после временного бита говорит о том, что соответству щий бит данных равен единице, отсут ствие импульса говорит о том, что соответствую11р1й бит данйьпс равен ну лю. Блок 1 вьщеления временных бито и битов данных отделяет импульсы данных от временных. Биты данных поступают с выхода блока 1 вьщелени временных битов и битов данных на и формационный вход регистра 3 сдвига На вход сдвига регистра 3 сдвига подается с первого выхода 48 блока синхронизация синхросигнала СИ1, по проховдении которого происходит сдвиг информации на одну позицию. Регистр 3 сдвига состоит из и +1 ра рядов. В п разрядов вдвигаются биты данных, в ()-й разряд вдвигается стартовый бит. Наличие единицы в (п+1)-м разряде означает то, что в регистре 3 сдвига имеется полный символ. Первьй символ является управлякщим и содержит адрес дорожки и признак последней дорожки массива. Следующие 2 символов являются дан ными. Блок 5 вьщеления и идентификации символа определяет момент, когда в регистре 3 сдвига имеется полный символ, а также тип символа - уп, равляющий или данные. В зависимости от типа символа блок 5 вьщеления и идентификации символа разрешает занесение символа в регистр 4 данных или со своего выхода 99. вьщает IB блок 14 связи с процессором сигнал устанавливающий триггер 104 последней дорожки блока 14 связи с процессором, если в управляющем сим воле имеется соответствующий призна После вьщеления символа блок 5 вьгделения и идентификации символа с своего ,вькада 103 вьщает в блок 1 вьщеления временных битов и битов данных и в регистр 3 сдвига сигнал сброса, который служит для отделения одного символа от другого.Кром того, вьщелив управляющий символ. блок 5 вьщеления и идентификации символа со своего выхода 102 вьщает в блок 8 управления движением головки разрешающий сигнал на сравнение адреса дорожки из счетчика 7 адреса дорожки с адресом дорожки из регистра 3 Сдвига. В зависимости от результата сравнения блок 8 управления движением головки вьщает один из сигналов Шаг назад, Шаг вперед, которые поступают соответственно с первого 25 или второго 26 выхо.дов устройства в пультовой накопитель, или вь1рабатывает сигнал сравнения, который с выхода 96 блока 8 управления движением головки поступает на первьй управляющий вход блока 5 вьщеления и идентификации символа. Вьщелив символ данных, блок 5 вьщеления и идентификации символа со своего выхода вьщеления символов 101 вьщает сигнал в .счетчик 6 символов на увеличение содержимого счетчика 6 символов на единицу, а со своего второго управляющего выхода 100 вьщает сигнал в регистр 4 данных, разрешающий занесение данных из регистра 3 сдвига в регистр 4 данных. Данные с выхода регистра 4 данных поступают на информационный вход, коммутатора 9. Со своего пятого управляющего выхода 77 блок 5 вьщеления и идентификации -символа вьщает в блок 13 управления памятью строб записи, разрешающий запись содержимого регистра 4 данных в блок памяти 10. Получив строб записи, блок 13 управления памятью со своего входа 81 вьщает в блок памяти 10 сигнал Запись а со своего выхода 82 сигнал выборки, по которому данные с выхода коммутатора 9 записываются в блок памяти 10 по адресу,, подаваемому с информационного выхода счетчика 11 адреса памяти на адресный вход блока памяти tO, в конце записи символа блок 13 управления памятью выдает со своего выхода 80 сигнал в счетчик 11 ёдреса памяти на увеличение содержимого последнего на единицу; Таким образом в блок памяти 10 устройства агрузки микропрограмм записывается один символ данных. Счетчик 6 символов считает принятые символы данных. Он содержит m разрядов. В начальном состоянии соДержимое счетчика 6 символов равно нулю. После приема 2 символов дан17ных счетчик 6 символов снова сбрасыв ется в нулевое состояние и вырабатывает сигнал переноса, который поступает на счетный вход счетчика 7 адреса дорожки для увеличения адреса дорожки на единицу и на вход сброса блока 5 вьиеления и идентификации символа для сброса его в исходное состояние. : Счетчик 7 адреса дорожки служит для указания адреса дорожки, с которой необходимо считывать информацию в данный момент времени. В нача ле загрузки микропрограмм с входа 1 устройства в счетчик 7 адреса дорож ки заносится начальньп адрес дорожки начиная с которого располагается загружаемый массив микропрограмм. В дальнейшем содеря имое счетчика 7 ад реса дорожки увеличивается на едини цу сигналом переноса счетчика 6 символов, поступающим на счетный вход счетчика 7 адреса дорожки. ЕСЛИ установлен триггер 104 последней дорожки блока 14 связи с процессором, то по сигналу переноса с выхода счетчика 6 символов блок 14 связи с процессором через выход 23 устройства передает в загружаемый процессор сигнал разрежения загрузки, сообщающий процессо ру о начале загрузки массива данных Для синхронной передачи данных в процессор последний через вход 19 устройства передает в блок 14 связи с процессором синхроимпульсы. Принимая синхроимпульсы от процессора, блок 14 связи с процессором со свое го входа 78 вьщает в блок 13 управления памятью сигнал запуска,по которому блок 13 управления памятью вьрабатьшает последовательность управляющих сигналов, необходимых для выполнения операции считывания данных из блока памяти 10, Приняв сигнал запуска, блок 13 управления па,мятью со своего выхода 82 вьщает сигнал выборки в блок памяти 10, а счетчик 11 адреса памяти, начальное состояние которого равно нулю,со своего информационного выхода подае в блок памяти 10 адрес считываемого символа данных. Считанньй символ да ных с выхода блока памяти 10 запоми нается в регистр 12 данных памяти п синхросигналу, поступающему на синхровход регистра 12, с входа 83 блока 13 управления памятью.Данные с выхода регистра 12 данных памяти 1918 через выход 29 устройства поступают в загрузочньпЧ процессор. Одновременно блок 14 связи с процессором через выход 27 устройства передает в процессор импульс передачи, по которому осуществляется прием символа данных, а со своего входа 79 передает в блок 13 управле:ния памятью сигнал, по которому блок 13 управления памятью со своего выхода 80 ньщает в счетчик 11 адреса памяти сигнал на увеличение содержимого последнего на единицу. После того, как все содержимое блока памяти 10 передано в загружаемый процессор, счетчик 11 адреса памяти переходит в нулевое состояние и формирует сигнал переноса, который поступает с выхода переноса счетчика 11 адреса памяти в блок 14 связи с процессором и сбрасывает последний в исходное состояние. При этом на выходе 28 устройства снимается сигнал разрещения загрузки, что служит загружаемому процессору признаком окончания загрузки. В случае необходимости оперативного изменения микропрограмм в памяти загружаемого процессора используется ручной режим работы устройства. Сначала исправляемая микрокоманда или несколько микрокоманд вводятся в блок памяти 10 устройства, затем содержимое памяти передается в процессор. Ручной режим работы задается подачей на вход 18 устройства потенциала 1, поступающего на управляющий вход коммутатора 9 и на управляющие входы блока 13 управления памятью и блока 14 связи с процеСт сором. При выполнении операций записи или чтения на вход 20 устройства подается код микрокоманды,который поступает на первьп информационный вход коммутатора 9. При записи на входе 22 устройства устанавливается потенциал 1, при наличии которого блок 13 управления памятью со своего входа 84 вьщает в счетчик 11 адреса.памяти сигнал занесения адреса микрокоманды, по которому адрес данной микрокоманды, поступающий на вход 21 устройства, заносится в счетчик 11 адреса памяти. С информационного выхода счетчика 11 адреса памяти адрес микрокоманды подается на адресный вход блока памяти 10. Затем со своего выхода 81 блок 13 управления памятью вьщает в

19

блок памяти 10 сигнал, разрешающий запись, а со своего выхода 82 ввдае в блок памяти tO сигнал выборки, по которому микрокоманда с выхода коммутатора 9 записывается в блок памяти 10.

При вьтолнении операции чтения на выходе 23 устройства устанавливается потенциал 1, при наличии которого блок 13 управления памятью со своего выхода 84 вьщает в счетчик 11 адреса памяти сигнал занесения адреса микрокоманд, по которому адрес микрокоманды, поступающий на вход 21 устройства, заносится в счетчик 11 адреса памяти. С информационного выхода счетчика 11 адрес памяти адрес микрокоманды подается на адресный йхОд блока памяти 10. Затем со своего выхода 82 блок 13 управления памятью вьщает в блок памяти 10 сигнал выборки, и считанная микрокоманда с выхода памяти 10 заносится в регистр 12 данных памят по управляющему сигналу, поступающему с выхода 83 блока управления памятью на вход записи регистра 12 данных памяти.

Для передачи содержимого блока памяти 10 в процессор на вход 24 устройства подается единичный сигнал, по которому блок 14 связи с процессором формирует сигнал разрещения загрузки, поступающий с выхода 28 устройства в процессор. Принимая с входа 19 устройства синхроимпульсы процессора, блок 14 связи с процессором организует передачу данных из блока памяти 10 в загружамый процессор таким же образом, как и в автоматическом режиме.

Бпок 2 синхронизации (фиг.2) работает следующим образом (см.фиг.8, на которой показана временная диаг1рамма работы блока 2 синхронизации). В начальньй момент времени второй 31 и третий 32 триггеры сброшены, четвертьй триггер 33 установлен, а все разряды счетчика 30 находятся в единичном состоянии.По временному импульсу, поступающему из пультового накопителя через вход 15 устройства на вход блока, и по установленному триггеру 33 устанавШ1вается триггер 31. По установленному триггеру 31 устанавливается триггер 32. По установленному триггеру 32 и сигналу с генератора 46 импульсов, который вьфабатьгоает

1901920

серию импульсов со скважинностью 1, элемент И 36 вьфабатьгоает сигнал, который сбрасывает триггер. 38 и разрешает увеличение содержимого 5 счетчика 30 на единицу. По сброшенному триггеру 33 сбрасывается триггер 31. Все время, пока установлен триггер 32, по сигналам с генератора 46 импульсов счетчик 30 увеличивает свое содержимое на единицу. По отсутствию сигналов на всех выходах счетчика 30 и по наличию сигнала на выходе генератора 46 импульсов элемент И 38 вьд абатывает синхросигнал СИ1, которьй через первый выход 48 блока поступает в блок 1 и на вход регистра 3 сдвига. По отсутствию сигналов на втором и третьем выходах счетчика 30 и по наличию сигналов на первом выходе счетчика 30 и на выходе генератора 46 импульсов элемент И 39 вырабатывает синхросигнал СИ2, который через пятый выход 51 блока поступает в блок 5 вьщеления иидентификации символа. По наличию сигналов на первом и втором выходах счетчика 30 и при отсутствии сигнала на третьем выходе счетчика 30 или при наличии сигнала на третьем выходе счетчика 30 и отсутствию сигнала на втором выходе счетчика 30 третий 40 и шестой 41 элементы И и элемент ИЛИ 45 вырабатьгоают синхросигнал СИЗ, который с третьего выхода 49 блока поступает в блок 1 и в блок 5 вьщеления и идентификации символа. По наличшо сигналов на втором и третьем выходах счетчика 30 и выходе генератора 46 импульсов и по отсутствию сигнала на первом выходе счетчика 30 элемент И 42 вырабатьшает синхросигнал СИ4, который через четвертый выход 52 блока поступает в блок 5 вьреления и идентификации символа. По наличию сигналов ни первом, втором и третьем выходах счетчика 30 и отсутствию сигнала на выходе генератора 46 импульсов элемент И 43 вырабатьгоает сигнал установки триггера 33. Установленный триггер 3.3 вьиает через второй выход 50 блока синхронизирующий сигнал СИ5, .который поступает в блок 1 и блок 5 выделения и идентификации символа.

5 По единичному состоянию триггера 33, нулевому состоянию триггера 31 и отсутствию сигнала с выхода генератора 46 импульсов элемент И 35 вы21рабатьшает сигнал сброса триггера 32. По нулевоьгу состоянию триггера 32 и по сигналу с выхода генератора 46 импульсов элемент И 37 вьфабатывает сигнал, который устанавливает все разряды счетчика 30 в единицу. Одновременно нулевое состояние триггера 32 запрещает выработку сигнала счета элементом И 36. Для выработки синхросерии импуль сов, необходимой для работы блока 1 управления памятью, используется делитель частоты, вклк- шющий в себя генератор импульсов 47, триггер 34 и элемент И 44. Генератор 47 импуль сов вырабатывает импульсы, поступаю щие на входы триггера 34. Каждый раз по заднему фронту сигнала, пос тупающего с выхода генератора импульсов 46 на синхровход триггера 3 последний изменяет свое состояние. При наличии сигналов на выходе триг гера 34 и на выходе генератора импульсов 46 элемент И 44 вьфабатывае серию импульсов СИП со скважностью 1/3, которая через шестой выход 53 .блока поступает в блок 13 управления памятью. Блок 13 управления памятью (фиг.З) работает следующим образом (см.фиг. 9 и 10, на которых показан временная диаграмма работы блока 13 управления памятью). В исходном состоянии первый 54, шестой 55, пятый 56, четвертьй 57 и третий 59 триггеры сброшены, второй триггер 58 установлен, а все разряды счетчи ка 76 находятся в нулевом состоянии Генератор 75 импульсов вырабатывает на своем выходе импульсы, которые поступают на информационные входы триггера 55, триггера 56, триггера 57, триггера 59 и на вход элемента НЕ 74. Запуск блока 1.3 управления памятью осуществляется при наличии на одном из входов элемента ИЛИ 71 единичного сигнала, устанавливаемого в следующих случаях. 1. В автоматическом режиме при записи информации в блок памяти 10 (см. фиг.9, на которой показана временная диаграмма записи). В этом случае с пятого управляющего выхода блока 5 вьщеления и идентификации символа на вход 77 блока 13 управления памятью поступает сброс записи, который через элемент РШИ 7 поступает на вход элемента ИЛИ 71. 922 2.При считывании информации из блока памяти (см. фиг. 10, на которой показана временная диаграмма считывания). В этом случае с выхода блока 14 связи с процессором через вход 78 блока 13 управления памятью на вход элемента ИЛИ 71 поступает сигнал запуска. 3.В ручном режиме (единичный сигнал на входе 18 блока) при появлении на входе 22 блока сигнала записи символа или-на входе 23 блока сигнала считывания символа. При этом при записи по переднему фронту сигнала записи, поступающему с входа 22 блока через элемент И 63, устанавливается триггер 56, единичный сигнал с выхода этого триггера через элемент ИЛИ 70 поступает на второй вход элемента ЦПИ 71. При чтении по переднему фронту сигнала чтения, поступающему с входа 23 блока через элемент 64, устанавливается триггер 57, единичный сигнал с выхода которого поступает на третий вход элемента ИЛИ 71. При считывании или записи в ручном режиме элемент И 62 вырабатьшает сигнал занесения адреса, который поступает на вход записи счетчика 11 адреса памяти, разрешая занесение в него адреса, поступающего со входа 21 устройства. Поскольку на информационньй вход триггера 58 подается с выхода элемента НЕ 74 нулевой сигнал, то по Еырабатьгоаемому единичному сигналу, поступающему с выхода элемента ИЛИ 71 на синхровход триггера 58, последкий сбрасывается в нулевое состояние . По сброшенному триггеру 58 элемент ИЛИ 72 вырабатывает нулевой сигнал, поступающий на первьш вход элемента И 61, на выходе которого также устанавливается нулевой сигнал, снимающий условие сброса счетчика 76. По прохождению каждого синхроимпульса, поступающего на вход 53 блока,счетчик 76 увеличивает свое содержимое на единицу. По отсутствию сигналов на втором и третьем выходах счетчика 76 и по наличию сигналов на первом выходе счетчика 76 и входе 53 блока элемент И 67 вырабатывает синхросигнал СИП1. В случае чтения по синхросигналу СИП1 устанавливается триггер 55,а в случае записи устанавливаются 23 триггер 54 и триггер 55. При установленном триггере 54 вьфабатьгоается сигнал записи, передаваемый с вы хода 81 блока в блок памяти 1О устройства, а при установленном триггере 53 в блок памяти 10 устройства передается сигнал выборки с выхода 82 блока. По синхросигналу СИП1 устанавливается также триггер 59, нулевой выход которого соединен с вторым входом элемента И 61 Поэтому пока триггер 59 находится в единичном состоянии, сброс счетчи ка 76 запрещается. При отсутствии сигналов на первом, третьем выходах счетчика 76 и на выходе элемента ИЛИ 70 и при наличии сигналов на втором выходе счетчика 76 и входе 53 блока элемент И 65 вьфабатывает синхросигнал СИП2, поступающий с выхода 83 блока в регистр 12 данных памяти. При отсутствии сигналов на первом, втором выходах счетчика 76 и при наличии сигналов на третьем выходе счетчика 76 и входе 53 блока элемент И 66 вырабатывает синхросигнал СИПЗ, по которому сбрасывают ся триггер 54, если он был установлен, и триггер 55. При наличии н входе 77 блока строба записи синхро сигнал СИПЗ через элемент И 60 и элемент ИЛИ 69 поступает на выход 80 блока и далее на счетный вход счетчика 11 адреса памяти для увеличения его содержимого на единицу, В режиме чтения наращивание содержимого счетчика 11 адреса памяти происходит по сигналу, вь1рабатываемому элементом ИЛИ 69 из сигнала, поступающего на вход 79 блока. При наличии сигналов на входе 53 блока, первом и третьем выходах счетчика 76 и отсутствию сигнала на втором выходе счетчика 76 элемент И 68 вырабатывает синхросигнал СИП4, являкнцийся условием сброса пятого 56 и четвертого 57 триггеров и усло вием установки триггера 58. По установленному триггеру 58 на выходе элемента ИЛИ 72 устанавливается единичный сигнал. Затем сбрасьгаается Timrrep 59, на нулевом выходе которого также устанавливается единичный сигнал. При этом со своего выхода элемент И 61 вырабатывает единичный сигнал, поступающий на вход установки в ноль счетчика 76. Счетчик 76 сбрасывается в блок 13 19 управления памятью, возвращается в исходное состояние. Блок 5 вьделения и идентификации символа (фиг.4) работает следующим образом. По заднему фронту синхросигнала СИ1 происходит сдвиг информации в регистре 3 сдвига на одну позицию. Наличие единицы в (п+1)-м разряде говорит о том, что в регистре 3 имеется полный символ. Поэтому при наличии единицы в (п+1)-м разряде регистра 3, поступающей с выхода регистра 3 через вход 97 блока 5 выделения и идентификации символа на информационньй вход триггера 85, по переднему фронту синхросигнала СМ2, поступающему на вход 51 блока, устанавливливается триггер 85.Первьй символ является управляющим. В нем имеется адрес текущей дорожки. В случае совпадения адреса текущей дорожки, с искомым блок 8 управления движением головки вырабатьтает разрешающий сигнал, который поступает на вход 96 блока 5 вьщеления и идентификации символа. Так как в начальный момент времени триггер 87 находится в нулевом состоянии, то на выходе элемента И 88 имеется состояние и по переднему фронту синхросигнала СИЗ, поступающему на выход 49 блока, устанавливается триггер 86. По установленному второму 85 и первому 86 триггерам и по синхросигналу СИЗ элемент И 91 вырабатывает сигнал занесения управляющего символа, который с выхода 99 блока 5 вьделения и идентификации символа поступает на вход 99 блока 14 связи с процессором. По установленному триггеру 86 и по синхросигналу СИ4, поступающему на вход 52 блока, устанавливается триггер 87. По установленному триггеру 85 и по синхросигналу СИ4 элемент И 92 вырабатьшает сигнал, поступающий через выход 103 блока в блок 1 и регистр 3 для их сброса.Если блок 8 управления движением головки не вырабатьшает разрешающего сигнала, поступающего на вход 96 блока 5 вьделения и идентификации символа, первый 86 и третий 87 триггеры не устанавливаются. По сброшенному третьему 87 и первому 86 триггерам элемент ИЛИ 95 вырабатьгеает разрешающий сигнал, по единичному сигналу по выходу элемента И 92, элемент И 25 94 вьфабатьшает управляющий сигнал, который через выход 102 блока 5 выделения и идентификации символа поступает на вход 102 разрешения бл ка 8 управления движением головки. По синхросигналу СИЗ, поступающему вход 50 блока, триггер 85 сбрасывается. Сброшенный триггер 85 запрещает выработку единичного сигнала элементом И 88. Поэтому по переднему фронту следующего синхросигнала СИЗ, поступающему на вход 49 блока, триггер 86 сбрасывается. При наличии следующей единицы в (п +1)-м разряде регистра 3 по переднему фронту синхросигнала СИ2, поступающему на вход 51 блока, триггер 85 устанавливается вновь. При этом имеющийся в регистре 3 символ является символом данных. Установленный триггер 87 своим нулевым выходом запрещает выработку единичного сигнала элементом И 88. Поэтому по синхросигналу СИЗ, поступающему на вход 49 блока, триггер 87 устанавли вается. По установленным второму 85 и третьему 87 триггерам и синхросигналу СИ2 элемент И 89 вырабатыва сигнал, которьй через выход 101 блока 5 вьщеления и идентификации символа поступает на счетный вход счетчика 6 символов для увеличения его содержимого на единицу. По уста новленному вторюму 85 и третьему 87 триггерам и синхросигналу СИЗ элемент И 90 вьфабатывает сигнал, который через выход 100 блока 5 вьщел ния и идентификации символа поступа ет на вход записи регистра 4 данных разрешая занесение данных из регист ра 3 в регистр 4 данных. По установ ленному второму 85 и третьему 87, сброшенному первому 86.триггерам и синхросигналу СИ4 элемент И 93 выра батывает стробирующий сигнал, который через вход 77 блока поступает в блок 13 управления памятью и опре деляет начало записи символа данных в блок памяти 10 устройства. Блок 14 связи с процессором (фиг.5) работает следующим образом. В исходном состоянии четвертый 104, первьй 105 и второй 107 триггеры сброшены, а третий триггер 106 делит на две частоту синхроимпульсов, которые поступают из загружаемого процессора на его синхррвход через вход 19 блока. После того, как в регистре 3 сдвига сформирован 926 управляющий символ, содержащий признак последней дорожки, на входе 114 блока, соединенном с информационным входом триггера 104, устанавливается единичный сигнал. При наличии единичного сигнала на информационном входе триггера 104 по переднему фронту сигнала, поступающего из блока 5 вьщеления и идентификации символа на вход 99 блока, триггер 104 устанавливается в единичное состояние. На вход 18 блока поступает признак ручного режима. В автоматическом режиме по сигналу переноса, поступающему с выхода счетчика 6 символов на вход 113 блока, при установленном триггере 104 через элемент И 108 и коммутатор 112 устанавливается триггер 105. В ручном режиме триггер 105 устанавливается по подаче единргчного сигнала на вход 24 блока. Единичный сигнал с выхода триггера 105 поступает через выход 28 блока в процессор, сообщая ему о начале загрузки массива данных. При установленном триггере 105 и нулевом состоянии триггера 107 на выходе элемента И 109, соединенного с информационным входом триггера 107, устанавливается единичный сигнал, по переднему фронту синхроимпульса, поступающего из процессора на вход 19 блока, триггер 10.7 устанавливается в единичное состояние. С приходом из процессора следующего синхроимпульса триггер 107 сбрасывается. Таким образом, при установленном триггере 105 по синхроимпульсам от процессора на выходе триггера 107 формируется серия импульсов запуска, которая через выход 78 блока поступает в блок 13 управления памятью. По каждому импульсу запуска блок 13 управления памятью формирует последовательность управляющих сигналов для выполнения считывания из блока памяти 10 одного символа данных.Одновременно с установкой сигнала запуска при установленном триггере 105 и триггере 106 по синхроимпульсу от процессора элемент И 110 через выход 27 блока передает в процессор импульс передачи, необходимьй для приема символа данных. По установленному триггеру 105, сброщенному триггеру 106 и при наличии синхроимпульса от процессора элемент И 111 через выход 79 блока передает в блок 13 управления памятью сигнал, по которому блок

271

13 управления памятью наращивает содержимое счетчика 11 адреса памяти. Когда содержимое блока памяти 10 передано в процессор, счетчик 11 адрес памяти вырабатьтает сигнал переноса, поступающий на вход 115 блока. При этом триггер 105 сбрасьюается и блок 1А связи с процессором устанавливается в исходное состояние.

Блок 8 управления,движением головки (фиг.6) работает следующим образом. На вход 121 блока поступает ад,рес дорожки из регистра 3. На вход 2i блока поступает адрес дорожки ;из счетчика 7 адреса дорожки.Схема сравнения 120 производит сравнение этих адресов и вьдает один из трех сигналов: Равно, Больше, Меньше. В случае равенства адресов единичный сигнал с выхода схемы сравнения 120 через выход 96 блока поступает на первьй управляющий вход блока 5 выделения и идентификации символа. На вход 102 блока 8 управления движением головки поступает из блока 5 вьдёления и идентификации символа стробируюпщй сигнал, который в случае несравнения адресов через первый 116 или второй 117 элемент И разрешает установку соответственно первого 118 или второго 119 триггеров. Сигналы с выходов первого 118 и второго 119 триггеровсоответственно через выход блока, соединенный с ВЕлходом 25 устройства, и через выход блока, соединенный с выходом 26 устройства, поступают в пультовой накопитель. По этим сигналам пультовый накопитель перемещает головку соответственно на одну дорожку назад или на одну дорожку вперед. На вход 16 устройства с пультового накопителя поступает сигнал начала доролжи, по которому

901928

сбрасывается первьпЧ 118 или второй 119 триггер.

Блок 1 выделения временных блоков к битов данных (фиг,7) работает

следующим образом. Из пультового накопителя через вход 15 устройства на вход блока 1 поступают импульсы данных. Наличие импульса данных в момент времени СТЗ говорит о том,

0 что соответствующий бит данных равен единице. Отсутствие импульса данных в момент времени СТЗ говорит о том, что соответствующий бит данных равен нулю; При наличии импульса данных .

5 и синхроимпульса СИЗ, который поступает из блока 2 синхронизации на вход 49, устанавливается первьй триггер 123. По синхросигналу СИ5, поступающему на вход 50 блока 1 из

0 блока 2 синхронизации, состояние первого триггера переписывается во второй триггер 124. Сигнал с выхода второго триггера 124 через выход 125 поступает на информационный

5 вход регистра 3. По следующему

синхросигналу СИ1 состояние второго триггера 124 вдвигается в регистр 3. Одновременно по синхросигналу СИ1, поступающему на вход 48, сбрасьшает0 ся первьй триггер 123. Когда в регистре 3 накопится полньй символ,, блок 5 вьщеления и идентификации символа вьщает на вход 103 сигнал сброса, который сбрасьшает второй триггер 124.

Таким образом в данном устройстве реализована возможность оперативно изменять (исправлять) информацию в памяти микропрограмм, что повышает

0 его быстродействие по сравнению с прототипом, в котором изменение информации в памяти микрокоманд возможно лишь после изменения ее на внешнем накопителе.

I

Pus.Z

78-8181

PtL

9J

53

Т 57

iJ2

т

75

us 3

Фе/гЛ

f21

т

/5 ff3

B

50 98

ГУ

фи,У

12В

Физ.7 JTJ

Фиг. в lJTjnJTJTJnJTJ

2LKicsoo - 22

о o 1 С. t to to o iS «o oc. oci « to

r

J С

на Ou

% (g «О QO

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Теплица | 1983 |

|

SU1258972A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Внешние устройства ЭВМ | |||

| М., Мир, 1977, с | |||

| Способ применения поваренной соли в нагревательной закалочной ванне при высоких температурах | 1923 |

|

SU412A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-15—Публикация

1983-01-27—Подача