Изобретение относится к измерительной и вычислительной технике и может быть использовано в информационно-измерительных системах.

Известен аналого-цифровой преобразователь, содержащий аналоговое запоминающее устройство, источник опорного напряжения и ряд последовательно включенных кодирующих каскадов, каждый из которых состоит из компаратора и блока взвешенного суммирования, последний каскад состоит только из компаратора, причем вход измеряемой величины преобразователя соединен со входом аналогового запоминающего устройства, управляющий вход которого соединен со стробирующим входом преобразователя, выход аналогового запоминающего устройства соединен с первым входом компаратора и первым входом блока взвешенного суммирования первого кодирующего каскада, выход каждого блока взвешенного суммирования соединен с

первым входом компаратора и первым входом блока взвешенного суммирования последующего каскада, причем блок взвешенного суммирования содержит два усилителя и два источника опорного напряжения.

Недостатком известного устройства является его сложность.

Наиболее близким к изобретению является аналого-цифровой преобразователь, содержащий источник опорного напряжения и ряд последовательно включенных кодирующих каскадов, каждый из которых состоит из компаратора, первый вход которого соединен с выходом предыдущего каскада, причем первый вход компаратора первого каскада соединен с шиной преобразуемого сигнала, а прямой выход - с управляющим входом первого переключателя, первый вход которого соединен с шиной нулевого потенциала, а выход - с первым входом блока взвешенного суммирования,

ел

С

4 00 С О О

второй вход которого соединен с выходом предыдущего каскада, последний каскад состоит только из компаратора, вторые входы первых переключателей всех каскадов объединены.

Недостатком известного устройства является невозможность преобразования биполярных сигналов.

Цель изобретения - расширение диапазона преобразуемых сигналов, а также обеспечение дополнительной возможности измерения разности аналоговых сигналов.

Указанная цель достигается тем, что аналого-ц ифровой преобразователь содержит источник опорного напряжения и последовательно соединенные п кодирующих каскадов,( п-1) из которых содержат компаратор, переключатель и блок взвешенного суммирования, а n-й кодирующий каскад содержит n-й компаратор, первый вход каждого i-ro компаратора, кроме первого, соединен с выходом (Н)-го блока взвешенного суммирования, первый вход первого компаратора соединен с входной шиной преобразователя, вторые входы всех компараторов объединены, а выход каждого i-ro компаратора подключен к управляющему входу i-ro переключателя, первый вход которого соединен с шиной нулевого потенциала, а выход - с первым входом i-ro блока взвешенного суммирования, второй вход которого соединен с первым входом i-ro компаратора, вторые входы переключателей всех кодирующих каскадов объединены и подключены к выходу источника опорного напряжения, а также вторую входную шину преобразователя, которая соединена с объединенными вторыми входами всех компараторов, а каждый из переключателей выполнен сдвоенным и содержит дополнительно второй переключатель, первый и второй входы которого соединены соответственно со вторым и первым входами первого переключателя, а выход второго переключателя соединен с третьим входом соответствующего блока взвешенного суммирования.

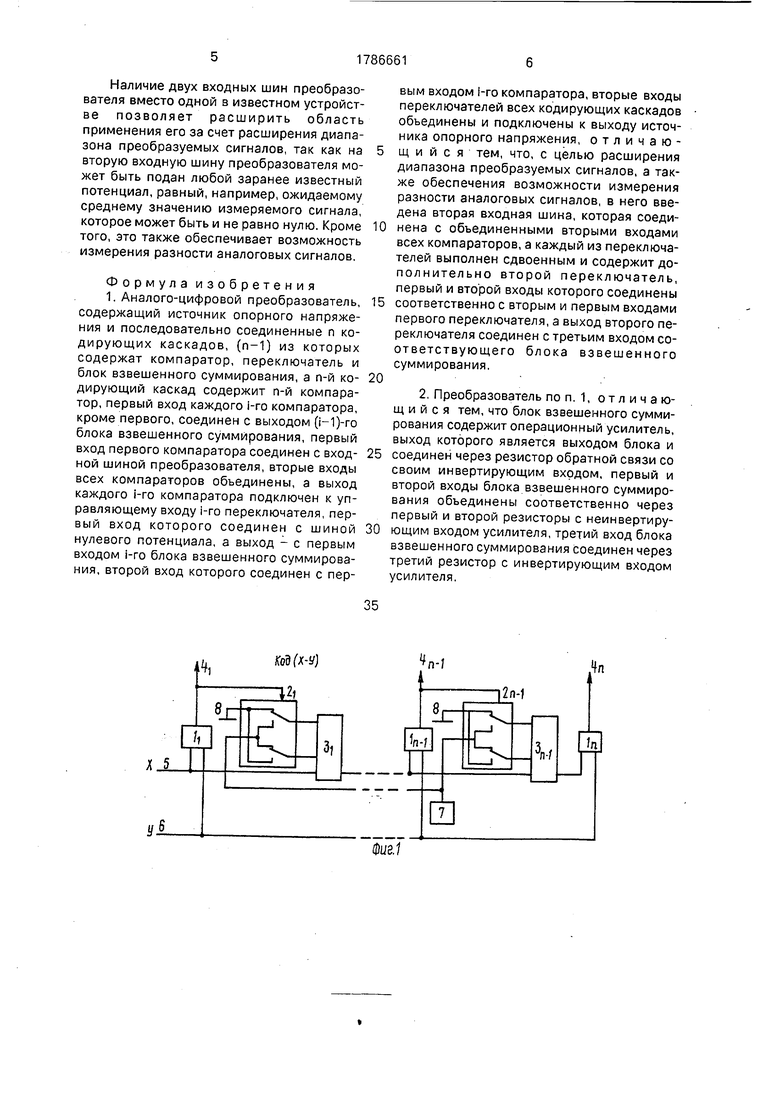

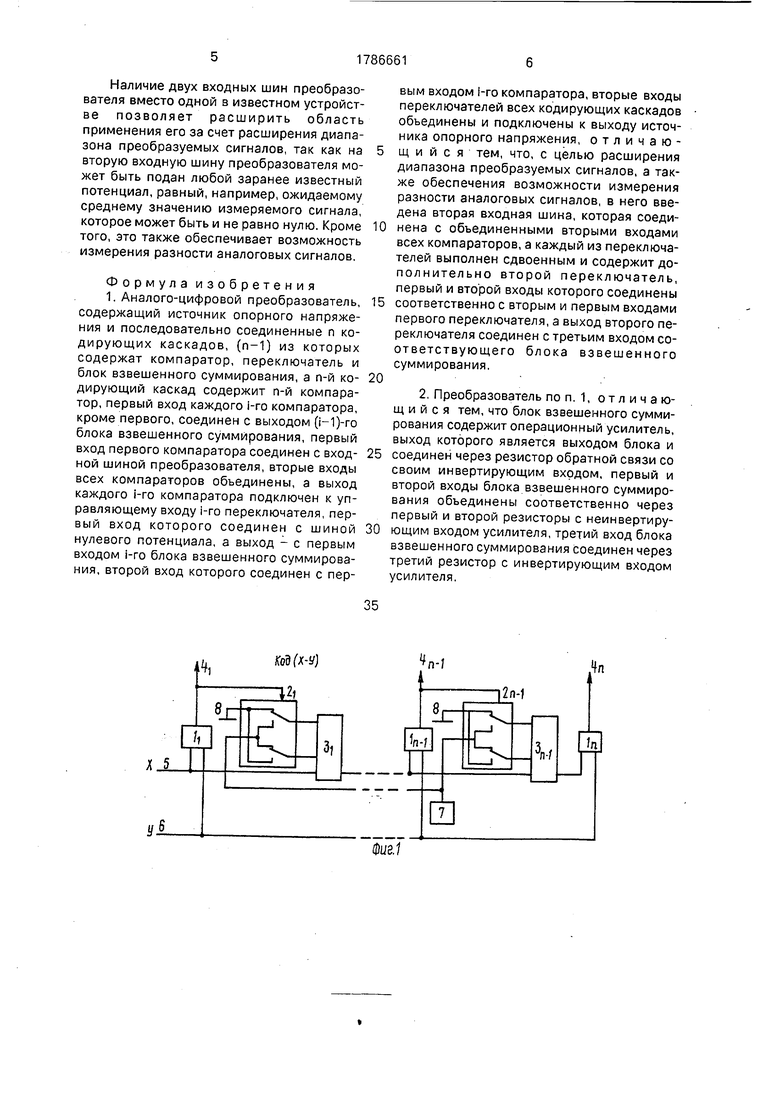

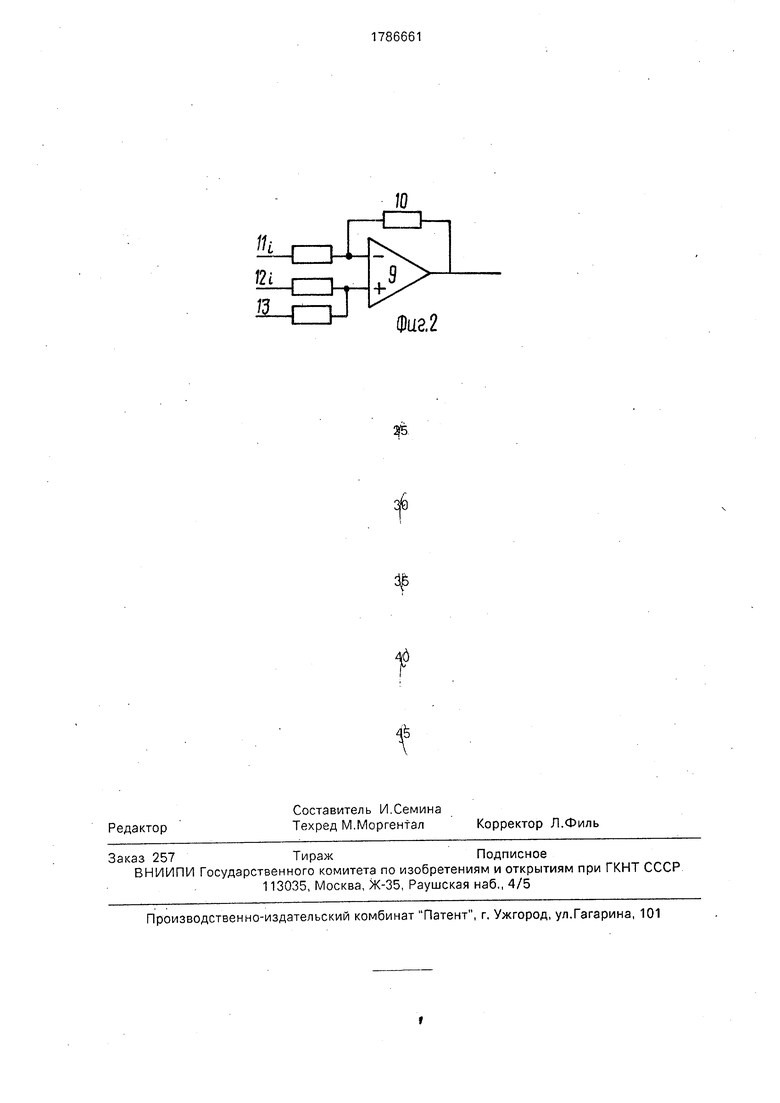

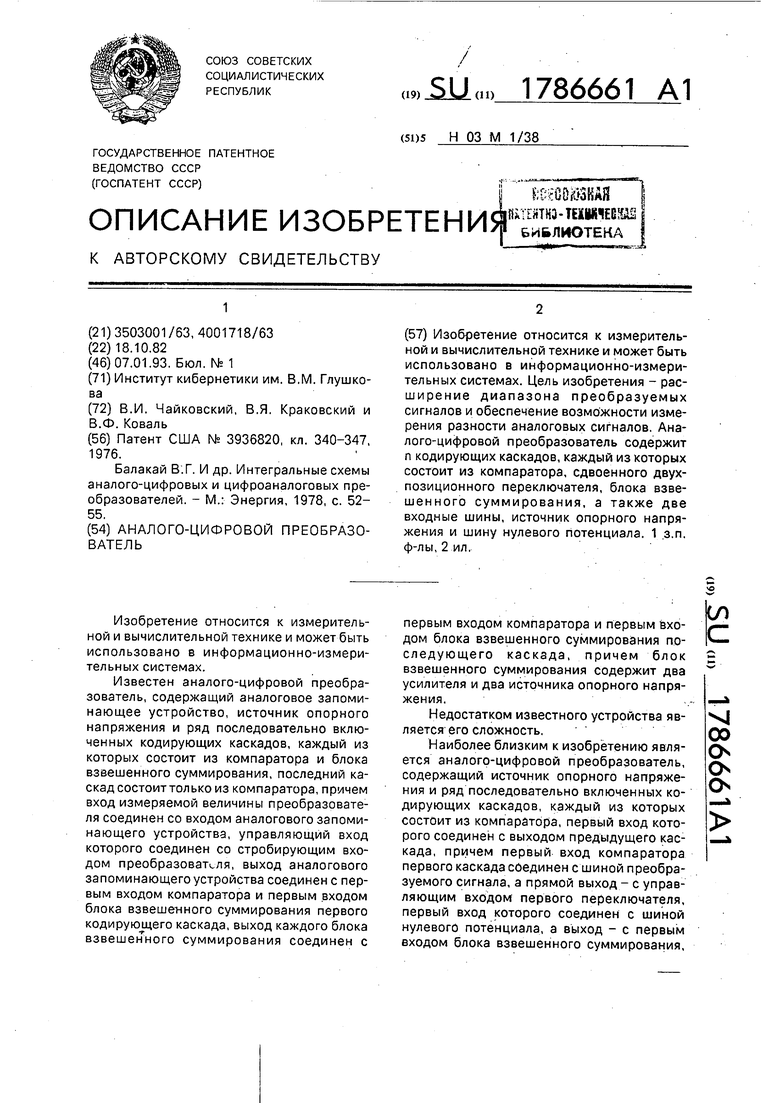

На фиг. 1 представлена функциональная схема аналого-цифрового преобразователя; на фиг. 2 - пример выполнения блока взвешенного суммирования.

Преобразователь содержит п кодирующих каскадов, каждый из которых состоит из компаратора 1i-1n, сдвоенного двухпо- зиционного переключателя 2i-2n-i, блока 3-|-Зп-1 взвешенного суммирования и выходов 4i-4n компараторов 1i-1n, а также в преобразователь входят две входные шины 5 и 6, источник 7 опорного напряжения и шина 8 нулевого потенциала.

Блок 3i взвешенного суммирования состоит из операционного усилителя 9 с резистором 10 обратной связи и входными резисторами 11j, 12|и 13, 5Преобразователь работает следующим образом.

На входные шины 5 и 6 преобразователя с помощью внешних устройств (например, аналоговых запоминающих устройств)

0 или непосредственно подаются потенциалы X и У аналоговых сигналов. Через некоторое небольшое время (время преобразования) на выходах 4-|-4п должен появиться цифровой код разности потенциалов Х-У.

5 Значение Е потенциала источника 7 опорного напряжения, равное половине диапазона измерения этой разности, подается на средние неподвижные контакты всех сдвоенных двухпозиционных переключате0 лей 2i 0 е 1, п-1). Компаратор 1i первого кодирующего каскада определяет знак (Х-У), выдает его на выход 4i и в зависимости от этого знака так управляет сдвоенным двух- позиционным переключателем 2т, чтобы на

5 выходе блока 3i взвешенного суммирования было получено значение Xi, удовлетворяющее условиям

slgn(X-Y)0 5 Xi X-E/2;

sign (X-Y) 0 E/2.(1)

0 На выходе каждого следующего i-ro каскада (i е 2, n-1) аналогично получаются значения:

sign (XM-Y) 0 ХгХм-Е/21;

sign (XM-Y) 0 Xi Xi-i+ E/21 (2)

5 В последнем кодирующем каскаде компаратор 1П определяет знак величины (Хп-1- -Y) и подает его значение на выход 4П.

Для выполнения вычислений по формулам (1) и (2) служат блоки 3i-3n-i взвешен0 ного суммирования, в которых значения сопротивлений резисторов 11| и удовлетворяют условиям:

Rio Ri3 R; , iel.n-1,(3)

5 где R - величина резистора обратной связи. Выходной код преобразователя представляет собой знакоразрядный код разности (X-Y) на выходах компараторов 1i-1n, т.е. {sign (X-Y), sign (Xi-Y), ... sign (Xn-i-Y).

0

Для перехода от этого знакоразрядно- го кода к обычному двоичному коду достаточно приписать числу знак старшего разряда, остальные разряды проинвертиро5 вать и сдвинуть их на один разряд влево, в освободившийся младший разряд записать единицу, в результате получается сразу дополнительный код, причем дополнительных аппаратурных затрат для такого преобразования не требуется.

Наличие двух входных шин преобразователя вместо одной в известном устройстве позволяет расширить область применения его за счет расширения диапазона преобразуемых сигналов, так как на вторую входную шину преобразователя может быть подан любой заранее известный потенциал, равный, например, ожидаемому среднему значению измеряемого сигнала, которое может быть и не равно нулю. Кроме того, это также обеспечивает возможность измерения разности аналоговых сигналов.

Формула изобретения 1. Аналого-цифровой преобразователь, содержащий источник опорного напряжения и последовательно соединенные п кодирующих каскадов, (п-1) из которых содержат компаратор, переключатель и блок взвешенного суммирования, а n-й ко- дирующий каскад содержит n-й компаратор, первый вход каждого i-ro компаратора, кроме первого, соединен с выходом (Ы)-го блока взвешенного суммирования, первый вход первого компаратора соединен с вход- ной шиной преобразователя, вторые входы всех компараторов объединены, а выход каждого 1-го компаратора подключен к управляющему входу 1-го переключателя, первый вход которого соединен с шиной нулевого потенциала, а выход - с первым входом i-ro блока взвешенного суммирования, второй вход которого соединен с первым входом 1-го компаратора, вторые входы переключателей всех кодирующих каскадов объединены и подключены к выходу источника опорного напряжения, отличающийся тем, что, с целью расширения диапазона преобразуемых сигналов, а также обеспечения возможности измерения разности аналоговых сигналов, в него введена вторая входная шина, которая соединена с объединенными вторыми входами всех компараторов, а каждый из переключателей выполнен сдвоенным и содержит до- полнительно второй переключатель, первый и второй входы которого соединены соответственно с вторым и первым входами первого переключателя, а выход второго переключателя соединен с третьим входом соответствующего блока взвешенного суммирования.

2. Преобразователь по п. 1, отличающийся тем, что блок взвешенного суммирования содержит операционный усилитель, выход которого является выходом блока и соединен через резистор обратной связи со своим инвертирующим входом, первый и второй входы блока взвешенного суммирования объединены соответственно через первый и второй резисторы с неинвертирующим входом усилителя, третий вход блока взвешенного суммирования соединен через третий резистор с инвертирующим входом усилителя.

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1322475A1 |

| Устройство для преобразования прямоугольных координат в полярные | 1979 |

|

SU781834A1 |

| Цифроаналоговый преобразователь с коммутацией тока | 1982 |

|

SU1084983A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1401608A2 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| Функциональный аналого-цифровой преобразователь | 1990 |

|

SU1809531A1 |

| ЦИФРОАНАЛОГОВЫЙ ГЕНЕРАТОР ШУМА | 2014 |

|

RU2549174C1 |

| Функциональный аналого-цифровой преобразователь | 1990 |

|

SU1809532A1 |

| ЦИФРОАНАЛОГОВЫЙ ГЕНЕРАТОР ШУМА | 2014 |

|

RU2559719C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

Изобретение относится к измерительной и вычислительной технике и может быть использовано в информационно-измерительных системах. Цель изобретения - расширение диапазона преобразуемых сигналов и обеспечение возможности измерения разности аналоговых сигналов. Аналого-цифровой преобразователь содержит п кодирующих каскадов, каждый из которых состоит из компаратора, сдвоенного двух- позиционного переключателя, блока взвешенного суммирования, а также две входные шины, источник опорного напряжения и шину нулевого потенциала. 1 ,з.п. ф-лы, 2 ил,

| Патент США № 3936820, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Балакай В.Г | |||

| И др | |||

| Интегральные схемы аналого-цифровых и цифроаналоговых преобразователей | |||

| - М.: Энергия, 1978, с | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

Авторы

Даты

1993-01-07—Публикация

1982-10-18—Подача