Изобретение относится к измерительной и вычислительной технике и может быть использовано в различных информационно-измерительных системах

Цель изобретения - расширение области прш-5енения за счет расширения диапазона преобразуемых сигналов и повьш1ение точности преобразования.

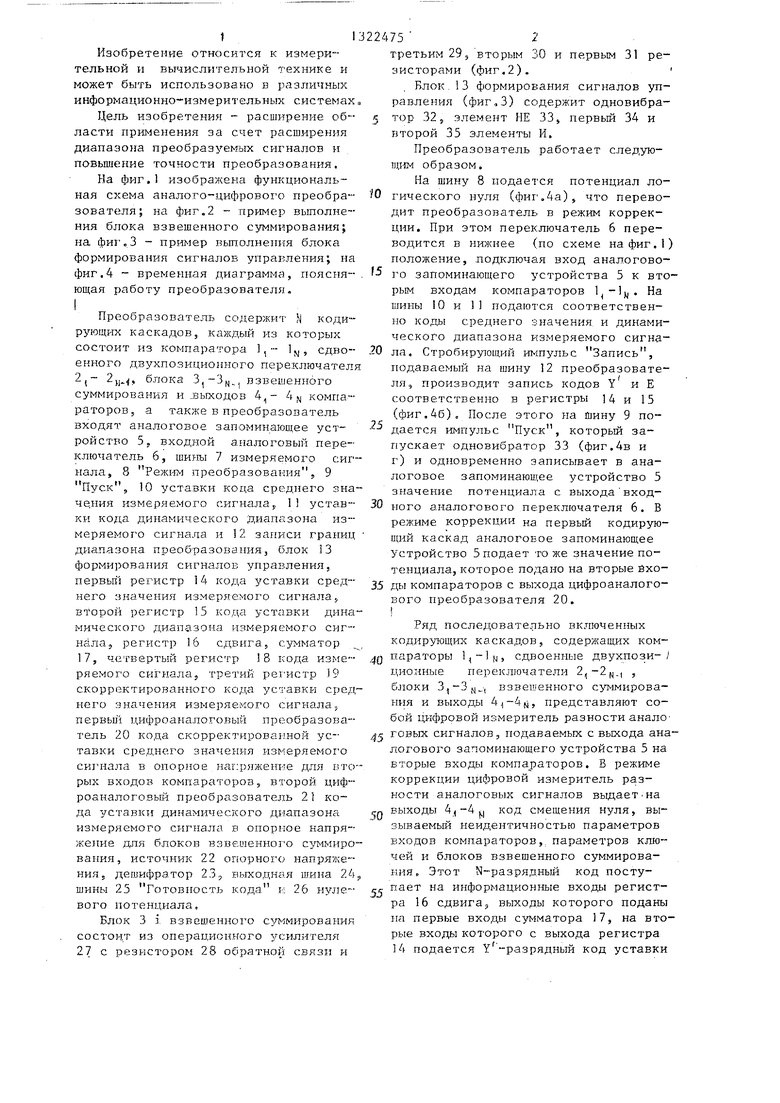

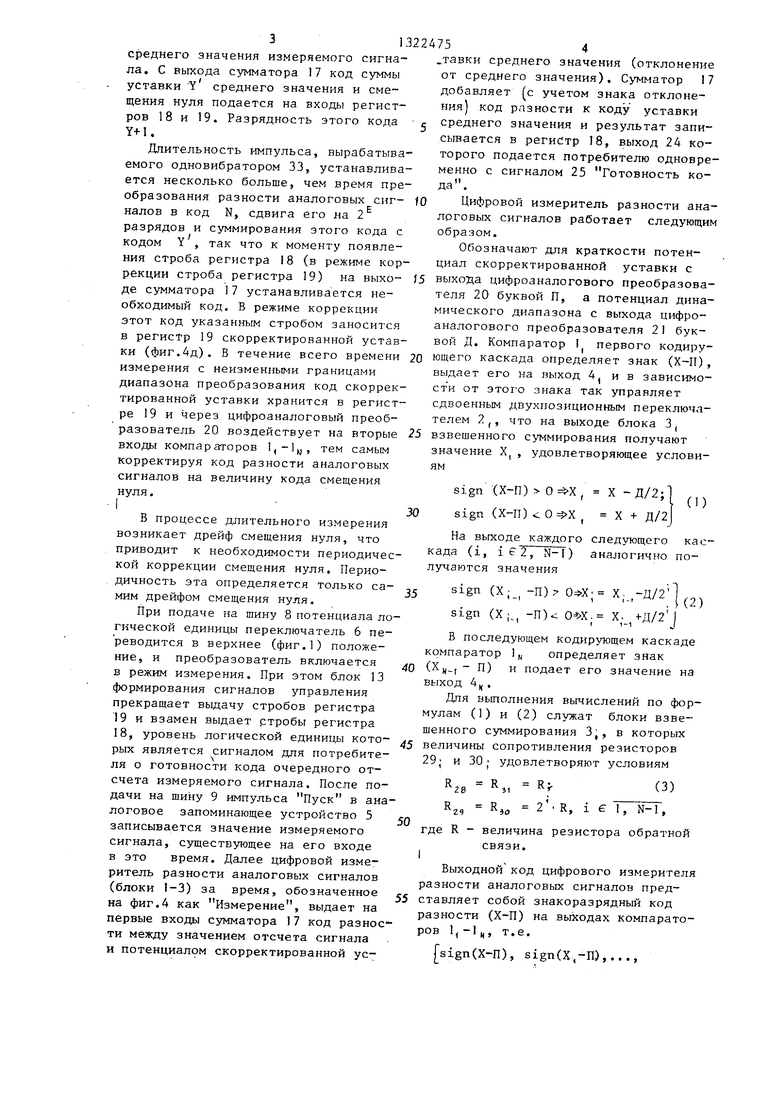

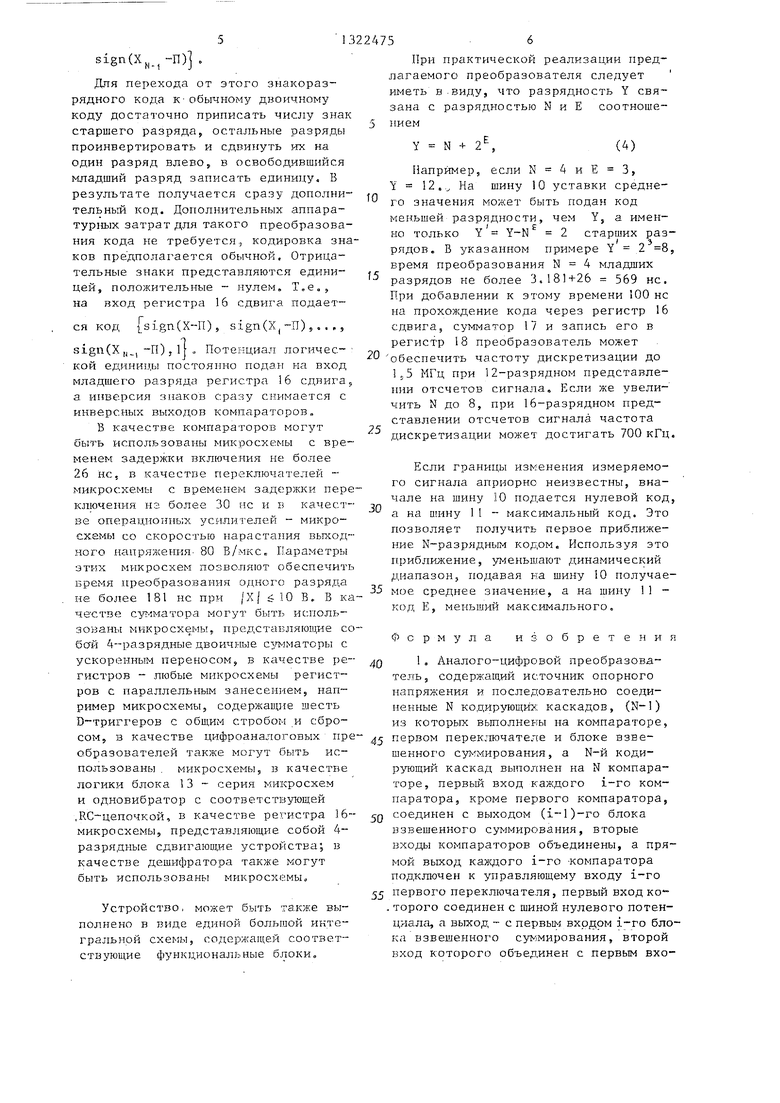

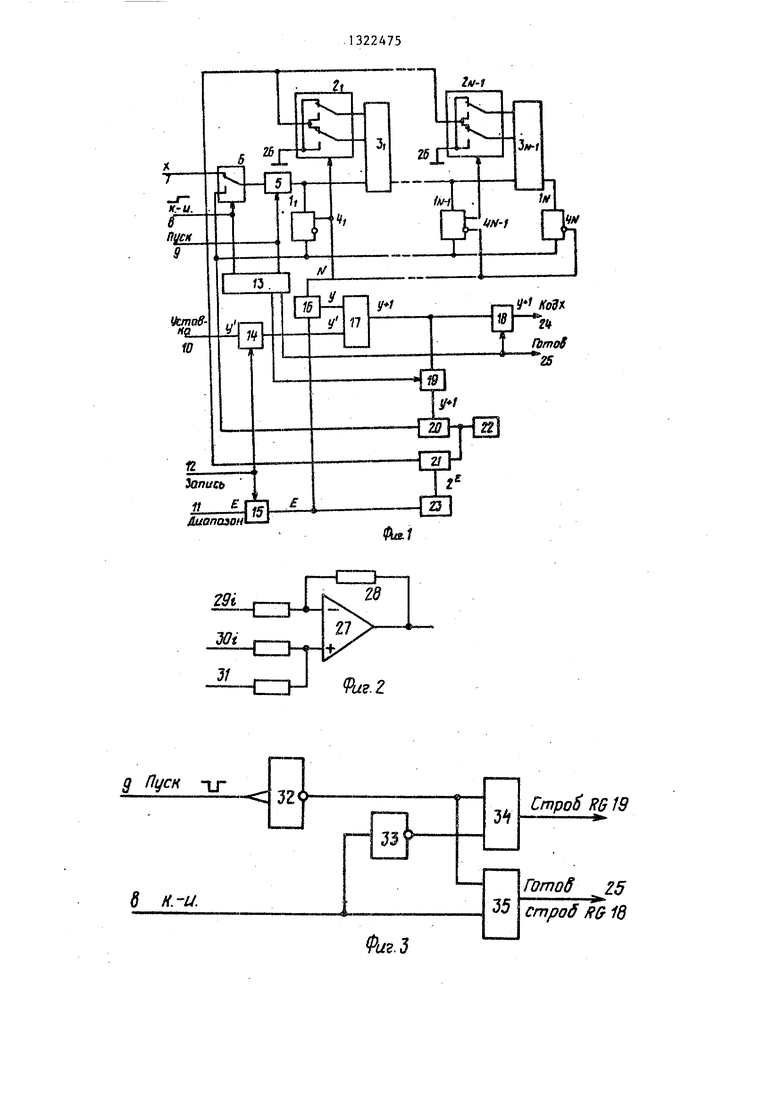

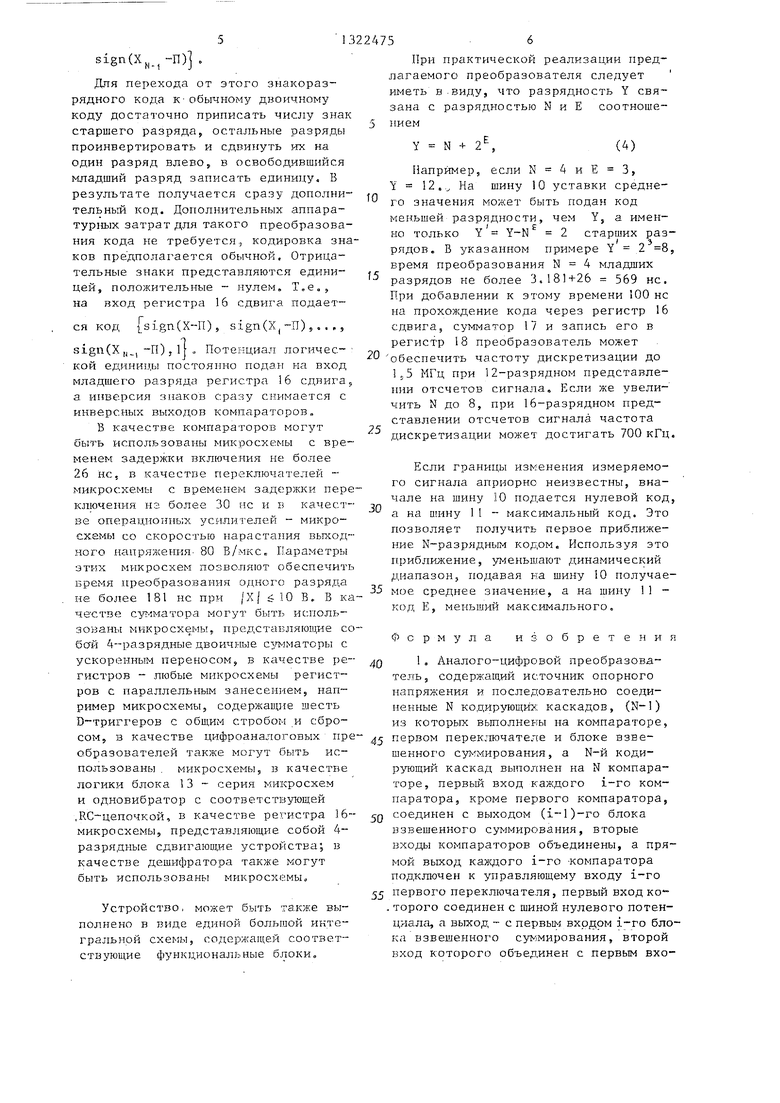

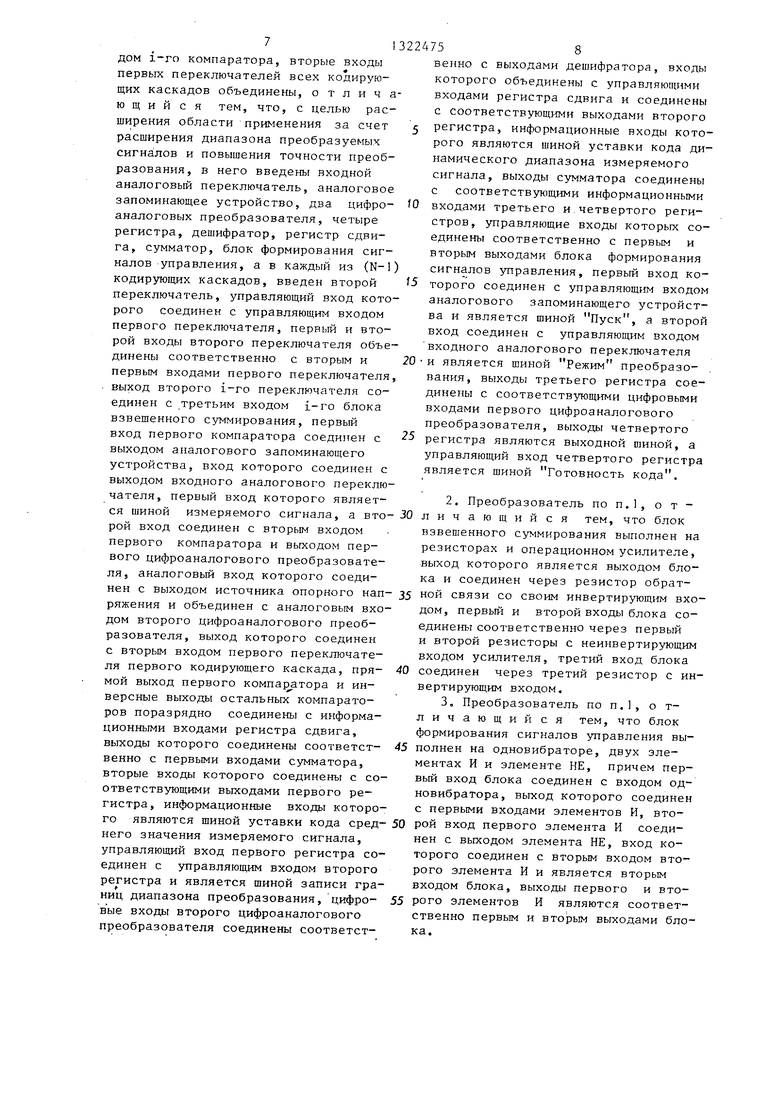

На фиг,1 изображена функциональная схема аналого-цифрового преобразователя; на фиг.2 - пример выполнения блока взвешенного суммирования; на фиг.З - пример выполнения блока формирования сигналов управления; на фиг.4 временная диаграмма, поясня- ющая работу преобразователя,

I

Преобразователь содержит Jj кодирующих каскадов, каждый из которых состоит из компаратора 1,- 1,, сдво-- енного двухпозиционного переключател ( блока 3,-3ц,, взвешенного суммирования и .выходов 4,- 41 компараторов, а также в преобразователь входят аналоговое запоминающее устройство 5; входной аналоговый переключатель 6, ШИР1Ы 7 измеряемого сигнала, 8 Режим преобразования, 9 Пуск, 10 уставки кода среднего значения измеряемого сигнала,, 11 уставки кода динамического диапазона измеряемого сигнала и 12 записи границ диапазона преобразования, блок 13 формировагп я сигналов управления, первьп регистр 14 кода уставки среднего значения измеряемого сигнала, второй регистр 15 кода уставки динамического диапазона измеряемого сиг- нг1ла5 регистр 16 сдвига, сумматор 17, четвертый регистр 8 кода измеряемого сигналаJ третий рег истр 19 скорректированного кода уставки среднего значения измеряемого сигнала,, первый цифроаналоговый преобразователь 20 кода скорректированной уставки среднего значения измеряемого сигнала в опорное напряжение для вто рых входов компараторов, второй цифроаналоговый преобразователь 21 кода 7/ставки динамичеслсого диапазона измеряемого с1-1гнала в опорное напря- жепие ) блоков взвеишнног о суммирования, источник 22 опорного напряжения , дешифратор 23, выходная шина 24 шины 25 Готовность кода. н 26 нулевого потенциала.

Блок 3 3. взвешенно1 О сз ммированик соетои.т из операцион.мого усилителя 27 с резистором 28 обратной связи и

третьим 29 5 вторым 30 и первым 31 резисторами (фиг.2), Блок.13 формирования сигналов управления (фиг„3) содержит одновибратор 325 злемент НЕ 33, первый 34 и второй 35 элементы И,

Преобразователь работает следующим образом.

На шину 8 подается потенциал логического нуля (фиг .4а)5 что переводит преобразователь в режим коррекции. При этом пере1 :лючатель 6 переводится в нижнее (по схеме на фиг.1) положение, .подключая вход аналогового запоминающего устройства 5 к вторым входам компараторов . На шины 10 и 11 подаются соответственно коды среднего значения и динамического диапазона измеряемого сигнапа, Стробирующий импульс Запись, подаваемый на шину 12 преобразователя, производит запись кодов Y и Е соответственно в регистры 14 и 15 (фиг.4б). После этого на Шину 9 подается импульс Пуск, который запускает одновибратор 33 (фиг.4в и г) и одновременно записьшает в аналоговое запоминающее устройство 5 значение потенциала с выхода вход-

ного аналогового переключателя 6. В режиме коррекции на первый кодирующий каскад аналоговое запоминающее устройство 5 подает тоже значение потенциала, которое подано на вторые ёходы компараторов с выхода цифроаналогового преобразователя 20.

I

Ряд последовательно включенных кодирующих каскадов, содержащих компараторы 1,-lfj, сдвоенные двухпози-/ ционные переклЕочатели , , блоки 3,-3fj, взвешенного суммирования и выходы 4.|-4(j, представляют собой цифровой измеритель разности акалоговых сигналов, подаваемых с выхода аналогового запоминающего устройства 5 на вторые входы компараторов, В режиме коррекции цифровой измеритель разности аналоговых сигналов вьщаеТ На

выходы 4(-4|,| код смещения нуля, вызываемый неидентичностью параметров входов компараторов,, параметров ключей и блоков взвешенного суммирования. Этот N-разрядньй код посту..55

. пает на информационные входы регистра 16 сдвигаJ выходы которого поданы на первые входы сумматора 17, на вторые входы которого с выхода регистра 14 подается Y -разрядный код уставки

среднего значения измеряемого сигнала. С выхода сумматора 17 код суммы уставки Y среднего значения и смещения нуля подается на входы регистров 18 и 19. Разрядность этого кода Y-H.

Длительность импульса, вырабатываемого одновибратором 33, устанавливается несколько больше, чем время преобразования разности аналоговых сиг- налов в код N, сдвига его на 2 разрядов и суммирования этого кода с кодом Y , так что к моменту появления строба регистра 18 (в режиме коррекции строба регистра 19) на выхо- де сумматора 17 устанавливается необходимый код. В режиме коррекции этот код указанным стробом заносится в регистр 19 скорректированной уставки (фиг.4д). В течение всего времени измерения с неизменными границами диапазона преобразования код скорректированной уставки хранится в регистре 19 и через цифроаналоговый преобразователь 20 воздействует на вторые входы компараторов 1,-, тем самым корректируя код разности аналоговых сигналов на величину кода смещения нуля.

В процессе длительного измерения возникает дрейф смещения нуля, что приводит к необходимости периодической коррекции смещения нуля. Периодичность эта определяется только самим дрейфом смещения нуля.

При подаче на щину 8 потенциала логической единицы переключатель 6 переводится в верхнее (фиг.1) положение, и преобразователь включается в режим измерения. При этом блок 13 формирования сигналов управления прекращает выдачу стробов регистра 19 и взамен выдает ртробы регистра 18, уровень логической единицы которых является сигналом для потребителя о готовности кода очередного отсчета измеряемого сигнала. После подачи на шину 9 импульса Пуск в аналоговое запоминающее устройство 5 записывается значение измеряемого сигнала, существующее на его входе в это время. Далее цифровой измеритель разности аналоговых сигналов (блоки 1-3) за время, обозначенное на фиг.4 как Измерение, выдает на первые входы сумматора 17 код разности между значением отсчета сигнала и потенциалом скорректированной ус.тавки среднего значения (отклонение от среднего значения). Сумматор 17 добавляет с учетом знака отклонения) код разности к коду уставки среднего значения и результат записывается в регистр 18, выход 24 которого подается потребителю одновременно с сигналом 25 Готовность ко- да.

Цифровой измеритель разности аналоговых сигналов работает следующим образом.

Обозначают для краткости потенциал скорректированной уставки с выхода цифроаналогового преобразователя 20 буквой П, а потенциал динамического диапазона с выхода цифро- аналогового преобразователя 21 буквой Д. Компаратор 1 первого кодирующего каскада определяет знак (Х-П), выдает его на выход 4 ив зависимо- ст и от этог О знака так управляет сдвоенным двухпозиционным переключателем 2, что на выходе блока 3 взвешенного суммирования получают значение X , удовлетворяющее условиям

sign (Х-П) , sign (Х-П) ОФХ

(I)

На выходе каждого следующего каскада (i, it 2, N-) аналогично получаются значения

(2)

sign (X; , -П) ОФХ X. -Д/2

-I1 I - г

sign (Х;,, -П) . Х.+Д/2 | В последующем кодирующем каскаде

компаратор 1.

определяет знак

(N-1 П) и подает его значение на выход 4.

Для вьтолнения вычислений по формулам (1) и (2) служат блоки взвешенного суммирования 3, в которых величины сопротивления резисторов 29 и 30 удовлетворяют условиям

0

5

R R,

28

R,

R.

Rf

2.R,

(3)

i € , N-1,

гч )o где R - величина резистора обратной

связи, I

Выходной код цифрового измерителя разности аналоговых сигналов представляет собой знакоразрядный код разности (Х-П) на выходах компараторов 1, -I ц, т.е.

sign(X-n), sign(X,-n),

sign(X,-n) .

Для перехода от этого знакораз- рядного кода к- обычному двоичному коду достаточно приписать числу знак старшего разряда,, остальные разряды проинвертировать и сдвинуть их на один разряд влево5 в освободивши.йся младший разряд записать единицу. В результате получается сразу дополнительный код. Дополнительных аппаратурных затрат для такого преобразования кода не требуется, кодировка знаков предполагается обычной. Отрицательные знаки представляются единицей, положительные - нулем. Т.е., на вход регистра 16 сдвига подается код, (X--Il) 5 sign(X|-П) 5.. ,,

1 sign(X, n)j И „ Потенциал логичес-

кой единицы постоят-то но дан на вход младшего разряда регистра 16 сдвига, а инверсия знаков сразу снимается с инверсных выходов компараторов,,

В качестве компараторов могут быть использованы микросхемы с временем задержки включения не более 26 НС, в качестве переключателей микросхемы с временем задержки нере- ключения нз более 30 ис и в качестве операционных усилителей - микро- схемгз со скоростью нарастания выходного напряжения 80 В/:мкс. П.араметрь этих микросхем позволяют обеспечить Бремя преобразования одного рс13ря,ца не более 181 не при , Х/ 10 В. В качестве c SfL-iMaTOpa могут быть ис;поль- зованы микросхемы, нредставляюидие со- бай 4-разрядные двоичные сзп маторы с ускоренным переносом, в качестве регистров любые микросхемы регистров с параллельным занесением, ример микросхемы, содержащие шесть В триггеров с обш,им стробом и сбро13224756

При практической реализации предлагаемого преобразователя следует иметь в.виду, что разрядность Y связана с разрядностью N и Е соотношением

10

Y N + 2

(А)

f5

Например, если N 4 и Е 3, Y 12,, На шину 10 уставки среднего значения может быть подан код меньшей разрядности, чем Y, а именно только Y Y-N 2 старших разрядов. В указанном примере Y 2 8, время преобразования N 4 младших

20

разрядов не более 3,181+26 569 не, При добавлении к этому времени 100 не на прохождение кода через регистр 16 сдвига, сумматор 17 и запись его в регистр 18 преобразователь может обеспечить частоту дискретизации до 1.5 МГц при 12-разрядном представлении отсчетов сигнала. Если же увеличить N до 8, нри 16-разрядном нред- ставлении отсчетов сигнала частота дискретизации может достигать 700 кГц.

Если границы изменения измеряемого сигнала априорно неизвестны, вначале на шину 10 подается нулевой код, а на П1ину 1 I - максимальный код. Это позволяет получить первое приближение N-разрядным кодом. Используя это приближение, уменьшают динамический диапазон, подавая на шину 10 нолучае- .35 мое среднее значение, а на шину 1 1 - код Е, меньший максимального.

Формула изобретения

4Q 1. Аналого-цифровой преобразователь, содержащий источник опорного напряжения и последовательно соединенные N кодирующи : каскадов, (N-1) из которых выполнены на компараторе,

30

сом, в качестве цифроаналоговых нре- первом переключателе и блоке взвеобразователей также могут быть использованы . микросхемы, в качестве логики блока 13 - серия микросхем и одновибратор с соответствутош;ей ,ЕС-цепочкой, в качестве рех истра 16- микросхемы, представляющие собой 4- разря,цные сдвигающие устройства; в качестве дешифратора также могут быть использованы микросхемы.

Устройство, может быть также выполнено в виде единой большой интегральной схемы, содержащей соответствующие функциональные блоки.

шейного су мирования, а N-й кодирующий каскад выполнен на N компара торе, первьш вход каждого i-ro ком наратора, кроме пеЕ)Вого компаратора

5Q соединен с выходом (i-l)-ro блока взвешенного суммирования, вторые входы компараторов объединены, а пр мой выход каждого i-ro -компаратора подключен к управляющему входу i-ro

55 первого переключателя, первый вход ко . торого соединен с шиной нулевого поте циала, а выход - с первьм входом i-ro б ка взвешенного су1У1Мирования, второ вход которого объединен с первым вх

Y N + 2

(А)

Например, если N 4 и Е 3, Y 12,, На шину 10 уставки среднего значения может быть подан код меньшей разрядности, чем Y, а именно только Y Y-N 2 старших разрядов. В указанном примере Y 2 8, время преобразования N 4 младших

разрядов не более 3,181+26 569 не, При добавлении к этому времени 100 не на прохождение кода через регистр 16 сдвига, сумматор 17 и запись его в регистр 18 преобразователь может обеспечить частоту дискретизации до 1.5 МГц при 12-разрядном представлении отсчетов сигнала. Если же увеличить N до 8, нри 16-разрядном нред- ставлении отсчетов сигнала частота дискретизации может достигать 700 кГц.

Если границы изменения измеряемого сигнала априорно неизвестны, вначале на шину 10 подается нулевой код, а на П1ину 1 I - максимальный код. Это позволяет получить первое приближение N-разрядным кодом. Используя это приближение, уменьшают динамический диапазон, подавая на шину 10 нолучае- мое среднее значение, а на шину 1 1 - код Е, меньший максимального.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий источник опорного напряжения и последовательно соединенные N кодирующи : каскадов, (N-1) из которых выполнены на компараторе,

шейного су мирования, а N-й кодирующий каскад выполнен на N компараторе, первьш вход каждого i-ro ком- наратора, кроме пеЕ)Вого компаратора,

5Q соединен с выходом (i-l)-ro блока взвешенного суммирования, вторые входы компараторов объединены, а прямой выход каждого i-ro -компаратора подключен к управляющему входу i-ro

55 первого переключателя, первый вход ко . торого соединен с шиной нулевого потенциала, а выход - с первьм входом i-ro блока взвешенного су1У1Мирования, второй вход которого объединен с первым входом 1-го компаратора, вторые входы первых переключателей всех кодирующих каскадов объединены, о т л и ч а ю щ и и с я тем, что, с целью расширения области применения за счет расширения диапазона преобразуемых сигна лов и повышения точности преобразования, в него введе а. входной аналоговый переключатель, аналоговое запоминающее устройство, два цифро- аналоговых преобразователя, четыре регистра, дешифратор, регистр сдвига, сумматор, блок формирования сигналов управления, а в каждый из (N-1 кодирующих каскадов, введен второй переключатель, управляющий вход кото рого соединен с управляющим входом первого переключателя, первьй и второй входы второго переключателя объе динены соответственно с вторым и первым входами первого переключателя выход второго i-ro переключателя соединен с третьим входом i-ro блока взвешенного суммирования, первый вход первого компаратора соединен с выходом аналогового запоминающего устройства, вход которого соединен с выходом входного аналогового переключателя, первый вход которого является шиной измеряемого сигнала, а второй вход соединен с вторым входом первого компаратора и выходом первого цифроаналогового преобразователя, аналоговый вход которого соединен с выходом источника опорного напряжения и объединен с аналоговым входом второго цифроаналогового преобразователя, выход которого соединен с вторым входом первого переключателя первого кодирующего каскада, прямой выход первого компаратора и инверсные выходы остальных компараторов поразрядно соединены с информационными входами регистра сдвига, выходы которого соединены соответственно с первыми входами сумматора, вторые входы которого соединены с со- ответств-ующими выходами первого регистра, информационные входы которого являются шиной уставки кода среднего значения измеряемого сигнала, управляющий вход первого регистра соединен с управляющим входом второго регистра и является шиной записи границ диапазона преобразования, цифровые входы второго цифроаналогового преобразователя соединены соответст224758

венно с выходами дешифратора, входы которого объединены с управляющими входами регистра сдвига и соединены с соответствующими выходами второго

регистра, информационные входы которого являются шиной уставки кода динамического диапазона измеряемого сигнала, выходы сумматора соединены с соответствующими информационными

Ш входами третьего и.четвертого регистров, управляющие входы которых соединены соответственно с первым и вторым выходами блока формирования сигналов -управления, первый вход ко 5 торого соединен с управляющим входом

аналогового запоминающего устройства и является шиной Пуск, а второй вход соединен с управляющим входом

входного аналогового переключателя 20и является шиной Режим преобразования, выходы третьего регистра соединены с соответствующими цифровыми входами первого цифроаналогового преобразователя, выходы четвертого 5 регистра являются выходной шиной, а управляющий вход четвертого регистра является шиной Готовность кода,

2.Преобразователь по п., о т - 30 л и чающийся тем, что блок

взвешенного суммирования выполнен на резисторах и операционном усилителе, выход которого является выходом блока и соединен через резистор обрат35 ой связи со своим инвертирующ входом, первый и второй входы блока соединены соответственно через первый и второй резисторы с неинвертирующим входом усилителя, третий вход блока 40 соединен через третий резистор с инвертирующим входом,

3,Преобразователь по п., о т- личающий ся тем, что блок формирования сигналов управления вы45 полнен на одновибраторе, двух элементах И и элементе НЕ, причем первый вход блока соединен с входом од- новибратора, выход которого соединен с первыми входами элементов И, вто50 рой вход первого элемента И соединен с выходом элемента НЕ, вход которого соединен с вторым входом второго элемента И и является вторым входом блока, выходы первого и вто- 55 рого элементов И являются соответственно первым и вторым выходами блока.

Ь

26

К:-и.

г

Пуск 9

ч,

aJj

У

Id

Уставке.

10

7

iH-l

п

ш

L-Jl

//yj

M-f

r-tS/ A oJX

ltfr- f

fbmoS

2ff

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1982 |

|

SU1786661A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1401608A2 |

| Устройство для преобразования прямоугольных координат в полярные | 1979 |

|

SU781834A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1078608A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Аналого-цифровой функциональный преобразователь | 1985 |

|

SU1298920A1 |

Изобретение относится к измерительной и вычислительной технике. Целью -изобретения является расширение области применения за счет расширения диапазона преобразуемых сигналов и повышение точности измерения. Преобразователь содержит источник опорного напряжения, ряд последовательно включенных кодирующих каскадов, каждый из которьк состоит из компаратора, сдвоенного двухпозици- онного переключателя и блока взвешенного суммирова1шя, последний каскад состоит только из компаратора, а также дополнительно введенные в него входной аналоговый переключатель, аналоговое запоминающее устройство, блок формирования сигналов управле-. ния, четыре регистра, регистр сдвига, сумматор, дешифратор и два циф- роаналоговых преобразователя. 2 з.п. ф-лы, 4 ил. С/)

П

Записи

ffg

Диапазон

{

/

.2

ff /7уся IT J

зг

5 /у.-//.

3

r/T7yt70i5 Л /5

J5

Гот off Z5

1

rm/7 P /5

Й/г.5

а 5 8 г д е

Редактор И. Горная

Составитель В. Солодова

Техред А.КравчукКорректор С, Шекмар

Заказ 2878/55Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.

| Автоматика , 1985, № 1, с | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Балакай В.Г | |||

| и др | |||

| Интегральные схемы АЦП и ЦАП | |||

| -М,: Энергия, 1978, с.52-53, рис.1-15. | |||

Авторы

Даты

1987-07-07—Публикация

1986-01-31—Подача