Фиг. 1

Изобретение относится к области вычислительной техники и может быть использовано в системах автоматизации диагностирования цифровых блоков ЭВМ.

Известен выходной узел тестера для контроля логических устройств, содержащий первый и второй ключи, два вентиля, триггер, элемент сравнения, первый и второй резисторы, третий и четвертый ключи, инвертор, сумматор, пять входных и две выходных шины с их связями.

Устройство является сложным и обладает ограниченными функциональными возможностями, так как предназначено для тестеров, контролирующих микросхемы с КМОП технологией изготовления.

Известен выходной узел тестера для контроля логических блоков, содержащий первый и второй ключи, первый и второй вентили, элемент сравнения, триггер, элемент И-НЕ, шесть входных и три выходных шины с их связями.

Недостатком этого устройства является его относительная сложность.

Наиболее близким по своей технической сущности к предлагаемому изобретению является выходной узел тестера для контроля логических устройств, содержащий два ключа, два элемента И и элемент сравнен ия, выходы ключей подсоединены к выходному контакту и к первому входу элемента сравнения, первые входы первого и второго ключей соединены соответственно с шинами логической единицы и логического нуля, а вторые входы - с выходами соответственно первого и второго элементов И, первая входная шина подключена ко втрро-. му входу элемента сравнения, к первому входу первого элемента И и через инвертор к первому входу второго элемента И, а вторые входы элементов И связаны со второй входной шиной. Узел содержит также триггер; выход которого соединен с третьими входами элементов И, выход элемента сравнения соединен с D-входом триггера, С-вход которого подключен к шине синхронизаТдийТ а инверсный S-вход связан со второй входной шиной.

Недостаток этого устройства заключается в ненадежной защите ключей узла от перегрузок при случайном замыкании выходной шины узла с шиной питания. Управление отключением ключей узла осуществляется через D-триггер, запись информации в который производится по фронту импульса синхронизации. Так как D-триггер изменяет свое состояние только через период следования синхроимпульсов, то в течение этого периода через ключи узла будет протекать значительный сквозной ток, который может вызвать повреждение ключей узла.

Цель изобретения - повышение надежности защиты устройства от перегрузок за

5 счет сокращения времени воздействия больших токов на выходные ключи.

Указанная цель достигается тем, что в выходной узел тестера для контроля цифровых блоков, содержащий два ключа, два эле0 мента И и элемент сравнения, выходы ключей подсоединены к выходному контакту и к первому входу элемента сравнения, первые входы первого и второго ключей соединены соответственно с шинами логиче5 ской единицы и логического нуля, в вторые входы -с выходами соответствен но первого и второго элементов И, первая входная шина подключена ко второму входу элемента сравнения, к первому входу первого эле0 мента И и через инвертор к первому входу второго элемента И, а вторые входы элементов И связаны со второй входной шиной, введены формирователь импульсов и элемент ИЛИ, выход которого подсоединен к

5 третим входам элементов И, первый вход - к выходу элемента сравнения, а второй вход - к выходу формирователя импульсов, первый и второй входы которого соединены с первой и второй входными шинами соответ0 ственно. Формирователь импульсов содержит два элемента сравнения и инвертирующий элемент задержки, входы первого элемента сравнения являются входами формирователя импульсов, выход первого элемента срав5 нения связан с одним из входов второго элемента сравнения непосредственно и через инвертирующий элемент задержки - со вторым входом второго элемента сравнения, выход которого является выходом

0 формирователя импульсов.

Введение в состав устройства вместо D-три ггера, имеющегося в прототипе, формирователя импульсов и элемента ИЛИ с их связями обеспечивает асинхронное сраба5 тывание защиты выходных ключей от пере Грузок, т.е. повышается надежность защиты устройства от перегрузок.

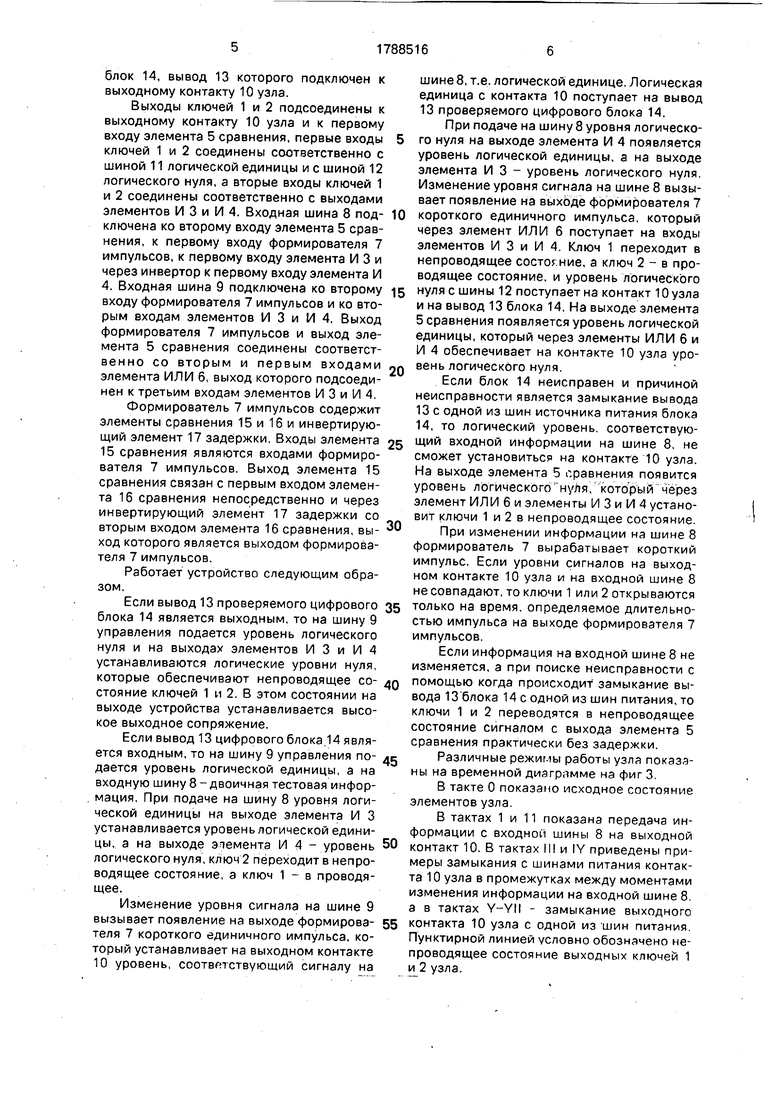

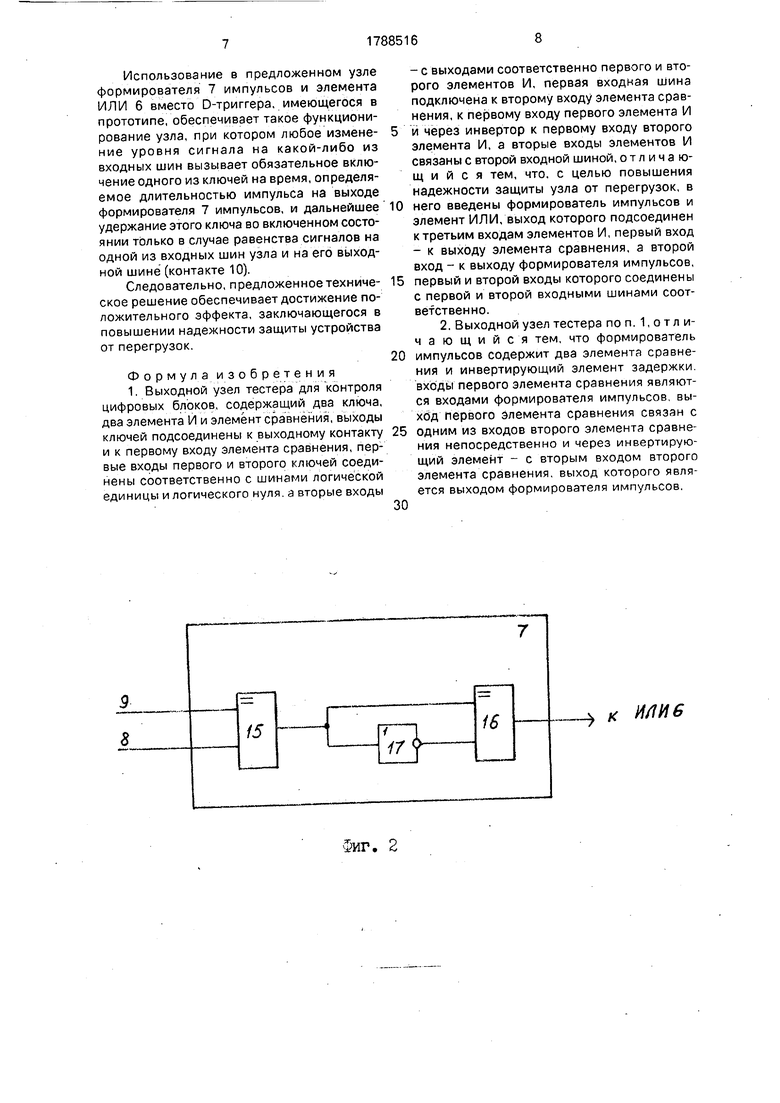

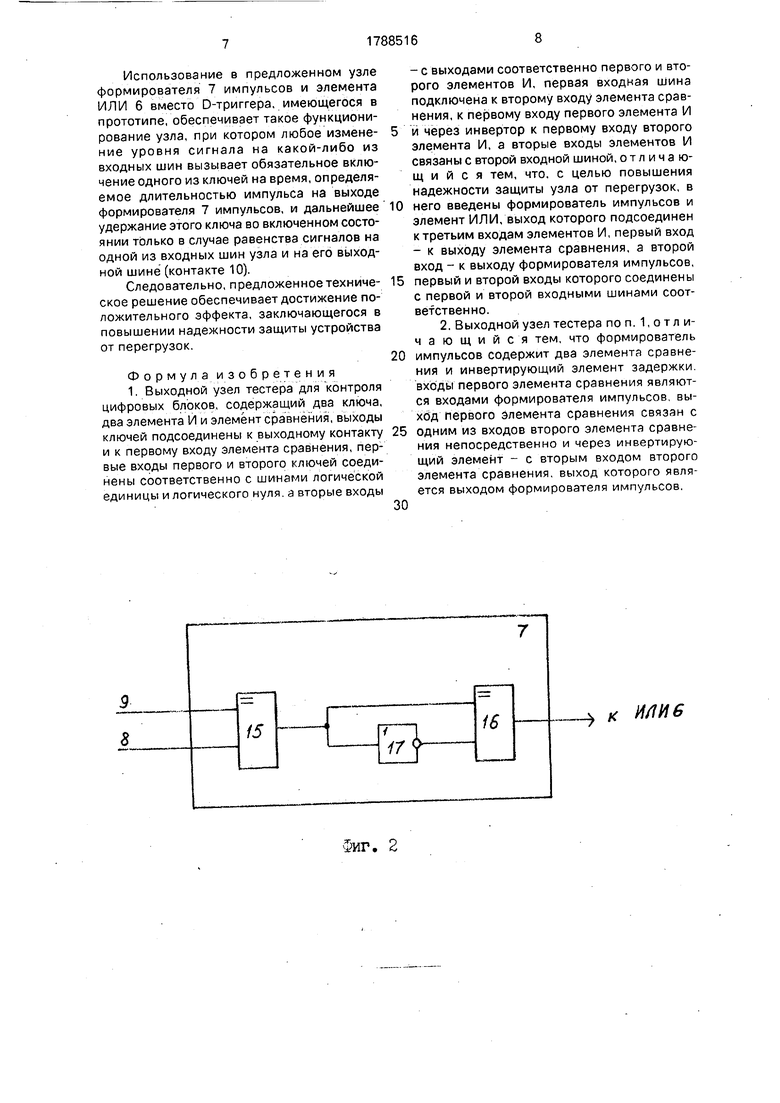

На фиг. 1 показана блок-схема выходного узла тестера; на флг. 2 - схема формиро- 0 вателя импульсов; на фиг. 3 - временная диаграмма работы выходного узла.

Выходной узел тестера, блок-схема которого приведена на фиг. 1, содержит ключи 1 и 2, элементы И 3 и И 4, элемент 5 сравне- ния, элемент ИЛИ 6. формирователь 7 им- пульсов, информационную входную шину 8. входную шину 9 управления, выходной контакт 10, шины 11,12 логической единицы и логического нуля, проверяемый цифровой

блок 14, вывод 13 которого подключен к выходному контакту 10 узла.

Выходы ключей 1 и 2 подсоединены к выходному контакту 10 узла и к первому входу элемента 5 сравнения, первые входы ключей 1 и 2 соединены соответственно с шиной 11 логической единицы и с шиной 12 логического нуля, а вторые входы ключей 1 и 2 соединены соответственно с выходами элементов И 3 и И 4. Входная шина 8 под- ключена ко второму входу элемента 5 сравнения, к первому входу формирователя 7 импульсов, к первому входу элемента И 3 и через инвертор к первому входу элемента И 4. Входная шина 9 подключена ко второму входу формирователя 7 импульсов и ко вторым входам элементов И 3 и И 4, Выход формирователя 7 импульсов и выход элемента 5 сравнения соединены соответственно со вторым и первым входами элемента ИЛИ 6, выход которого подсоединен к третьим входам элементов И 3 и И 4.

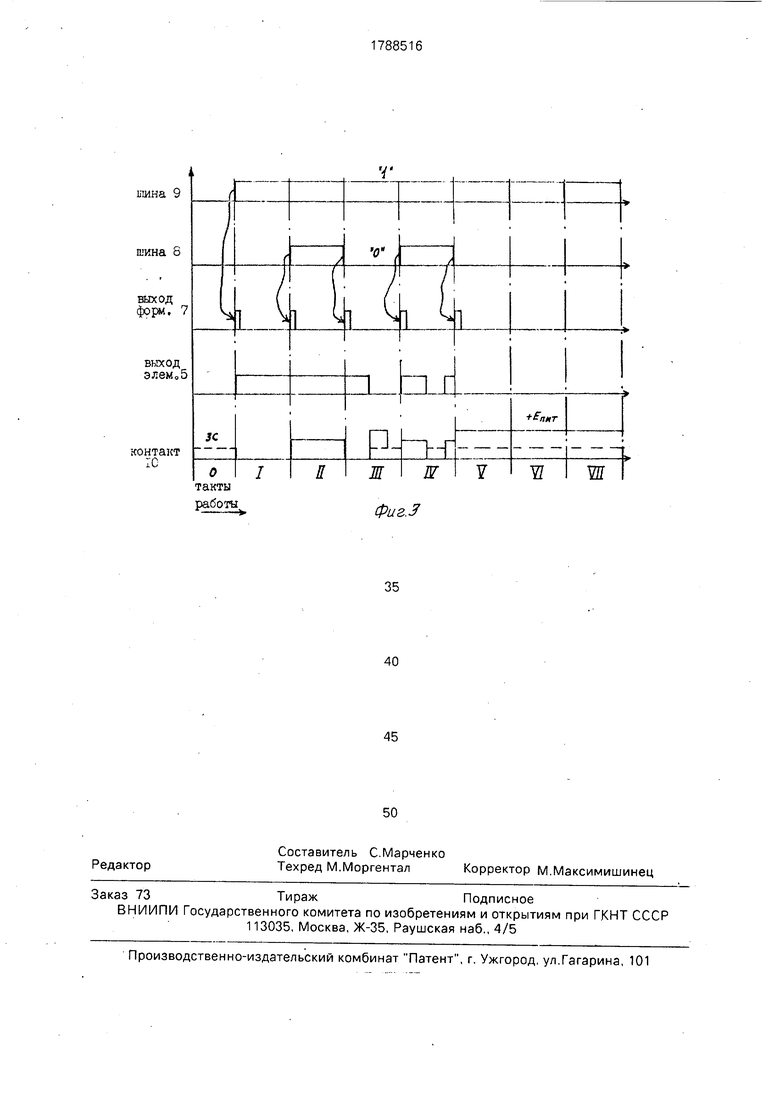

Формирователь 7 импульсов содержит элементы сравнения 15 и 16 и инвертирующий элемент 17 задержки. Входы элемента 15 сравнения являются входами формирователя 7 импульсов. Выход элемента 15 сравнения связан с первым входом элемента 16 сравнения непосредственно и через инвертирующий элемент 17 задержки со вторым входом элемента 16 сравнения, вы- ход которого является выходом формирователя 7 импульсов.

Работает устройство следующим образом.

Если вывод 13 проверяемого цифрового блока 14 является выходным, то на шину 9 управления подается уровень логического нуля и на выходах элементов И 3 и И 4 устанавливаются логические уровни нуля, которые обеспечивают непроводящее со- стояние ключей 1 и 2. В этом состоянии на выходе устройства устанавливается высокое выходное сопряжение.

Если вывод 13 цифрового блока.14 является входным, то на шину 9 управления по- дается уровень логической единицы, а на входную шину 8 - двоичная тестовая информация. При подаче на шину 8 уровня логической единицы на выходе элемента И 3 устанавливается уровень логической единицы, а на выходе элемента И 4 - уровень логического нуля, ключ 2 переходите непроводящее состояние, а ключ 1 - в проводящее.

Изменение уровня сигнала на шине 9 вызывает появление на выходе формирова- теля 7 короткого единичного импульса, который устанавливает на выходном контакте 10 уровень, соответствующий сигналу на

шине 8, т.е. логической единице. Логическая единица с контакта 10 поступает на вывод 13 проверяемого цифрового блока 14.

При подаче на шину 8 уровня логического нуля на выходе элемента И 4 появляется уровень логической единицы, а на выходе элемента И 3 - уровень логического нуля. Изменение уровня сигнала на шине 8 вызывает появление на выходе формирователя 7 короткого единичного импульса, который через элемент ИЛИ 6 поступает на входы элементов И 3 и И 4. Ключ 1 переходит в непроводящее состояние, а ключ 2 - в проводящее состояние, и уровень логического нуля с шины 12 поступает на контакт 10 узла и на вывод 13 блока 14. На выходе элемента 5 сравнения появляется уровень логической единицы, который через элементы ИЛИ 6 и И 4 обеспечивает на контакте 10 узла уровень логического нуля.

Если блок 14 неисправен и причиной неисправности является замыкание вывода 13с одной из шин источника питания блока 14, то логический уровень, соответствующий входной информации на шине 8, не сможет установиться на контакте 10 узла. На выходе элемента 5 сравнения появится уровень логического нуля, которыйi через элемент ИЛИ 6 и элементы И 3 и И 4 установит ключи 1 и 2 в непроводящее состояние.

При изменении информации на шине 8 формирователь 7 вырабатывает короткий импульс. Если уровни сигналов на выходном контакте 10 узла и на входной шине 8 не совпадают, то ключи 1 или 2 открываются только на время, определяемое длительностью импульса на выходе формирователя 7 импульсов,

Если информация на входной шине 8 не изменяется, а при поиске неисправности с помощью когда происходит замыкание вывода 13 блока 14 с одной из шин питания, то ключи 1 и 2 переводятся в непроводящее состояние сигналом с выхода элемента 5 сравнения практически без задержки.

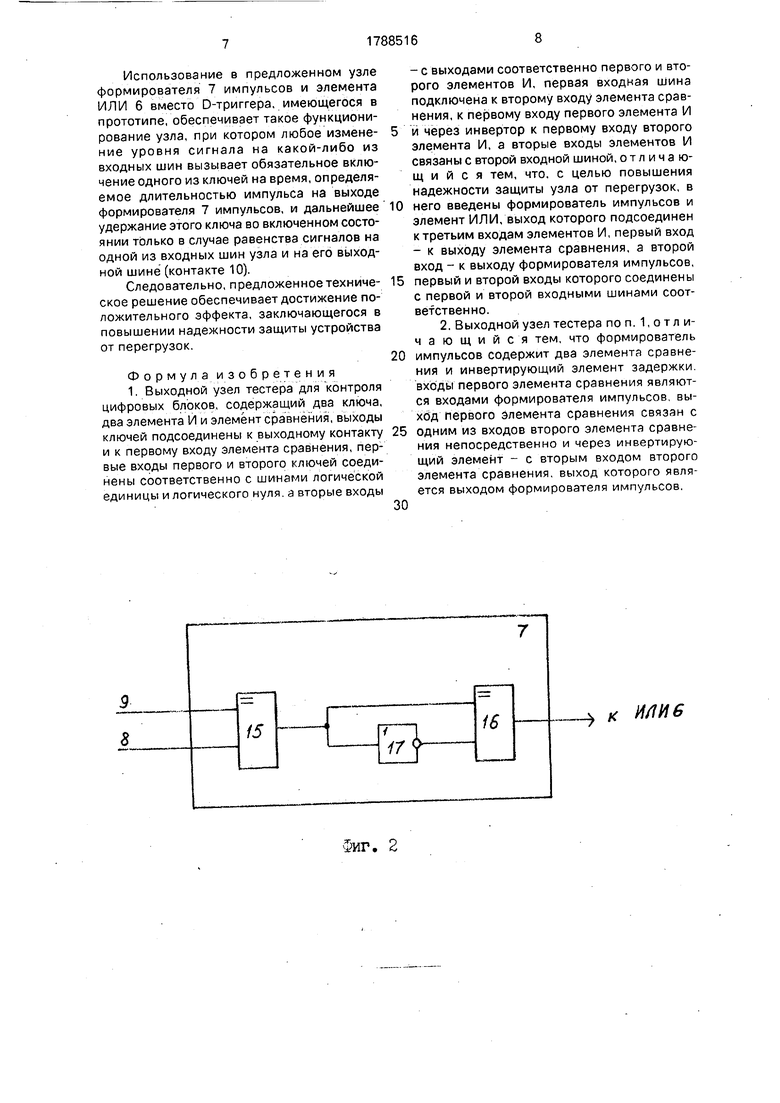

Различные режимы работы узла показаны на временной диаграмме на фиг 3.

В такте 0 показано исходное состояние элементов узла.

В тактах 1 и 11 показана передача информации с входной шины 8 на выходной контакт 10. В тактах III и IY приведены примеры замыкания с шинами питания контакта 10 узла в промежутках между моментами изменения информации на входной шине 8, а в тактах Y-YII - замыкание выходного контакта 10 узла с одной из шин питания. Пунктирной линией условно обозначено непроводящее состояние выходных ключей 1 и 2 узла.

Использование в предложенном узле формирователя 7 импульсов и элемента ИЛИ 6 вместо D-триггера, имеющегося в прототипе, обеспечивает такое функционирование узла, при котором любое изменение уровня сигнала на какой-либо из входных шин вызывает обязательное включение одного из ключей на время, определяемое длительностью импульса на выходе формирователя 7 импульсов, и дальнейшее удержание этого ключа во включенном состоянии только в случае равенства сигналов на одной из входных шин узла и на его выходной шине (контакте 10).

Следовательно, предложенное техническое решение обеспечивает достижение положительного эффекта, заключающегося в повышении надежности защиты устройства от перегрузок.

Формула изобретения 1, Выходной узел тестера для контроля цифровых блоков, содержащий два ключа, два элемента И и элемент сравнения, выходы ключей подсоединены к выходному контакту и к первому входу элемента сравнения, первые входы первого и второго ключей соединены соответственно с шинами логической единицы и логического нуля, а вторые входы

0

5

0

5

0

-с выходами соответственно первого и второго элементов И, первая входная шина подключена к второму входу элемента сравнения, к первому входу первого элемента И и через инвертор к первому входу второго элемента И, а вторые входы элементов И связаны с второй входной шиной, отличающийся тем, что, с целью повышения надежности защиты узла от перегрузок, в него введены формирователь импульсов и элемент ИЛИ, выход которого подсоединен к третьим входам элементов И, первый вход

- к выходу элемента сравнения, а второй вход - к выходу формирователя импульсов, первый и второй входы которого соединены с первой и второй входными шинами соответственно.

2. Выходной узел тестера поп. 1, о т л и- чающийс я тем, что формирователь импульсов содержит два элемента сравнения и инвертирующий элемент задержки, входы первого элемента сравнения являются входами формирователя импульсов, выход первого элемента сравнения связан с одним из входов второго элемента сравнения непосредственно и через инвертирующий элемент - с вторым входом второго элемента сравнения, выход которого является выходом формирователя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Выходной узел тестера для контроля логических блоков | 1980 |

|

SU940090A1 |

| Выходной узел тестера для контроля логических схем | 1982 |

|

SU1018064A1 |

| Выходной узел тестера для контроля логических устройств | 1977 |

|

SU651274A1 |

| Выходной узел тестера для контроля логических элементов | 1982 |

|

SU1180818A1 |

| Выходной узел тестера | 1989 |

|

SU1732301A1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

RU2042026C1 |

| Стабилизатор переменного напряжения | 1988 |

|

SU1534434A1 |

| Стабилизированный преобразователь постоянного напряжения | 1981 |

|

SU1012224A1 |

| Устройство для измерения температуры | 1984 |

|

SU1229601A1 |

| Устройство для управления трехфазным инвертором | 1984 |

|

SU1354365A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах автоматизации диагностирования цифровых блоков ЭВМ. Цель изобретения - повышение надежности защиты узла от перегрузок - достигается за счет сокращения времени воздействия больших токов на выходные ключи. Выходной узел тестера для контроля цифровых блоков содержит ключи 1 и 2, элементы И 3 и 4, элемент 5 сравнения, элемент ИЛИ 6, формирователь 7 импульсов, информационную входную шину 8, входную шину 9 управления, выходной контакт 10, шины 11 и 12 логической единицы и логического нуля соответственно. 1 з.п. ф-лы, 3 ил.

8

15

Фиг. 2

Vf

16

к И/1И6

| Выходной узел тестера для контролялОгичЕСКиХ уСТРОйСТВ | 1979 |

|

SU822190A1 |

| Выходной узел тестера для контроля логических блоков | 1980 |

|

SU940090A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Выходной узел тестера для контроля логических устройств | 1977 |

|

SU651274A1 |

Авторы

Даты

1993-01-15—Публикация

1987-10-05—Подача