(54) ВЫХОДНОЙ УЗЕЛ ТЕСТЕРА ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ УСТРОЙСТВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля состояния контактов логических блоков | 1982 |

|

SU1061145A1 |

| Выходной узел тестера для контроля логических схем | 1982 |

|

SU1018064A1 |

| Устройство для контроля логических и временных параметров сигналов | 1990 |

|

SU1777235A1 |

| Выходной узел тестера для контроля цифровых блоков | 1987 |

|

SU1788516A1 |

| Стабилизированный преобразователь постоянного напряжения с защитой | 1986 |

|

SU1317597A2 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

| Выходной узел тестера для контроля логических элементов | 1982 |

|

SU1180818A1 |

| ЧАСТОТНО-РЕГУЛИРУЕМЫЙ ЭЛЕКТРОПРИВОД С НЕУПРАВЛЯЕМЫМ ЗВЕНОМ ПОСТОЯННОГО ТОКА | 1993 |

|

RU2067352C1 |

| МИКРОПРОЦЕССОРНОЕ МНОГОФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО РЕЛЕ ЧАСТОТЫ | 2000 |

|

RU2171475C1 |

| Выходной блок тестера для контроля цифровых блоков | 1990 |

|

SU1805470A1 |

Изобретение относится к вычислительной технике и может быть исполь зовано в тестерах для контроля логи ческих устройств, выполненных на микросхемах с К-МОП технологией изготовления. Известен выходной узел тестера для контроля логических устройств, содержащий.элемент И, элемент ЗАПРЕТ схему сравнения, первый и второй ключи, выходы которых подключены к выводу контролируемого логического устройства и ко входу схемы срав нения, первые входы соединены соответственно с первым и вторым входами выходного узла, вторые входы соответственно с выходами элементов И и ЗАПРЕТ, первые и вторые входы которых соединены соответственно с треть им и четвертым входами выходного узла 1 . Недостатком такого устройства являются ограниченные функциональные возможности вследствие того, что оно не может быть использовано в тестерах, обеспечивающих специальный режим обнаружения неисправностей, контролируемых логических устройств связанных, например, с несоответствием заданной и реальной принадлежности данного вывода логического устройства ко входам или выходам. Это устройство характеризуется также низкой надежностью из-за наличия токовой перегрузки его выхода при изменении принадлежности данного вывода логического устройства за счет ошибок в монтаже, закорачивания соседних контактов, ошибок в работе выходного узла и т.д. Наиболее близким к предлагаемому является выходной узел тестера для контроля логических устройств, содержащий первый и второй ключи с объединенными выходами, первые . входы которых соединены с соответствующими входами узла, а вторые входы - с выходами элемента ЗАПРЕТ и элемента И соответственно, первые входы элементов И и ЗАПРЕТ соединены с соответствующими входами узла, вторые входы - с выходом триггера, первый и второй входы соторого соединены с соответствующими, входами узла, элемент сравнения, соединенный первым входом с соответствующим входом узла, вторым входом - с выводом контролируемого логического устройства, а- выходом - с выходом узла 2.

Недостатками этого устройства являются ограниченные функциональные возможности и. низкая надежность, связанные с указанными причинами, Цель изобретения - расширение функциональных возможностей и повышение надежности устройства.

Поставленная цель достигается тем, что в выходной узел тестера введены первый и второй резисторы, третий и четвертый ключи с объединенными выходами, инвертор и сумматор, первый вход которого соединен с первым входом элемента сравнения, второй вход - с соответствующим входом узла и третьими входами элементов И и ЗАПРЕТ, а выход - с четвертыми входами элементов И и ЗАПРЕТ, первым входом четвертого ключа и через инвертор с первым,. входом третьего ключа, выходы второго и третьего ключей через первый и второй резисторы соответственно подключены к выводу контролируемого логического устройства вторые входы третьего и четвертого ключей соединены с первыми входами первого и второго ключей соответственно.

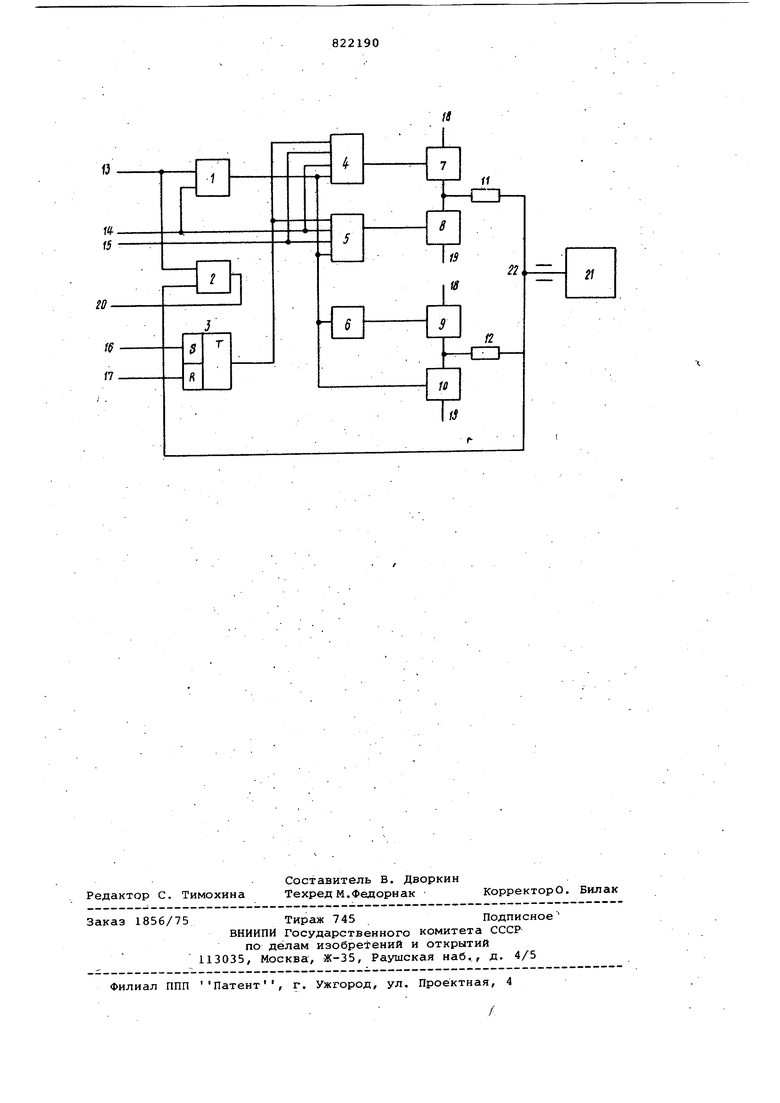

На чертеже дана блок-схема выходного узла тестера для контроля логических устройств.

Выходной узел тестера содержит сумматор 1 по модулю два/ элемент 2 сравнения триггер 3, элемент 4 ЗАПРЕТ, элемент И 5, инвертор 6, первый 7, .второй 8, третий 9 и четвертый 10 ключи, первый 11 и второй 12 резисторы, входы 13-19 и выход 2

Логическое устройство 21 не входит в состав выходного узла тестера а приведено на чертеже для пояснени его принципа действия.

Выходной узел тестера работает следующим образом.

Режимы работы выходного узла задаются двоичным кодом на его входах 14 и 15. Выходной узел работает в следующих основных режимах:

Вход

если вывод, на который

работает выходной узел, является входом контролируемого логического устройства;

Выход, если вывод, на которы работает выходной узел, является выходом контролируемого логического устройства;

третье состояние , если вывод, на который работает выходной узел, представляет собой выход на магистраль, находящийся в отключенном состоянии, и к нему со стороны логического устройства подключена выходом, например, схема типа ТТЛ с закрытыми верхним и нижним транзисторами.

Во всех режимах работы на входах 18 и 19 установлены логическая и О Соответственно.

Режим Вход задается на входах 14, 15 сигналами логической I I 1 I I «

Сигналы, поступающие на вход ГЗ, содержат двоичную информацию, которая должна быть передана выходным узлом на вход контролируемого логического устройства 21.

Синхроимпульсы-на входе 16 появляются в моменты обновления информации на входе 13 от набора к набору теста, а на входе 17 - с задержкой по отношению к этим моментам. С входа 16 синхроимпульс проходит на З-вход триггера 3, в результате чего выход триггера 3 приобретает значение логической .

Если на входе 13 сигнал равен , то на выходе сумматора 1, при равенстве сигналов логической i на его входах, логический сигнал 0 равен О .

Так как на входах элемента 5

О

один из сигналов равен

то

на выходе элемента 5 сигнал также

О

и ключ 8 закрыт.

равен

Ключ 10 закрыт, так как на его вход поступает сигнал с выхода сумматора 1.

Так как на трех входах элемента

4 сигналы равны 1

а на четвер0

том входе сигнал равен

то на

выходе элемента 4 сигнал равен 1

и ключ 7 закрыт, в результате

чего сигнал с входа 18 поступает на

общий выход ключей 7 и 8.

Так как на входе инвертора 6 сигнал равен О, то на его выходе сигнал равен , ключ 9 открыт и сигнал с входа 18 проходит на рбщий выход ключей 9 и 10.

Через резисторы 11, 12 сигнал, равный , поступает на вход устройства 21 и на вход элемента 2.

Сопротивление резистора 11 зна- чительно меньше сопротивления резисTopia 12 и достаточно мало для того, чтобы обеспечить требуемую крутизну фронта передаваемого сигнала при наличии емкостной нагрузки.

Если сигнал на входе 13 после обновления информации равен О , то на выходе сумматора 1 сигнал равен 1 .

Этот сигнал поступает на входы элементов 4 и 5 и инвертора 6, в результате чего на выходах элемента 4 и инвертора 6 сигналы равны О, а на выходе,элемента 5 сигнал равен 1 .

Поэтому ключи 7 и 9 закрыты, а ключи 8 и 10 открыты, уровень логического О с входа 19 проходит 0 через резисторы 11 и 12 на вход устройства 21.

После прохождения первого синхроимпульса со входа 16 через некоторый период времени,со входа 17 проходит второй синхроимпульс. Он поступает на R-вход триггера 3, с выхода которого на входы элементо 4 и 5 поступает сигнал О. В результате этого ключи 7,. 8 закры ты, а ключи 9, 10 удерживают чере резистор 12 требуемое значение си ла на входе устройства 21 до след щего момента обновления информаци Интервал времени между первым вторым синхроимпульсами достаточн велик для формирования неискаженн переднего фронта передаваемого си ла. Ключи 7, 8 надежно защищены о перегрузки резистором 11 при наличии на выходе устройства 21 сигналов питающего напряжения. Величина сопротивления резистор 12 достаточна для устранения перегрузок ключей выходного узла тестера. Резистор 12 существенно больше сопротивления выхода контролируемо устройства, например, имеет величи порядка десятков килоом, а сопроти ление выхода - от нескольких десят ков ом до нескольких килоом. В то же время сопротивление резистора 12 значительно меньше вход ного сопротивления контролируемого устройства 21. . В случае, если выходной узел работает в режиме Вход, а к выводу устройства 21 в результате каких-либо причин подключен выход микросхемы, принадлежащий устройству 21, резистор 12 защищает от токовой перегрузки эту микросхему. Режим Выхрд задается сигналами О на входе 14 и i на входе 15. Наличие на входах элементов 4 и 5 сигнала с входа 14, равного приводит к появлению на их выходах сигналов О, в результа чего ключи 7 и 8 закрыты. Если сигнал на входе 13 равен , то при на входе 14 вы сумматора 1 вырабатывает сигнал М, который поступает на вход ключа 9 и через инвертор - на вход ключа 10. В результате этого ключ 9 закрыт, ключ 10 открыт и сигнал О со входа 19 поступает на общий выход ключей 9 и 10, Если.сигнал на входе 13 равен О на входе 14 вы О, то при вырабатывает сигна ход сумматора 1 О, закрывающий ключ 10, и откр вает через инвертор 6 ключ 9 ко рый пропускает сигнал i с вход 18 на. общий выход ключей 9 и 10, На выходе устройства 21 ожидаемый сигнсш имеет другой логический уровень, чем сигнал на общем выходе ключей 9, 10. Резистор -12 позволяет произвест проверку выхода устройства 21 сигналом, противоположным по логическо му уровню ожидаемому сигналу контакта 22. Так как сопротивление выхода устройства 21 существенно меньше по своей величине сопротивления резистора 12, то сигнал ключей 9 и 10 влияет на логическое состояние этого выхода. Поэтому в случае несоответствия . логического сигнала на данном выходе, заданному с входа 13, схема сравнения фиксирует факт неисправности устройства 21 по данному выходу. . Режим Третье состояние задается сигналами на входе 14 и О на входе.15. Наличие на входах элементов 4 и 5 сигнала с входа 15, равного О, приводит к появлению на их выходах сигналов О, в результате чего ключи 7 и 8 закрыты. Ключи 9 и 10 работают так же, как и в режиме Выход. При работе в составе тестера логических устройств выходной узел обеспечивает обнаружение несоответ-ствия принадлежности данного вывода устройства 21 к входам, выходам или третьим состояниям, заданной со входов 14 и 15, и его реальной принадлежности. Такое несоответствие может образоваться в следующих случаях. 1.Вывод устройства 21 является ошибочно выходом, но для выходного узла он правильно определен со входов 14 и 15 как вход 2.Вывод устройства 21 ошибочно является входом или третьим состоянием, а для выходного узла он правильно определен со входов 14 и 15 как выход, 3.Вывод устройства 21 ошибочно является выходом, а для выходного узла он правильно определен со входов 14 и 15 как третье состояние, 4.Вывод устройства 21 является входом, а для выходного узла он ошибочно определен со в Ход в 14 и 15 как третье состояние. Для первого случая тестер обнаруживает все ошибочно заданные выходы путем подачи на входы 13 всех выходных узлов, подключаемых к выходам устройства 21, сигнала О в двух следующих и сигнала руг за другом тестовых наборах. ри этом сигналы, поступающие а входь 13 всех остальных выходных злов, равны по логическому уровню жидаемым сигналам с соответствуюих выводов устройства 21, В том случае резисторы 11 и 12 отклюают общие выходы ключей 7 и 8, и 10 от низкоомного выхода устойства 21, и на одном из двух тесовых наборов элемент 2 обнаруживает есоответствие состояний на выходе стройства 21 и входе 13, что сигналиэирует о несоответствии заданно и реальной принадлежности данного вывода устройства 21.

Для второго случая тестер обнаруживает все выводы устройства 21, которые должны быть выходами, однако ошибочно являются входами или третьими состояниями. В этом случае при заланном логическом сигнале на входе 13, на общем выходе ключей 9 и 10,вырабатывается инверсный сигнал, который передается без потер на резисторе 12 на более высокоомны вход устройства 21 и вход элемента который и фиксирует несоответствие заданной и рёгшьной принадлежности данного вывода устройства 21. Кроме того, в этом случае проверяются и н справности, связанные с ошибочным определением выходного узла на выход

при правильном определении вывода . устройства 21 как входа или третьег состояния..

Для третьего случая тестер для контроля логических устройств обнаруживает несоответствие заданной и реальной принадлежности так ,как и в первом случае, при сохр1анении неизменными сигналов, поступающих на выходы и входы 13 всех остальных выходных узлов.

В четвертом случае проверка выводов устройства 21 аналогична проверке для первого случая, при фиксации результата проверки в интервале времени между двумя синхроимпульсами, поступающи /ш со входов 16 и 17. В этом случае из-за наличия высокого значения сопротивления резистора 12 и емкости вывода . устройства 21, а также соединительной линии между ними и выходным узлом при изменении логического уровн сигнала на входе 13 сигнал на вывод устройства 21 не успевает изменить свое значение.

Таким образом, за счет введения сумматора 1, инвертора 6, ключей 9 и 10 и резисторов 11 и 12 обеспечивается защита выходов выходного узла от токовых перегрузок и, следовательно, большая наработка и надежность работы, а также возможность использования выходного узла в более широком классе тестеров.

т.е.расширение области применения и функциональных возможностей.

Формула изобретения

Выходной узел тестера для контрол логических устройств, содержащий первый и второй ключи с объединенным выходами, первые входы которых соединены с соответствующими входами узла, а вторые входы - с выходами элемента ЗАПРЕТ и элемента И соответственно, первые входы элементов И и ЗАПРЕТ соединены с соответствующими входами узла, вторые входы - с выходами триггера, первый и второй входы которого соединены с соответствующими входами узла, элемент сравнения, соединенный первым входом с соответствующим входом узла, вторым входом - с выводом контролируемого логического устройства, а выходом - с выходбм узла, о т л ичающийс я тем, что, с целью расширения функциональных возможностей и повышения нгщежности, ,в него введены первый и второй резисторы, третий и четвертый ключи с объединенными выходами, инвертор и сумматор, первый вход которого соединен с первым входом элемента сравнения, второй вход - с соответс твующим входом узла и третьими входами элементов И и ЗАПРЕТ, а выход - с четвертыми входами элементов И и ЗАПРЕТ, первым входом четвертого ключа и через инвертор с первым входом третьего ключа, выходы второго и третьего ключей через первый и второй резисторы соответственно подключены к выводу контролируемого логического устройства, в-горые входы третьего и четвертого ключей соединены с первыми входами первого и второго ключей соответственно.

Источники информации, принятые во внимание.при экспертизе

Авторы

Даты

1981-04-15—Публикация

1979-07-09—Подача