оо to

со

Изобретение относится к контрольно-измерительной технике и предназначено для контроля логических блоков.

Цель изобретения - повышение достоверности контроля за счет обеспечения возможности выявления несанкционированного появления высокоим- педансного состояния на выходе контролируемого логического блока.

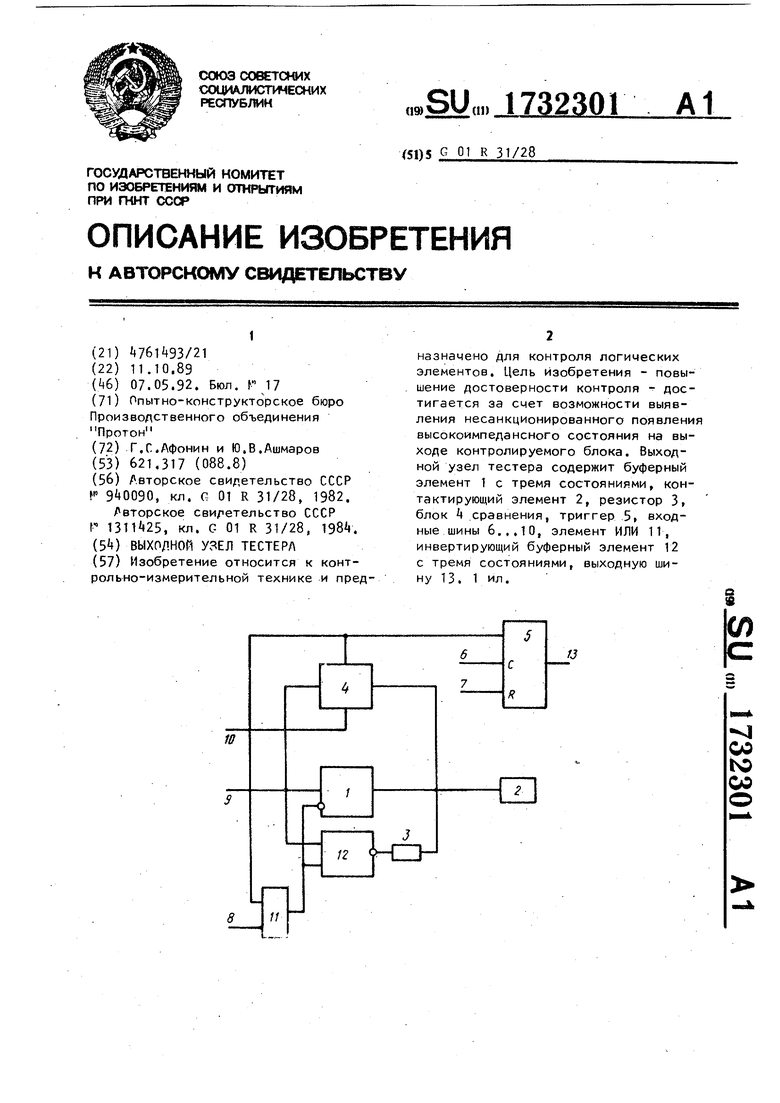

На чертеже представлена функциональная схема выходного узла тестера,

Выходной, узел тестера содержит буферный элемент 1 с тремя состояниями, контактирующий элемент 2, резистор 3, блок k сравнения, триггер 5, входные шины 6 - 10, элемент ИЛИ И и инвертирующий буферный элемент 12 с тремя состояниями, выходную шину 13 с соответствующими связями.

Выходной узел тестера работает следующим образом.

Если контактирующий элемент 2 соединяется с выходом проверяемого устройства, то на шину 8 подается 1, При этом 1 с шины 8 поступает на один из входов элемента ИЛИ 11, устанавливая его выходе, 1, которая с выхода элемента ИЛИ 11 поступает на управляющий вход буферного элемента 1 с тремя состояниями, и переводит его в третье состояние. На шину 9} вход блока f сравнения, информационные входы буферных элементов 1 и 12 подается уровень напряжения эталонной выходной реакции. Так как буферный элемент 1 находится в третьем состоянии, он не влияет на результат контроля. На выходе инвертирующего буферного элемента 12 появляется сигнал, противоположный ожидаемому на контактирующем элементе 2, и благодаря наличию резистора 3 нагружает небольшим током выход контролируемого блока. При равенстве сигналов на входах блока сравнения (на шине 9 и контактирующем элементе 2), на его выходе устанавливается О, а при входных сигналах с разными уровнями напряжения - 1, Результат сравнения коммутируется на информационный вход триггера 5 уровнем логической 1 с шины 10 стробирования и переписывается в триггер 5 задним фронтом синхронизирующего импульса. При появлении на контактирующем элементе 2 высоко-

5

5

импедансного состояния на вход блока сравнения поступает сигнал, инверсный поступающему на его второй вход, и на его выходе появляется уровень напряжения - 1.

Если контактирующий элемент 2 соединяется с входом проверяемого устройства, то на шину 8 подается О.

Затем на шине 9 устанавливают уровень сигнала (О или 1), который нужно задать на входе контролируемого устройства. При этом в момент смены информации на шины 9 и 10 подается импульс с низким уровнем напряжения. С шины 10 стробирующие импульсы устанавливают на входе блока сравнения О, независимо от соотношения сравниваемых сигналов на его входах. Сигнал логического О с выхода блока Ц сравнения поступает на первый вход элемента ИЛИ 11 и, так как на его втором входе О, на выходе элемента ИЛИ 11. устанавливается О, поступающий на управляющие входы буферных элементов 1 и 12.

Таким образом,инвертирующий буферный элемент 12 переходит в третье

0 состояние, а буферный элемент 1 переходит в активное состояние и на его выходе появляется сигнал (с шины 9), который необходимо подать на входной контакт проверяемого устройства, При этом на первый и второй входы блока Ц сравнения поступают одноименные сигналы с информационного входа и выхода буферного элемента 1. Через определенное вреQ мя, когда сигналы на входе буферного элемента 1 и контактирующего элемента 2 имеют устойчивое значение О, на имеют устойчивое значение О, на шине 10 устанавливается 1, комму5 тируя результат сравнения на информационный вход триггера 5. Результат сравнения переписывается задним фронтом синхронизирующего импульса в триггер 5, При этом результат сравQ нения - U сигнализирует о отсутствии перегрузки буферного элемента 1. Если же во входной цепи проверяемого устройства имеются короткие замыкания на шины питания или имеются нет

5 исправные элементы, способные вызвать перегрузку буферного элемента 1, то при перегрузке последнего не будут равны между собой сигналы на первом и втором входах блока срав5

нения, В результате на выходе блока

сравнения устанавливается

Ч1

торая транслируется через вход элемента ИЛИ 11 на управляющие входы буферных элементов 1 и 12, переводя . буферный элемент 1 в третье состояние, инвертирующий буферный элемент 12 в активное, уровень сигнала на выходе которого совпадает с сигналом на контактном элементе 2 и не приводит к перегрузке инвертирующего буферного элемента, Время нахождения буферного элемента 1 в перегруженном состоянии определяется суммарным временем переключения блока сравнения по входу синхронизации и элемента ИЛИ 11, 1 с выхода блока 4 сравнения переписывается в триг гер 5. При этом 1 на выходе триггера 5 сигнализирует о наличии во входной цепи неисправных элементов.

Формула-изобретения

Выходной узел тестера, содержащий буферный элемент с тремя состояниями, выход которого соединен с контактирующим элементом и первым входом

иа

,

10

15

20

25

блока сравнения, выход которого соединен с информационным входом триггера, синхронизирующий и установочный входы которого соединены соответственно с первым и вторым входами выходного узла тестера, третий вход выходного узла тестера соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом блока сравнения, а выход - с управляющим входом буферного элемента с тремя состояниями, информационный вход которого соединен с четвертым входом выходного узла тестера и вторым входом блока сравнения, стробирующий вход которого соединен с пятым входом выходного узла тестера, отличающийся тем, что, с целью повышения достоверности контроля, в него введены ре.яистор и инвертирующий буферный элемент с тремя состояниями, вход которого соединен с информационным входом буферного элемента с тремя состояниями, управляющий вход с выходом элемента ИЛИ, выход с первым выводом резистора, второй вывод которого соединен с выходом буферного элемента с тремя состояниями

| название | год | авторы | номер документа |

|---|---|---|---|

| Выходной узел тестера для контроля логических блоков | 1980 |

|

SU940090A1 |

| Выходной узел тестера для контроля цифровых блоков | 1987 |

|

SU1788516A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Выходной узел тестера для контроля логических элементов | 1982 |

|

SU1180818A1 |

| Выходной узел тестера для контроля логических устройств | 1977 |

|

SU651274A1 |

| Выходной узел тестера для контроля логических схем | 1982 |

|

SU1018064A1 |

| Устройство для контроля КМОП-логических схем | 1987 |

|

SU1552137A1 |

| Устройство для контроля состояния контактов логических блоков | 1982 |

|

SU1061145A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ АППАРАТУРЫ РЕЛЕЙНОЙ ЗАЩИТЫ И АВТОМАТИКИ | 1986 |

|

RU1478884C |

| Устройство для проверки логических микросхем | 1980 |

|

SU918867A1 |

Изобретение относится к контрольно-измерительной технике и предназначено для контроля логических элементов. Цель изобретения - повышение достоверности контроля - достигается за счет возможности выявления несанкционированного появления высокоимпедансного состояния на выходе контролируемого блока. Выходной узел тестера содержит буферный элемент 1 с тремя состояниями, контактирующий элемент 2, резистор 3, блок Ц сравнения, триггер 5, входные шины 6...10, элемент ИЛИ 11, инвертирующий буферный элемент 12 с тремя состояниями, выходную шину 13. 1 ил. § (Л

| Авторское свидетельство СССР V , кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ получения продукта конденсации бетанафтола с формальдегидом | 1923 |

|

SU131A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ( ВЫХОДНОЙ УЗЕЛ ТЕСТЕРА | |||

Авторы

Даты

1992-05-07—Публикация

1989-10-11—Подача