Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства систем обработки информации.

Цель изобретения - повышение надежности устройства.

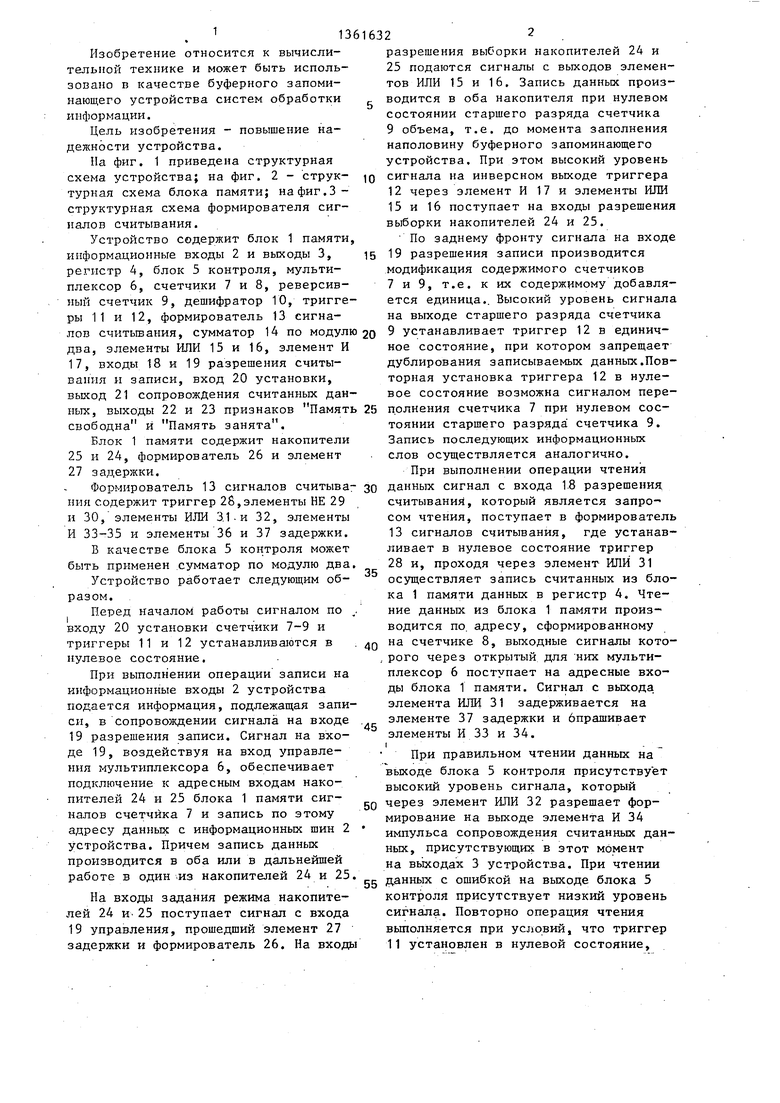

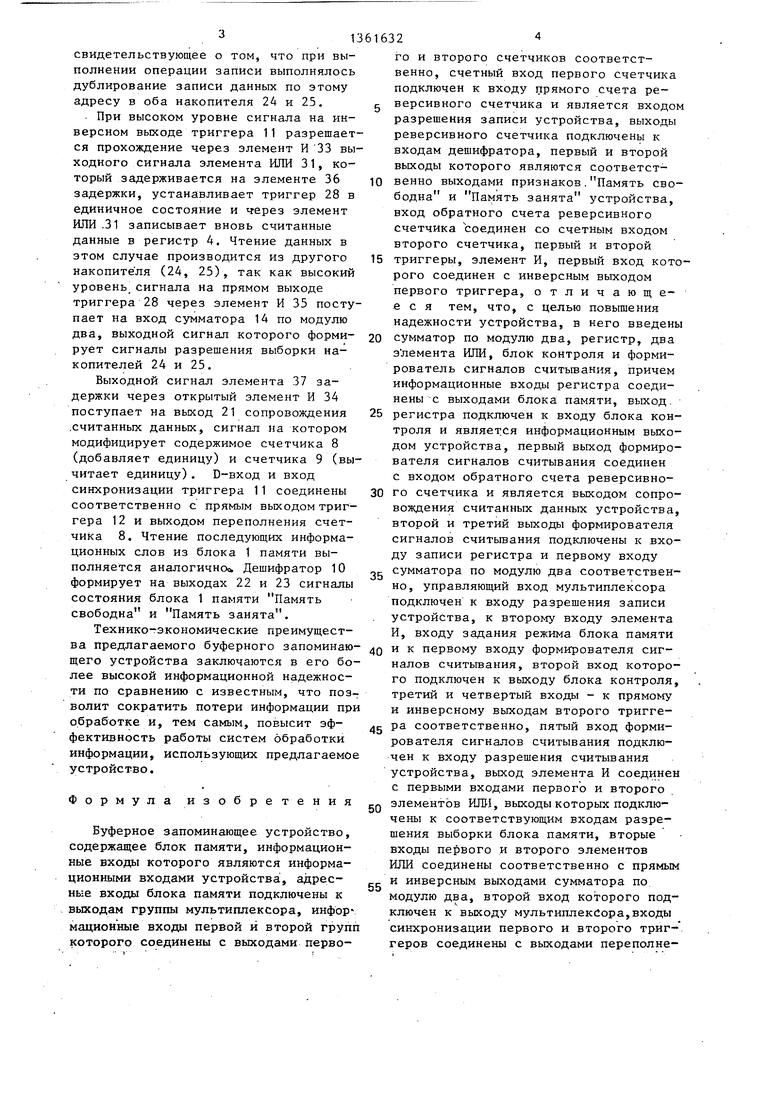

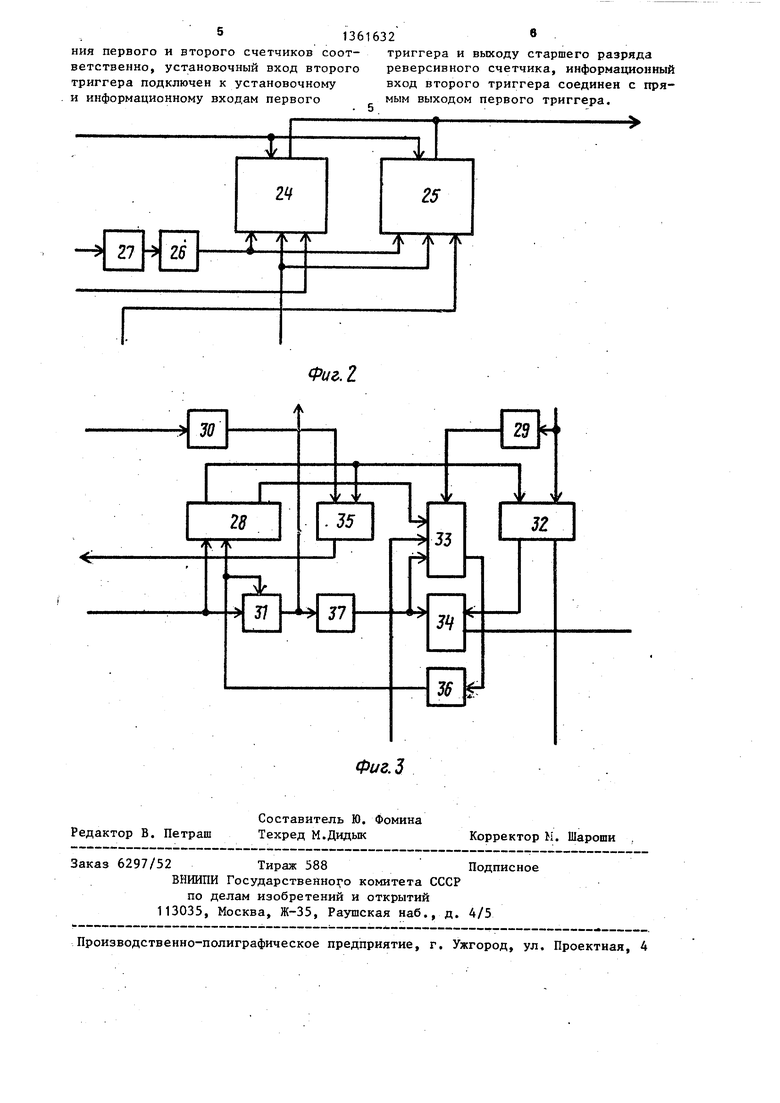

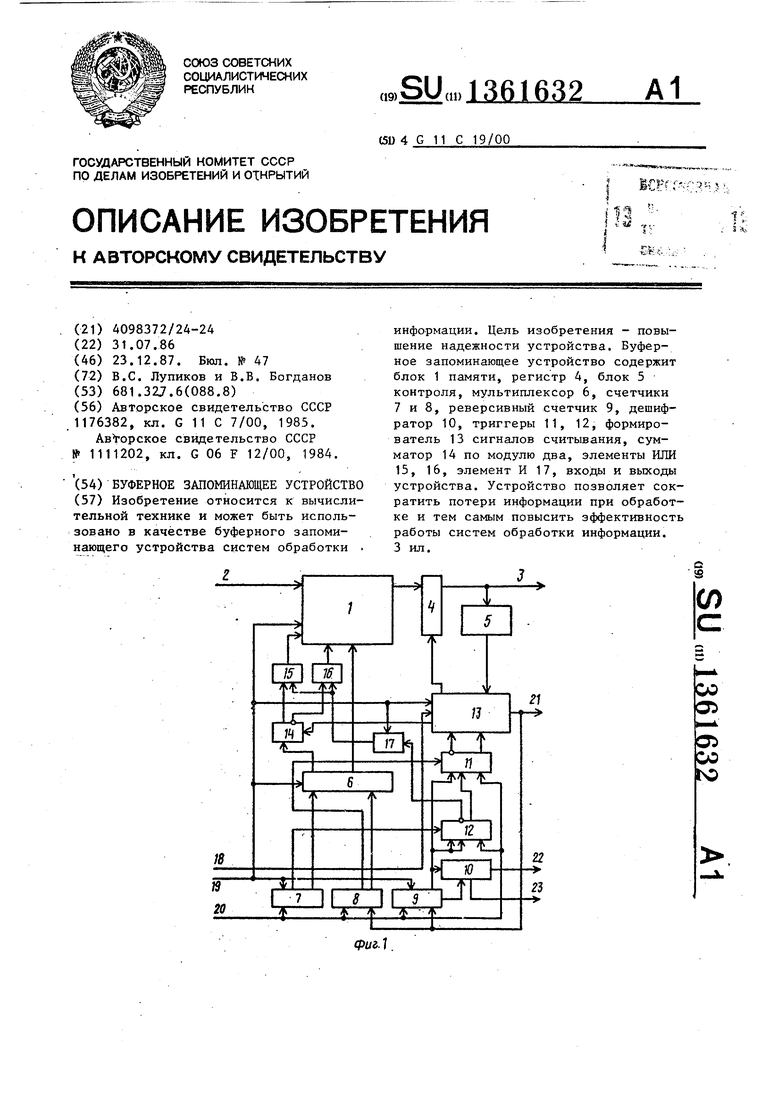

Па фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока памяти; нафиг.З- структурная схема формирователя сиг- налов считывания.

Устройство содержит блок 1 памяти информационные входы 2 и выходы 3, регистр 4, блок 5 контроля, мультиплексор 6, счетчики 7 и 8, реверсивный счетчик 9, дешифратор 10, триггеры 11 и 12, формирователь 13 сигналов считьшания, сумматор 14 по модулю 20 9 устанавливает триггер 12 в единичдва, элементы ИЛИ 15 и 16, элемент И 17, входы 18 и 19 разрешения считывания и записи, вход 20 установки, выход 21 сопровождения считанных данное состояние, при котором запрещает дублирования записываемых данных.Повторная установка триггера 12 в нулевое состояние возможна сигналом переных, выходы 22 и 23 признаков Память 25 полнения счетчика 7 при нулевом сос- свободна и Память занята.

Блок 1 памяти содержит накопители 25 и 24, формирователь 26 и элемент 27 задержки.

Формирователь 13 сигналов считыва- зо данных сигнал с входа 1-8 разрешения

тоянии старшего разряда счетчика 9. Запись последующих информационных слов осуществляется аналогично. При выполнении операции чтения

ния содержит триггер 2S,элементы НЕ 29 и 30, элементы ИЛИ 3.1. и 32, элементы И 33-35 и элементы 36 и 37 задержки.

В качестве блока 5 контроля может быть применен сумматор по модулю два.

Устройство работает следующим образом.

Перед началом работы сигналом по . входу 20 установки счетчики 7-9 и триггеры 11 и 12 устанавливаются в нулевое состояние.

При выполнении операции записи на информационные входы 2 устройства подается информация, подлежащая записи, в сопровождении сигнала на входе 19 разрешения записи. Сигнал на входе 19, воздействуя на вход управления мультиплексора 6, обеспечивает подключение к адресным входам накопителей 24 и 25 блока 1 памяти сигналов счетчика 7 и запись по этому адресу данных с информационных шин 2 устройства. Причем запись данных производится в оба или в дальнейшей работе в один .из накопителей 24 и 25.

На входы задания режима накопителей 24 и.25 поступает сигнал с входа 19 управления, прошедший элемент 27 задержки и формирователь 26. На входы

35

считывания, который является запросом чтения, поступает в формирователь 13 сигналов считывания, где устанавливает в нулевое состояние триггер 28 и, проходя через элемент ИЛИ 31

осуществляет запись считанных из блока 1 памяти данных в регистр 4. Чтение данных из блока 1 памяти производится по. адресу, сформированному 4Q на счетчике 8, выходные сигналы кото- , рого через открытый для них мультиплексор 6 поступает на адресные входы блока 1 памяти. Сигнал с выхода элемента ИЛИ 31 задерживается на элементе 37 задержки и бпрашивает

элементы И 33 и 34.

I. При правильном чтении данных на

выходе блока 5 контроля присутствует высокий уровень сигнала, который

50 через элемент ИЛИ 32 разрешает формирование на выходе элемента И 34 импульса сопровождения считанных данных, присутствующих в этот момент на вьЬсодах 3 устройства. При чтении

55 д.анных с ошибкой на выходе блока 5 контроля присутствует низкий уровень сигнала. Повторно операция чтения выполняется при условий, что триггер

IIустановлен в нулевой состояние.

разрешения выборки накопителей 24 и 25 подаются сигналы с выходов элементов ИЛИ 15 и 16. Запись данньпх производится в оба накопителя при нулевом состоянии старшего разряда счетчика 9 объема, т.е. до момента заполнения наполовину буферного запоминающего устройства. При этом высокий уровень

сигнала на инверсном выходе триггера 12 через элемент И 17 и элементы ИЛИ 15 и 16 поступает на входы разрешения выборки накопителей 24 и 25. По заднему фронту сигнала на входе

19 разрешения записи производится модификация содержимого счетчиков 7 и 9, т.е. к их содержимому добавляется единица.. Высокий уровень сигнала на выходе старшего разряда счетчика

ное состояние, при котором запрещает дублирования записываемых данных.Повторная установка триггера 12 в нулевое состояние возможна сигналом переполнения счетчика 7 при нулевом сос-

тоянии старшего разряда счетчика 9. Запись последующих информационных слов осуществляется аналогично. При выполнении операции чтения

5

считывания, который является запросом чтения, поступает в формирователь 13 сигналов считывания, где устанавливает в нулевое состояние триггер 28 и, проходя через элемент ИЛИ 31

осуществляет запись считанных из блока 1 памяти данных в регистр 4. Чтение данных из блока 1 памяти производится по. адресу, сформированному Q на счетчике 8, выходные сигналы кото- , рого через открытый для них мультиплексор 6 поступает на адресные входы блока 1 памяти. Сигнал с выхода элемента ИЛИ 31 задерживается на элементе 37 задержки и бпрашивает

элементы И 33 и 34.

I. При правильном чтении данных на

выходе блока 5 контроля присутствует высокий уровень сигнала, который

0 через элемент ИЛИ 32 разрешает формирование на выходе элемента И 34 импульса сопровождения считанных данных, присутствующих в этот момент на вьЬсодах 3 устройства. При чтении

5 д.анных с ошибкой на выходе блока 5 контроля присутствует низкий уровень сигнала. Повторно операция чтения выполняется при условий, что триггер

IIустановлен в нулевой состояние.

свидетельствующее о том, что при выполнении операции записи выполнялось дублирование записи данных по этому адресу в оба накопителя 24 и 25.

. При высоком уровне сигнала на инверсном выходе триггера 11 разрешается прохождение через элемент И 33 выходного сигнала элемента ИЛИ 31, который задерживается на элементе 36 задержки, устанавливает триггер 28 в единичное состояние и через элемент ИЛИ .31 записывает вновь считанные данные в регистр 4. Чтение данных в этом случае производится из другого накопителя (24, 25), так как высокий уровень, сигнала на прямом выходе триггера 28 через элемент И 35 поступает на вход сумматора 14 по модулю два, выходной сигнал которого формирует сигналы разрешения выборки накопителей 24 и 25.

Выходной сигнал элемента 37 задержки через открытый элемент И 34 поступает на выход 21 сопровождения .считанных данных, сигнал на котором модифицирует содержимое счетчика 8 (добавляет единицу) и счетчика 9 (вычитает единицу). D-вход и вход синхронизации триггера 11 соединены соответственно с прямым выходом триггера 12 и выходом переполнения счетчика 8. Чтение последующих информационных слов из блока 1 памяти выполняется аналогично Дешифратор 10 формирует на выходах 22 и 23 сигналы состояния блока 1 памяти Память свободна и Память занята.

Технико-экономические преимущества предлагаемого буферного запоминаю- о и к первому входу формирователя сиг- щего устройства заключаются в его бо- налов считывания, второй вход которолее высокой информационной надежности по сравнению с известным, что позволит сократить потери информации при обработке и, тем самым, повысит эффективность работы систем обработки информации, использующих предлагаемое устройство.

Формула изобретения

Буферное запоминающее устройство, содержащее блок памяти, информационные входы которого являются информационными входами устройства, адресные входы блока памяти подключены к выходам группы мультиплексора, информационные входы первой и второй групп которого соединены с выходами первого и второго счетчиков соответственно, счетный вход первого счетчика подключен к входу прямого счета реверсивного счетчика и является входом разрешения записи устройства, выходы реверсивного счетчика подключены к входам дешифратора, первый и второй выходы которого являются соответственно выходами признаков.Память свободна и Память занята устройства, вход обратного счета реверсивного счетчика соединен со счетным входом второго счетчика, первый и второй

триггеры, элемент И, первый вход которого соединен с инверсным выходом первого триггера, отличающееся тем, что, с целью повышения надежности устройства, в него введены

сумматор по модулю два, регистр, два э лемента ИЛИ, блок контроля и формирователь сигналов считывания, причем информационные входы регистра соединены с выходами блока памяти, выход.

регистра подключен к входу блока контроля и является информационным выходом устройства, первый выход формирователя сигналов считывания соединен с входом обратного счета реверсивного счетчика и является выходом сопровождения считанных данных устройства, второй и третий выходы формирователя сигналов считьшания подключены к входу записи регистра и первому входу

сумматора по модулю два соответственно, управляющий вход мультиплексора подключен к входу разрешения записи устройства, к второму входу элемента И, входу задания режима блока памяти

го подключен к выходу блока контроля, третий и четвертый входы - к прямому и инверсному выходам второго триггеpa соответственно, пятый вход формирователя сигналов считывания подключен к входу разрешения считывания устройства, выход элемента И соединен с первыми входами первого и второго

элементов ИЛИ, выходы которых подключены к соответствующим входам разрешения выборки блока памяти, вторые входы первого и второго элементов ШШ соединены соответственно с прямьм и инверсным выходами сумматора по модулю два, второй вход которого подключен к выходу мультиплексора,входы синхронизации первого и второго триггеров соединены с выходами переполне

51361632 в

ния первого и второго счетчиков соот- триггера и выходу старшего разряда ветственно, установочный вход второго реверсивного счетчика, информационный триггера подключен к установочному вход второго триггера соединен с пряи информационному входам первого

2

27

16

/ уV

Фиг. 2

Редактор В. Петраш

Составитель Ю. Фомина Техред М.Дидык

Заказ 6297/52 Тираж 588Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

мым выходом первого триггера.

25

/V /V

Фиг.З

Корректор М. Шароши

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1288757A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Буферное запоминающее устройство | 1986 |

|

SU1312646A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1396158A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства систем обработки . информации. Цель изобретения - повышение надежности устройства. Буферное запоминающее устройство содержит блок 1 памяти, регистр 4, блок 5 контроля, мультиплексор 6, счетчики 7 и 8, реверсивный счетчик 9, дешифратор 10, триггеры 11, 12, формирователь 13 сигналов считьшания, сумматор 14 по модулю два, элементы ИЛИ 15, 16, элемент И 17, входы и выходы устройства. Устройство позволяет сократить потери информации при обработке и тем самым повысить эффективность работы систем обработки информации. 3 ил. СО Oi 05 СО

| Буферное запоминающее устройство | 1983 |

|

SU1176382A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-07-31—Подача