Изобретение относится к области вычислительной техники и может быть использовано в устройствах вывода электронных вычислительных машин и телеметрических устройствах.

Целью изобретения является повышение точности интегрирования за счет обеспечения ввода кода начальной загрузки для уменьшения среднего значения и максимального значения ошибок.

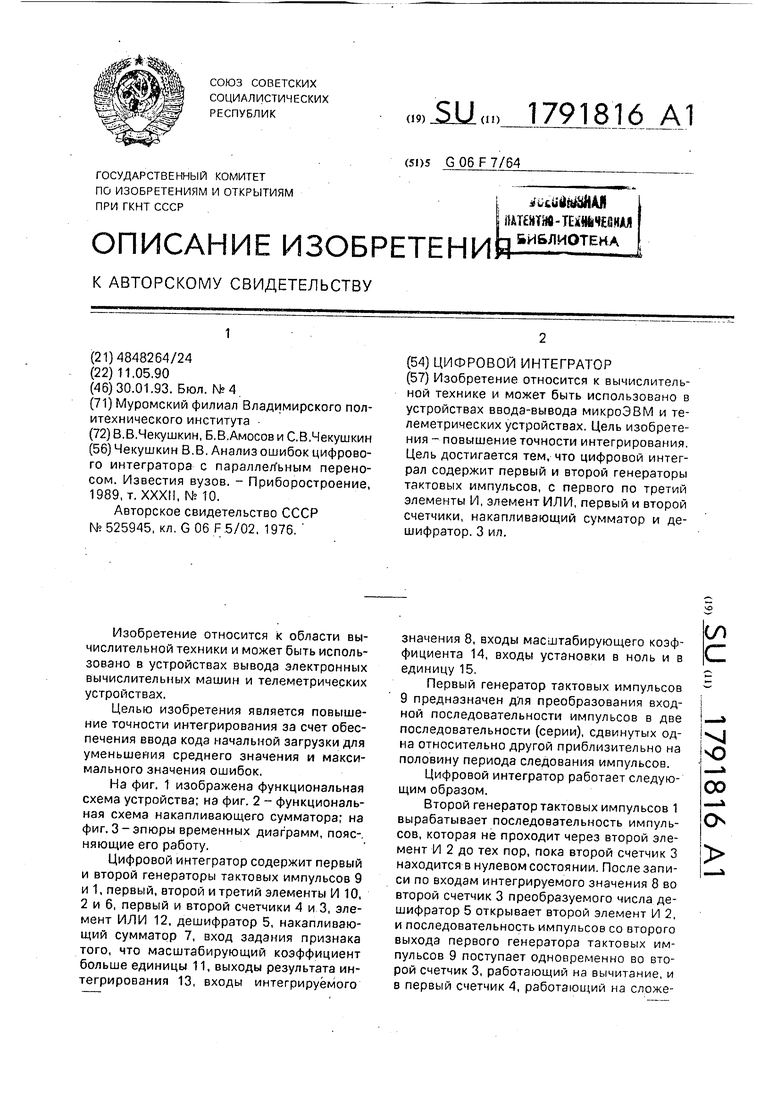

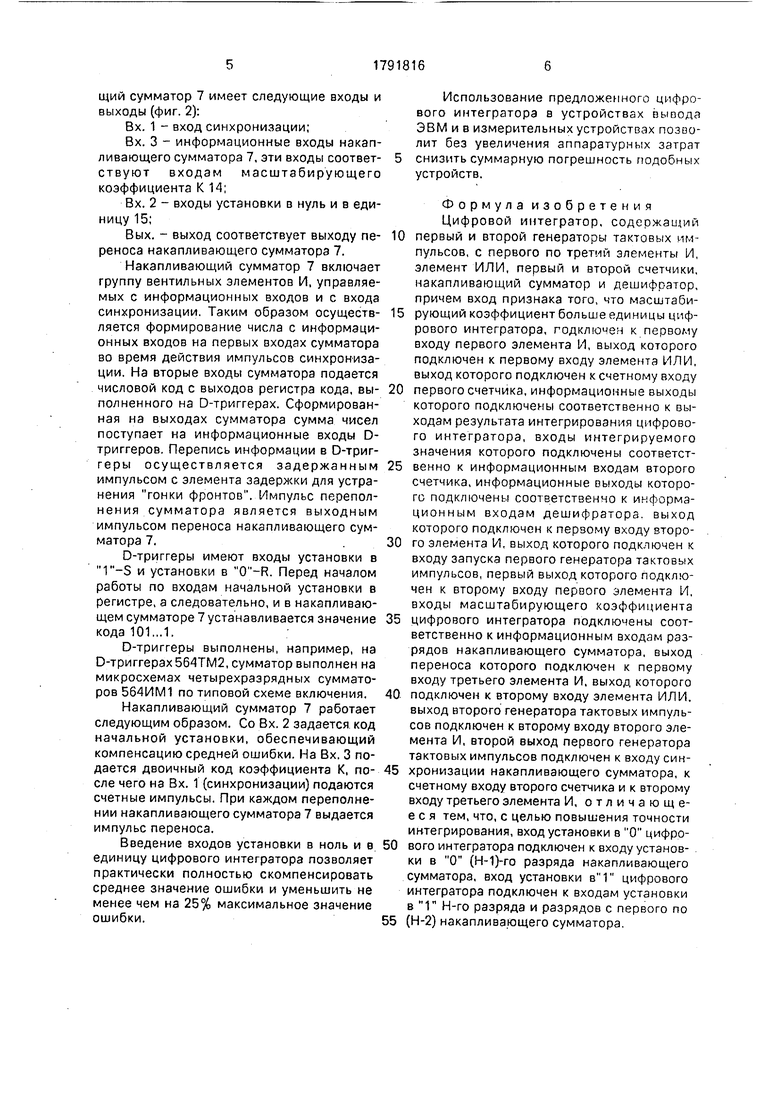

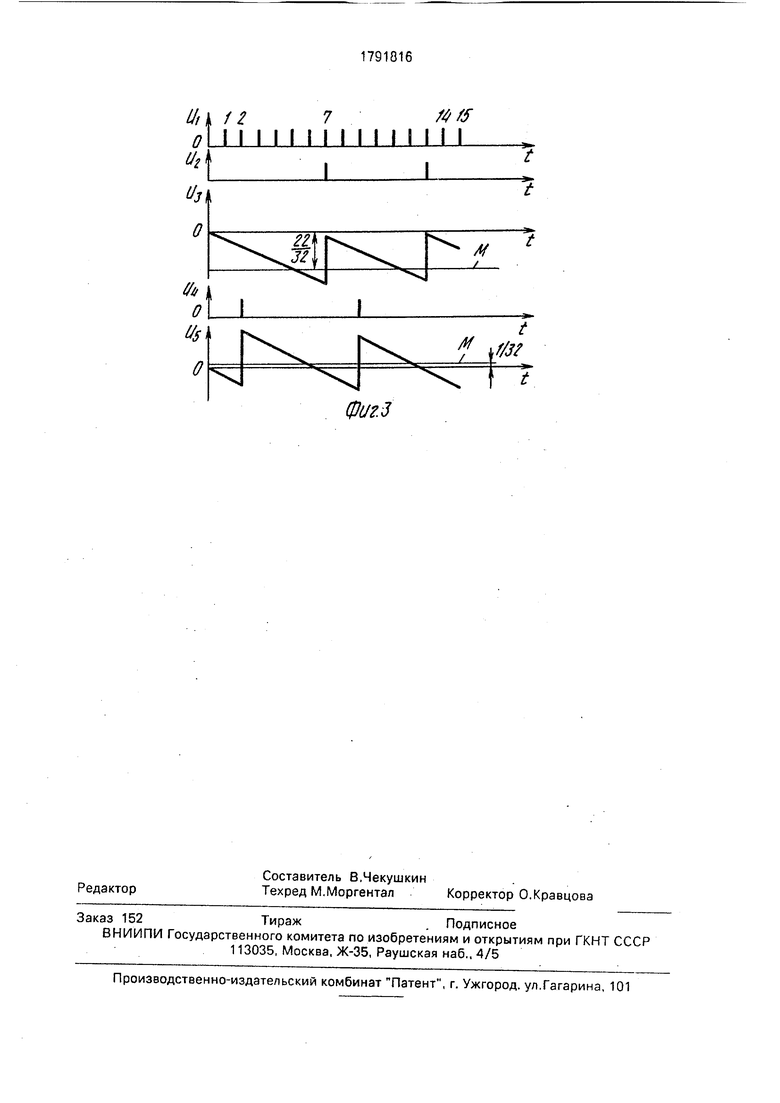

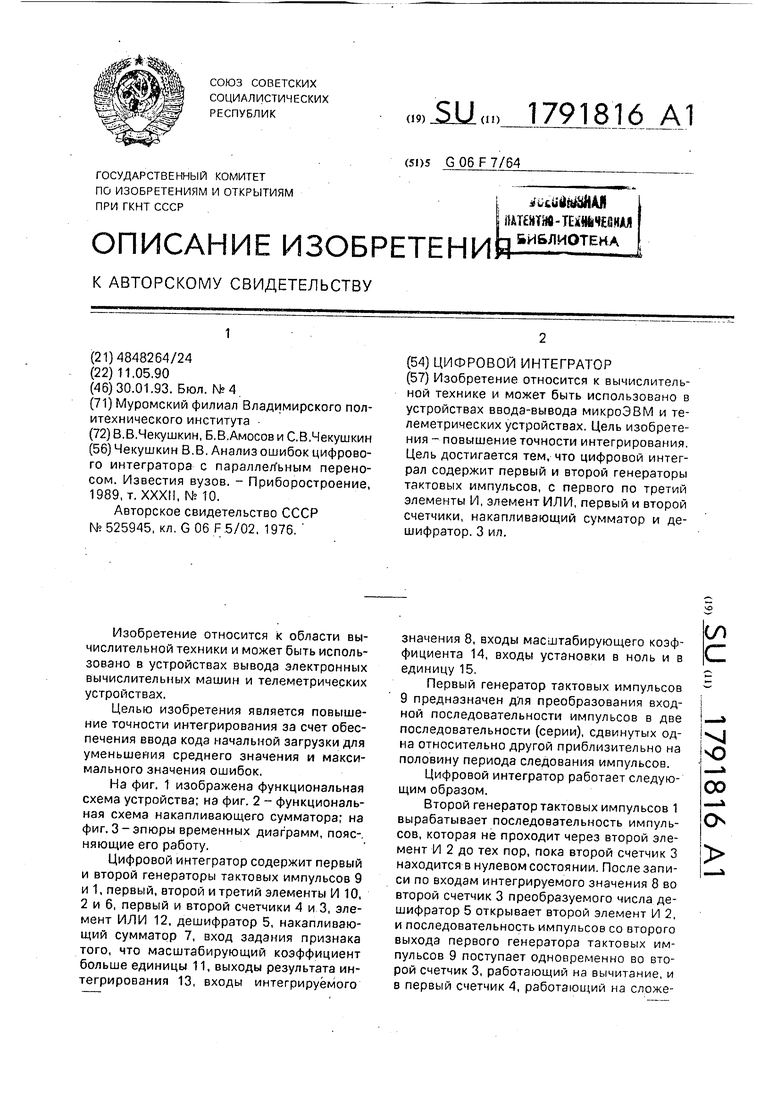

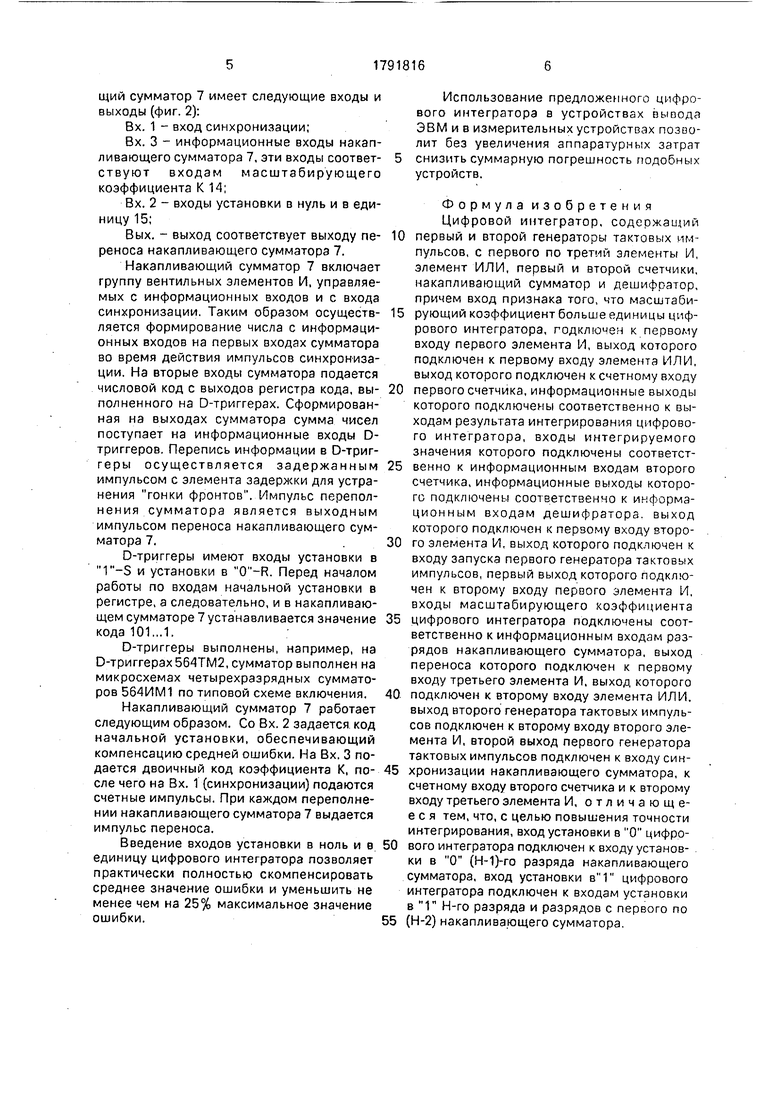

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональная схема накапливающего сумматора; на фиг. 3-эпюры временных диаграмм, поясняющие его работу.

Цифровой интегратор содержит первый и второй генераторы тактовых импульсов 9 и 1, первый, второй и третий элементы И 10, 2 и 6, первый и второй счетчики 4 и 3, элемент ИЛИ 12, дешифратор 5, накапливающий сумматор 7, вход задания признака того, что масштабирующий коэффициент больше единицы 11, выходы результата интегрирования 13, входы интегрируемого

значения 8, входы масштабирующего коэффициента 14, входы установки в ноль и в единицу 15.

Первый генератор тактовых импульсов 9 предназначен для преобразования входной последовательности импульсов в две последовательности (серии), сдвинутых одна относительно другой приблизительно на половину периода следования импульсов.

Цифровой интегратор работает следующим образом.

Второй генератор тактовых импульсов 1 вырабатывает последовательность импульсов, которая не проходит через второй элемент И 2 до тех пор, пока второй счетчик 3 находится в нулевом состоянии. После записи по входам интегрируемого значения 8 во второй счетчик 3 преобразуемого числа дешифратор 5 открывает второй элемент И 2, и последовательность импульсов со второго выхода первого генератора тактовых импульсов 9 поступает одновременно во второй счетчик 3, работающий на вычитание, и в первый счетчик 4, работающий на сложесо С

vj о

со о

ние импульсов. При этом во второй счетчик 3 импульсы поступают непосредственно, а в первый счетчик 4 - через третий элемент И 6 при совпадении с импульсами переноса накапливающего сумматора 7. В момент равенства счетных импульсов двоичному числу, записанному ранее во второй счетчик 3, дешифратор 5 закрывает второй элемент 1/12. При этом во втором счетчике 4 фиксируется выходное число, например, в двоично-десятичном коде, умноженное на масштабирующий коэффициент К, код которого устанавливается на входах 14 и 11,

Например, при перед преобразованием на вход признака масштабного коэффициента подается сигнал О (так как ), а на входы масштабирующего коэффициента цифрового интегратора 14 - код дробной части числа К, т.е. 0,00101.

Число К будет добавляться в накапливающий сумматор 7 при поступлении на его вход синхронизации каждого импульса со второго выхода первого генератора тактовых импульсов 9. При этом число импульсов переполнения- накапливающего сумматора 7, а следовательно, и число счет- ных импульсов на выходе третьего элемента И 6 будет пропорционально К.

Временная диаграмма работы устройства приведена на фиг. 3.. Эпюра Ui изображает импульсы на входе синхронизации накапливающего сумматора 7 и в счетном входе второго счетчика 3. Эпюры )г и Уз - соответственно импульсы на выходе третьего элемента И 6, погрешность преобразования при и начальном состоянии сумматора 00000. Значение погрешности по оси ординат откладывается в долях единицы младшего разряда выходного кода, Значение ошибки определяется по.отношению к идеальному алгоритму интегрирования. На эпюре Уз горизонтальной линией показано также значение математического ожидания при числе разрядов накапливающего сумматора . В общем случае значение математического ожидания, относимое ко всем комбинациям значений коэффициента К, определяется выражением

гт п 3 - 3 + п t n 4 77

22

Для получим , 5

Поскольку в процессе работы остаток в накапливающем сумматоре 7 всегда меньше 1, то в результате интегрирования в первом счетчике 4 будет зафиксировано число

0

5

0

5

0

5

0

31 ,

7мзкс -у2 (К°Д в на

с погрешностью, не превышающей единицы младшего разряда выходного кода. При нулевом начальном состоянии накапливающего сумматора 7 (эпюра Уз) указанная погрешность всегда отрицательна, и ее максимальное абсолютное значение равно

/макс 1-2 п, Для ,,

капливающем сумматоре 7 11111).

При произвольном начальном состоянии накапливающего сумматора 7 погрешность в общем случае будет разнополярной, и ее максимальное абсолютное значение тока может быть близко к единице, а среднее значение ошибки не скомпенсировано. Поэтому в предложенном цифровом интеграторе перед началом пересчета по-входам установки в единицу и в ноль 15 в накапливающий сумматор 7 заносят код 10111, т.е. триггеры Н-го разряда и разрядов с первого по (Н-2)-й накапливающего сумматора 7 устанавливаются в единицу, а (Н-1)-го разряда - в ноль. Тогда при пересчете независимо от величины К первый и все последующие импульсы переноса с выхода накапливающего сумматора 7 будут появляться раньше по отношению к импульсам переноса накапливающего сумматора 7 при его начальном нулевом состоянии, вследствие чего средняя ошибка будет практически скомпенсирована. На эпюрах Ш и Us приведены соответственно импульсы на выходе третьего элемента И 6 и погрешность преобразования при и начальной установке накапливающего сумматора 7 в состояние 10111. На эпюре Us горизонтальной линией показано также значение математического ожидания ошибки после его компенсации, 1

т.е.

32

Уменьшение среднего значения ошибки интегратора производится более чем в 10 раз. Контур изменения максимальной ошибки остается прежним, но смещается. Максимальная ошибка уменьшается не менее чем на 25%.

Если , то перед началом пересчета на вход признака масштабного коэффициента 11 подают сигнал 1, разрешающий дополнительно прохождение импульсов с первого выхода первого генератора тактовых импульсов в первый счетчик 4. В остальном схема работает так же, как и при .

Введение входов начальной установки в ноль и в единицу позволяет уменьшить среднее значение ошибки практически до О, а максимальное значение - на 25%.

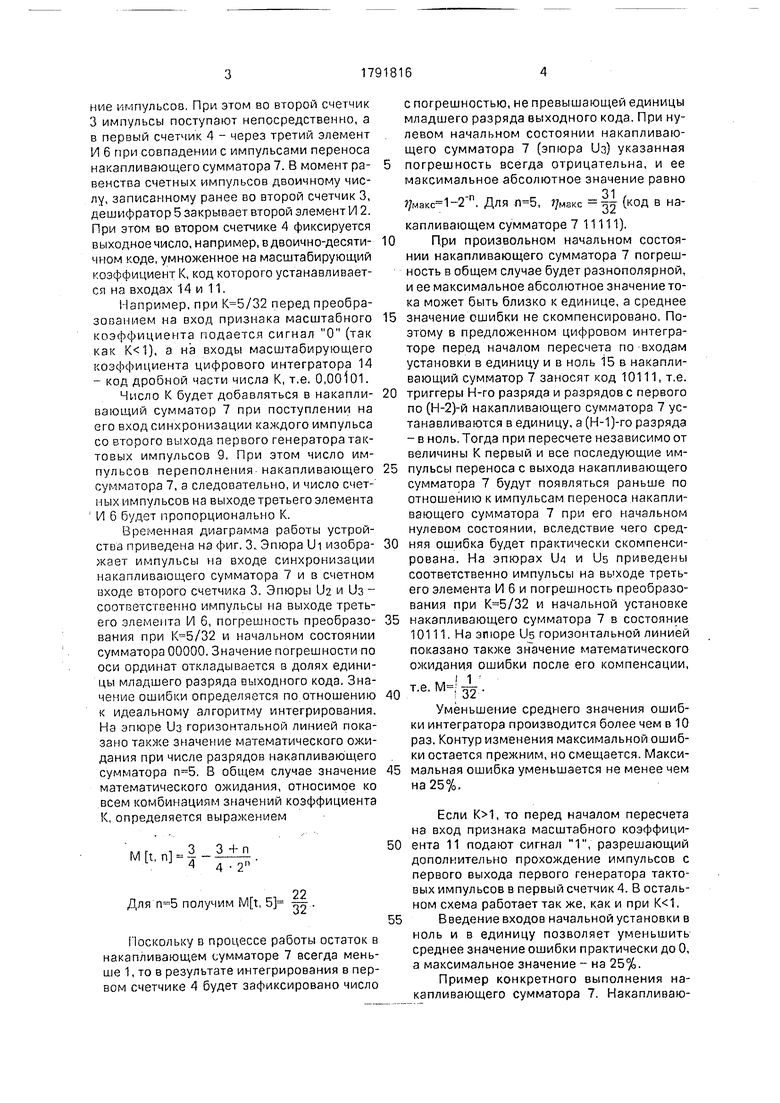

Пример конкретного выполнения накапливающего сумматора 7. Накапливающий сумматор 7 имеет следующие входы и выходы (фиг. 2):

Вх. 1 - вход синхронизации;

Вх. 3 - информационные входы накапливающего сумматора 7, эти входы соответствуют входам масштабирующего коэффициента К 14;

Вх. 2 - входы установки в нуль и в единицу 15;

Вых. - выход соответствует выходу переноса накапливающего сумматора 7.

Накапливающий сумматор 7 включает группу вентильных элементов И, управляемых с информационных входов и с входа синхронизации. Таким образом осуществляется формирование числа с информационных входов на первых входах сумматора во время действия импульсов синхрон-иза- ции. На вторые входы сумматора подается числовой код с выходов регистра кода, выполненного на D-триггерах. Сформированная на выходах сумматора сумма чисел поступает на информационные входы D- триггеров. Перепись информации в D-триг- геры осуществляется задержанным импульсом с элемента задержки для устранения гонки фронтов. Импульс переполнения сумматора является выходным импульсом переноса накапливающего сумматора 7.

D-триггеры имеют входы установки в и установки в . Перед началом работы по входам начальной установки в регистре, а следовательно, и в накапливающем сумматоре 7 устанавливается значение кода 101...1.

D-триггеры выполнены, например, на D-триггерах 564ТМ2, сумматор выполнен на микросхемах четырехразрядных сумматоров 564ИМ1 по типовой схеме включения.

Накапливающий сумматор 7 работает следующим образом. Со Вх. 2 задается код начальной установки, обеспечивающий компенсацию средней ошибки. На Вх. 3 подается двоичный код коэффициента К, после чего на Вх. 1 (синхронизации) подаются счетные импульсы. При каждом переполнении накапливающего сумматора 7 выдается импульс переноса.

Введение входов установки в ноль и в. единицу цифрового интегратора позволяет практически полностью скомпенсировать среднее значение ошибки и уменьшить не менее чем на 25% максимальное значение ошибки.

Использование предложенного цифрового интегратора в устройствах вывода ЭВМ и в измерительных устройствах позволит без увеличения аппаратурных затрат снизить суммарную погрешность подобных устройств.

Формула изобретения Цифровой интегратор, содержащий

первый и второй генераторы тактовых импульсов, с первого по третий элементы И, элемент ИЛИ, первый и второй счетчики, накапливающий сумматор и дешифратор, причем вход признака того, что масштабирующий коэффициент больше единицы цифрового интегратора, подключен к первому входу первого элемента И, выход которого подключен к первому входу элемента ИЛИ, выход которого подключен к счетному входу

первого счетчика, информационные выходы которого подключены соответственно к выходам результата интегрирования цифрового интегратора, входы интегрируемого значения которого подключены соответственно к информационным входам второго счетчика, информационные выходы которого подключены соответственно к информационным входам дешифратора, выход которого подключен к первому входу второго элемента И, выход которого подключен к входу запуска первого генератора тактовых импульсов, первый выход которого подключен к второму входу первого элемента И, входы масштабирующего коэффициента

цифрового интегратора подключены соответственно к информационным входам разрядов накапливающего сумматора, выход переноса которого подключен к первому входу третьего элемента И. выход которого

подключен к второму входу элемента ИЛИ, выход второго генератора тактовых импульсов подключен к второму входу второго элемента И, второй выход первого генератора тактовых импульсов подключен к входу синхронизации накапливающего сумматора, к счетному входу второго счетчика и к второму входу третьего элемента И, отличающееся тем, что, с целью повышения точности интегрирования, вход установки в О цифрового интегратора подключен к входу установки в О (Н-1)-го разряда накапливающего сумматора, вход установки цифрового интегратора подключен к входам установки в Г Н-го разряда и разрядов с первого по

(Н-2) накапливающего сумматора.

1791816

8

у у w v v

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

| Цифровой генератор инфранизких частот | 1982 |

|

SU1051693A1 |

| СПОСОБ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА НА ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА РАКЕТЕ. ЛИНЕАРИЗАТОР СИГНАЛА. ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА. СПОСОБ ИНТЕГРИРОВАНИЯ ДЛЯ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2549231C1 |

| Устройство для определения спектральных коэффициентов разложения случайного процесса по функциям Хаара | 1980 |

|

SU935814A1 |

| СПОСОБ УПРАВЛЕНИЯ ГРУППОЙ ИМПУЛЬСНЫХ ПРЕОБРАЗОВАТЕЛЕЙ | 1983 |

|

SU1284443A1 |

| Устройство для преобразования координат объекта | 1980 |

|

SU951317A1 |

| СЧЕТЧИК ПОТЕРЬ ЭЛЕКТРОЭНЕРГИИ С ИНДИКАЦИЕЙ ПОТЕРЬ МОЩНОСТИ (ВАРИАНТЫ) | 2010 |

|

RU2449356C1 |

| ИЗМЕРИТЕЛЬ КООРДИНАТ ПОДВИЖНЫХ ОБЪЕКТОВ | 1986 |

|

SU1436846A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах ввода-вывода микроЭВМ и телеметрических устройствах. Цель изобретения -- повышение точности интегрирования. Цель достигается тем, что цифровой интеграл содержит первый и второй генераторы тактовых импульсов, с первого по третий элементы И, элемент ИЛИ, первый и второй счетчики, накапливающий сумматор и дешифратор. 3 ил.

Cto/г.;

Ист.8 „О

V | у у j,tf

О

ut

Уз О

&

о

%

о

Af

L-

№

фиг.З

| Чекушкин В.В | |||

| Анализ ошибок цифрового интегратора с параллельным переносом | |||

| Известия вузов | |||

| - Приборостроение, 1989, т | |||

| XXXII, № 10 | |||

| Преобразователь кода | 1974 |

|

SU525945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-30—Публикация

1990-05-11—Подача