Изобретение относится к вычислительной технике и может найти применение при построении средств коммутации мультипроцессорных систем,абонентских систем связи с децентрализованным управлением, коммутационных средств параллельного обмена информацией в измерительных системах.

Известен модуль матричного коммутатора, содержащий блоки организации очереди сообщений, мультиплексор, регистр идентификатора модуля, демультиплексор, регистр, триггер, два дешифратора, блок синхронизации, блок анализа очереди сообщений, два элемента сравнения, элемент И.

Недостатком основного изобретения является ограниченная область его применения, обусловленная следующим. Передача сообщений осуществляется по двум конвейерам - по горизонтали и вертикали. Этим достигается полная связность в системе, коммутационная сеть которой основана на базе сети однотипных модулей. Однако, например, при отказе одного из модулей нарушается обмен сообщениями как в вертикальном, так и горизонтальном конвейере, что приводит к ограничению обменных взаимодействий, Кроме того, в вычислительных системах возникает необходимость адаптивной настройки средств передачи сообщений. В известном устройстве такая возможность отсутствует.

Целью изобретения является расширение функциональных возможностей за счет возможности изменения направления передачи на противоположное.

Поставленная цель достигается тем, что модуль матричного коммутатора, содержащий с первого по пятый блоки организации очереди сообщений, мультиплексор, блок анализа очереди сообщений, блок синхронизации, две схемы сравнения, демультиплексор, триггер запуска, два дешифратора. регистр идентификатора модуля, регистр, элемент И, причем первый выход блока синхронизации соединен с управляющим входом регистра идентификатора модуля и синхронизирующим входом регистра, выход первого поля которого соединен с информационным входом демультиплексора, первый выход которого соединен с первым выходом модуля, первые выход перпого-пяел С

XI

О

СА

N О)

о

ND

того блоков организации очереди сообщений с соответствующими информационными входами мультиплексора, прямой выход триггера запуска соединен с управляющим входом блока синхронизации, второй выход которого соединен с тактовыми входами первого-пятого блоков организации очереди сообщений, выход элемента И соединен с R-входом триггера запуска; третий выход блока синхронизации соединен с информационным входом дёмультиплексора и прямым, входом элемента И, выходы первого дешифратора соединены с соответствующими управляющими входами первого-пя- тотр блоков организации очереди сообщений, выходы первой и второй схем сравнения.соединены с входами второго дешифратора, выход которого соединен с уп- р а в гся ю щи м .вх о до м де му л ьти о л е к с о ра, п е рвы ивы ход ре гистра и дентифи катора модуля соединен с первым входом первой схемы: сравнения, второй вход которой соединен с выходом второго поля регистра и информационным входом демультиплексора, второй выход регистра идентификатора модуля соединен с первым входом -второй схемы сравнения, второй вход которой соединен с выходом демутильтиплексо- ра, вторые выходы первого-пятого блоков организации очереди сообщений соединены с входом блока анализа очереди сообще- ний, выход которого соединен с управляющим входом мультиплексора, и входом первого дешифратора, выход. мультиплексора соединен с информационным входам регистра, управляющий выход блока анализа очереди сообщений соединен с S-входом триггера запуска и инверсным входом элемента И, дополнительно содержит с первого по четвертый входные демультиплексоры, с первого по четвертый блохи элементов ИЛИ, триггер управления, вход установки в начальное состояние которого соединен суправляющим входо м.мод у- л я, прямой выход триггера управления соединен с управляющими входами перво- го-четверто го входных .демультиплексоров, первые выходы которых соединены с ин-. форма ционными входами соответственно второго-пято го блоков организации очереди сообщений, вторые выходы первогр-чет- вертото входных демультиплексоров соединены с первыми входами блоков с Т по 4 элементов ИЛИ, выходи которых соединены с выходами обмена модуля, входы обменакоторого соединены с информационными входами входных де- мультиплексоров, вторые входы первого- четвертого блоков элементов ИЛИ

соединены соответственно с вторым-пятым выходами демультиплексора.

Сущность изобретения состоит в следующем. В системе распределенной обработки матричного типа коммутации сообщений осуществляется матричным коммутатором, состоящим из однотипных модулей (М), Каждому модулю присваивается номер, идентификатор, определяющий его

О местоположение в матрице однотипных модулей. Коммутация сообщений в матрице модулей осуществляется по горизонтали (по строкам) и вертикали (столбце). При этом вертикальный и горизонтальный обмен в

5 матрице модулей реализуется в виде двух однонаправленных колец: сверху-вниз; снизу-вверх; справа-налево и слева-направо. Каждый модуль коммутации может изменить направление передачи сообще0 ния на противоположное направление и тем самым расширить функциональные возможности модуля, а следовательно, и область целесообразного его применения.

Определение принадлежности сообще5 ния происходит путем анализа поступившей информации на основе сравнения кода идентификатора модуля и адреснойУчасти передаваемого сообщения. При несовпадении этих кодов сообщение передается сл.е0 дующему модулю.

Введение первого-четвертого демультиплексоров и обусловленных ими связей . необходимо для коммутации поступающих сообщений либо к данному модулю, либо

5 транзитом к соседним модулям коммутации. ..

Введение триггера управления и обусловленных им связей необходимо для идентификации и управления, передачей

0 транзитом поступающих сообщений.

Введение первого-четвертогб блоков элементов ИЛИ и обусловленных ими связей необходимо для сборки сообщений от собственного модуля либо от модулей, пере5 дающих сообщения транзитом.

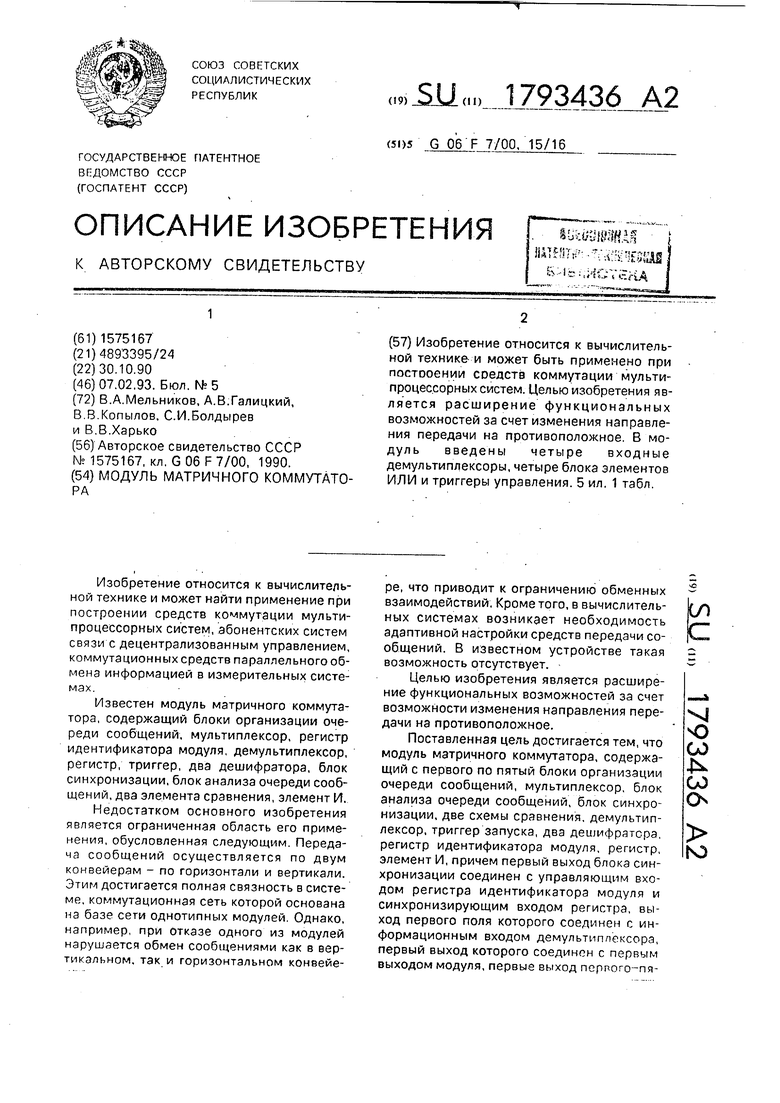

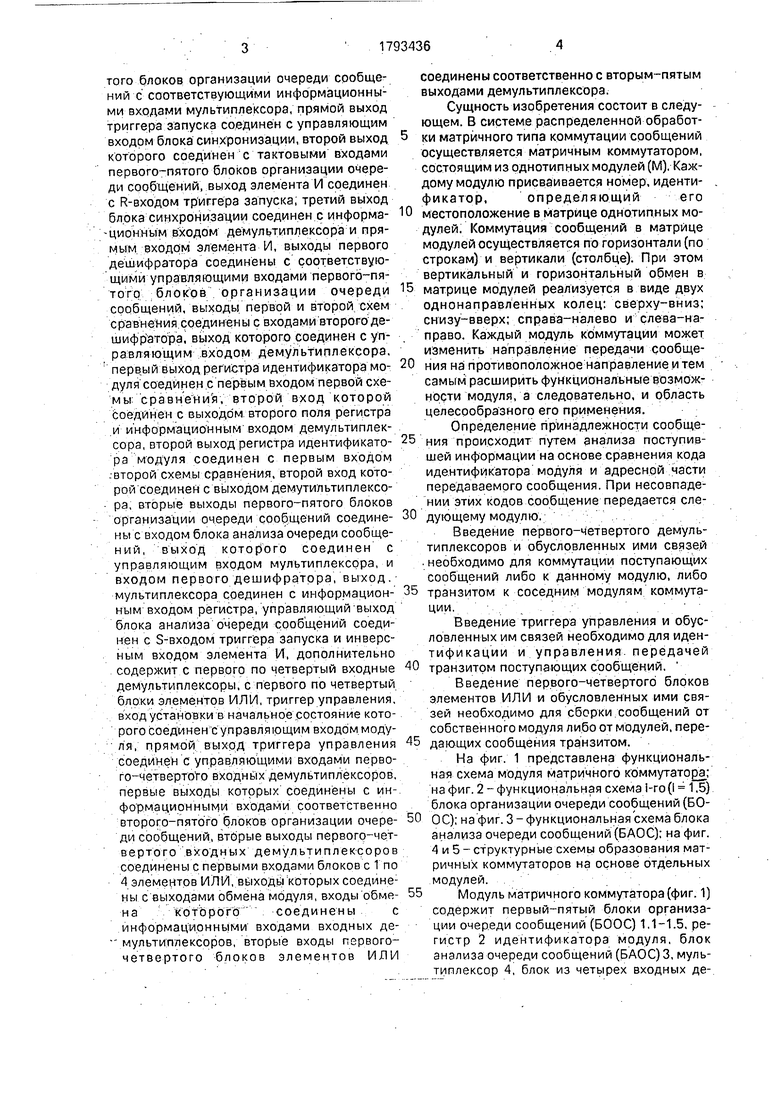

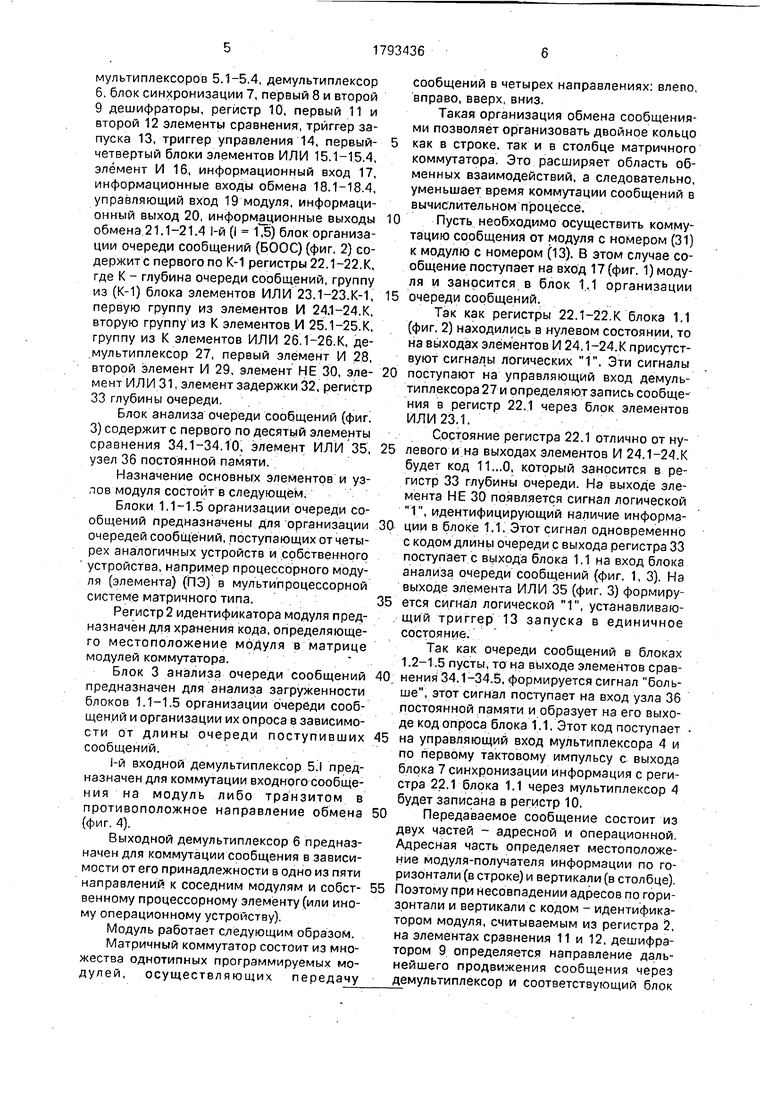

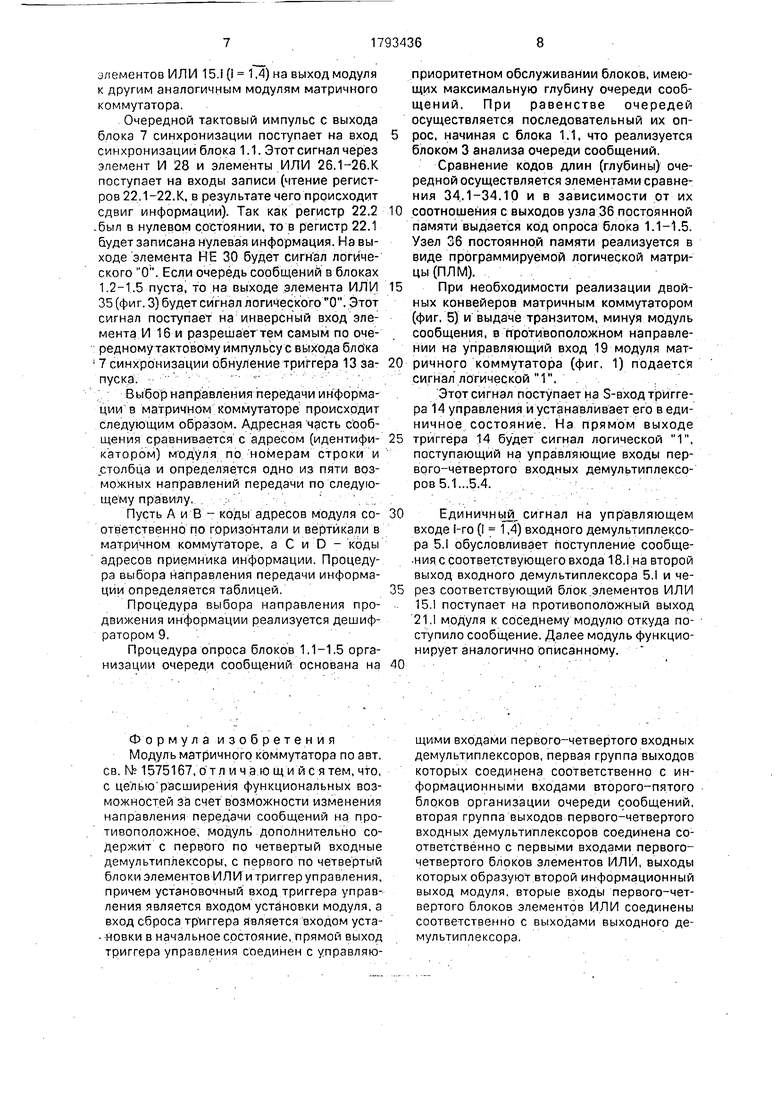

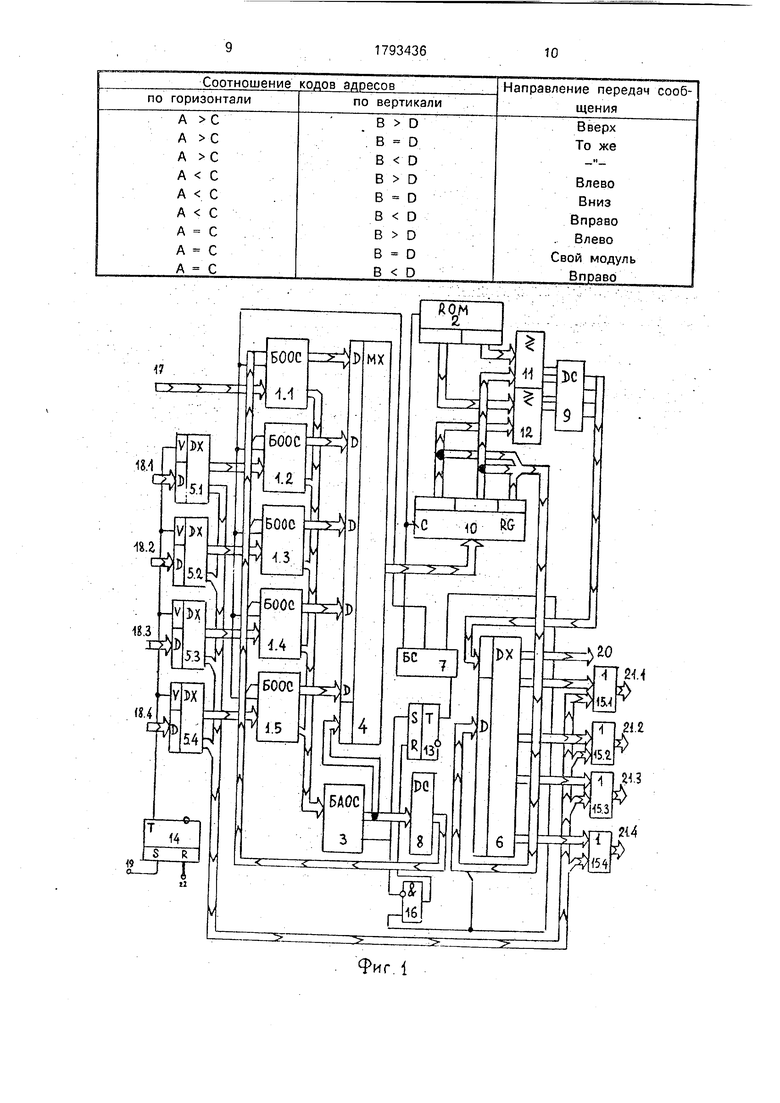

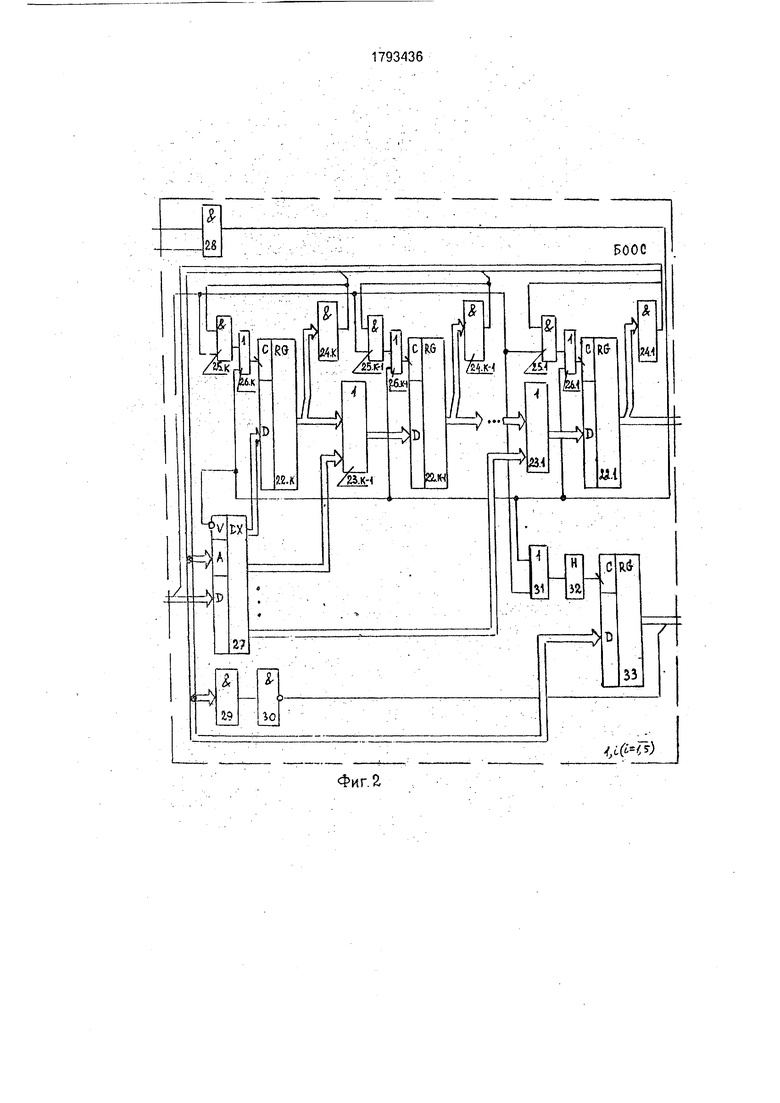

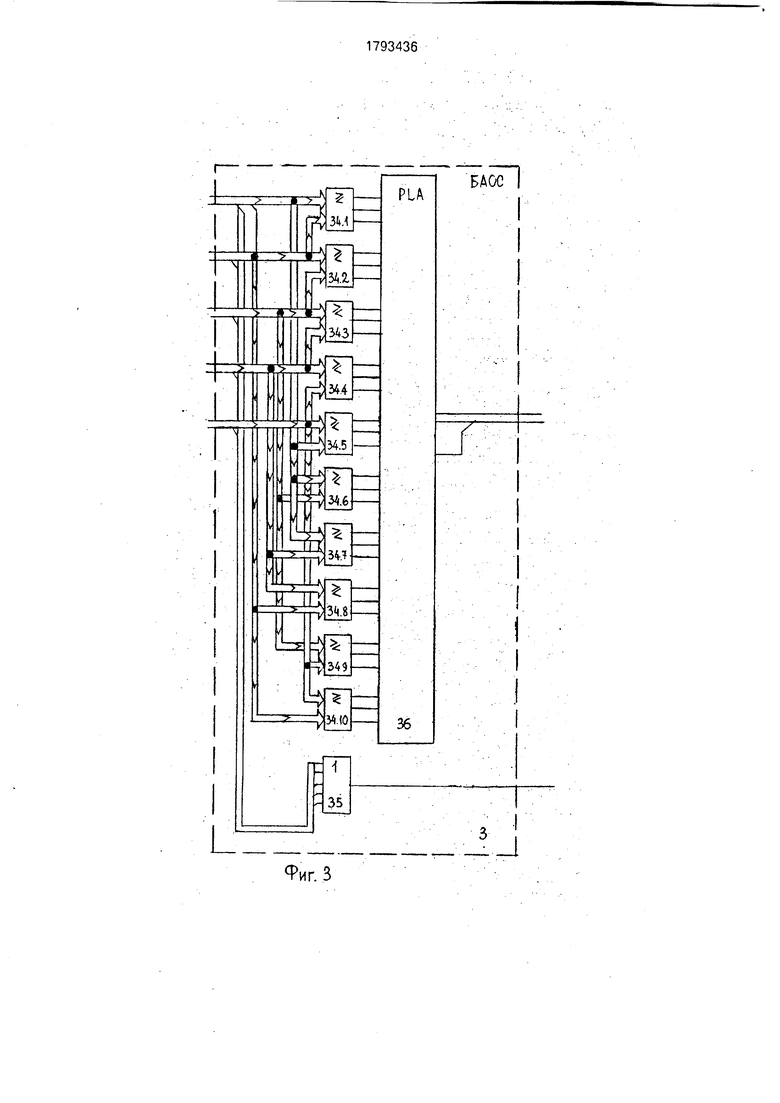

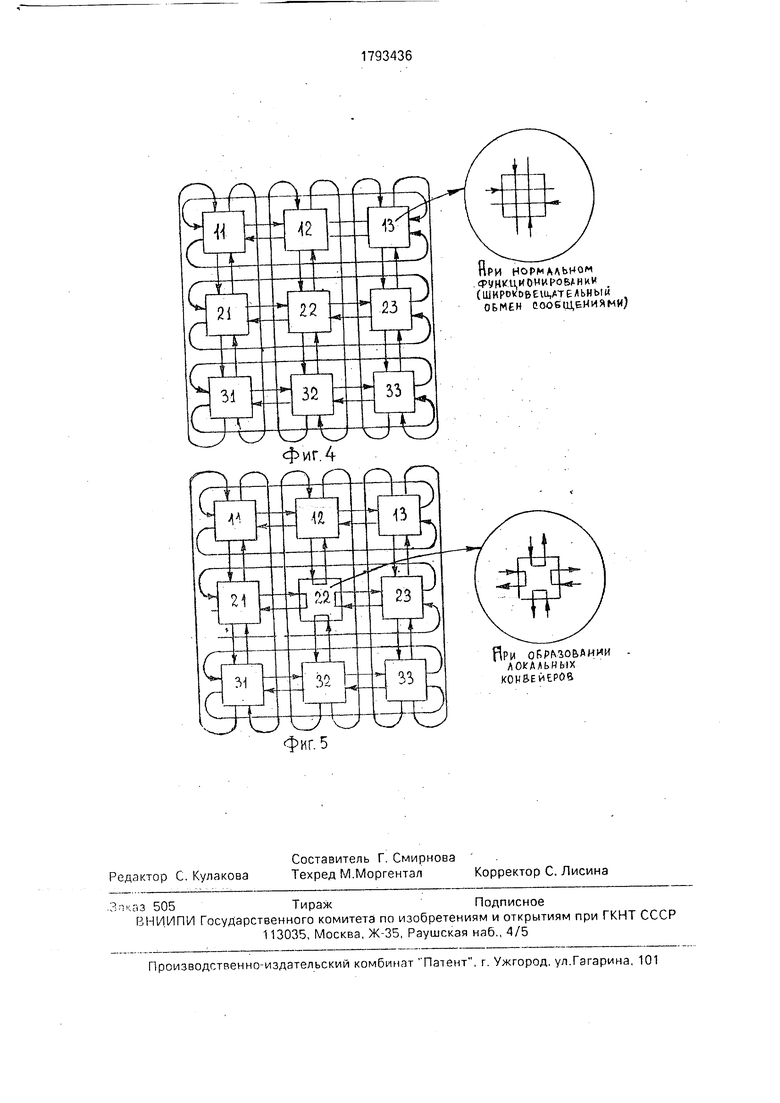

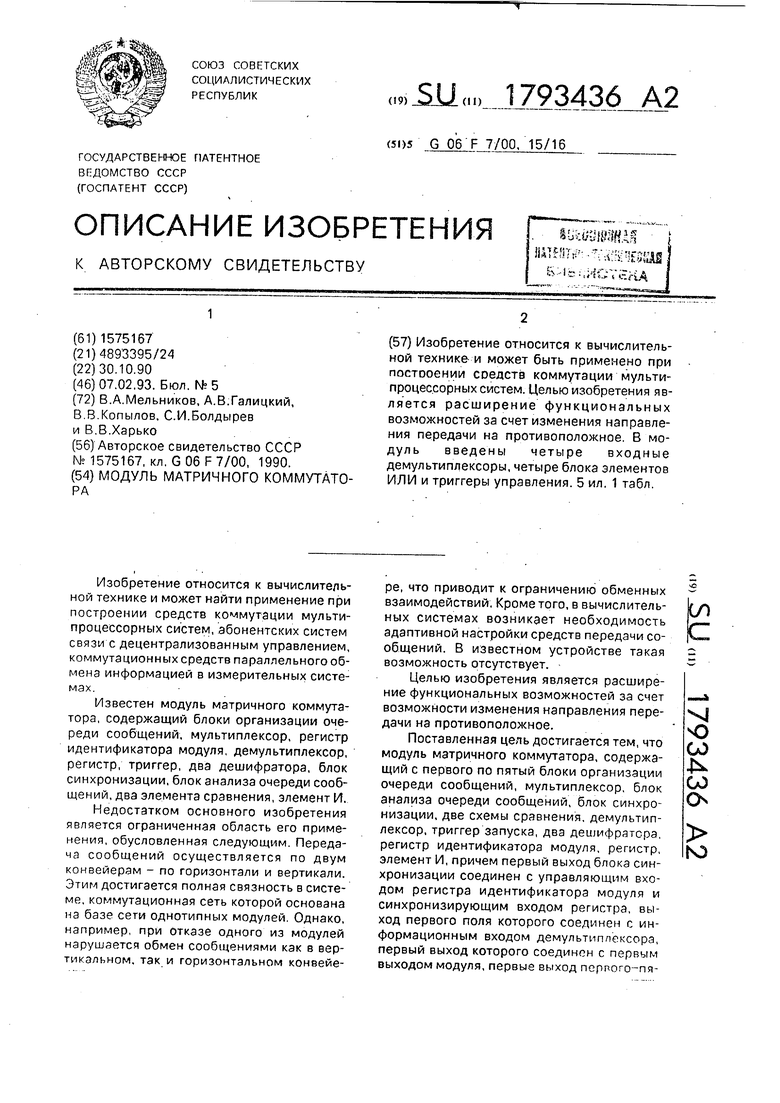

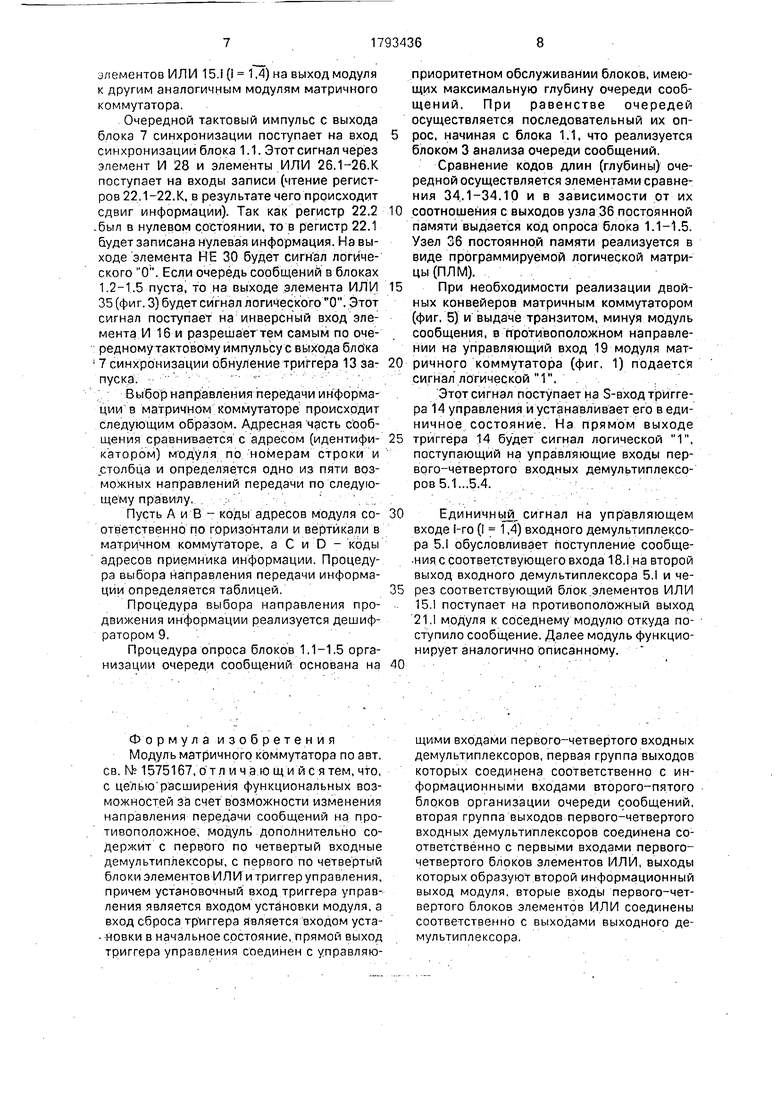

На фиг. 1 представлена функциональная схема модуля матричного коммутатору; на фиг. 2-функциональная схема i-ro(l 1.5). блока организации очереди сообщений (БО0 ОС); на фиг. 3-функциональная схема блока анализа очереди сообщений (БАОС); на фиг. 4 и 5-структурные схемы образования матричных коммутаторов на основе отдельных .модулей. .

5 Модуль матричного коммутатора (фиг. 1) содержит первый-пятый блоки организации очереди сообщений (БООС) 1,1-1.5, регистр 2 идентификатора модуля, блок анализа очереди сообщений (БАОС) 3, мультиплексор 4, блок из четырех входных демультиплексоров 5.1-5.4, демультиплексор 6. блок синхронизации 7, первый 8 и второй 9 дешифраторы, регистр 1.0. первый 11 и второй 12 элементы сравнения, триггер запуска 13, триггер управления 14, первый- четвертый блоки элементов ИЛИ 15.1-15.4, элемент И 16, информационный вход 17, информационные входы обмена 18.1-18.4, управляющий вход 19 модуля, информационный выход 20, информационные выходы обмена 21.1-21.4 1-й (I 1,5) блок организации очереди сообщений (БООС) (фиг. 2} содержит с первого по К-1 регистры 22.1-22.К, где К - глубина очереди сообщений, группу из (К-1) блока элементов ИЛИ 23.1-23.К-1, первую группу из элементов И 24.1-24.К, вторую группу из К элементов И 25.1-25. К, группу из К элементов ИЛИ 26.1-26.К, де- .мультиплексор 27, первый элемент И 28, второй элемент И 29, элемент НЕ 30, элемент ИЛИ 31, элемент задержки 32, регистр 33 глубины очереди.

Блок анализа очереди сообщений (фиг. 3) содержит с первого по десятый элементы сравнения 34.1-34.10. элемент ИЛИ 35, узел 36 постоянной памяти.

Назначение основных элементов и узлов модуля состоит в следующем.

Блоки 1.1-1.5 организации очереди сообщений предназначены для организации очередей сообщений, поступающих от четырех аналогичных устройств и собственного устройства, например процессорного модуля (элемента) (ПЭ) в мультипроцессорной системе матричного типа.

Регистр 2 идентификатора модуля предназначен для хранения кода, определяющего местоположение модуля в матрице модулей коммутатора.

Блок 3 анализа очереди сообщений предназначен для анализа загруженности блоков 1,1-1.5 организации очереди сообщений и организации их опроса в зависимости от длины очереди поступивших сообщений.

i-й входной демультиплексор 5.1 предназначен для коммутации входного сообщения на модуль либо транзитом в противоположное направление обмена (фиг. 4).

Выходной демультиплексор б предназначен для коммутации сообщения в зависимости от его принадлежности в одно из пяти направлений к соседним модулям и собственному процессорному элементу (или иному операционному устройству).

Модуль работает следующим образом.

Матричный коммутатор состоит из множества однотипных программируемых модулей, осуществляющих передачу

сообщений в четырех направлениях: влево, вправо, вверх, вниз.

Такая организация обмена сообщениями позволяет организовать двойное кольцо 5 как в строке, так и в столбце матричного коммутатора. Это расширяет область обменных взаимодействий, а следовательно, уменьшает время коммутации сообщений в вычислительном процессе.

0 Пусть необходимо осуществить коммутацию сообщения от модуля с номером (31) к модулю с номером (13). В этом случае сообщение поступает на вход 17 (фиг. 1) модуля и заносится в блок 1.1 организации

5 очереди сообщений.

Так как регистры 22.1-22.К блока 1.1 (фиг. 2) находились в нулевом состоянии, то на выходах элементов И 24,1-24.К присутствуют сигналы логических Г. Эти сигналы

.0 поступают на управляющий вход демуль- типлексора 27 и определяют запись сообщения в регистр 22.1 через блок элементов ИЛИ 23.1.

Состояние регистра 22.1 отлично от ну5 левого и.на выходах элементов И 24.1-24.К будет код 11...О, который заносится в регистр 33 глубины очереди. На выходе элемента НЕ 30 появляется сигнал логической 1, идентифицирующий наличие информз0- ции в блоке 1,1. Этот сигнал одновременно с кодом длины очереди с выхода регистра 33 поступаете выхода блока 1.1 на вход блока анализа очереди сообщений (фиг. 1, 3). На выходе элемента ИЛИ 35 (фиг. 3) формиру5 ется сигнал логической 1, устанавливаю- , щий триггер 13 запуска в единичное состояние.

Так как очереди сообщений в блоках 1.2-1.5 пусты, то на выходе элементов срав0 нения 34.1-34.5, формируется сигнал больше, этот сигнал поступает на вход узла 36 постоянной памяти и образует на его выходе код опроса блока 1.1. Этот код поступает .

5 на управляющий вход мультиплексора 4 и по первому тактовому импульсу с выхода блока 7 синхронизации информация с регистра 22.1 блока 1.1 через мультиплексор 4 будет записана в регистр 10.

0 Передаваемое сообщение состоит из двух частей - адресной и операционной. Адресная часть определяет местоположение модуля-получателя информации по горизонтали (в строке) и вертикали (в столбце).

5 Поэтому при Несовпадении адресов по горизонтали и вертикали с кодом - идентификатором модуля, считываемым из регистра 2, на элементах сравнения 11 и 12, дешифратором 9. определяется направление дальнейшего продвижения сообщения через демультиплексор и соответствующий блок

элементов ИЛИ 15.1(1 1.4) на выход модуля к другим аналогичным модулям матричного коммутатора.

Очередной тактовый импульс с выхода блока 7 синхронизации поступает на вход синхронизации блока 1.1. Этот сигнал через элемент И 28 и элементы ИЛИ 26.1-26.К поступает на входы записи (чтение регистров 22.1-22.К. в результате чего происходит сдвиг информации). Так как регистр 22.2 -был в нулевом состоянии, то в регистр 22.1 будет записана нулевая информация/На выходе элемента НЕ 30 будет сигнал логического О. Если очередь сообщений в блоках 1.2-1.5 пуста, то на выходе элемента ИЛИ 35 (фиг. 3) будет сигнал логического О. Этот сигнал поступает на инверсный вход элемента И 16 и разрешает тем самым по оче- : редному тактовому импульсу с выхода блока 1 7 синхронизации обнуление триггера 13 запуска, v - - ;

Выбор направления передачи информации в матричном коммутаторе происходит следующим образом. Адресная часть сообщения сравнивается с адресом (идентификатором) модуля по номерам строки и столбца и определяется одно из пяти возможных направлений передачи по следую- ще му правилу.. . .:. . . ,;,

Пусть А и В - коды адресов модуля соответственно по горизонтали и вертикали в матричном коммутаторе, а С и D - коды адресов приемника информации. Процедура выбора направления передачи информации определяется таблицей.

Процедура выбора направления продвижения информации реализуется дешифратором 9.

Процедура опроса блоков 1.1-1.5 организации очереди сообщений основана на

приоритетном обслуживании блоков, имеющих максимальную глубину очереди сообщений, При равенстве очередей осуществляется последовательный их опрос, начиная с блока 1.1, что реализуется блоком 3 анализа очереди сообщений.

Сравнение кодов длин (глубины) очередной осуществляется элементами сравнения 34.1-34.10 и в зависимости от их

соотношения с выходов узла 36 постоянной памяти выдается код опроса блока 1.1-1.5. Узел 36 постоянной памяти реализуется в виде программируемой логической матрицы (ПЛМ),

При необходимости реализации двойных конвейеров матричным коммутатором (фиг. 5) и выдаче транзитом, минуя модуль сообщения, в противоположном направлении на управляющий вход 19 модуля матричного коммутатора (фиг. 1) подается сигнал логической 1. .

Этот сигнал поступает на S-вход триггера 14 управления и устанавливает его в единичное состояние. На прямом выходе

триггера 14 будет сигнал логической 1, поступающий на управляющие входы первого-четвертого входных демультиплексо- ров 5.1...5.4.

Единичный, сигнал на управляющем входе 1-го (I 1,4) входного демультиплексо- ра 5.I обусловливает поступление сообще- ния с соответствующего входа 18.1 на второй выход входного демультиплексора 5.1 и через соответствующий блок элементов ИЛИ 15.1 поступает на противоположный выход 21.1 модуля к соседнему модулю откуда поступило сообщение. Далее модуль функционирует аналогично описанному.

. .

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1999 |

|

RU2168204C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1508228A1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2110831C1 |

| МОДУЛЬ ДЛЯ ПЕРЕДАЧИ И ВЕЩАНИЯ СООБЩЕНИЙ В МАТРИЧНОМ КОММУТАТОРЕ | 2003 |

|

RU2249848C2 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ, ПРЕДНАЗНАЧЕННЫЙ ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ, ОБМЕНА СООБЩЕНИЯМИ И ОРГАНИЗАЦИИ ВЕЩАТЕЛЬНЫХ РЕЖИМОВ ОБМЕНА СООБЩЕНИЯМИ | 2000 |

|

RU2178584C1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| МОДУЛЬ КОММУТАЦИОННОЙ СЕТИ | 2009 |

|

RU2413971C2 |

Изобретение относится к вычислительной технике и может быть применено при построении соедста коммутации мультипроцессорных систем. Целью изобретения является расширение функциональных возможностей за счет изменения направления передачи на противоположное. В модуль введены четыре входные демультиплексоры, четыре блока элементов ИЛИ и триггеры управления. 5 ил. 1 табл.

Ф о р м у л а и з о б р е т е н и л Модуль матричного коммутатора по авт. св. N 1575167, от л и чаю щи и с я тем, что, с целью расширения функциональных возможностей за счет возможности изменения направления передачи сообщений на противоположное, модуль дополнительно содержит с первого по четвертый входные демультиплексоры,с первого по четвертый блоки элементов ИЛИ и триггер управления, причем установочный вход триггера управления является входом установки модуля, а вход сброса триггера является входом уста- новки в начальное состояние, прямой выход триггера управления соединен с управляющими входами первого-четвертого входных демультиплексоров, первая группа выходов которых соединена соответственно с информационными входами второго-пятого блоков организации очереди сообщений, вторая группа выходов первого-четвертого входных демультиплексоров соединена соответственно с первыми входами первого- четвертого блоков элементов ИЛИ, выходы которых образуют второй информационный выход модуля, вторые входы первого-четвертого блоков элементов ИЛИ соединены соответственно с выходами выходного демультиплексора.

Фиг.1

«

v«

m

т

ШТЙ

01

6

f

9Ct7C6iL

Фиг. 3

фиг.4

фиг. 5

ПРИ НОРМАЛЬНОМ ФУНКЦИОНИРОВАНИИ

(ЩИРОКО&ЕШ ТЕЛЬНЫИ ОБМЕН СООБЩЕН И Я МИ)

| Модуль матричного коммутатора | 1988 |

|

SU1575167A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-07—Публикация

1990-10-30—Подача