Изобретение относится к вычислительной технике и может быть использовано при построении средств коммутации мультипроцессорных систем, абонентских систем связи с децентрализованным управлением, микроконтроллерных сетей, а также коммутационных средств информационно-измерительных систем.

Известна ячейка матричного коммутатора, содержащая схему сравнения, триггер, элемент И, шинный формирователь (а.с. 1290291 СССР, G 06 F 7/00, опубл. 15.02.87, БИ N 6).

Недостатком известной ячейки является невозможность построения коммутаторов с транзитной передачей информации, а следовательно, узкая область ее применения.

Наиболее близким к предлагаемому устройству по технической сущности является модуль матричного коммутатора, содержащий с первого по пятый блоки организации очереди сообщений, блок анализа очереди сообщений, мультиплексор, регистр идентификатора модуля, с первого по четвертый входные демультиплексоры, регистр, триггер управления, триггер запуска, демультиплексор, два дешифратора, блок синхронизации, две схемы сравнения, элемент И, с первого по четвертый блоки элементов ИЛИ (а.с. 1793436 СССР, G 06 F 7/00, 15/16, опубл.07.02.93, БИ N 5).

Недостатком данного модуля является ограничения область его применения, обусловленная невозможностью динамичного изменения маршрутов передачи сообщений в формируемых на его основе коммутаторах.

Технической задачей изобретения является расширение области применения устройства путем включения средств, позволяющих осуществлять динамическое изменение маршрутов передачи сообщений в матричных коммутаторах.

Техническая задача решается тем, что в модуль матричного коммутатора, содержащий с первого по пятый блоки организации очереди сообщений, мультиплексор, блок анализа очереди сообщений, блок синхронизации, демультиплексор, триггер запуска, первый и второй дешифраторы, регистр, элемент И, сигнальный триггер, причем первый выход первого блока организации очереди сообщений соединен с первым информационным входом мультиплексора, выход которого соединен с информационным входом регистра, выходы которого с первого по четвертый соединены с информационным входом демультиплексора, первый выход которого соединен с первым информационным выходом модуля, первый информационный вход модуля соединен с информационным входом первого блока организации очереди сообщений, вторые выходы блоков организации очереди сообщений с первого по пятый соединены с входом блока анализа очереди сообщений, первый выход которого соединен с управляющим входом мультиплексора и входом первого дешифратора, второй выход блока анализа очереди сообщений соединен с входом установки триггера запуска и инверсным входом элемента И, выход которого соединен с входом сброса триггера запуска, выходы первого дешифратора с первого по пятый соединены с управляющими входами блоков организации очереди сообщений с первого по пятый соответственно, прямой выход триггера запуска соединен с входом блока синхронизации, третий выход которого соединен с тактовыми входами блоков организации очереди сообщений с первого по пятый и входом синхронизации регистра, четвертый выход блока синхронизации соединен с информационным входом демультиплексора и прямым входом элемента И, второй выход второго дешифратора соединен с управляющим входом демультиплексора, вход отказа модуля соединен с входом установки сигнального триггера, дополнительно введены с первого по четвертый счетчики, первый и второй мультиплексоры отказа, первый и второй элементы ИЛИ-НЕ, причем первые выходы блоков организации очереди сообщений со второго по пятый соединены с информационными входами счетчиков с первого по четвертый соответственно и информационными входами мультиплексора со второго по пятый соответственно, выходы счетчиков с первого по четвертый соединены с информационными входами мультиплексора со второго по пятый соответственно, первый выход блока синхронизации соединен с входами синхронизации счетчиков с первого по четвертый, второй выход блока синхронизации соединен с входами декремента счетчиков с первого по четвертый, информационные входы модуля со второго по пятый соединены с информационными входами блоков организации очереди сообщений со второго по пятый соответственно, первый и второй сигнальные входы модуля соединены с первым и вторым информационными входами первого мультиплексора отказа соответственно, выход которого соединен со вторым входом второго дешифратора, третий и четвертый сигнальные входы модуля соединены с первым и вторым информационными входами второго мультиплексора отказа соответственно, выход которого соединен с третьим входом второго дешифратора, второй выход регистра соединен с управляющими входами первого и второго мультиплексоров отказа и с пятым входом второго дешифратора, третий выход регистра соединен с входом первого элемента ИЛИ-НЕ, выход которого соединен с первым входом второго дешифратора, четвертый выход регистра соединен с входом второго элемента ИЛИ-НЕ, выход которого соединен с четвертым входом второго дешифратора, первый выход которого соединен с выходом фатальной ситуации модуля, со второго по пятый выходы демультиплексора соединены с информационными выходами модуля со второго по пятый соответственно, прямой выход сигнального триггера соединен с сигнальными выходами модуля с первого по четвертый.

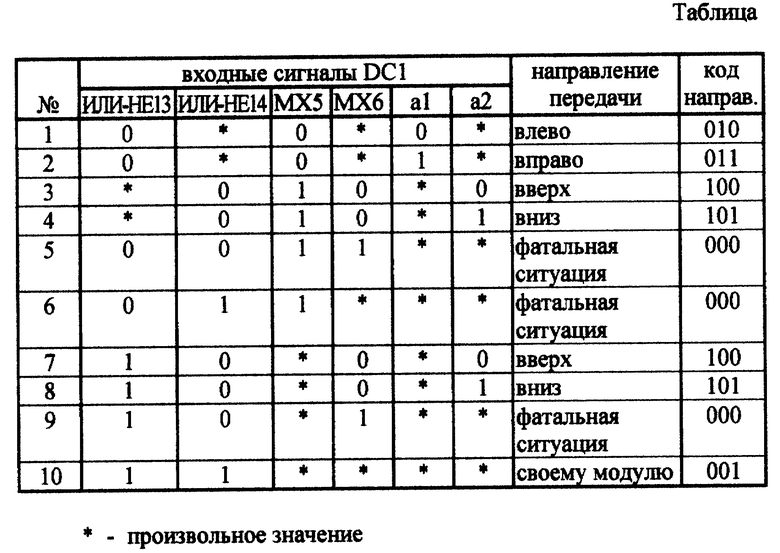

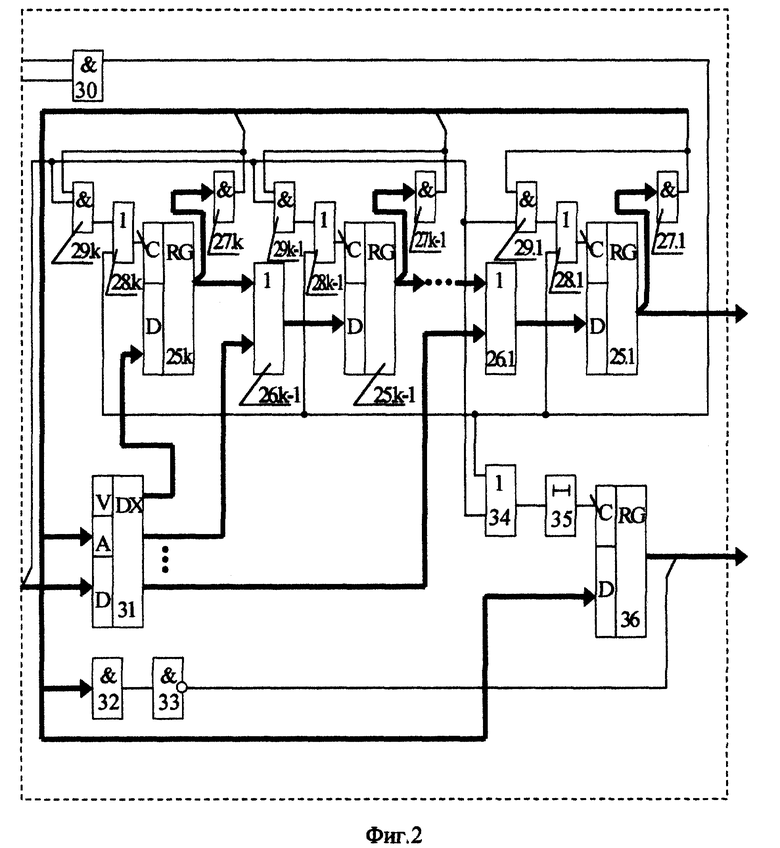

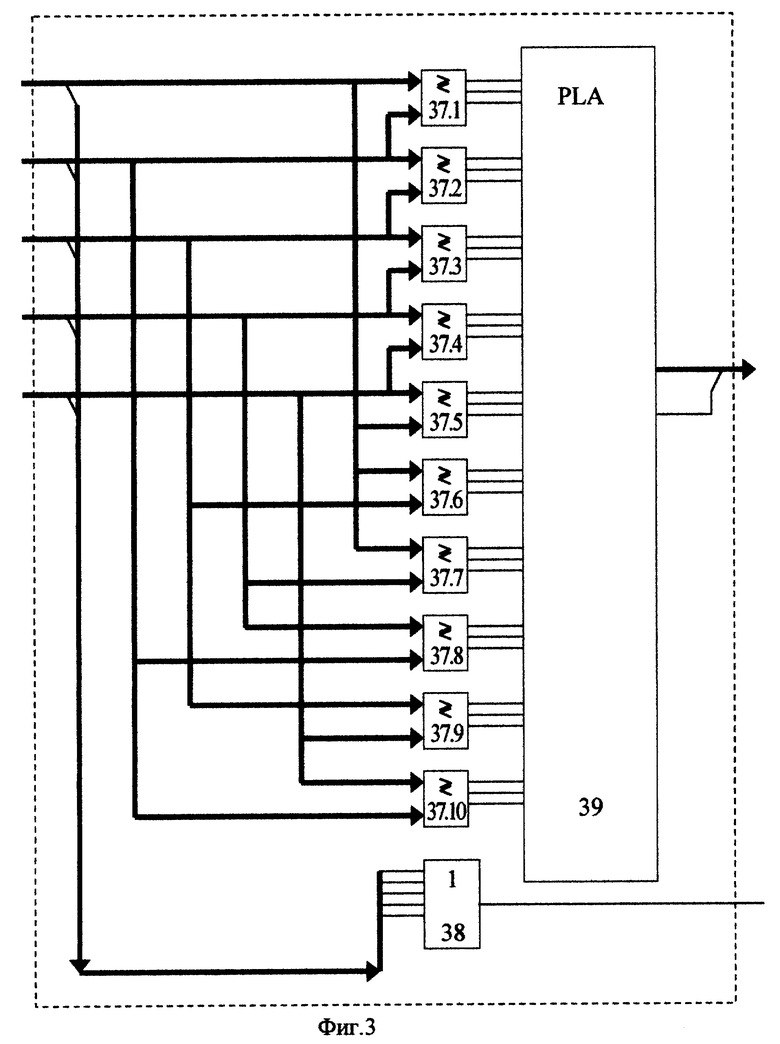

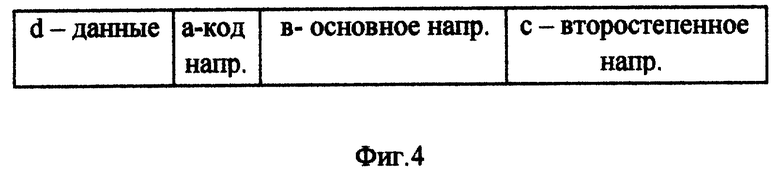

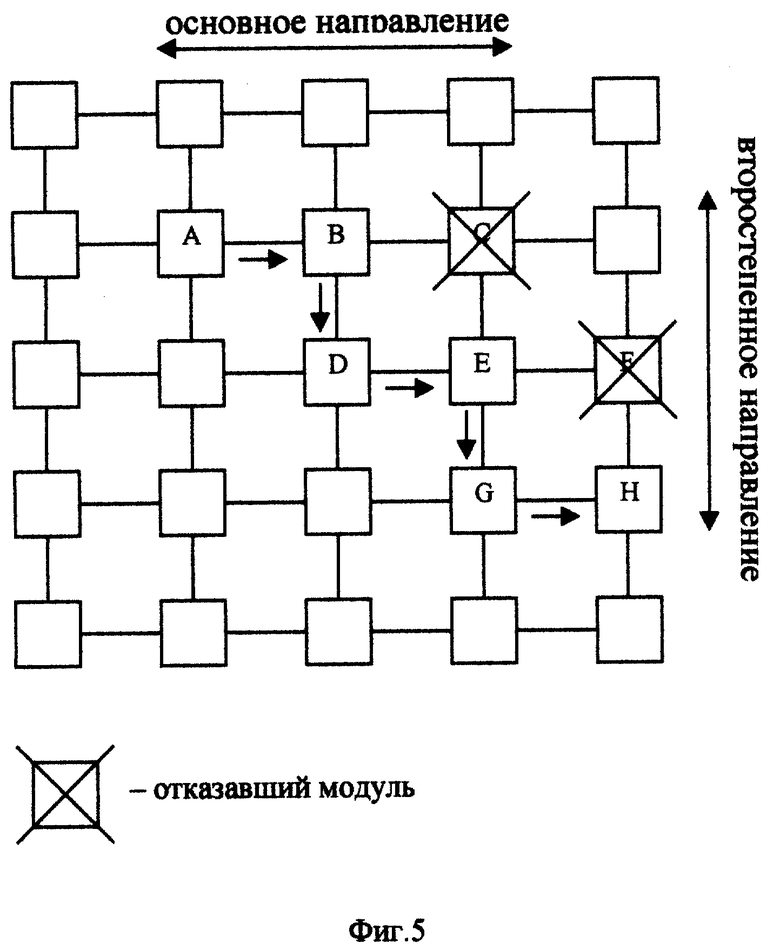

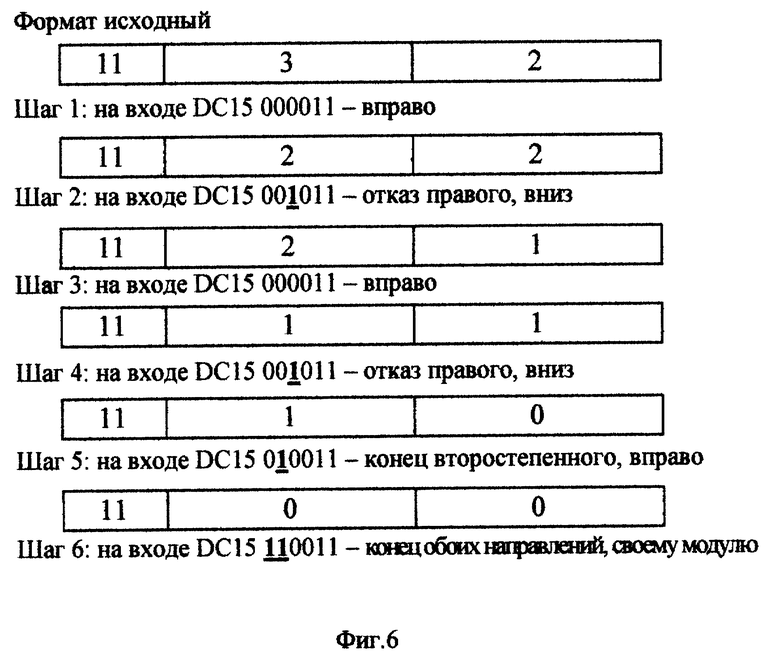

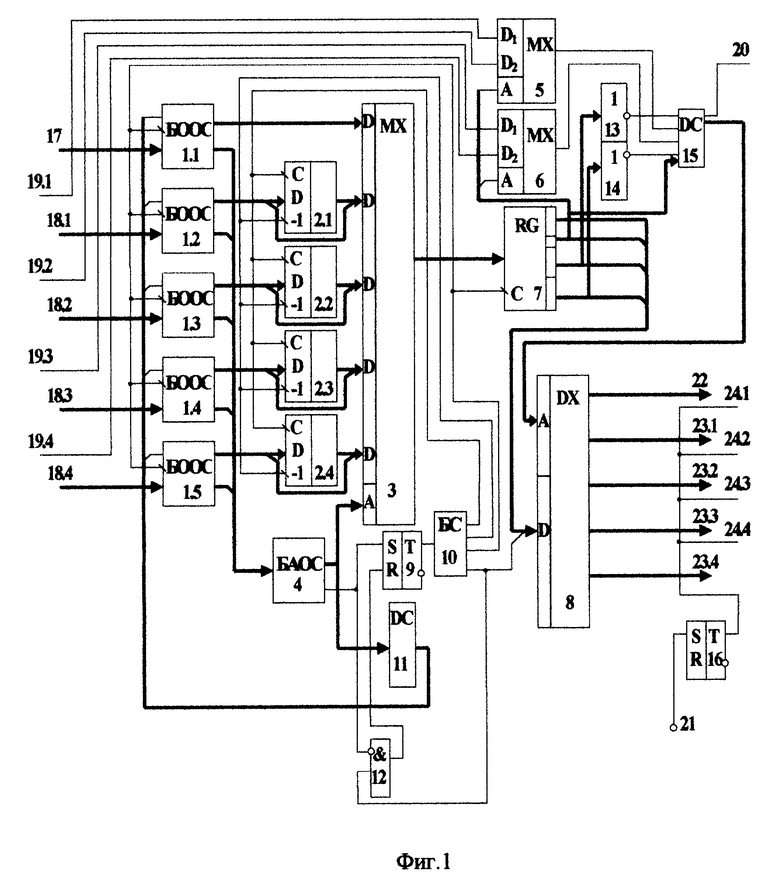

Сущность изобретения поясняется чертежами, где на фиг. 1 представлена функциональная схема модуля матричного коммутатора; на фиг. 2 показана функциональная схема i-го (i=1...5) блока организации очереди сообщений (БООС); на фиг. 3 приведена функциональная схема блока анализа очереди сообщений (БАОС); на фиг. 4 изображен формат сообщения; на фиг. 3 дана структурная схема матричного коммутатора, рассматриваемого в качестве примера; на фиг. 6 изображена динамика изменения адресной части сообщения при его передаче требуемому модулю.

Модуль матричного коммутатора (фиг. 1) содержит блоки 1.1-1.5 организации очереди сообщений, мультиплексор 3, блок 4 анализа очереди сообщений, блок 10 синхронизации, демультиплексор 8, триггер 9 запуска, первый дешифратор 11, второй дешифратор 15, регистр 7, элемент И 12, сигнальный триггер 16, причем первый выход блока 1.1 организации очереди сообщений соединен с первым информационным входом мультиплексора 3, выход которого соединен с информационным входом регистра 7, выходы которого с первого по четвертый соединены с информационным входом демультиплексора 8, первый выход которого соединен с информационным выходом 22 модуля, информационный вход 17 модуля соединен с информационным входом блока 1.1 организации очереди сообщений, вторые выходы блоков 1.1-1.5 организации очереди сообщений соединены с входом блока 4 анализа очереди сообщений, первый выход которого соединен с управляющим входом мультиплексора 3 и входом дешифратора 11, второй выход блока 4 анализа очереди сообщений соединен с входом установки триггера 9 запуска и инверсным входом элемента И 12, выход элемента И 12 соединен с входом сброса триггера 9 запуска, выходы дешифратора 11 с первого по пятый соединены с управляющими входами блоков 1.1-1.5 организации очереди сообщений соответственно, прямой выход триггера 9 запуска соединен с входом блока 10 синхронизации, третий выход которого соединен с тактовыми входами блоков 1.1-1.5 организации очереди сообщений и входом синхронизации регистра 7, четвертый выход блока 10 синхронизации соединен с информационным входом демультиплексора 8 и прямым входом элемента И 12, второй выход дешифратора 15 соединен с управляющим входом демультиплексора 8, вход 21 отказа модуля соединен с входом установки сигнального триггера 16, а также дополнительно введенные счетчики 2.1-2.4, первый мультиплексор 5 отказа, второй мультиплексор 6 отказа, первый элемент ИЛИ-НЕ 13, второй элемент ИЛИ-НЕ 14, причем первые выходы блоков 1.2-1.5 организации очереди сообщений соединены с информационными входами счетчиков 2.1-2.4 соответственно и информационными входами мультиплексора 3 со второго по пятый соответственно, выходы счетчиков 2.1-2.4 соединены с информационными входами мультиплексора 3 со второго по пятый соответственно, первый выход блока 10 синхронизации соединен с входами синхронизации счетчиков 2.1-2.4, второй выход блока синхронизации соединен с входами декремента счетчиков 2.1-2.4, информационные входы 18.1-18.4 модуля соединены с информационными входами блоков 1.2-1.5 организации очереди сообщений соответственно, сигнальные входы 19.1 и 19.2 модуля соединены с первым и вторым информационными входами мультиплексора 5 отказа соответственно, выход которого соединен со вторым входом дешифратора 15, сигнальные входы 19.3 и 19.4 модуля соединены с первым и вторым информационными входами мультиплексора 6 отказа соответственно, выход которого соединен с третьим входом дешифратора 15, второй выход регистра 7 соединен с управляющими входами мультиплексоров 5 и 6 отказа и с пятым входом дешифратора 15, третий выход регистра 7 соединен с входом элемента ИЛИ-НЕ 13, выход которого соединен с первым входом дешифратора 15, четвертый выход регистра 7 соединен с входом элемента ИЛИ-НЕ 14, выход которого соединен с четвертым входом дешифратора 15, первый выход которого соединен с выходом 20 фатальной ситуации модуля, со второго по пятый выходы демультиплексора 8 соединены с информационными выходами 23.1-23.4 модуля соответственно, прямой выход сигнального триггера 16 соединен с сигнальными выходами 24.1-24.4 модуля.

Блок 1.i организации очереди сообщений, где i = 1...5, (фиг. 2) включает регистры 25.1 -25. k, где k - длина очереди сообщений, группу блоков элементов ИЛИ 26.1-26. k-1, группу элементов И 27.1- 27.k, группу элементов И 29.1- 29. k, группу элементов ИЛИ 28.1-28.k, демультиплексор 31, элемент И 30, элемент И 32, элемент НЕ 33, элемент ИЛИ 34, элемент задержки 35, регистр длины очереди 36, причем управляющий вход блока соединен с первым входом элемента И 30, выход которого соединен со вторыми входами элементов ИЛИ 28.1-28.k и с первым входом элемента ИЛИ 34, тактовый вход блока соединен со вторым входом элемента И 30, информационный вход блока соединен с информационным входом демультиплексора 31, входами элементов И 29.1-29-k и вторым входом элемента ИЛИ 34, выходы элементов И 29.1-29-k соединены с первыми входами элементов ИЛИ 28.1-28-k соответственно, выходы элементов ИЛИ 28.1-28. k соединены с входами синхронизации регистров 25.1-25.k соответственно, прямые выходы регистров 25.2-25-k соединены с первыми входами блоков элементов ИЛИ 26.1-26. k-1 соответственно, инверсные выходы регистров 25.1-25.k соединены с входами элементов И 27.1-27.k соответственно, прямой выход регистра 25.1 соединен с первым выходом блока, выходы элементов И 27.1-27.k соединены с первыми входами элементов И 29.1-29.k соответственно, управляющим входом демультиплексора 31, входом элемента И 32 и информационным входом регистра 36 длины очереди, первый выход демультиплексора 31 соединен с информационным входом регистра 25. k, выходы со k-го по второй демультиплексора 31 соединены со вторыми входами блоков элементов ИЛИ 26.1-26.k-1 соответственно, выходы блоков элементов ИЛИ 26.1-26.k-1 соединены с информационными входами регистров 25.1-25.k-1 соответственно, выход элемента И 32 соединен с входом элемента НЕ 33, выход которого соединен со вторым выходом блока, выход элемента ИЛИ 34 соединен с входом элемента задержки 35, выход которого соединен с входом синхронизации регистра 36 длины очереди, выход которого соединен со вторым выходом блока.

Блок 4 анализа очереди сообщений (фиг. 3) включает элементы сравнения 37.1-37.10, элемент ИЛИ 38, узел 39 постоянной памяти, причем вход блока соединен с входами элементов сравнения 37.1-37.10 и входами элемента ИЛИ 38, выходы элементов сравнения 37.1-37.10 соединены с входами узла 39 постоянной памяти, выход которого соединен с первым выходом блока, выход элемента ИЛИ 38 соединен со вторым выходом блока.

Назначение элементов модуля матричного коммутатора (фиг. 1) состоит в следующем.

Блоки 1.1-1.5 организации очереди сообщений предназначены для организации очередей сообщений, поступающих от четырех аналогичных модулей и собственного устройства, например, процессорного модуля в мультипроцессорной системе матричного типа.

Счетчики 2.1-2.4 используются для декремента соответствующих полей адресной части сообщения.

Мультиплексор 3 предназначен для передачи сообщения в регистр 7 с блока 1. i (i=1...5) организации очереди сообщений по управляющему коду с блока 4 анализа очереди сообщений.

Блок 4 анализа очереди сообщений служит для анализа загруженности блоков 1.1-1.5 организации очереди сообщений и организации их опроса в зависимости от длины очереди поступивших сообщений.

Мультиплексор 5 отказа используется для передачи информации об отказе левого или правого соседних модулей на дешифратор 15 по управляющему сигналу с регистра 7.

Мультиплексор 6 отказа используется для передачи информации об отказе верхнего или нижнего соседних модулей на дешифратор 15 по управляющему сигналу с регистра 7.

Регистр 7 предназначен для временного хранения сообщения и выдачи информации, служащей для определения направления дальнейшей передачи сообщения.

Демультиплексор 8 служит для коммутации сообщения в одно из пяти направлений к соседним модулям и собственному устройству (процессорному элементу или иному операционному устройству).

Триггер 9 запуска служит для управления включением и выключением блока 10 синхронизации.

Блок 10 синхронизации (БС) используется для синхронизации работы модуля.

Дешифратор 11 предназначен для выбора блока организации очереди сообщений, из которого осуществляется считывание сообщения.

Элемент И 12 служит для блокировки передачи сигнала на вход сброса триггера 9 запуска.

Элемент ИЛИ-НЕ 13 служит для сравнения с нулем содержимого поля основного направления адресной части сообщения.

Элемент ИЛИ-НЕ 14 служит для сравнения с нулем содержимого поля второстепенного направления адресной части сообщения.

Дешифратор 15 предназначен для определения направления дальнейшей передачи сообщения или фатальной ситуации.

Сигнальный триггер 16 служит для передачи соседним модулям информации об отказе модуля: с выхода 24.1 соседу слева, с выхода 24.2 соседу справа, с выхода 24.3 соседу сверху, с выхода 24.4 соседу снизу.

Общие функциональные особенности предлагаемого изобретения заключаются в следующем. Матричный коммутатор состоит из множества однотипных модулей, осуществляющих передачу сообщений в четырех направлениях: влево, вправо, вверх, вниз. Такая организация обмена сообщениями позволяет задать маршрут передачи сообщения от модуля к модулю двухразрядным кодом направления ("а" = 00 - влево-вверх, 01 - влево-вниз, 10 - вправо-вверх, 11 - вправо-вниз) и количеством шагов в этих направлениях ("b" и "c"). Направление влево-вправо - основное, вверх-вниз - второстепенное. Передаваемое сообщение состоит из 2-х частей: адресной и информационной. Адресная часть состоит из 3-х полей (фиг. 4): "а", "b" и "c", которые задают соответственно код направления, число шагов в основном направлении, число шагов во второстепенном направлении.

Сообщение передается сначала в основном, а затем во второстепенном направлении. После очередного шага передачи в основном направлении происходит декремент поля "b", во второстепенном - декремент поля "с". Если в связи с отказом следующего модуля передача в основном направлении невозможна, то сообщение передается во второстепенном направлении на один шаг, а затем возобновляется передача в основном направлении. Таким образом, осуществляется динамическое изменение маршрутов передачи сообщений.

Определение принадлежности сообщения некоторому модулю происходит путем анализа поступившей информации на основе сравнения значений полей "b" и "с" сообщения с нулем. При совпадении с нулем обоих полей, сообщение считается доставленным по назначению и передается собственному устройству.

Рассмотрим работу предлагаемого модуля более детально.

Первоначально все элементы памяти модуля (триггеры, регистры и счетчики) находятся в состоянии логического нуля.

Работа модуля начинается с поступления сообщения на вход 17 (фиг. 1). Сообщение заносится в блок организации очереди сообщений 1.1. Так как регистры 25.1-25.k БООС 1.1 (фиг. 2) находятся в нулевом состоянии, то на выходах элементов И 27.1-27.k присутствуют сигналы логической единицы. Эти сигналы поступают на управляющий вход демультиплексора 31 и определяют запись сообщения, поступающего на информационный вход демультиплексора 31, в регистр 25.1 через элемент ИЛИ 26.1. После записи сообщения состояние регистра 25.1 становится отлично от нулевого и на выходах элементов И 27.1-27.k формируется код 11. . .10, который заносится в регистр длины очереди 36 по импульсу, поступающему одновременно с сообщением на вход синхронизации регистра 36 длины очереди через элемент ИЛИ 34 и элемент 35 задержки. Тот же код поступает на элемент И 32, в результате чего на вход элемента НЕ 33 поступает логический нуль, а на выходе элемента НЕ 33 появляется сигнал логической единицы, индицирующий наличие информации в блоке 1.1. Этот сигнал одновременно с кодом длины очереди с выхода регистра 36 поступает с выхода блока 1.1 на вход блока 4 анализа очереди сообщений (фиг. 1).

На выходе элемента ИЛИ 38 (фиг. 3) формируется сигнал логической единицы, который со второго выхода БАОС 4 (фиг. 1) поступает на вход установки триггера 9 запуска и устанавливает его в единичное состояние. Сигнал логической единицы с триггера 9 запуска включает блок 10 синхронизации.

Дальнейшую работу модуля рассмотрим при случае, когда коммутатор какое-то время уже работает и некоторые БООС не пусты. Пусть самая большая очередь сообщений будет в БООС 1.3. Тактовый импульс с первого выхода блока 10 синхронизации поступает на вход синхронизации счетчиков 2.1-2.4. По этому импульсу поле "b" сообщения с блока 1.3 записывается через информационный вход на счетчик 2.2 (с блоков 1.2 и 1.3 на счетчики 2.1 и 2.2 соответственно поступает поле "b", с блоков 1.4 и 1.5 на счетчики 2.3 и 2.4 соответственно поступает поле "с"). По тактовому импульсу со второго выхода БС 10, поступающему на вход декремента счетчиков 2.1-2.4, значение этого поля уменьшается на единицу.

Одновременно происходит выделение БООС с наибольшей очередью. Так как очередь сообщений в блоке 1.3 наибольшая, то на выходе элементов сравнения 37.2, 37.3, 37.6, 37.9 (фиг. 3) формируется сигнал "больше". Этот сигнал поступает на вход узла постоянной памяти 39 и образует на его выходе код опроса блока 1.3 (фиг. 1). Этот код поступает на управляющий вход мультиплексора 3 и коммутирует его выход с третьим информационным входом. По тактовому импульсу с третьего выхода блока 10 синхронизации сообщение с регистра 25.1 (фиг. 2) блока 1.3 (фиг. 1) вместе с уменьшенным на единицу полем "b" из счетчика 2.2 через мультиплексор 3 заносится в регистр 7.

Тактовый импульс с третьего выхода блока 10 поступает и на тактовый вход блока 1.3, обеспечивая сдвиг очереди сообщений в данном блоке. Этот импульс через элемент И 30 (фиг. 2) и элементы ИЛИ 28.1-28.k поступает на входы синхронизации регистров 25.1- 25.k, и обеспечивает сдвиг информации. В результате в регистр 25.1 переписывается сообщение, ранее находившееся в регистре 25.2. На этом процесс считывания очередного сообщения из БООС 1.3 завершается.

Рассмотрим процесс определения направления выдачи сообщения и выдачу сообщения в выбранном направлении.

Первый разряд поля "а" сообщения (фиг. 4) со второго выхода регистра 7 поступает на управляющий вход мультиплексора отказа 5, на вход D1 которого с левого соседнего модуля через сигнальный вход 19.1 модуля поступает логический ноль, если левый соседний модуль функционирует, или единица, если нет, а на вход D2 с правого соседнего модуля через сигнальный вход 19.2 модуля поступает логический ноль, если правый соседний модуль функционирует, или единица, если нет. Второй разряд поля "а" со второго выхода регистра 7 поступает на управляющий вход мультиплексора отказа 6, на вход D1 которого с верхнего соседнего модуля через сигнальный вход 19.3 модуля поступает логический ноль, если верхний соседний модуль функционирует, или единица, если нет, а на вход 02 с нижнего соседнего модуля через сигнальный вход 19.4 модуля поступает логический ноль, если нижний соседний модуль функционирует, или единица, если нет. Если поступившее на управляющий вход мультиплексора отказа 5 или 6 значение равно нулю, то с выхода этого мультиплексора на дешифратор 15 поступит значение с входа D1, а если поступившее на управляющий вход мультиплексора 5 или 6 отказа значение равно единице, то с выхода мультиплексора на дешифратор 15 поступит значение с входа 02. Значение поля "а" со второго выхода регистра 7 поступает, кроме того, на дешифратор 15.

Содержимое поля "b" сообщения (фиг. 4) с третьего выхода регистра 7 подается на элемент ИЛИ-НЕ 13. Содержимое поля "с" сообщения (фиг. 4) с четвертого выхода регистра 7 подается на элемент ИЛИ-НЕ 14. Если значение, поступившее на элемент ИЛИ-НЕ 13 или 14 равно нулю, то с выхода этого элемента на дешифратор 15 поступит логическая единица, при любом другом поступившем значении с выхода этого элемента на дешифратор 15 поступит нуль.

Поступившие на дешифратор 15 значения в соответствии с Таблицей определят дальнейшее направление передачи сообщения. Если имеет место фатальная ситуация, то с первого выхода дешифратора 15 на выход 20 фатальной ситуации модуля поступает единичный сигнал, индицирующий о невозможности передачи сообщения. Если фатальной ситуации нет, тогда в соответствии с Таблицей с дешифратора 15 на управляющий вход демультиплексора 8 поступает код направления передачи сообщения. По тактовому импульсу с четвертого выхода БС 10 сообщение с регистра 7 поступает на информационный вход демультиплексора 8 и с выхода этого демультиплексора через информационные выходы 23.1-23.4 модуля сообщение передается дальше (со второго выхода демультиплексора 8 через выход 23.1 модуля соседу слева, с третьего выхода демультиплексора 8 через выход 23.2 модуля соседу справа, с четвертого выхода демультиплексора 8 через выход 23.3 модуля соседу сверху, с пятого выхода демультиплексора 8 через выход 23.4 модуля соседу снизу). На этом процесс обработки сообщения текущим модулем завершается.

Завершение передачи сообщения происходит, когда поля "b" и "с" сообщения (фиг. 4) равны нулю. Тогда в соответствии с Таблицей с дешифратора 15 на управляющий вход демультиплексора 8 поступает код направления передачи сообщения, определяющий передачу собственному устройству. По тактовому импульсу с четвертого выхода БС 10 сообщение с регистра 7 поступает на информационный вход демультиплексора 8 и с выхода этого демультиплексора через информационный выход 22 модуля сообщение передается собственному устройству.

Останов модуля происходит следующим образом. Когда сообщение прошло через модуль и тот БООС, на который это сообщение поступало, пуст, то в регистрах 25.1 -25. k (фиг. 2) этого БООС находится нулевая информация. На выходе элемента НЕ 33 будет сигнал логического нуля. Если очередь сообщений в остальных БООС пуста, то на выходе элемента ИЛИ 38 (фиг. 3) тоже будет сигнал логического нуля. Этот сигнал со второго выхода БАОС 4 (фиг. 1) поступает на инверсный вход элемента И 12. Тактовый импульс с четвертого выхода блока 10 через элемент И 12 поступает на вход сброса триггера 9 запуска и обеспечивает его обнуление. Это приводит к выключению блока 10 синхронизации.

Как только на информационные входы 17 или 18.1-18.4 поступает очередное сообщение, работа модуля может быть возобновлена (см. выше).

Рассмотрим пример.

Пусть необходимо передать сообщение от модуля А к модулю H (фиг. 5).

Исходное состояние адресной части сообщения (фиг. 4): поле "b" = 11 (вправо-вниз), поле "b" = 3 (три шага в основном направлении), поле "c" = 2 (два шага во второстепенном направлении).

Передача сообщения происходит согласно вышеописанному алгоритму функционирования. Вид адресной части сообщения на каждом шаге представлен на фиг. 6. От A к B, от D к E, от G к H сообщение передается в соответствии со строкой 2 Таблицы. Так как модули C и F отказали, то от B к D и E к G сообщение передается в соответствии со строкой 4 Таблицы. В прототипе передача сообщения от модуля A к модулю H была бы невозможна.

Таким образом, как следует из описания, введение в модуль дополнительных элементов и обусловленных ими связей позволяет значительно расширить область его применения, поскольку дает возможность динамического изменения маршрутов передаваемых сообщений в матричном коммутаторе.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2110831C1 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| МОДУЛЬ КОММУТАЦИОННОЙ СЕТИ | 2000 |

|

RU2175146C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| МОДУЛЬ ДЛЯ ПЕРЕДАЧИ И ВЕЩАНИЯ СООБЩЕНИЙ В МАТРИЧНОМ КОММУТАТОРЕ | 2003 |

|

RU2249848C2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАРШРУТА СООБЩЕНИЯ | 2000 |

|

RU2175144C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2198417C2 |

Изобретение относится к вычислительной технике и может быть использовано при построении средств коммутации мультипроцессорных систем. Техническим результатом является расширение области применения устройства. Устройство содержит с первого по пятый блоки организации очереди сообщений, мультиплексор, блок анализа очереди сообщений, блок синхронизации, демультиплексор, триггер запуска, первый и второй дешифраторы, регистр, элемент И, сигнальный триггер, с первого по четвертый счетчики, первый и второй мультиплексоры отказа, первый и второй элементы ИЛИ-НЕ. 1 табл., 6 ил.

Модуль матричного коммутатора, содержащий с первого по пятый блоки организации очереди сообщений, мультиплексор, блок анализа очереди сообщений, блок синхронизации, демультиплексор, триггер запуска, первый и второй дешифраторы, регистр, элемент И, сигнальный триггер, причем первый выход первого блока организации очереди сообщений соединен с первым информационным входом мультиплексора, выход которого соединен с информационным входом регистра, выходы которого с первого по четвертый соединены с информационным входом демультиплексора, первый выход которого соединен с первым информационным выходом модуля, первый информационный вход модуля соединен с информационным входом первого блока организации очереди сообщений, вторые выходы блоков организации очереди сообщений с первого по пятый соединены с входом блока анализа очереди сообщений, первый выход которого соединен с управляющим входом мультиплексора и входом первого дешифратора, второй выход блока анализа очереди сообщений соединен с входом установки триггера запуска и инверсным входом элемента И, выход которого соединен с входом сброса триггера запуска, выходы первого дешифратора с первого по пятый соединены с управляющими входами блоков организации очереди сообщений с первого по пятый соответственно, прямой выход триггера запуска соединен с входом блока синхронизации, третий выход которого соединен с тактовыми входами блоков организации очереди сообщений с первого по пятый и входом синхронизации регистра, четвертый выход блока синхронизации соединен с информационным входом демультиплексора и прямым входом элемента И, второй выход второго дешифратора соединен с управляющим входом демультиплексора, вход отказа модуля соединен с входом установки сигнального триггера, отличающийся тем, что в него дополнительно введены с первого по четвертый счетчики, первый и второй мультиплексоры отказа, первый и второй элементы ИЛИ-НЕ, причем первые выходы блоков организации очереди сообщений со второго по пятый соединены с информационными входами счетчиков с первого по четвертый соответственно и информационными входами мультиплексора со второго по пятый соответственно, выходы счетчиков с первого по четвертый соединены с информационными входами мультиплексора со второго по пятый соответственно, первый выход блока синхронизации соединен с входами синхронизации счетчиков с первого по четвертый, второй выход блока синхронизации соединен с входами декремента счетчиков с первого по четвертый, информационные входы модуля со второго по пятый соединены с информационными входами блоков организации очереди сообщений со второго по пятый соответственно, первый и второй сигнальные входы модуля соединены с первым и вторым информационными входами первого мультиплексора отказа соответственно, выход которого соединен со вторым входом второго дешифратора, третий и четвертый сигнальные входы модуля соединены с первым и вторым информационными входами второго мультиплексора отказа соответственно, выход которого соединен с третьим входом второго дешифратора, второй выход регистра соединен с управляющими входами первого и второго мультиплексоров отказа и с пятым входом второго дешифратора, третий выход регистра соединен с входом первого элемента ИЛИ-НЕ, выход которого соединен с первым входом второго дешифратора, четвертый выход регистра соединен с входом второго элемента ИЛИ-НЕ, выход которого соединен с четвертым входом второго дешифратора, первый выход которого соединен с выходом фатальной ситуации модуля, со второго по пятый выходы демультиплексора соединены с информационными выходами модуля со второго по пятый соответственно, прямой выход сигнального триггера соединен с сигнальными выходами модуля с первого по четвертый.

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| Ячейка матричного коммутатора | 1985 |

|

SU1290291A1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| КОММУТАЦИОННАЯ СРЕДА | 1993 |

|

RU2092896C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2111532C1 |

| Система коммутации устройств обработки информации | 1989 |

|

SU1798796A1 |

| КОНСТРУКТИВНЫЙ ЭЛЕМЕНТ ВОЗДУШНОГО СУДНА | 2007 |

|

RU2428353C2 |

| US 3835896 A, 23.07.1974. | |||

Авторы

Даты

2001-05-27—Публикация

1999-09-13—Подача