Изобретение относится к вычислительной технике и может быть использовано при построении средств коммутации мультипроцессорных систем, абонентских систем связи с децентрализованным управлением, коммутационных средств параллельного обмена информацией в измерительных системах.

Известна ячейка матричного коммутатора, содержащая с первой по шествую схемы сравнения, первый и второй шифраторы, регистр, с первого по четвертый элементы И, с первого по четвертый шинные формирователи (авт.св. СССР N 1783510, кл. G 06 F 7/00, опублик. 23.12.92).

Недостатком данной ячейки являются ограниченные функциональные возможности.

Наиболее близким к предлагаемому устройству по технической сущности является модуль матричного коммутатора, реализующий возможность полносвязного взаимодействия и содержащий с первого по третий блоки организации очередей сообщений, регистр идентификатора модуля, блок анализа очередей сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, первый и второй элементы сравнения, первый и второй дешифраторы, элемент И (авт.св. СССР N 1575167, кл. G 06 F 7/00, 15/16, опублик. 30.06.90.

Недостатком этого устройства является неустойчивость функционирования в случае одновременного поступления сигналов записи сообщений и сдвига очереди, что возможно ввиду асинхронного протекания процессов в устройствах - приемниках сообщений и устройствах - источниках.

Техническая задача изобретения - повышение устойчивости работы устройства.

Техническая задача решается тем, что в модуль матричного коммутатора, содержащий с первого по третий блоки организации очередей сообщений (БООС), регистр идентификатора модуля, блок анализа очередей сообщений (БАОС), мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, первую и вторую схемы сравнения, первый и второй дешифраторы и элемент И, причем n выходов (где n -разрядность передаваемых сообщений) первой группы БООС с первого по третий подключены к соответствующим группам информационных входов мультиплексора, выходы которого подключены к информационным входам регистра; k+1 выходов (где k - максимальная длина очередей сообщений) второй группы БООС с первого по третий соединены с соответствующими группами входов БАОС, информационные выходы которого подключены к адресным входам мультиплексора и к входам первого дешифратора, выходы которого с первого по третий подключены к входам опроса БООС с первого по третий соответственно; группы n+2 информационных входов БООС с первого по третий подключены соответственно к первой - третьей входным информационным шинам устройства; первая и вторая группы выходов регистра подключены к вторым группам входов первой и второй схем сравнения соответственно, первые группы входов которых соединены соответственно с первой и второй группами выходов регистра идентификатора модуля; выходы первой и второй схем сравнения подключены к входам второго дешифратора, выходы которого соединены с адресными входами демультиплексора, группа n+2 выходов которого с первой по третью подключены к первой - третьей выходным информационным шинам устройства соответственно; управляющий выход БАОС подключен к входу установки S триггера и к первому входу элемента И, выход которого соединен с входом сброса R триггера, прямой выход которого соединен с входом разрешения блока синхронизации, первый выход которого подключен к входу синхронизации регистра, а третий выход - к второму входу элемента И и к первому информационному входу демультиплексора, группа n информационных входов с третьего по (n+2)-й которого соединена с выходами регистра, дополнительно вводятся связь второго выхода блока синхронизации со вторым информационным входом демультиплексора и связь первого выхода блока синхронизации с входами сдвига БООС с первого по третий, а каждый БООС, содержащий группу регистров с первого по k-й, группу блока элементов ИЛИ с первого по (k-1)-й, демультиплексор, первую группу элементов И с первого по k-й, вторую группу элементов И с первого по k-й, группу элементов ИЛИ с первого по k-й, первый и второй элементы И, элемент НЕ, регистр длины очереди и первый элемент ИЛИ, дополнительно включает одновибратор, триггеры запроса, блокировки и управления демультиплексором, третий элемент И и второй элемент ИЛИ, причем выход одновибратора подключен к вторым входам элементов ИЛИ соответствующей группы с первого по k-й, к первому входу первого элемента ИЛИ и к второму входу второго элемента ИЛИ, выход которого соединен со счетным входом триггера запроса, прямой выход которого подключен к первому входу третьего элемента И, выход которого подключен к входу третьего элемента И, выход которого подключен к входу одновибратора; первый вход второго элемента ИЛИ соединен с выходом первого элемента И, первый и второй входы которого являются соответственно входами опроса и сдвига БООС; второй вход третьего элемента И соединен с прямым выходом триггера блокировки, инверсный выход которого подключен к счетному входу триггера управления демультиплексором, прямой выход которого соединен с выходом разрешения демультиплексора, первая группа выходов которого соединена с информационными входами k-го регистра, вторая группа - со второй группой выходов (k-1)-го блока элементов ИЛИ и т. д. , k-я группа выходов соединена со второй группой входов первого блока элементов ИЛИ, а группа n информационных входов подключена к информационным входам с третьего по (n+2)-й БООС; первый информационный вход БООС подключен к счетному входу триггера блокировки, к установочному S входу триггера управления демультиплексором, а также ко вторым входам элементов И первой группы с первого по k-й, выходы которых подключены к первым входам элементов ИЛИ соответствующей группы с первого по k-й соответственно, и ко второму входу первого элемента ИЛИ, выход которого соединен с входом синхронизации регистра длины очереди; второй информационный вход БООС подключен к входу сброса R триггера блокировки; прямые выходы регистров со второго по k-й подключены к первым группам входов блоков элементов ИЛИ с первого по (k-1)-й соответственно, а выходы первого регистра образуют первую группу выходов БООС; инверсные выходы регистров с первого по k-й подключены к входам элементов И второй группы с первого по k-й соответственно, выходы которых подключены к адресным входам демультиплексора, к информационным входам регистра длины очереди, к первым входам элементов И первой группы с первого по k-й соответственно, а также к входам второго элемента И, выход второго соединен с входом элемента НЕ, выход которого в объединении с выходами регистра длины очереди образуют вторую группу k+1 выходов БООС, при этом одновибратор, триггер управления демультиплексором и регистры с первого по k-й срабатывают по переднему фронту сигнала, а триггеры запроса, блокировки и регистр длины очереди - по заднему фронту.

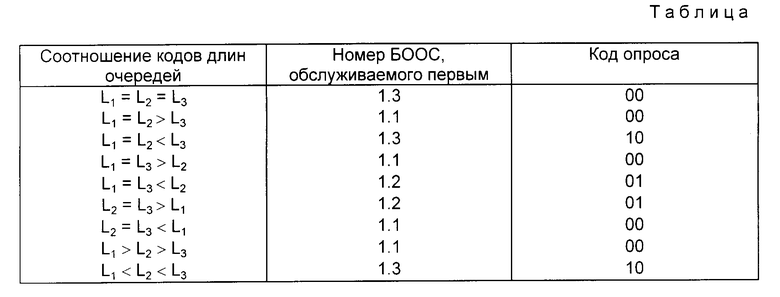

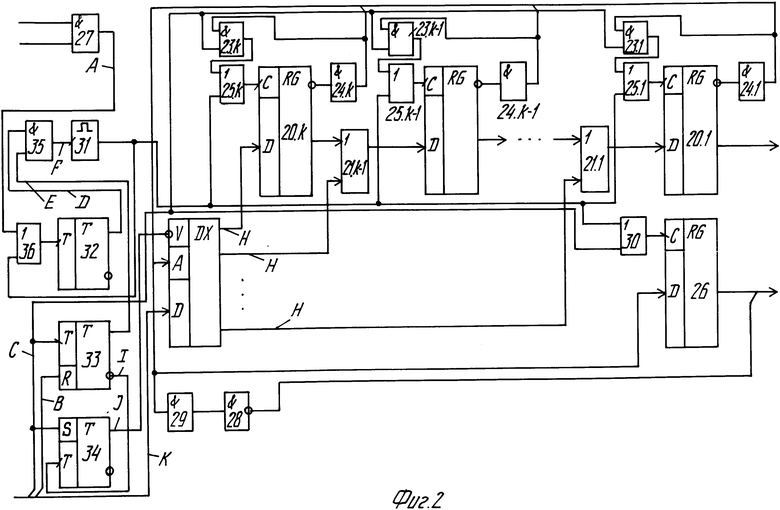

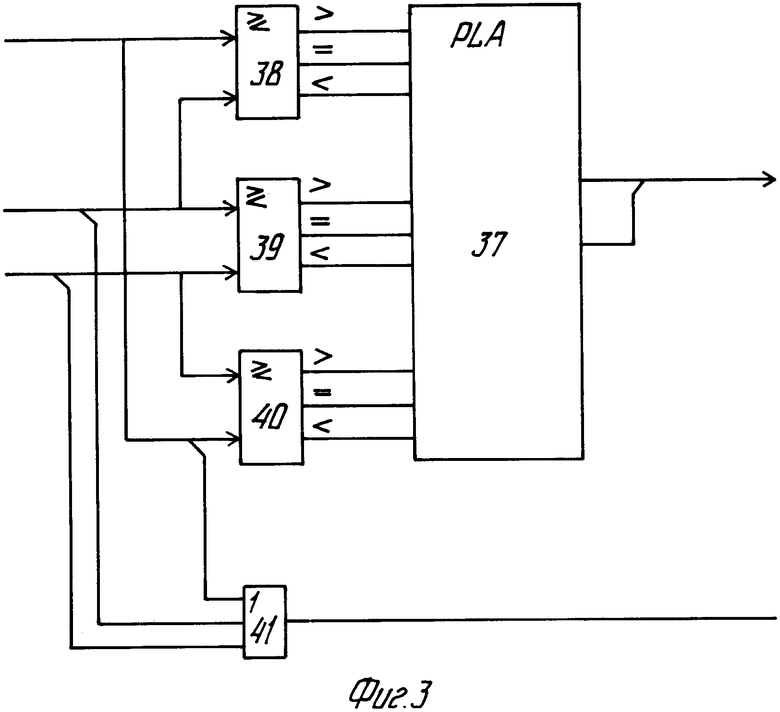

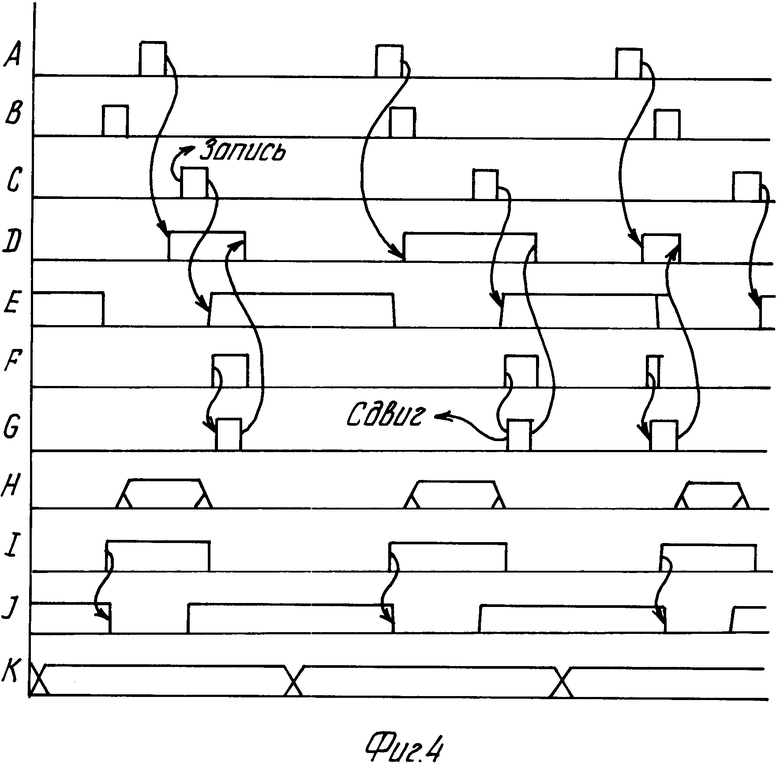

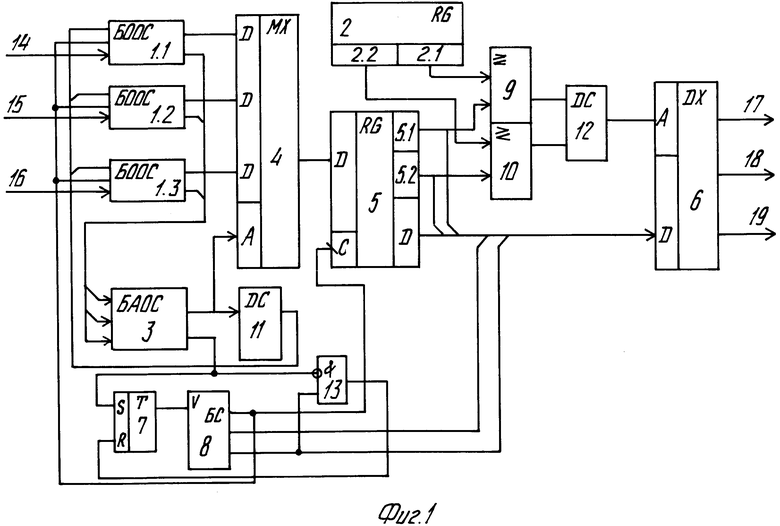

На фиг. 1 изображена схема модуля матричного коммутатора; на фиг. 2 - схема блока организации очередей сообщений; на фиг. 3 - схема блока анализа очередей сообщений; на фиг. 4 - временные диаграммы работы блока организации очередей сообщений при различных соотношениях моментов появления импульсов записи сообщений и сдвига очереди.

Модуль матричного коммутатора (фиг. 1) содержит с первого по третий блоки организации очередей сообщений (БООС) 1.1-1.3, регистр идентификатора модуля 2 (включающий первое 2.1 и второе 2.2 адресные поля), блок анализа очередей сообщений (БАОС) 3, мультиплексор 4, регистр 5 (включающий первое 5.1, второе 5.2 адресные поля и информационное поле), демультиплексор 6, триггер 7, блок 8 синхронизации, первую 9 и вторую 10 схемы сравнения, первый 11 и второй 12 дешифраторы и элементы И 13, причем n выходов первой группы БООС с первого по третий подключены к соответствующим группам информационных входов мультиплексора, выходы которого подключены к информационным входам регистра; k+1 выходов второй группы БООС с первого по третий соединены с соответствующими группами входов БАОС, информационные выходы которого подключены к адресным входам мультиплексора и к входам первого дешифратора, выходы которого с первого по третий подключены к входам опроса БООС с первого по третий соответственно; группы n+2 информационных входов БООС с первого по третий подключены соответственно к первой - третьей 14-16 входным информационным шинам устройства; первая и вторая группы выходов регистра подключены к вторым группам входов первой и второй схем сравнения соответственно, первые группы входов которых соединены соответственно с первой и второй группами выходов регистра идентификатора модуля; выходы первой и второй схем сравнения подключены к входам второго дешифратора, выходы которого соединены с адресными входами демультиплексора, группы n+2 выходов которого с первой по третью подключены к первой - третьей 17-19 выходным информационным шинам устройства соответственно; управляющий выходов БАОС подключен к входу установки S триггера и к первому входу элемента И, выход которого соединен с входом сброса R триггера, прямой выход которого соединен с входом разрешения блока синхронизации, первый выход которого подключен к входу синхронизации регистра, а третий выход - ко второму входу элемента И и к первому информационному входу демультиплексора, группа n информационных входов которого с третьего по (n+2)-й соединена с выходами регистра, второй выход блока синхронизации дополнительно соединен с вторым информационным входом демультиплексора, а первый выход - с входами сдвига БООС с первого по третий.

Блок организации очередей сообщений (БООС) (фиг. 2) предназначен для приема, хранения и выдачи сообщений в порядке их поступления и содержит регистры 20.1-20.k (где k - максимальная длина очереди сообщений), группу блоков элементов ИЛИ 21.1-21. k-1, демультиплексор 22, группу элементов И 23.1-23. k, группу элементов И 24.1-24.k, группу элементов ИЛИ 25.1-25.k, регистр 26 длины очереди, первый элемент И 27, элемент НЕ 28, второй элемент И 29, первый элемент ИЛИ 30, а также дополнительно введенные одновибратор 31, триггеры запроса 32, блокировки 33 и управления демультиплексором 34, третий элемент И 35 и второй элемент ИЛИ 36, причем выход одновибратора подключен к вторым входам элементов ИЛИ 25.1-25.k, к первому входу элемента ИЛИ 30 и к второму входу элемента ИЛИ 36, выход которого соединен со счетным входом триггера запроса, прямой выход которого подключен к первому входу элемента И 35, выход которого подключен к входу одновибратора; первый вход элемента ИЛИ 36 соединен с выходом элемента И 27, первый и второй входы которого являются соответственно входами опроса и сдвига БООС; второй вход элемента И 35 соединен с прямым выходом триггера блокировки, инверсный выход которого подключен к счетному входу триггера управления демультиплексором, прямой выход которого соединен с входом разрешения демультиплексора, первая группа выходов которого соединена с информационными входами регистра 20.k, вторая группа - со второй группой входов блока 21.k-1 элементов ИЛИ и т.д., k-я группа выходов соединена со второй группой входов блока 21.1 элементов ИЛИ, а группа n (где n - разрядность передаваемых сообщений) информационных входов подключена к информационным входам с третьего по (n+2)-й БООС; первый информационный вход БООС подключен к счетному входу триггера блокировки, к установочному S входу триггера управления демультиплексором, а также ко вторым входам элементов И 23.1-23. k, выходы которых подключены к первым входам элементов ИЛИ 25.1-25.k соответственно, и к второму входу элемента ИЛИ 30, выход которого соединен с входом синхронизации регистра 26 длины очереди; второй информационный вход БООС подключен к входу сброса R триггера блокировки; прямые выходы регистров 20.2-20.k подключены к первым группам входов блоков 21.1-21. k-1 элементов ИЛИ соответственно, а выходы регистра 20.1 образуют первую группу выходов БООС; инверсные выходы регистров 20.1-20. k подключены к входам элементов И 24.1-24.k соответственно, выходы которых подключены к адресным входам демультиплексора, к информационным входам регистра длины очереди, к первым входам элементов И 23.1-23.k соответственно, а также к входам элемента И 29, выход которого соединен с входом элемента НЕ, выход которого в объединении с выходами регистра длины очереди образуют вторую группу k+1 выходов БООС, при этом одновибратор, триггер управления демультиплексором и регистры 20.1-20.k срабатывают по переднему фронту сигнала, а триггеры запроса и блокировки и регистр длины очереди - по заднему.

Блок анализа очередей сообщений (БАОС) (фиг. 3) предназначен для определения соотношения длин очередей сообщений в различных БООС и формирования кода БООС, содержащего наибольшее число сообщений, и включает узел постоянной памяти 37, с первой по третью схемы сравнения 38-40 и элемент ИЛИ 41, причем первая и вторая группы входов первой схемы сравнения подключены к k входам первой и второй групп входов БАОС соответственно, первая и вторая группы входов второй схемы сравнения подключены к k входам второй и третьей групп входов БАОС соответственно, первая и вторая группы входов третьей схемы сравнения подключены к k входам третьей и первой групп входов БАОС соответственно; выходы схем сравнения с первой по третью подключены к входам узла постоянной памяти, выходы которого являются информационными выходами БАОС; входы элемента ИЛИ с первого по третий подключены к (k+1)-м входам соответствующих групп входов БАОС, а выход является управляющим выходом БАОС.

Матричный коммутатор состоит из множества однотипных модулей, каждый из которых соединен с двумя другими модулями по входу и с двумя по выходу, и обеспечивает возможность взаимодействия любой пары модулей. Каждому модулю соответствует идентификатор A, B (где A, B - номера строки и столбца коммутатора, содержащих данный модуль, "." - символ конкатенации), определяющий его расположение в пределах коммутационного поля. Взаимодействие модулей осуществляется на основе обмена сообщениями, формат которых включает информационное и адресное поля. Адресное поле сообщения содержит код C, D номера модуля - приемника этого сообщения. Доставка сообщения требуемому модулю реализуется путем его передачи через промежуточные модули, а признаком достижения приемника является совпадение его номера A, B с номером C, D, указанным в адресной части передаваемого сообщения.

Модуль маточного коммутатора работает следующим образом.

В исходном состоянии регистры 20.1-20.k и 26 БООС 1.1-1.3 содержат нулевые коды, триггер запроса 32 БООС 1.1-1.3 находится в нулевом, а триггеры блокировки 33 и управления 34 демультиплексором - в единичном состоянии; триггер 7 и регистр 5 находятся в нулевом состоянии (цепи начальной установки на фиг. 1 и 2 условно не показаны), поэтому блок 8 синхронизации выключен, а на выходах элементов И 24.1-24.k БООС 1.1-1.3 присутствуют сигналы логической единицы, что обуславливает наличие низкого уровня сигнала на выходах элемента НЕ 28 БООС 1.1-1.3. Сигналы логического нуля с выходов последних поступают на (к + 1)-е выходы вторых групп выходов БООС 1.1-1.3 и далее на соответствующие входы элемента ИЛИ 41 БАОС 3, на выходе которого появляется нулевой сигнал.

Очередное сообщение с одной из входных информационных шин устройства (например, с шины 14) поступает на информационные входы соответствующего БООС (1.1). Так как на адресных входах демультиплексора 22 присутствует код 11...1, сообщение с информационных входов БООС поступает на k-ю группу выходов демультиплексора 22, затем через блок элементов ИЛИ 21.1 - на информационные входы регистра 20.1 и записывается в этом регистре по переднему фронту импульса синхронизации, который поступает на входы синхронизации регистров 20.1-20. k через элементы И 23.1-23.k и элементы ИЛИ 25.1-25.k с первого информационного входа БООС. Элементы И 23.1-23.k оказываются открытыми для указанного импульса, так как на их первых входах присутствуют единичные сигналы с выходов соответствующих элементов И 24.1-24.k.

Одновременно импульс синхронизации поступает на второй вход элемента ИЛИ 30. С выхода элемента ИЛИ 30 данный импульс подается на синхронизирующий вход регистра 26 длины очереди и своим задним фронтом фиксирует в этом регистре новый установившийся код длины очереди 11...10 с выходов элементов И 24.1-24. k. В то же время на выходе элемента И 29 появляется нулевой уровень сигнала, в связи с чем на выходе элемента НЕ 28 появляется сигнал логической единицы, который поступает на (k + 1)-й выход второй группы выходов БООС, сигнализируя тем самым о наличии сообщений.

Код длины очереди сообщений с выходов регистра 26 поступает на первые входы первой 38 и вторые входы 40 схем сравнения БАОС 3. На выходах схем сравнения 38-40 образуется код, определяемый соотношением длин очередей сообщений в БООС 1.1-1.3 в соответствии с таблицей (где L1, L2, L3 - коды длин очередей соответственно в БООС 1.1, 1.2 и 1.3). Сформированный код поступает на входы узла постоянной памяти 37, на выходе которого появляется двоичный код номера БООС, содержащего наибольшее число сообщений (в нашем случае это БООС 1.1 и код "00").

Одновременно сигнал логической единицы с выхода элемента НЕ 28 БООС 1.1 поступает на первый вход элемента ИЛИ 41, проходит на управляющий выход БАОС 3 и затем подается на вход установки S триггера 7, переключая последний в единичное состояние. Единичный сигнал с прямого выхода триггера 7 включает блок 8 синхронизации, и последний начинает вырабатывать три распределенные по времени последовательности тактовых импульсов τ1, τ2, τ3.

Унитарный код номера выбранного БООС ("001"), образующийся на выходах первого дешифратора 11, поступает на входы опроса БООС 1.1-1.3, а на информационных входах регистра 5 появляется сообщение из регистра 20.1 БООС 1.1. Тактовый импульс τ1 с первого выхода блока 8 синхронизации поступает на входы сдвига БООС 1.1-1.3 и на вход синхронизации регистра 5. Данный импульс проходит на выход элемента И 27 БООС 1.1, так как на первом входе этого элемента присутствует единичный сигнал и своим задним фронтом осуществляет сдвиг очереди сообщений в указанном БООС. Одновременно задний фронт этого же импульса появляется на входе синхронизации регистра 5 и фиксирует сообщение в рассматриваемом регистре.

После записи очередного сообщения в регистр 5 начинается анализ содержимого адресных полей 5.1 и 5.2 этого сообщения, в ходе которого определяется направление его дальнейшей передачи. Код идентификатора приемника сообщения C. D (где C и D - номера строки и столбца коммутатора, содержащих модуль - приемник) с выходов первой 5.1 и второй 5.2 групп регистра 5 поступает на вторые группы входов первой 9 и второй 10 схем сравнения, на первых группах входов которых постоянно присутствуют коды соответственно номера строки и столбца текущего модуля, зафиксированные в регистре идентификатора модуля 2. На выходах схем сравнения 9 и 10 формируется код направления передачи сообщения, который поступает на вход второго дешифратора 12 и преобразуется последним в соответствующий двоичный код. Сообщение с выходов регистра 5 поступает на информационные входы с третьего по (n+2)-й демультиплексора 6 и в соответствии с кодом установившимся на адресных входах демультиплексора, передается на одну из выходных информационных шин модуля в сопровождении импульса τ2, поступающего на второй информационный вход демультиплексора со второго выхода блока 8 синхронизации, и импульса τ3, поступающего на первый информационный вход демультиплексора с третьего выхода блока синхронизации.

В случае наличия (после сдвига) сообщений хотя бы в одном регистре БООС 1.1, 1.2, 1.3 триггер 7 остается в единичном состоянии, так как на управляющем выходе БАОС 3 присутствует единичный сигнал, обусловленный наличием единичного сигнала на выходе элемента НЕ 28 по крайней мере одного БООС, и устройство продолжает функционировать рассмотренным выше способом. В противном случае на выходе элемента ИЛИ 41 БАОС 3 устанавливается сигнал логического нуля, который с управляющего выхода БАОС 3 поступает на инверсный вход элемента И 13. Очередной тактовый импульс τ3 с третьего выхода блока 8 синхронизации, поступая через открытый элемент И 13 на вход сброса R триггера 7, устанавливают последний в нулевое состояние. Нулевой сигнал с прямого выхода триггера 7 выключает блок 8 синхронизации.

Так как сигналы записи сообщения и сдвига очереди могут появляться в произвольные моменты времени, что обусловлено асинхронностью работы различных модулей, в прототипе имеет место ситуация, когда при определенных соотношениях моментов возникновения указанных сигналов возможна неустойчивость в работе устройства.

Можно указать два следующих случая.

1. Задний фронт (активный в прототипе) импульса записи появляется позднее переднего, но раньше заднего фронта импульса сдвига. В этом случае поступившее на вход БООС игнорируется, так как появление импульса сдвига обеспечивает наличие на всех группах выходов демультиплексора нулевых уровней сигнала, которые сохраняются в момент действия заднего фронта импульса записи вплоть до момента появления заднего фронта импульса сдвига.

2. Задний фронт импульса сдвига появляется позднее переднего, но раньше заднего фронта импульса записи. В этом случае сообщение, находящееся в первом регистре БООС, не исключается из очереди после считывания, так как задний фронт импульса сдвига маскируется импульсом записи.

В предлагаемом устройстве одновременное инициирование операций сдвига и записи исключается путем временного распределения соответствующих сигналов.

Импульс сдвига формируется на выходе элемента И 27 при поступлении сигнала опроса БООС на его первый вход и импульса τ1 с первого выхода блока 8 синхронизации - на второй вход. Процесс записи синхронизируется источником сообщения и представляется в виде двух фаз: устранения блокировки и собственно записи сообщения. Блокировка устанавливается импульсом τ

Рассмотрим работу одного (любого) из БООС при различных соотношениях моментов поступления сигналов сдвига и записи.

1. Сигнал сдвига появляется раньше сигнала блокировки τ

Импульс π с выхода одновибратора 31 через элементы ИЛИ 25.1-25.k поступает на входы синхронизации регистров 20.1-20.k и своим передним фронтом обеспечивает сдвиг очереди сообщений в этих регистрах. При реализации сдвига на всех группах выходов демультиплексора 22 присутствуют нулевые сигналы, так как на прямом выходе триггера 34 управления демультиплексором присутствует единичный (запрещающий) сигнал, что обеспечивает правильность работы устройства при сдвиге. В то же время импульс π поступает на первый вход элемента ИЛИ 30 и на второй вход элемента ИЛИ 36, а с выходов указанных элементов - на вход синхронизации регистра 26 длины очереди и на счетный вход триггера 32 запроса соответственно. По заднему фронту импульса π триггер 32 устанавливается в исходное (нулевое) состояние, а в регистре 26 фиксируется новый код длины очереди (при этом предполагается, что к моменту появления заднего фронта импульса π переходные процессы завершены).

2. Сигнал сдвига поступает после сигнала блокировки. Импульс блокировки τ на первых входах которых присутствуют сигналы логической единицы, через элементы ИЛИ 25. t

на первых входах которых присутствуют сигналы логической единицы, через элементы ИЛИ 25. t  поступает на входы синхронизации соответствующих регистров и своим передним фронтом фиксирует сообщение в выбранном регистре. Одновременно триггер 34 управления демультиплексором переходит в единичное состояние и единичный сигнал с его прямого выхода, поступая на вход разрешения демультиплексора 22, устанавливает на всех выходах последнего сигналы логического нуля. Так как задержка распространения сигнала через пару элементов - элемент И 23.r и элемент ИЛИ 25.r

поступает на входы синхронизации соответствующих регистров и своим передним фронтом фиксирует сообщение в выбранном регистре. Одновременно триггер 34 управления демультиплексором переходит в единичное состояние и единичный сигнал с его прямого выхода, поступая на вход разрешения демультиплексора 22, устанавливает на всех выходах последнего сигналы логического нуля. Так как задержка распространения сигнала через пару элементов - элемент И 23.r и элемент ИЛИ 25.r  - меньше времени, которое требуется на переключение триггера 34, блокировку демультиплексора 22, и задержки блока элементов ИЛИ 21.h

- меньше времени, которое требуется на переключение триггера 34, блокировку демультиплексора 22, и задержки блока элементов ИЛИ 21.h  в момент появления на входах синхронизации регистров 20.1-20. k переднего фронта импульса τ

в момент появления на входах синхронизации регистров 20.1-20. k переднего фронта импульса τ

Задний фронт импульса τ

Временные диаграммы работы БООС при различных соотношениях моментов появления сигналов записи и сдвига представлены на фиг. 4, где буквами A, B, .. ., K обозначены цепи БООС (фиг. 2), соответствующие приведенным диаграммам.

Таким образом, дополнительно введенные в устройство элементы и соответствующие им связи обеспечивают его устойчивое функционирование при любых соотношениях моментов появления сигналов записи сообщений и сдвига очередей.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1999 |

|

RU2168204C1 |

| МОДУЛЬ ДЛЯ ПЕРЕДАЧИ И ВЕЩАНИЯ СООБЩЕНИЙ В МАТРИЧНОМ КОММУТАТОРЕ | 2003 |

|

RU2249848C2 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2166793C1 |

| МОДУЛЬ КОММУТАЦИОННОЙ СЕТИ | 2000 |

|

RU2175146C1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ, ПРЕДНАЗНАЧЕННЫЙ ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ, ОБМЕНА СООБЩЕНИЯМИ И ОРГАНИЗАЦИИ ВЕЩАТЕЛЬНЫХ РЕЖИМОВ ОБМЕНА СООБЩЕНИЯМИ | 2000 |

|

RU2178584C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

Использование: в вычислительной технике, и в частности при построении средств коммутации мультипроцессорных вычислительных систем. Сущность изобретения: повышение устойчивости работы устройства. В каждый блок организации очередей сообщений модуля, содержащего с первого по третий блоки организации очередей сообщений, регистр идентификатора модуля, блок анализа очередей сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, первую и вторую схемы сравнения, первый и второй дешифраторы и элемент И, включающий регистры с первого по К-й, группу блоков элементов ИЛИ с первого по ( К-1)-й, демультиплексор, первую и вторую группы элементов И с первого по К -й, группу элементов ИЛИ с первого по К -й, регистр длины очереди, первый и второй элементы И, элемент НЕ и первый элемент ИЛИ, дополнительно введены одновибратор, триггеры запроса, блокировки и управления демультиплексором, третий элемент И и второй элемент ИЛИ. 1 з.п.ф-лы, 4 ил., 1 табл.

| SU, авторское свидетельство, 1499364, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1793436, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1783510, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1575167, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-05-10—Публикация

1996-04-24—Подача