, Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых узлов повышенной надежности. Г

Цель изобретения - повышение достоверности определения числа единиц.

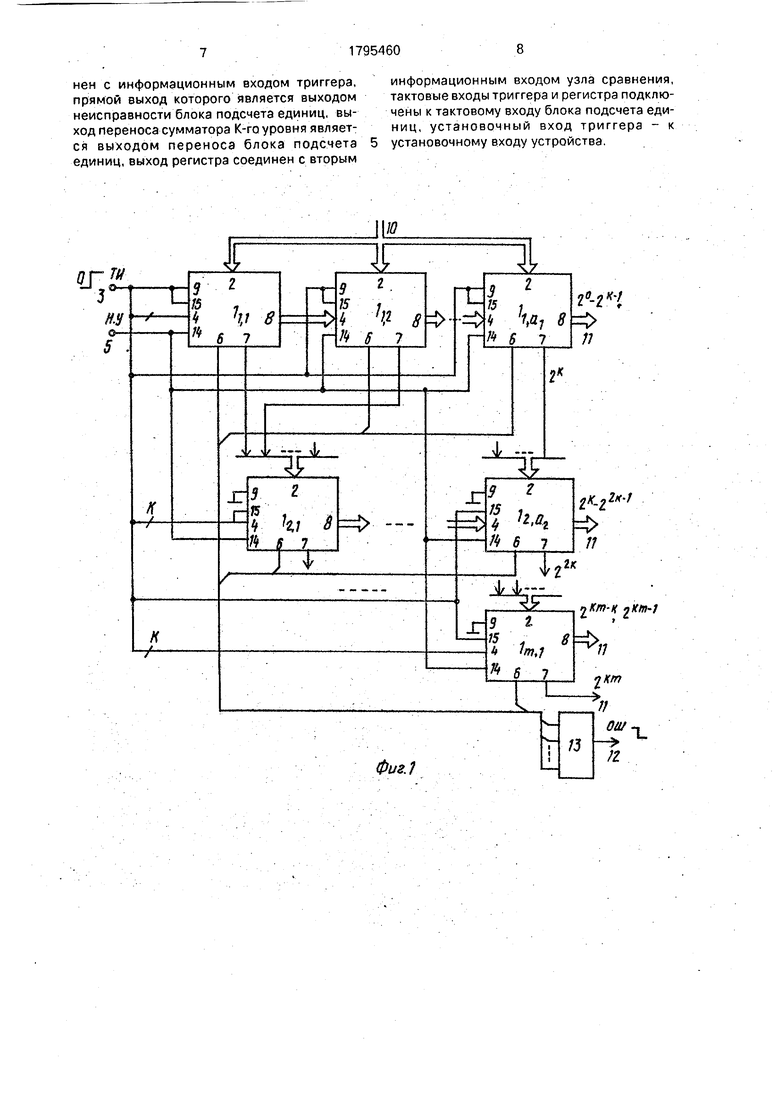

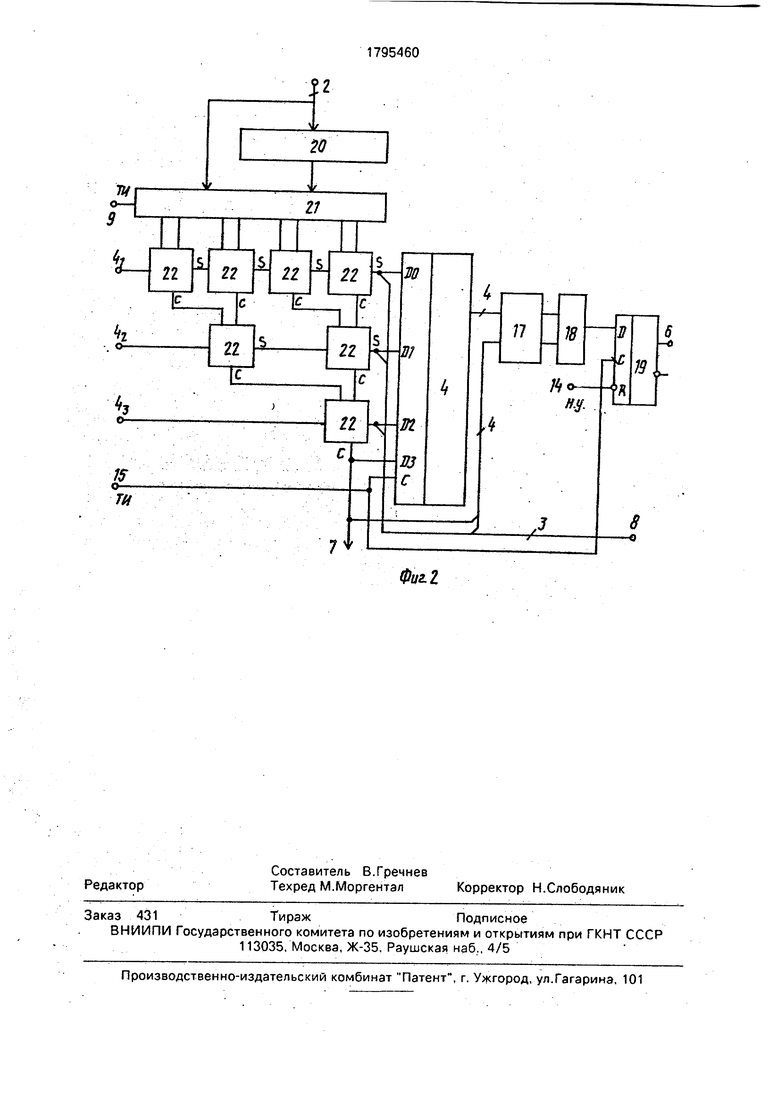

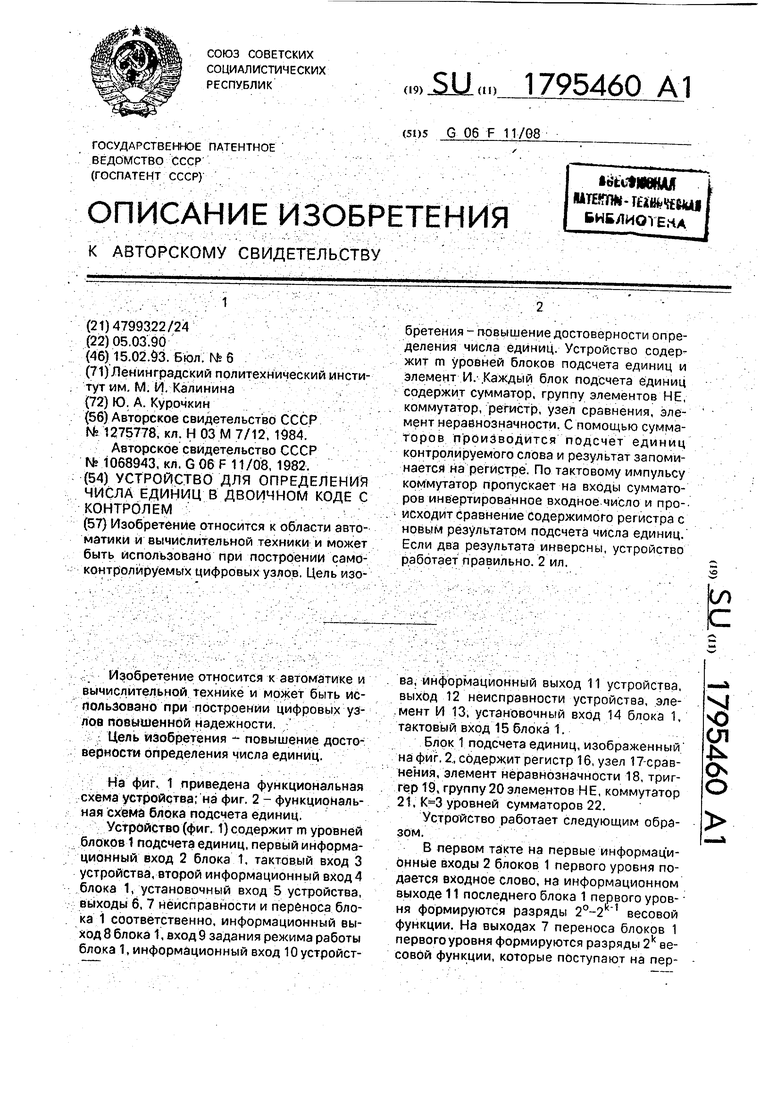

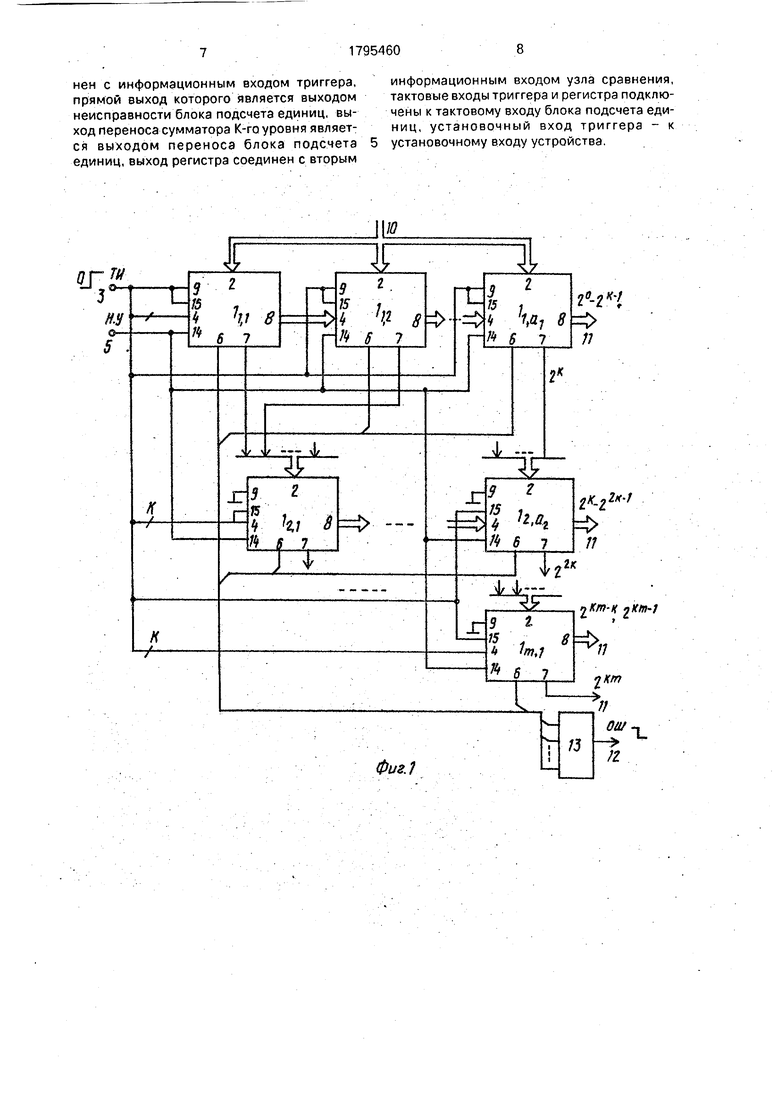

На фиг, 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока подсчета единиц.

Устройство (фиг. 1)содержит m уровней блоков 1 подсчета единиц, первый информационный вход 2 блока 1, тактовый вход 3 устройства, второй информационный вход 4 блока 1, установочный вход 5 устройства, выходы б, 7 неисправности и переноса блока 1 соответственно, информационный выход 8 блока 1, вход 9 задания режима работы блока 1, информационный вход 10 устройства, информационный выход 11 устройства, выход 12 неисправности устройства, эле- ,мент И 13, установочный вход 14 блока 1, тактовый вход 15 блока 1.

Блок 1 подсчета единиц, изображенный на фиг. 2, содержит регистр 16, узел 17-срав- нения, элемент неравнозначности 18, триггер 19, группу 20элементов НЕ, коммутатор 21, уровней сумматоров 22.

Устройство работает следующим образом. .

В первом такте на первые информационные входы 2 блоков 1 первого уровня подается входное слово, на информационном выходе 11 последнего блока 1 первого уров- ня формируются разряды 2°-2k t весовой функции. На выходах 7 переноса блоков 1 первого уровня формируются разряды 2k весовой функции, которые поступают на пер Ю

ел J о о

вые информационные входы 2 блоков 1 второго уровня, и т.д.

По положительному переходу тактового сигнала ТИ на тактовом входе 3 устройства блоки 1 фиксируют значение своих выходных сигналов, действующих в первом такте. Во втором такте за счет смены сигналов на входах 9 задания режима работы инвертируются входные сигналы на входах сумматоров 22 блоков 1 первого уровня. Входы 9 задания режима работы блоков 1 последующих уровней подключены к шине нулевого потенциала устройства, поэтому эти блоки 1 не инвертируют сигналы, поступающие на первые информационные входы 2.

При исправности блоков 1 предыдущих уровней инверсия на входах блоков 1 последующих уровней получается автоматически. Этим обусловлено зануление входов 9 блоков 1 всех уровней, кроме первого. Иначе имела бы место двойная инверсия сигналов на входах 2 этих блоков 1 и режим проверки нельзя было бы осуществить.

Если в предыдущих блоках 1 ошибок не было, то сигналы на входах 2 любого из последующих блоков примут инверсное значение. При этом все свободные разряды первых и вторых информационных входов 2, 4 первых блоков 1 всех уровней соединены с тактовым входом 3 устройства, смена сигналов которого обеспечивает условные инвертирования выходных сигналов блоков 1, если они работают безошибочно.

Неисправность некоторого блока 1 ведет к ошибке сравнения выходных сигналов двух тактов его работы. Эта ошибка распространяется на все последующие блоки. На выходах 6 заданных блоков 1 устанавливается нулевой сигнал, поступающий на выход 12 неисправности устройства через элемент И 13. Поиск неисправности сводится к определению блока 1 с нулевым сигналом на выходе б, для которого все предыдущие блоки 1 имели единичный сигнал на этом выходе-.

Рассмотрим работу блока 1 подсчета единиц. Основной функциональной частью этого блока является группа сумматоров 22. Функции суммы и переноса полного Сумматора являются самодвойственными, поэтому инверсией входных сигналов можно обнаружить любые константные неисправности на входах и выходах сумматора. Данное свойство сохраняется и для матрицы сумматоров в целом. Проведенный анализ показал, что для некоторых схем сумматоров обнаруживаются и все константные неисправности промежуточных логических элементов. Константные неисправности группы элементов НЕ 20 и коммутатора 21

приводят к нарушению инверсии входных переменных во втором также работы, что такое может быть обнаружено средствами контроля.

В первом такте данные с входов 2 через коммутатор 21 поступают на входы первой линейки сумматоров 22, одновременно на входы 4 подаются данные от блока 1, стоящего слева (или нули, если рассматриваемый блок является первым блоком 1 уровня). С выходов последних сумматоров 22 линеек код веса поступает на выходы 8 и выход переноса 7. По положительному перепаду сигнала на входе 15 выходные сигналы записываются на регистр 16.

Во втором также в зависимости от подключения входа 9 данные со входов 2 .поступают на матрицу сумматоров либо через группу 20 элементов НЕ, либо без инверсии.

В последнем случае полагается, что инвертирование входных сигналов проводит предыдущий блок 1. Сигналы на входах 4 инвертируются либо предыдущим блоком, либо изменением уровня сигнала тактового

импульса. При инверсии входных данных в условиях отсутствия ошибок выходные сигналы второго такта инверсны выходным сигналам первого такта.

Узел 17 сравнения сравнивает вектор,

записанный на регистре 16 в первом такте, с вектором на выходах сумматоров 22 последнего столбца блока, полученным во втором такте. Пусть в первом такте имеем вектор Vi D3D2DiDp, а во втором, если нет

ошибок, вектор N/2 63620iDo. Эти вектора сравниваются поразрядно, согласно весу разрядов.

Если каждый разряд вектора. V2 инверсен соответствующему разряду вектора Vi,

то на выходах узла 17 сравнения имеем наборы 01 или 10, иначе - сигналы 00 или 11. Обнаружение ошибки вызывает установку триггера 19 по спаду сигнала ТИ в нулевое состояние и формирование нулевого .сигнала на контрольном выходе 6 блока. 1.

. Определим число m уровней устройства в зависимости от числа п разрядов информационного входа 10 устройства и числа

разрядов 8 входа 2 одного блока 1 подсчета единиц. Значение m определяется из неравенства.

55

ет

1 или п 2

кт

Возьмем двоичный логарифм от обоих частей неравенства, откуда получим

d m

|П2 П

общее число 1 задается выражением:

и ш-иЈг +

+1

Примеры:

1), , , N 16+4+1 21

2) , , т ,66 - , N 32+4+1 35.

3) , , т (1п2450)/3 - , N 57+7+1 65.

Формула изобретения

Устройство для определения числа единиц в двоичном коде с контролем, содержащее m уровней блоков подсчета единиц (mHogan/logab (округлять в большую сторону), где п - разрядность информационного входа устройства, - разрядность первого информационного входа блока подсчета единиц, k: - разрядность информационного выхода блока подсчета единиц), прием первые информационные входы блоков подсчета единиц первого уровня образуют информационный вход устройства, информационные выходы ад-х блока подсчета единиц всех уровней и выхода переноса блока подсчета единиц т-го уровня образуют информационный выход устройства (q-номер уровня, 1 q m,aq- число блоков подсчета единиц q-ro уровня, (округлять в большую сторону), в каждом 1-м уровне блоков подсчета единиц (1 I m-1) информационный выход j-ro блока подсчета единиц соединен с вторым информационным входом 0+1)Го блока подсчета единиц (1 J аи, где а - число блоков подсчета единиц i-ro уровня, (округлять в большую сторону), выход переноса каждого j-ro блока подсчета единиц i-ro уровня соединен с соответствующим разрядом первого информационного входа l j/b-ro блока подсчета единиц 0+1)- го уровня (1 округлять в большую сторону), выход переноса aq-ro блока подсчета единиц каждого 1-го уровня соединен с соответ- ствующимразрядом первого информационного входа ач-го блока подсчета единиц (i+1)-ro уровня, отличающее- с я тем. что, с целью повышения достоверности определения числа единиц, в устройство введен элемент И, а каждый блок

подсчета единиц содержит группу элементов НЕ, коммутатор, регистр, узел сравнения, элемент неравнозначности, триггер и К уровней сумматоров, причем установочные входы всех блоков подсчета единиц подключены к установочному входу устройства, тактовые входы блоков подсчета единиц - к тактовому входу устройства, входы задания режима работы блоков подсчета единиц

первого уровня - к тактовому входу устройства, входы задания режима работы блоков подсчета единиц всех уровней, начиная с второго - к шине нулевого потенциала устройства, вторые информационные входы

первых блоков подсчета единиц каждого уровня подключены к тактовому входу устройства, выходы неисправности каждого блока подсчета единиц - к соответствующим входам элемента И, выход которого

является выходом неисправности устройства, в каждом блоке подсчета единиц управляющий вход коммутатора подключен к входу задания режима работы блока подсчета единиц, в каждом блоке подсчета единиц

первый информационный вход коммутатора подключен к первому информационному входу блока подсчета единиц, входы элементов НЕ группы подключены к соответствующимразрядам первого

информационного входа блока, подсчета единиц, выходы элементов НЕ группы подключены к соответствующим разрядам второго информационного входа коммутатора; входы первого и второго операндов каждого

сумматора первого уровня соединены с соответствующими разрядами информационного выхода коммутатора, выход результата каждого предыдущего сумматора в р-м уровне (1 р п-1) соединен с входом переноса последующего сумматора, входы первого и второго операндов каждого сумматора (р+1)-го уровня соединены с выходами переноса соответствующих сумматоров, р-го уровня, входы переноса первых

сумматоров каждого уровня подключены к соответствующим разрядам второго информационного входа блока подсчета единиц, выходы результата сумматоров г-х уровней (1 г к) образуют мнформационный выход блока подсчета единиц, выходы результата последних сумматоров всех уровней и выход переноса сумматора последнего уровня подключены к соответствующим разрядам информационного входа

регистра и первого информационного входа узла сравнения, выходы сравнения и несравнения которого соединены с соответствующимивходами элемента неравнозначности, выход которого соединен с информационным входом триггера, прямой выход которого является выходом неисправности блока подсчета единиц, выход переноса сумматора К-го уровня является выходом переноса блока подсчета единиц, выход регистра соединен с вторым

информационным входом узла сравнения, тактовые входы триггера и регистра подключены к тактовому входу блока подсчета единиц, установочный вход триггера - к установочному входу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1314386A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для поиска кратных дефектов в группе объектов | 1983 |

|

SU1233157A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении само- контролйруемых цифровых узлов. Цель изобретения - повышение достоверности определения числа единиц. Устройство содержит m уровней блоков подсчета единиц и элемент И.-.Каждый блок подсчета единиц содержит сумматор, группу элементов НЕ, коммутатор, регистр, узел сравнения, элемент неравнозначности. С помощью сумматоров производится подсчет единиц контролируемого слова и результат запоминается на регистре. По тактовому импульсу коммутатор пропускает на входы сумматоров инвертированное входное число и про-, исходит сравнение Содержимого регистра с новым результатом подсчета числа единиц. Если два результата инверсны, устройство работает правильно. 2 ил.

5

Ik

г«-1

2КМ-1

я

11 ОШ

X

| Устройство для определения количества единиц в двоичном числе | 1984 |

|

SU1275778A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля импульсов синхронизации | 1982 |

|

SU1068943A2 |

Авторы

Даты

1993-02-15—Публикация

1990-03-05—Подача