Изобретение относится к технике передачи и приема информации и может быть использовано при создании системы с высокой частотой и энергетической эффективностью.

Наиболее близкой к изобретению по технической сущности к достигаемому эффекту является система передачи информации перфорированным сверточным кодом, содержащая на передающей стороне пер&ый кодер, вход которого является информационным входом системы, преобразователь кода в фазу, выход которого подключен к входу модулятора, выход которого является входом линии связи, тактовые входы преобразователя кода в фазу и первого кодера являются первым и вторым тактовыми входами передающей стороны соответственно, на приемной стороне демодулятор, вход которого является выходом линии связи, декодер, выход которого подключен к первому входу блока синхронизации и является информационным выходом системы, тактовые входы декодера и блока синхронизации являются первым и вторым тактовыми входами приемной стороны.

Общими признаками предлагаемого технического решения и прототипа являются на передающей стороне первый кодер, вход которого является информационным входом системы, преобразователь кода в фазу, выход которого подключен к входу модулятора, выход которого является входом линии связи, тактовые входы преобразователя кода в фазу и первого кодера являются первым и вторым тактовыми входами передающей стороны соответственно, на приемной стороне демодулятор, вход которого является выходом линии связи, декодер, выход которого подключен к первому входу блока синхронизации и является информационным выходом системы, тактовые входы декодера и блока синхронизации являются первым и вторым тактовыми входами приемной стороны.

Недостатками известного технического решения являются: ограниченная пропускная способность канала вследствие того, что модем при данном методе обработки сигнала может работать только со сверточным кодом с результирующей кодовой скоростью R 2/3, сложность вычисления метрик ветвей отдельно для перфорированной и неперфорированной ветви кода относительно точек, соответствующих центрам ..секторов сигнала, в том числе, трудности определения точек центра при приеме реальных сигналов и необходимость введения операций возведения в квадрат и извлече

ния корня при определении расстояния принятого сигнала до точек центра, что приводит к усложнению системы и уменьшению ее быстродействия.

Целью изобретения является повышение пропускной способности системы с восьмифазной модуляцией.

Поставленная цель достигается тем, что усовершенствуется система передачи ин0 формации перфорированным сверточным кодом с восьмифазной модуляцией, содержащая на приемной стороне первый кодер, вход которого является информационным входом системы, преобразователь кода в

5 фазу, выход которого подключен к входу модулятора, выход которого является входом линии связи, тактовые входы преобразователя кода в фазу и первого кодера являются первым и вторым тактовыми входами пере0 дающей стороны соответственно, на приемной стороне демодулятор, вход которого является выходом линии связи, декодер, выход которого подключен к первому входу блока синхронизации и является информа5 ционным выходом системы, тактовые входы декодера и блока синхронизации являются первым и вторым тактовыми входами приемной стороны.

Отличительными признаками системы

0 передачи информации перфорированным сверточным кодом с восьмифазной модуляцией являются на передающей стороне второй кодер, первый и второй выходы первого кодера подключены к первому и второму

5 информационным входам второго кодера, первый, второй и третий выходы которого подключены к первому, второму и третьему информационным входам преобразователя кода в фазу, соответственно, первый и вто0 рой тактовые входы второго кодера являются первым и вторым тактовыми входами передающей стороны соответственно, на приемной стороне селекторы знака сигнала, блоки выделения модуля сигнала, блоки

5 выделения максимума сигналов, блоки масштабирования сигнала, сумматоры, вычитэ- тели, блок сравнения, блок контроля четности, кодер и коммутатор, первый выход демодулятора подключен к объединен0 ным первому входу первого сумматора, к входу первого блока масштабирования сигнала, к входу первого блока выделения модуля сигнала и к входу первого селектора знака сигнала, второй вход демодулятора

5 подключен к объединенным первому входу второго сумматора, к входу второго блока масштабирования сигнала, к входу второму блока выделения модуля сигнала и к входу второго селектора знака сигнала, выходы первого и второго блоков выделения модуля

сигналов подключены к первому и второму входам первого блока выделения максимуа сигналов соответственно, выход которого подключен к первому входу блока сравнения , выходы первого и второго селекторов знака сигналов подключены к первому и второму информационным входам коммутатора соответственно, выход первого блока масштабирования сигнала подключен к первым входам третьего сумматора и первого вычитателя, выход первого сумматора через третий блок выделения модуля сигнала подключен к первым входам кодера -, и второго вычитателя, выход второго сумматора через четвертый блок выделения модуля сигнала подключен к вторым входам кодера и второго вычислителя, выход третьего сумматора подключен к второму входу второго сумматора, через пятый блок выделения модуля сигнала к первому входу второго блока выделения максимума сигналов и через третий селектор знака сигналив к третьему информационному входу коммутатора, выход первого вычитателя подключен к второму входу первого сумматора, через шестой блок выделения модуля сигнала к второму входу второго блока выделения максимума сигналов и через четвертый селектор знака сигнала к четвертому информационному входу коммутатора, выход которого вычитателя через седьмой блок выделения модуля сигнала подключен к третьему входу кодера, выход второго блока выделения максимума сигналов подключен к второму входу блока сравнения, выход которого подключен к управляющим входам кбммутатора и блока контроля чётности, выход последнего подключен к четвертому входу кодера первый и второй выходы ком-, мутатора подключены к первому и второму входам блока контроля чётности и к пятому и шестому входам кодера соответственно, выходы первой и второй групп выходов и первый выход которого подключены к соответствующим входам декодера, второй выход кодера подключен к вторым входам екодера и блока синхронизации, выход коорого подключен к управляющему входу кодера, первый тактовый вход последнего вляется первым тактовым входом приемной стороны, второй тактовый вход кодера вляется третьим тактовым входом прием ной стороны, тактовые входы блока сравнеия, блока контроля четности, коммутатора третьего входа кодера объединены и являтся четвертым тактовым входом приемной тороны.

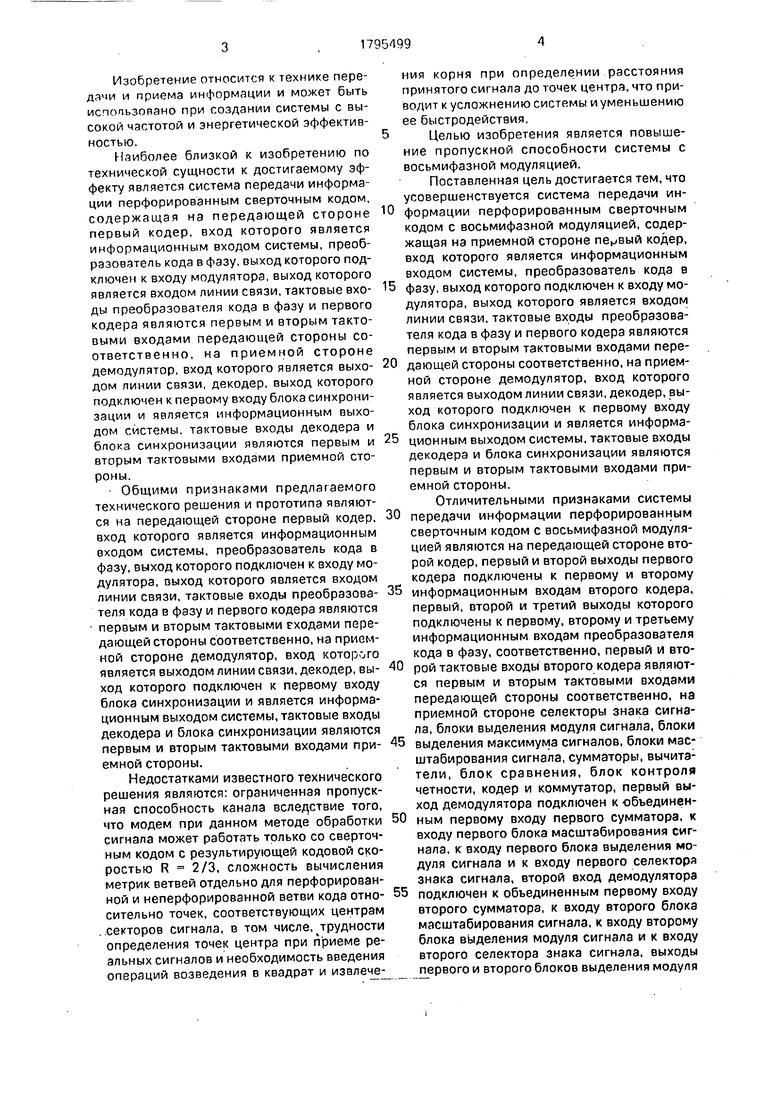

На фиг. 1 представлена структурная хема системы передачи информации перорированным сверточным кодом с восьми

фазной модуляцией, на фиг. 2,3- структурные схемы второго кодера 2 на передающей стороне и кодера 30 на приемной стороне, на фиг.4 - диаграмма формирования коор- 5 динатных систем, на фиг. 5 - энергетические характеристики системы.

Система передачи информации содер: жит на передающей стороне первый кодер

1 сверточного кода, второй кодер 2, преоб10 разователь 3 кода в фазу, восъмифазный

-модулятор .4. линия связи 5, на приемной

стороне четырехфазный демодулятор б с

блоком восстановления несущей, первый 7

и второй 8 селекторы знака сигнала, первый

15 9 и второй 10 блоки масштабирования сигнала, первый 11, второй 12 и третий 13 сумматоры; первый 14 вычитатель. первый 15 и второй 16 блоки выделения модуля сигнала, ; третий 18, четвёртый 19, пятый 20 и шестой

20.-2.1 блоки выделения модуля сигнала, третий 22 и четвертый 23 селекторы знака сигнала,

второй 24 блок выделения максимума, ком. мутатор 25, второй 26 вычитатель, седьмой

: 27 блок выделения модуля сигнала, блок 28

25 .сравнения, блок 29 контроля четности, кодер 30, сверточный декодер 31, блок 32 узловой синхронизации.

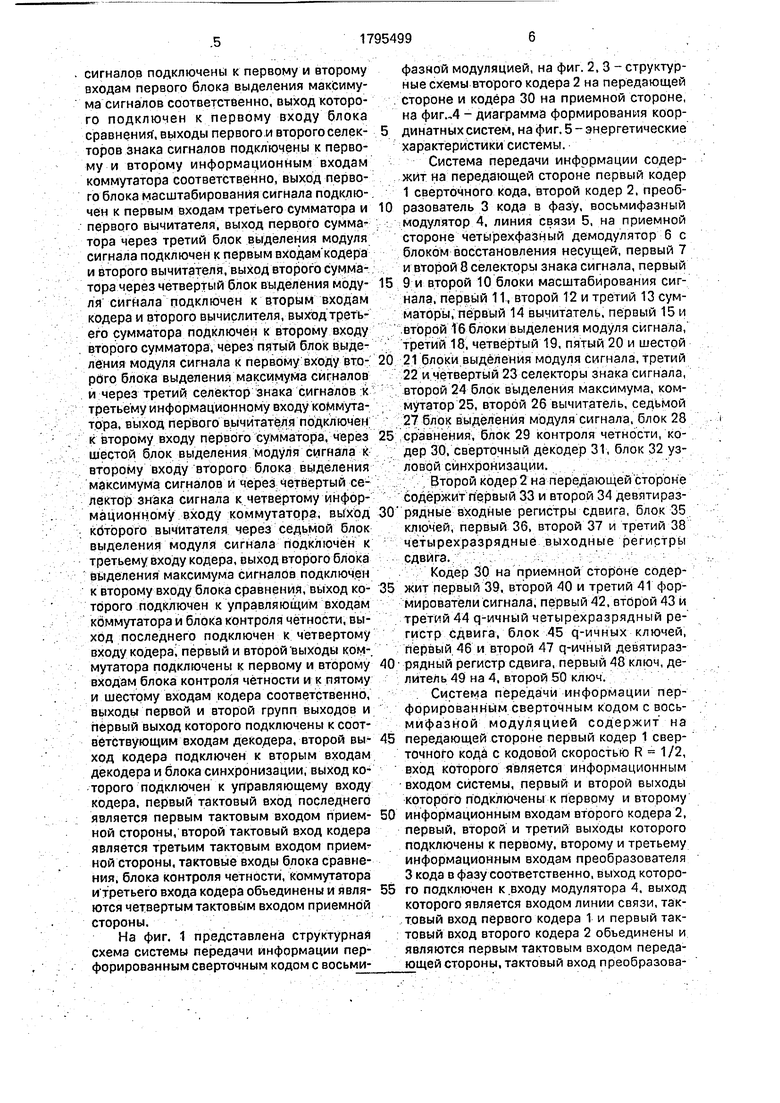

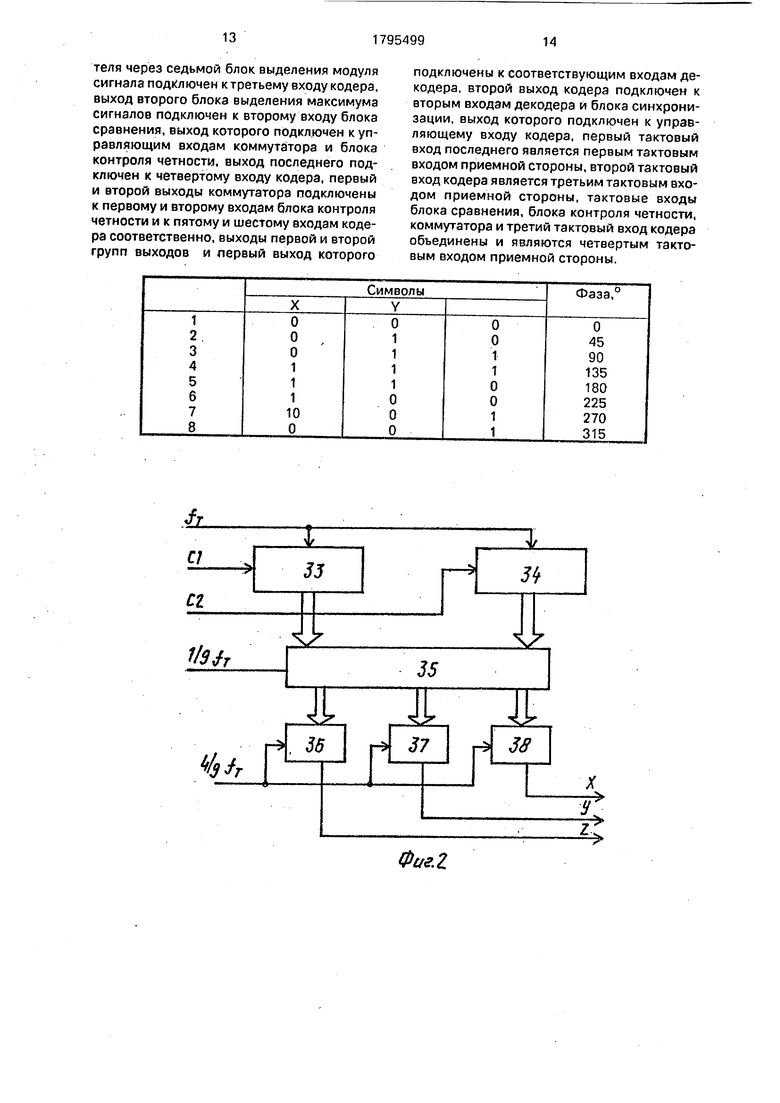

, . . Второй кодер 2 на передающей стороне содержитпервый 33 и второй 34 девптираз0 рядные входные регистры сдвига, блок 35

ключей, первый 36, второй 37 и третий 38

четырехразрядные выходные регистры

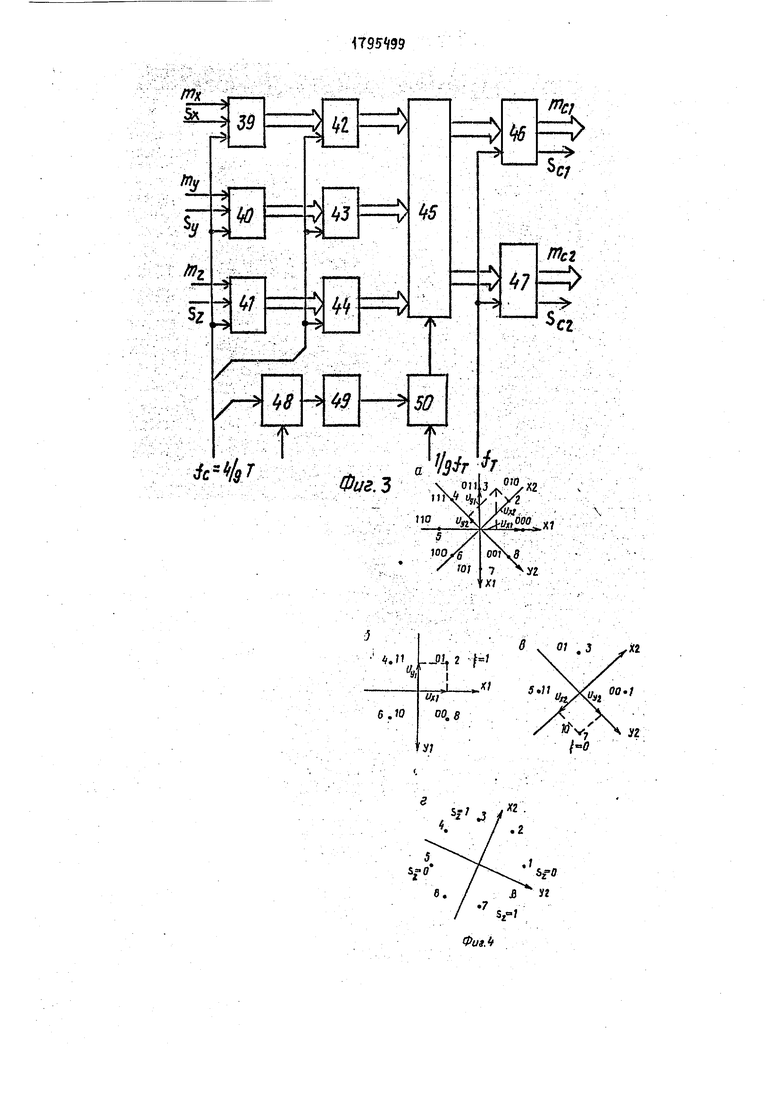

сдвига. ; .- ..-:.,:; .--: : ; - - ; Кодер 30 на приемной стороне содер5 жит первый 39, второй 40 и третий 41 формирователи сигнала, первый 42, второй 43 и третий 44 q-ичный четырехразрядный регистр сдвига, блок 45 q-ичных ключей, первый 46 и второй 47 q-ичный девятираз0; рядный регистр сдвига, первый 48 ключ, делитель 49 на 4, второй 50 ключ. . Система передачи информации перфорированным сверточным кодом с вось- мифазной модуляцией содержит на

5 передающей стороне первый кодер 1 сверточного кода с кодовой скоростью R 1/2, вход которого является информационным входом системы, первый и второй выходы которого подключены к первому и второму

0 информационным входам второго кодера 2, первый, второй и третий выходы которого подключены к первому, второму и третьему информационным входам преобразователя 3 кода в фазу соответственно, выход которо5 го подключен к .входу модулятора 4, выход которого является входом линии связи, тактовый вход первого кодера 1 и первый тактовый вход второго кодера 2 объединены и являются первым тактовым входом передающей стороны, тактовый вход преобразоватепя J кода в фазу и второй тактовый вход второго.кодера 2 объединены и являются вторым тактовым входом передающей стороны системы, на приемной стороне демодулятор 6с блоком восстановления несущей, вход демодулятора 6 является вы- - ходом линии связи, первый выход которого подключен к объединенным первому входу первого сумматора 11, входу первого блока 9 масштабирования сигнала, к входу первого блока 15 выделения модуля сигнала и к входу первого селектора 7 знака сигнала, второй вход демодулятора 6 подключен к объединенным первому входу второго 12 сумматора, к входу второго блока 10 масштабирования сигнала, к входу второго блока 16 выделения модуля сигнала и к входу второго селектора 8 знака сигнала, выходы первого 15 и второго 16 блоков выделения модуля сигналов подключены к первому и второму входам первого блока 17 выделения максимума сигналов соответственно, выход которого подключен к первому входу блока 28 сравнения, выходы первого 7 и второго 8 селекторов знака сигнала подключены к первому и второму информационным входам коммутатора 25 соответственно, выход первого блока 9 масштабирования сигнала подключен к первым входам третьего 13 сумматора и первого 14 вычитателя. выход первого 11 сумматора через третий блок 20 выделения модуля сигнала подключен к первым входам кодера 30 и второго 26 вычитателя, выход второго 12 сумматора через четвертый блок 21 выделения модуля сигнала подключен к вторым входам кодера 30 и второго 26 вычитателя, выход третьего 13 сумматора подключен к второму входу второго 12 сумматора, через пятый блок 18 выделения модуля сигнала к первому входу второго блока 24 выделения максимума сигнала и через третий 22 селектор знака сигнала к третьему информационному входу коммутатора 25, выход первого 14 вычитателя подключен к второму входу первого 11 сумматора, через шестой блок 19 выделения модуля сигнала к второму входу второго блока 24 выделения максимума сигналов и через четвертый 23 селектор знака сигнала к четвертому информационному входу коммутатора 30, выход второго 26 вычитателя через седьмой блок 27 выделения модуля сигнала подключен к третьему входу кодера 30, выход второго блока 24 выделения максимума сигналов подключен к второму входу блока 28 сравнения, выход которого подключен к управляющим входам коммутатора 25 и блока 29 контроля четности, выход последнего подключен к четвертому входу кодера 30, первый и второй выходы коммутатора 25 подключены к первому и второму входам блока 29 контроля четности и к пятому и шестому входам кодера 30 соответственно, выходы которого объединены в

первую и вторую группы выходов, ггервая группа выходов подключена к первой группе входов декодера 31, выход которого под- ключен к первому входу блока 32 синхронизации и является информацион0 ным выходом системы, второй выход кодера 30 подключен к вторым входам декодера 31 и блока 32 синхронизации, выход которого подключен к управляющему входу кодера 30, объединенные первый тактовый вход и

5 тактовый вход декодера являются первым тактовым входом приемной стороны, такто: вый вход блока 32 узловой синхронизации является вторым тактовым входом приемной стороны, второй тактовый вход кодера

0 является тактовым входом приемной стороны, тактовые входы блока 28 сравнения, блока 29 контроля четности, коммутатора 25 и третий тактовый вход кодера объединены и являются четвертым тактовым входом

5 приемной стороны.

Система передачи информации перфорированным сверточным кодом работает следующим, образом.

На передающей стороне первый кодер

0 1 формирует канальные последовательности С1 и С2, соответствующие входной информационной последовательности, которые поступают с частотой fT на вход второго кодера, где они записываются в два

5 соответствующих дёвятиразрядных регистра 33, 34 сдвига. В конце каждого девятого тактового импульса (1/9 fr) блок 35 ключей открывается и осуществляется параллельная запись двенадцати символов С1, С2 в

0 регистры 36,37,38 сдвига с частотой fc 4/9 fT, причем выбор этих переписываемых символов определяется матрицей перфорированного кода, задаваемой связями блока 35 ключей между входными 33,34 и выходными

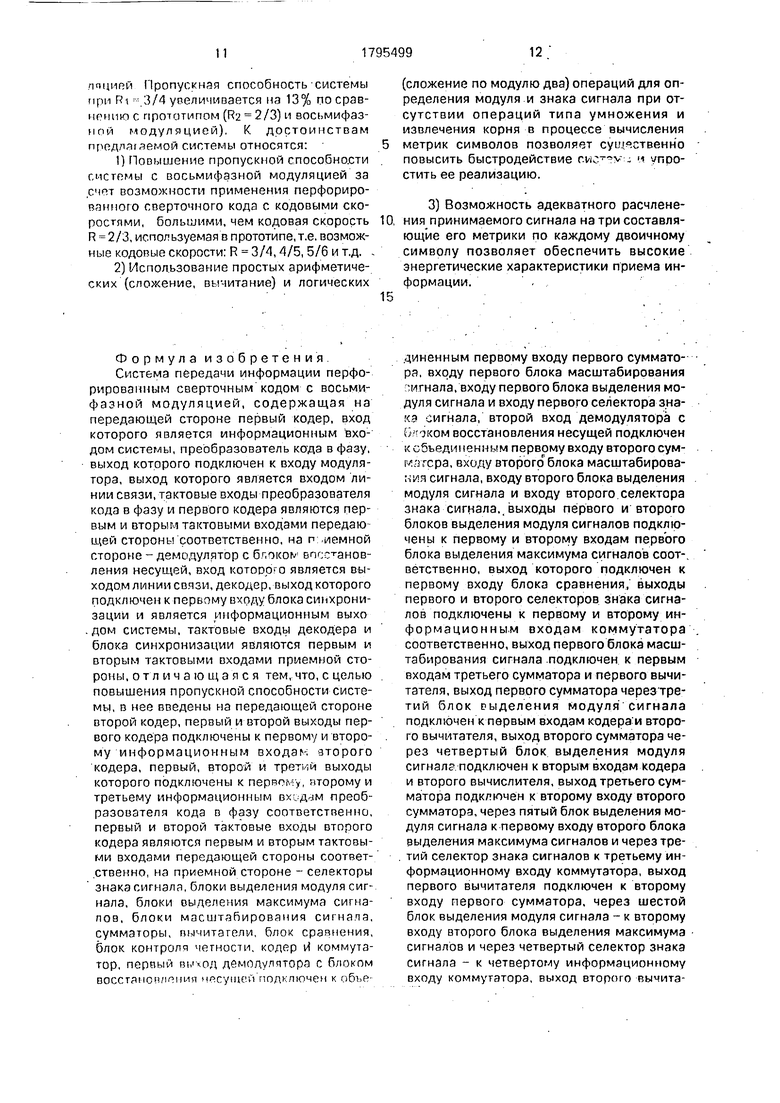

5 Зб, 37, 38 регистрами сдвига. На выходе второго кодера 2 получаем код XY, который с частотой 4/9 fV поступает на вход преобразователя 3 кода в фазу, где происходит преобразование входного кода в-соответст0 вующий фазовый сигнал и подаче его на модулятор 4. работа преобразователя 3 кода в фазу поясняется таблицей.

На приемной стороне принятый сигнал поступает на вход четырехфазного демоду5 лятора 6 с блоком восстановления несущей. Выходные сигналы Xi и Yi с четырехфазного демодулятора 6 поступают одновременно на первый 7 и второй 8 селекторы знака сигнала, первый 9 и второй 10 блоки масш- табирования сигнала, коэффициент которых

равен 0,707, на первый 11 и второй 12 сумматоры. Выходы первого 9 и второго 10 блока масштабирования сигнала соединены с входами первого 14 вычитателя и третьего 13 сумматора, где осуществляется преобразование выходных сигналов четырехфазн.о- го демодулятора по формуле:

V5 X2 Xi -тр-Yi (XiYi).

Y2 Xi- + Yi (Х1 + Yi),

т.е. происходит поворот координатных осей Xi и Yi на 45° (см.рис.4). .

С выхода третьего 13 сумматора .и первого 14 вычитателя сигнал поступает на втот рые входы первого 11 л второго 12 сумматоров соответственно, выходные сигналы которых поступают на блоки 18 и 19 выделения модуля. Осуществляется вычитание модулей соответственно для символов X и Y по формуле:

mx (Xi + Хз) - mY (Yi + Y2)

Модуль символа Z, определяемый как

mz (тх - ту).

вычисляется вторым 26 вычитателем и седьмым 27 блоком выделения модуля.

Определение зн.аков символов X, Y осуществляется в системе координат Xi, Yi или .Х2, Y2, для чего в каждой системе координат определяется максимальное значение модулей символов Xi, YI блоками 15, 16, 17. (rnax/Xi/, /Yi/) и символов Ха, Y2 блоками 20, 21,.24 (max/X2/, /Y2/), после-сравнения которых в блоке 28 сравнения вырабатывается логический сигнал управления (0 или 1), управляющий коммутатором 25.

Если max{/Xi/. /Yi/}- max{/X2/, /Y2/} О, то Ј 1 и на выходе коммутатора 25 появятся сигналы, соответствующие знакам символов Xi и YI, т.к.. Sx Sxi и Sy SYL Если max{/Xi/, /Yi/}-max{/X2/. /Y2/} 0, то Ј 0 на выходе коммутатора 25

Sx 8x2: Sv Sv2.

Знак третьего символа Z выделяется в блоке 29 определения четности сложением логических сигналов Sx, SY и Ј по модулю 2

.

Полученные таким образом модули сигналов и знаки символов X, Y, Z поступают на соответствующие входы кодера 30, где последовательность принятых символов, соответствующих выделенной фазе, преобразуется в последовательность ветвей сигналов выколотого сверточного кода, которая затем декодируется декодером 31 с кодовой скоростью R 3/4. Разделение последовательности символов на ветви осуществляется методом перебора возможных вариантов блоком 32 синхронизации, первый вход которого соединен с выходом декодера 31, а второй вход со знаковым выходом Sx 5 кодера 30 сигнала. При правильной синхронизации на выходе декодера 31 будет выделяться информация, полностью совпадающая с входной информацией системы, задержанной на гзад . В случае неправиль0 ной узловой синхронизации на выходе блока 32 синхронизации будет.вырабатываться сигнал ошибки, управляющий сдвигом фазы в кодере 30 сигнала.

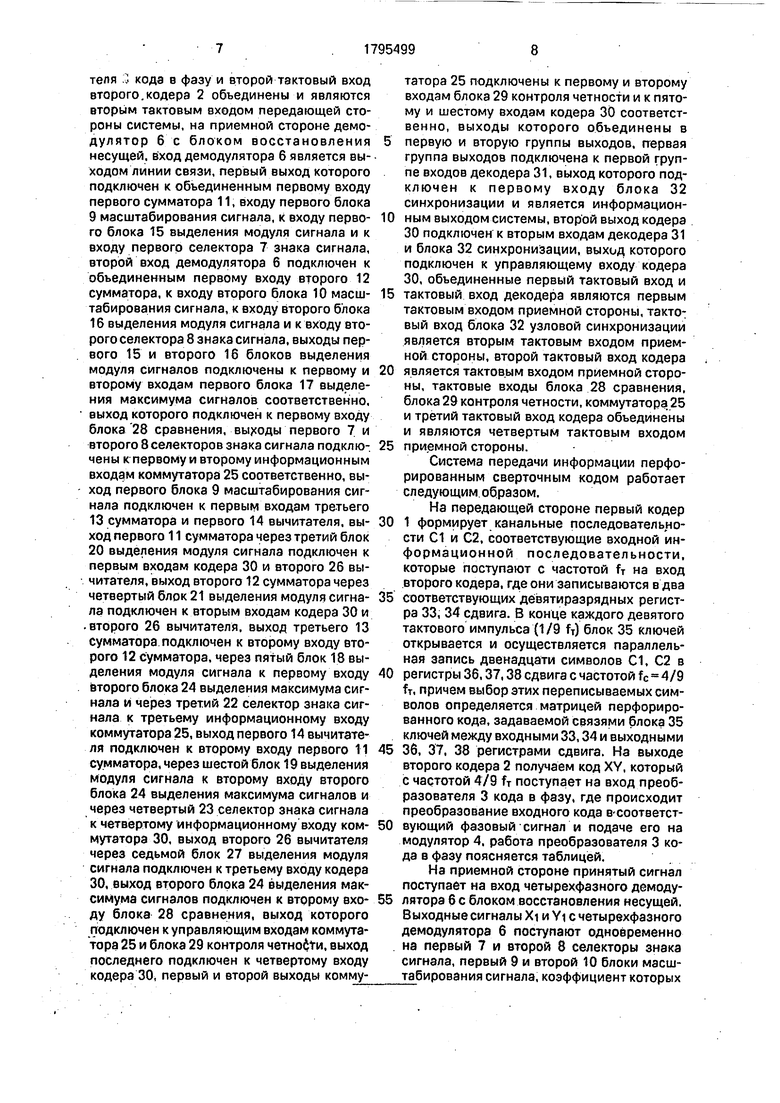

Поясним функционирование системы

5 на конкретном примере. На фиг. 4а изображена фазовая плоскость и ансамбль передаваемых сигналов X, Y, Z. При приеме этот ансамбль разделяется на два подансамбля, как показано на фиг. 46, в. Направления

0 осей X, Y в подансамблях выбраны таким образом, чтобы знаки .символов Sx и SY были равны нулю при положительных проекциях принятого сигнала на оси X, Y и единице - при отрицательных проекциях.

5 Знак символа Z (Sz) выбирается равным нулю, если принятый сигнал находится в I и III квадрантах (см.фиг, 4г) и единице - во

II и IV квадрантах при условии, что система координат X2Y2 повернута на угол я/8.

0 Из.фиг. 4г видно, что при фазовом угле, равном 67,5°, знак символа может быть принят равновероятно как за ноль, так и за единицу. Допустим, что на передающей стороне был выработан код 010 (точка 2 на

5 фиг. 4е). На приемной стороне принят вектор Z, соответствующий некоторому фазовому углу р . Обозначим проекции принятого . вектора на оси Xi, Yi и Х2, Y2 как Uxi и UYI Ux2, UY2. Из примера на фиг. 4а видно, что

0. |UYil IUxil

IUx2l lUY2l

и lUYtl - I Ux21 0, следовательно Ј 1. . В этом случае выбирается система координат XiYi, в которой при Uxi 0 Sx 0 при

5 UYI , знак Sz определяется как Sz Sx®Sy© Ј. Модули сигналов определяем из выражений:. mx lUxi + Ux2l ту I UYI + Uv21

0 mz .1тх - глу|

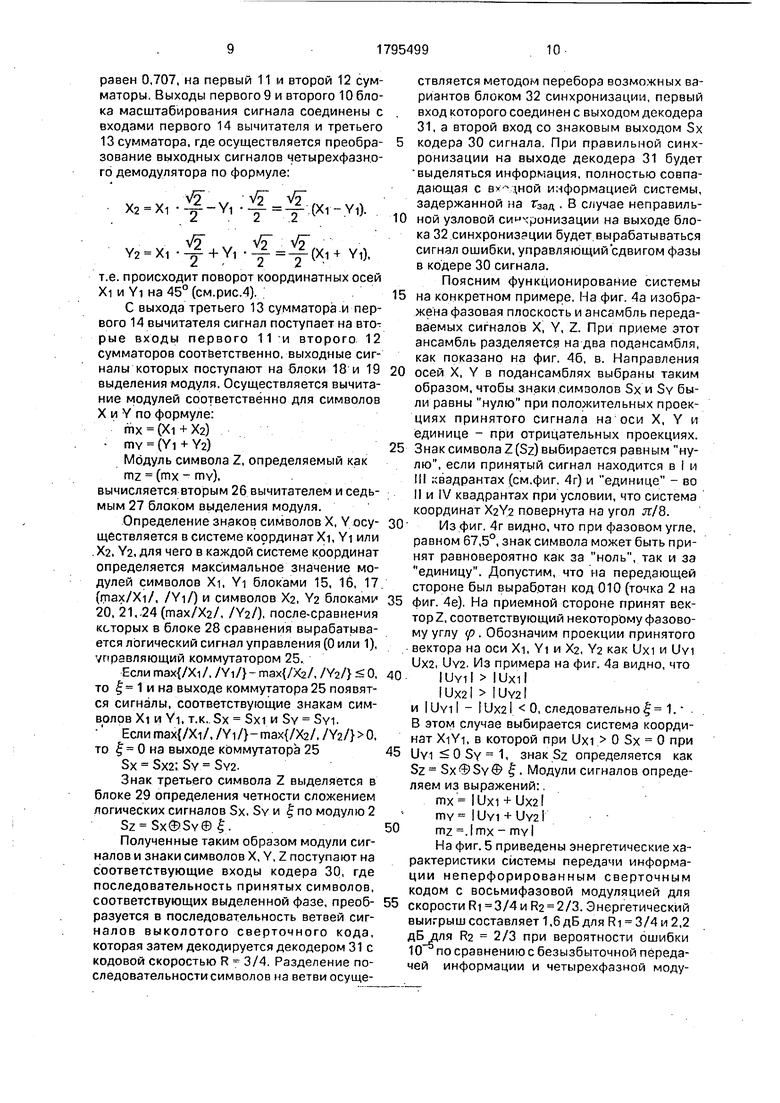

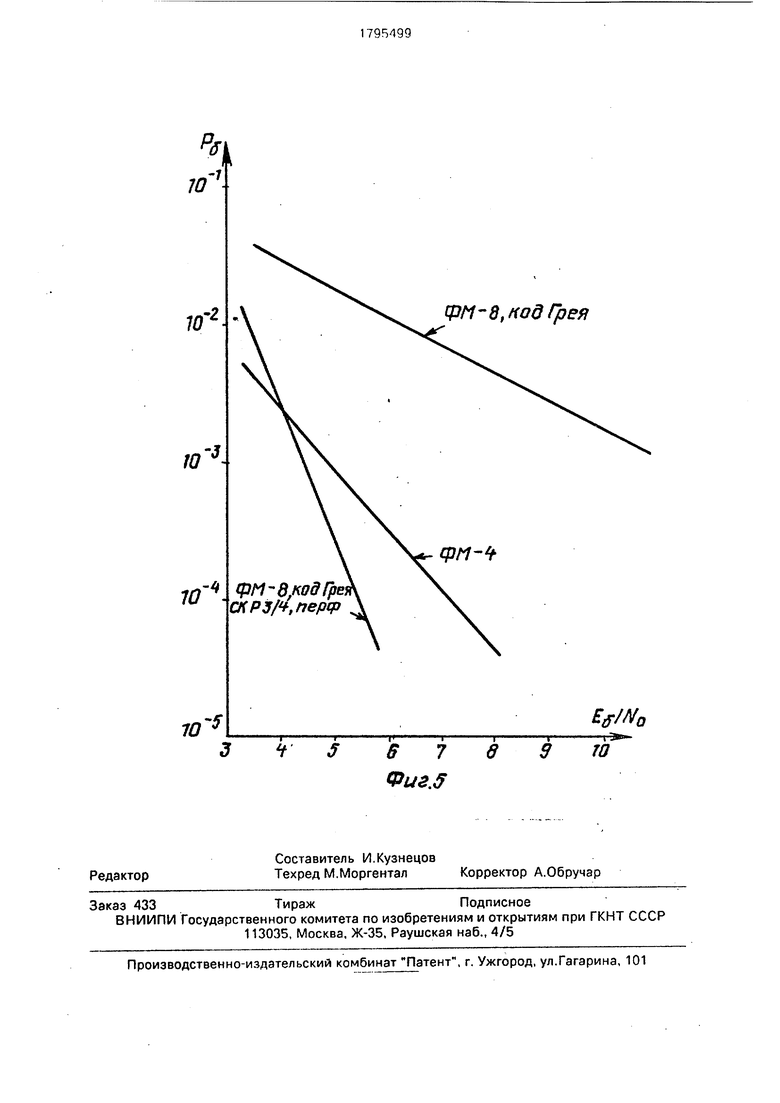

На фиг. 5 приведены энергетические характеристики системы передачи информации неперфорированным сверточным кодом с восьмифазовой модуляцией для

5 скорости RI 3/4 и R2 2/3. Энергетический выигрыш составляет 1,6дБдля Ri 3/4ti2,2 дБ для R2 2/3 при вероятности ошибки 10 по сравнению с безызбыточной передачей информации и четырехфазной модулпцией Пропускная способность системы при RI - 3/4 увеличивается на 13% по сравнению с прототипом (R2 2/3) и восьмифаз- ной модуляцией). К достоинствам предлагяемой системы относятся:

1) Повышение пропускной способности системы с восьммфазной модуляцией за счет возможности применения перфорированного сверточного кода с кодовыми скоростями, большими, чем кодовая скорость R 2/3, используемая в прототипе,т.е. возможные кодовые скорости: R 3/4,4/5, 5/6 и т.д. ,

2) Использование простых арифметических (сложение, вычитание) и логических

(сложение по модулю два) операций для определения модуля и знака сигнала при отсутствии операций типа умножения и извлечения корня в процессе вычисления метрик символов позволяет существенно повысить быстродействие r. - ч упростить ее реализацию.

3) Возможность адекватного расчлене- ния принимаемого сигнала на три составляющие его метрики по каждому двоичному символу позволяет обеспечить высокие энергетические характеристики приема информации..

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Кодек для системы связи с многократной фазовой модуляцией | 1987 |

|

SU1629992A1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| Система для передачи информации с двукратной фазовой манипуляцией сверточным кодом | 1982 |

|

SU1027748A1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНОЖЕСТВЕННЫМ ДОСТУПОМ И ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2023 |

|

RU2819030C1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Кодек сигнально-кодовой конструкции | 1990 |

|

SU1830623A1 |

Изобретение относится к технике передачи информации и может быть использова- но при создании системы с высокой частотной и энергетической эффективностью. Целью изобретения является повышение пропускной способности системы с восьмифазной модуляцией. Система передачи информации перфорированным свер- точным кодом с восьмифазной модуляцией 8пд -- fe 4/3fr fr содержит на передающей стороне первый кодер 1 сверточного кода, второй кодер 2, преобразователь 3 кода в фазу, восьмифаз- ный модулятор 4, линию связи 5, на приемной стороне - четырехфазиый модулятор 6 с блоком восстановления несущей, первый 7 и второй 8 селекторы знака сигнала, первый 9 и второй 10 блоки масштабирования сигнала, первый 11, второй 12 и третий 13 сумматоры, первый вычитатель 14, первый 15 и второй 16 блоки выделения модуля сигнала, первый блок 17 выделения максимума сигнала, третий 18, четвертый 19, пятый 20 и шестой 21 блоки выделения модуля сигнала, третий 22 и четвертый 23 селекторы знака сигнала, второй блок 24 выделения максимума, коммутатор 25, второй вычитатель 26, седьмой блок 27 выделения модуля сигнала, блок 28 сравнения, блок 29 контроля четности, кодер 30, сверточный декодер 31,блок 32 узловой синхронизации, функционально соединенные между собой. 1 табл., 5 ил. бшод :4lSfr S вб/ход ел С XI 4D СЛ N ю ю

Формула изобретения. Система передачи информации перфорированным сверточным кодом с восьми- фазной модуляцией, содержащая на передающей стороне первый кодер, вход которого является информационным входом системы, преобразователь када в фазу, выход которого подключен к входу модулятора, выход которого является входом линии связи, тактовые входы преобразователя кода в фазу и первого кодера являются первым и вторым тактовыми входами передаю щей стороны соответственно, на приемной стороне - демодулятор с бг.оког впсстанов- ления несущей, вход которого является вы- ходо.м линии связи, декодер, выход которого подключен к первому входу блока синхронизации и является информационным выхо .дом системы, тактовые входы декодера и блока синхронизации являются первым и вторым тактовыми входами приемной стороны, от л имеющаяся тем, что, с целью повышения пропускной способности системы, в нее введены на передающей стороне второй кодер, первый и второй выходы первого кодера подключены к первому и второму информационным входам второго кодера, первый, второй и третий выходы которого подключены к первому, второму и третьему информационным входам преобразователя кода в фазу соответственно, первый и второй тактовые входы второго кодера являются первым и вторым тактовыми входами передающей стороны соответственно, на приемной стороне - селекторы знака сигнала, блоки выделения модуля сигнала, блоки выделения максимума сигналов, блоки масштабирования сигнала, сумматоры, гшчитагели, блок сравнения, блок контроля четности, кодер и коммутатор, первый выход демодулятора с блоком восстансв/юния несущей подключен к объеиненным первому входу первого сумматора, входу первого блока масштабирования питала, входу первого блока выделения моуля сигнала и входу первого селектора знака сигнала, второй вход демодулятора с локом восстановления несущей подключен к объединенным первому входу второго сум- магсра, входу второго блока масштабирования сигнала, входу второго блока выделения модуля сигнала и входу второго.селектора знака сигнала., выходы первого и второго блоков выделения модуля сигналов подключены к первому и второму входам первого блока выделения максимума сигналов соот-, вётственно, выход которого подключен к первому входу блока сравнения, выходы первого и второго селекторов знака сигнаов подключены к первому и второму информационным входам коммутатора соответственно, выход первого блока масштабирования сигнала подключен к первым входам третьего сумматора и первого вычи- тателя, выход первого сумматора черезтре- тий блок рыделения модуля сигнала подключен к первым входам кодерам второго вычитателя, выход второго сумматора через четвертый блок выделения модуля сигнала подключен к вторым входам кодера и второго вычислителя, выход третьего сумматора подключен к второму входу второго сумматора, через пятый блок выделения модуля сигнала к первому входу второго блока выделения максимума сигналов и через тре- тий селектор знака сигналов к третьему информационному входу коммутатора, выход первого вычитателя подключен к второму входу первого сумматора, через шестой блок выделения модуля сигнала - к второму входу второго блока выделения максимума сигналов и через четвертый селектор знака сигнала - к четвертому информационному входу коммутатора, выход второго вычитателя через седьмой блок выделения модуля сигнала подключен к третьему входу кодера, выход второго блока выделения максимума сигналов подключен к второму входу блока сравнения, выход которого подключен к управляющим входам коммутатора и блока контроля четности, выход последнего подключен к четвертому входу кодера, первый и второй выходы коммутатора подключены к первому и второму входам блока контроля четности и к пятому и шестому входам кодера соответственно, выходы первой и второй групп выходов и лервый выход которого

подключены к соответствующим входам декодера, второй выход кодера подключен к вторым входам декодера и блока синхронизации, выход которого подключен к управляющему входу кодера, первый тактовый вход последнего является первым тактовым входом приемной стороны, второй тактовый вход кодера является третьим тактовым входом приемной стороны, тактовые входы блока сравнения, блока контроля четности, коммутатора и третий тактовый вход кодера объединены и являются четвертым тактовым входом приемной стороны.

Фие2

Я

ю

Ъ

70

-f

Г

6

EffMo

.

70

| Бансет В.Л., Дорофеев В.М | |||

| Цифровые методы в спутниковой связи | |||

| М.: Радио и связь, 1988 | |||

| с | |||

| Устройство для вытяжки и скручивания ровницы | 1923 |

|

SU214A1 |

Авторы

Даты

1993-02-15—Публикация

1990-04-03—Подача