Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при построении систем контроля, а также цифровых устройств, работающих в системе остаточных классов.

Известен сумматор по модулю три, содержащий 6 элементов И. 2 элемента ИЛИ- НЕ, 2 элемента ИЛИ и 2 элемента сложения по модулю два 1.

Недостатком сумматора является невозможность сложения по модулю три полных операндов (операндов, принимающих значения 0, 1, 2, 3)..

Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемомуявляется сумматор по модулю три, который выполняет сложение полных операндов и содержит два последовательно включенных одноразрядных двоичных сумматора.

Недостатком известного сумматора по модулю три является низкое быстродействие, определяемое глубиной схемы и равное

Т 4tsM. где TSM - быстродействие однораз рядного двоичного сумматора.

Цель изобретения - повышение быстродействия сумматора по модулю три;

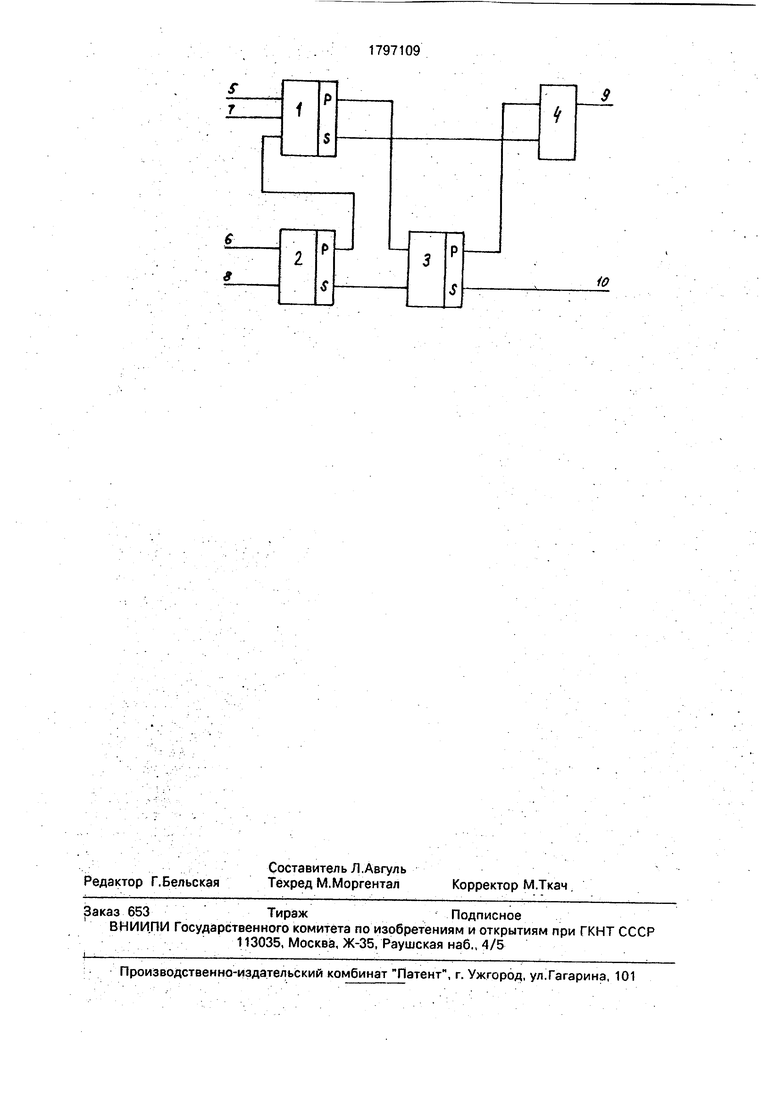

На чертеже представлена Функциональная схема сумматора по модулю три. Сумматор по модулю три содержит одноразрядный двоичный сумматор 1, два полусумматора 2 и 3, элемент ИЛИ 4, входы старшего 5 и младшего 6 разрядов первого операнда, входы старшего. 7 и младшего 8 разрядов второго операнда, выходы старшего 8 и младшего 10 разрядов суммы.

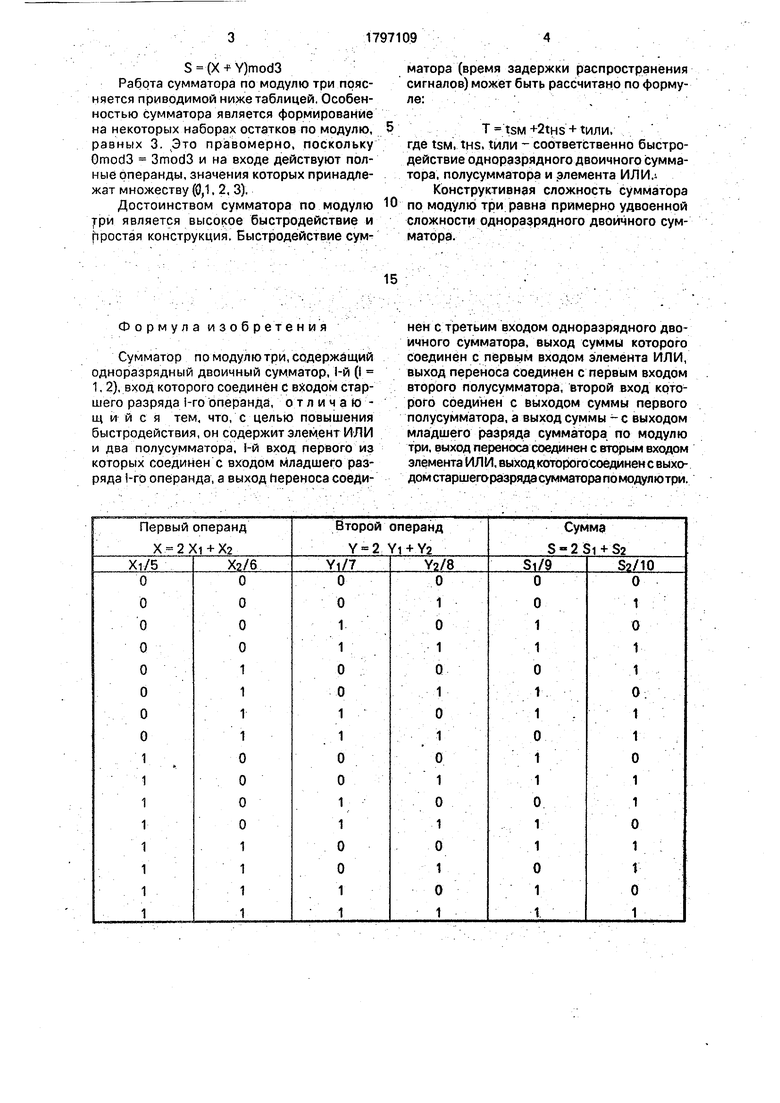

Сумматор по модулю три работает следующим образом. На входы 5 и 6 поступают соответственно старший Xi и младший Х2 разряды первого операнда X 2Xi + Xzi на входы 7 и 8 - соответственно, старший YI и младший Y2 разряды второго операнда Y 2Yt + Y2. На выходах 9 и 10 формируются значения соответственно старшего Si и младшего S2 разрядов суммы S 2Si + 82 по модулю три входных операндов X и Y:

Ё

VI

Ч VI

О О

S (X Y)mod3

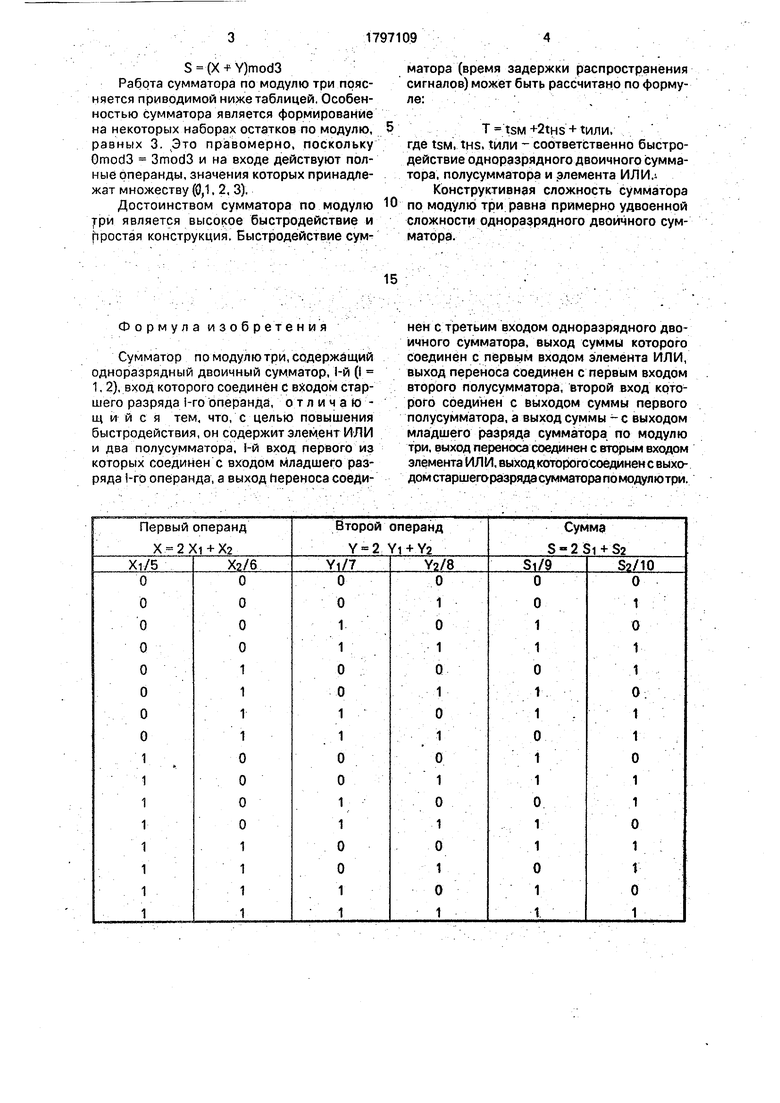

Работа сумматора по модулю три поясняется приводимой ниже таблицей, Особенностью сумматора является формирование на некоторых наборах остатков по модулю, равных 3. Это правомерно, поскольку Omod3 3mod3 и на входе действуют полные операнды, значения которых принадлежат множеству (0,1, 2, 3).

Достоинством сумматора по модулю три является высокое быстродействие и простая конструкция. Быстродействие сумматора (время задержки распространения сигналов) может быть рассчитано по формуле:

Т tsM +2tHS + т.или,

где tsM, tHs, или - соответственно быстродействие одноразрядного двоичного сумматора, полусумматора и элемента ИЛИл

Конструктивная сложность сумматора по модулю три равна примерно удвоенной сложности одноразрядного двоичного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018923C1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2018924C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018925C1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ШЕСТНАДЦАТИ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2050584C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018927C1 |

| Устройство для сложения по модулю три | 1991 |

|

SU1827671A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2+1 | 1992 |

|

RU2018929C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ N ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2047897C1 |

| Сумматор по модулю три | 1991 |

|

SU1798777A1 |

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при построении систем контроля и цифровых устройств, работающих в системе остаточных классов. Цель изобретения - повышение быстродействия сумматора по модулю три. Сумматор содержит одноразрядный двоичный сумматор, два полусумматора и элемент ИЛИ. На входы суммматора поступают двухразрядные полные операнды, на выходах формируется двухразрядная сумма по модулю три входных операндов. 1 ил., 1 табл.

Формула из обретения

Сумматор по модулю три, содержащий одноразрядный двоичный сумматор, 1-й (I 1, 2), вход которого соединён с входом старшего разряда i-ro операнда, о т л и ч а ю - щ и и с я тем, что, с целью повышения быстродействия, он содержит элемент ИЛИ и два полусумматора, 1-й вход первого из которых соединен с входом младшего разряда t-ro операнда, а выход Переноса соединен с третьим входом одноразрядного двоичного сумматора, выход суммы которого соединен с первым входом элемента ИЛИ, выход переноса соединен с первым входом второго полусумматора, второй вход которого соединен с выходом суммы первого полусумматора, а выход суммы - с выходом младшего разряда сумматора по модулю три, выход переноса соединен с вторым входом элемента ИЛ И, выход которого соединен с выходом старшего разряда сумматора помодулютри.

| Устройство для выделения максимального числа | 1986 |

|

SU1381483A1 |

| и др | |||

| Надежность и контроль ЭВМ | |||

| М.: Советское радио, 1978, с.-114-115, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-02-23—Публикация

1991-05-20—Подача